Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1574t-i-st |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

DS40001782C-page 31

| TABLE 3-9: PIC16(L)F1574/5/8/9 MEMORY MAI |                              |      |                              |      |                              |      | KS 16-23                     |      |                              |      |                              |      |                              |      |                              |

|-------------------------------------------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|

|                                           | BANK16                       |      | BANK17                       |      | BANK18                       |      | BANK19                       |      | BANK20                       |      | BANK21                       |      | BANK22                       |      | BANK23                       |

| 800h                                      | Core Registers               | 880h | Core Registers               | 900h | Core Registers               | 980h | Core Registers               | A00h | Core Registers               | A80h | Core Registers               | B00h | Core Registers               | B80h | Core Registers               |

| 80Bh                                      | (Table 3-2)                  | 88Bh | (Table 3-2)                  | 90Bh | (Table 3-2)                  | 98Bh | (Table 3-2)                  | A0Bh | (Table 3-2)                  | A8Bh | (Table 3-2)                  | B0Bh | (Table 3-2)                  | B8Bh | (Table 3-2)                  |

| 80Ch                                      | _                            | 88Ch | _                            | 90Ch | _                            | 98Ch | _                            | A0Ch |                              | A8Ch | _                            | B0Ch |                              | B8Ch | _                            |

| 80Dh                                      | _                            | 88Dh |                              | 90Dh | _                            | 98Dh | _                            | A0Dh | 1                            | A8Dh | _                            | B0Dh |                              | B8Dh | _                            |

| 80Eh                                      | _                            | 88Eh | _                            | 90Eh |                              | 98Eh |                              | A0Eh | _                            | A8Eh | _                            | B0Eh | _                            | B8Eh | _                            |

| 80Fh                                      | _                            | 88Fh | _                            | 90Fh |                              | 98Fh |                              | A0Fh | _                            | A8Fh | _                            | B0Fh | _                            | B8Fh | _                            |

| 810h                                      | _                            | 890h | _                            | 910h |                              | 990h |                              | A10h | _                            | A90h | _                            | B10h | _                            | B90h | _                            |

| 811h                                      | _                            | 891h | _                            | 911h |                              | 991h |                              | A11h | _                            | A91h | _                            | B11h | _                            | B91h | _                            |

| 812h                                      | _                            | 892h | _                            | 912h |                              | 992h |                              | A12h | _                            | A92h | _                            | B12h | _                            | B92h | _                            |

| 813h                                      | _                            | 893h | _                            | 913h |                              | 993h |                              | A13h | _                            | A93h | _                            | B13h | _                            | B93h | _                            |

| 814h                                      | _                            | 894h | _                            | 914h |                              | 994h |                              | A14h | _                            | A94h | _                            | B14h | _                            | B94h | _                            |

| 815h                                      | _                            | 895h | _                            | 915h |                              | 995h |                              | A15h | _                            | A95h | _                            | B15h | _                            | B95h | _                            |

| 816h                                      | _                            | 896h | _                            | 916h | _                            | 996h |                              | A16h | _                            | A96h | _                            | B16h | _                            | B96h | _                            |

| 817h                                      | _                            | 897h | _                            | 917h | _                            | 997h | _                            | A17h | _                            | A97h | _                            | B17h | _                            | B97h | _                            |

| 818h                                      | _                            | 898h | _                            | 918h | _                            | 998h | _                            | A18h | _                            | A98h | _                            | B18h | _                            | B98h | _                            |

| 819h                                      | _                            | 899h | _                            | 919h | _                            | 999h | _                            | A19h | _                            | A99h | _                            | B19h | _                            | B99h | _                            |

| 81Ah                                      | _                            | 89Ah | _                            | 91Ah | _                            | 99Ah | _                            | A1Ah | _                            | A9Ah | _                            | B1Ah | _                            | B9Ah | _                            |

| 81Bh                                      | _                            | 89Bh | _                            | 91Bh |                              | 99Bh | _                            | A1Bh | _                            | A9Bh | _                            | B1Bh | _                            | B9Bh | _                            |

| 81Ch                                      | _                            | 89Ch | _                            | 91Ch |                              | 99Ch |                              | A1Ch | _                            | A9Ch | _                            | B1Ch | _                            | B9Ch | _                            |

| 81Dh                                      | _                            | 89Dh | _                            | 91Dh |                              | 99Dh |                              | A1Dh | _                            | A9Dh | _                            | B1Dh | _                            | B9Dh | _                            |

| 81Eh                                      | _                            | 89Eh | _                            | 91Eh | _                            | 99Eh | _                            | A1Eh | _                            | A9Eh | _                            | B1Eh | _                            | B9Eh | _                            |

| 81Fh                                      | _                            | 89Fh | _                            | 91Fh | _                            | 99Fh | _                            | A1Fh | _                            | A9Fh | _                            | B1Fh | _                            | B9Fh | _                            |

| 820h                                      |                              | 8A0h |                              | 920h |                              | 9A0h |                              | A20h |                              | AA0h |                              | B20h |                              | BA0h |                              |

|                                           | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |

| 86Fh                                      |                              | 8EFh |                              | 96Fh |                              | 9EFh |                              | A6Fh |                              | AEFh |                              | B6Fh |                              | BEFh |                              |

| 870h                                      |                              | 8F0h |                              | 970h |                              | 9F0h |                              | A70h |                              | AF0h |                              | B70h |                              | BF0h |                              |

|                                           | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |

| 87Fh                                      |                              | 8FFh |                              | 97Fh |                              | 9FFh |                              | A7Fh |                              | AFFh |                              | B7Fh |                              | BFFh |                              |

**Legend:** = Unimplemented data memory locations, read as '0'.

TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY

| Address | Name                 | Bit 7              | Bit 6              | Bit 5          | Bit 4           | Bit 3          | Bit 2  | Bit 1  | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------|--------------------|--------------------|----------------|-----------------|----------------|--------|--------|---------|----------------------|---------------------------------|

| Bank 0  |                      |                    |                    |                |                 |                |        |        |         |                      |                                 |

| 00Ch    | PORTA                | _                  | _                  | RA5            | RA4             | RA3            | RA2    | RA1    | RA0     | xx xxxx              | xx xxxx                         |

| 00Dh    | PORTB <sup>(1)</sup> | RB7                | RB6                | RB5            | RB4             | _              | _      | _      | _       | xxxx                 | xxxx                            |

| 00Eh    | PORTC                | RC7 <sup>(1)</sup> | RC6 <sup>(1)</sup> | RC5            | RC4             | RC3            | RC2    | RC1    | RC0     | xxxx xxxx            | xxxx xxxx                       |

| 00Fh    | _                    | Unimplemen         | nted               |                |                 |                |        |        |         | _                    | _                               |

| 010h    | _                    | Unimplemer         | nted               |                |                 |                |        |        |         | _                    | _                               |

| 011h    | PIR1                 | TMR1GIF            | ADIF               | RCIF           | TXIF            | _              | _      | TMR2IF | TMR1IF  | 000000               | 000000                          |

| 012h    | PIR2                 | _                  | C2IF               | C1IF           | _               | _              | _      | _      | _       | -00                  | -00                             |

| 013h    | PIR3                 | PWM4IF             | PWM3IF             | PWM2IF         | PWM1IF          | _              | _      | _      | _       | 0000                 | 0000                            |

| 014h    | _                    |                    |                    |                |                 |                |        |        |         | _                    | _                               |

| 015h    | TMR0                 | Holding Reg        | ister for the      | 8-bit Timer0 ( | Count           |                |        |        |         | xxxx xxxx            | uuuu uuuu                       |

| 016h    | TMR1L                | Holding Reg        | ister for the I    | Least Signific | ant Byte of the | 16-bit TMR1 Co | ount   |        |         | xxxx xxxx            | uuuu uuuu                       |

| 017h    | TMR1H                | Holding Reg        | ister for the I    | Most Significa | ant Byte of the | 16-bit TMR1 Co | unt    |        |         | xxxx xxxx            | uuuu uuuu                       |

| 018h    | T1CON                | TMR1C              | S<1:0>             | T1CK           | PS<1:0>         | _              | T1SYNC | _      | TMR10N  | 0000 -0-0            | uuuu -u-u                       |

| 019h    | T1GCON               | TMR1GE             | T1GPOL             | T1GTM          | T1GSPM          | T1GGO/<br>DONE | T1GVAL | T1GS   | S<1:0>  | 0000 0x00            | uuuu uxuu                       |

| 01Ah    | TMR2                 | Timer2 Mod         | ule Register       |                |                 |                |        |        |         | 0000 0000            | 0000 0000                       |

| 01Bh    | PR2                  | Timer2 Perio       | od Register        |                |                 |                |        |        |         | 1111 1111            | 1111 1111                       |

| 01Ch    | T2CON                | _                  |                    | T2OL           | JTPS<3:0>       |                | TMR2ON | T2CKF  | PS<1:0> | -000 0000            | -000 0000                       |

| 01Dh    | _                    | Unimplemen         | Unimplemented      |                |                 |                |        |        |         |                      | _                               |

| 01Eh    | _                    | Unimplemen         | nted               |                |                 |                |        |        |         | _                    | _                               |

| 01Fh    | _                    | Unimplemer         | nted               |                |                 |                |        |        |         | _                    | _                               |

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.Note1:PIC16(L)F1578/9 only.2:PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6 | Bit 5 | Bit 4    | Bit 3  | Bit 2  | Bit 1    | Bit 0  | Register on Page |

|---------|--------|-------|-------|----------|--------|--------|----------|--------|------------------|

| OSCCON  | SPLLEN |       | IRCF  | <3:0>    |        | _      | SCS<1:0> |        | 69               |

| OSCSTAT | _      | PLLR  | OSTS  | HFIOFR   | HFIOFL | MFIOFR | LFIOFR   | HFIOFS | 70               |

| OSCTUNE | _      |       |       | TUN<5:0> |        |        |          |        |                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

## TABLE 5-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|------------------|

| CONFICA | 13:8 | _       | _       | _        | _        | CLKOUTEN | BOREN<1:0> |         | _       | 50               |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | _          | FOSC    | C<1:0>  | 56               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### REGISTER 11-3: LATA: PORTA DATA LATCH REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|-----|---------|---------|---------|

| _     | _   | LATA5   | LATA4   | _   | LATA2   | LATA1   | LATA0   |

| bit 7 |     |         |         |     |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 LATA<5:4>: RA<5:4> Output Latch Value bits<sup>(1)</sup>

bit 3 **Unimplemented:** Read as '0'

bit 2-0 LATA<2:0>: RA<2:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 U-0 U-0 |   | R/W-1/1 | R/W-1/1 U-0 F |       | R/W-1/1 R/W-1/1 |       |

|-------|-------------|---|---------|---------------|-------|-----------------|-------|

| _     | _           | _ | ANSA4   | _             | ANSA2 | ANSA1           | ANSA0 |

| bit 7 |             |   |         |               |       |                 | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-5 **Unimplemented:** Read as '0'

bit 4 ANSA4: Analog Select between Analog or Digital Function on pins RA4, respectively

$1 = \text{Analog input. Pin is assigned as analog input}^{(1)}$ . Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

bit 3 **Unimplemented:** Read as '0'

bit 2-0 ANSA<2:0>: Analog Select between Analog or Digital Function on pins RA<2:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

## REGISTER 11-14: ODCONB: PORTB OPEN DRAIN CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| ODB7    | ODB6    | ODB5    | ODB4    | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 ODB<7:4>: PORTB Open-Drain Enable bits

For RB<7:4> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

bit 3-0 **Unimplemented:** Read as '0'

#### REGISTER 11-15: SLRCONB: PORTB SLEW RATE CONTROL REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 SLRB<7:4>: PORTB Slew Rate Enable bits

For RB<7:4> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

bit 3-0 **Unimplemented:** Read as '0'

#### REGISTER 11-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 INLVLB<7:4>: PORTB Input Level Select bits

For RB<7:4> pins, respectively

1 = ST input used for port reads and interrupt-on-change 0 = TTL input used for port reads and interrupt-on-change

bit 3-0 **Unimplemented:** Read as '0'

TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name       | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|------------|------------------------|------------------------|---------|---------|---------|---------|---------|---------|------------------|

| ANSELC     | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | _       | _       | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 132              |

| INLVLC     | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 133              |

| LATC       | LATC7 <sup>(1)</sup>   | LATC6 <sup>(1)</sup>   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 131              |

| ODCONC     | ODC7 <sup>(1)</sup>    | ODC6 <sup>(1)</sup>    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    | 133              |

| OPTION_REG | WPUEN                  | INTEDG                 | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         | 178              |

| PORTC      | RC7 <sup>(1)</sup>     | RC6 <sup>(1)</sup>     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 131              |

| SLRCONC    | SLRC7 <sup>(1)</sup>   | SLRC6 <sup>(1)</sup>   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 133              |

| TRISC      | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 131              |

| WPUC       | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 132              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: PIC16(L)F1578/9 only.

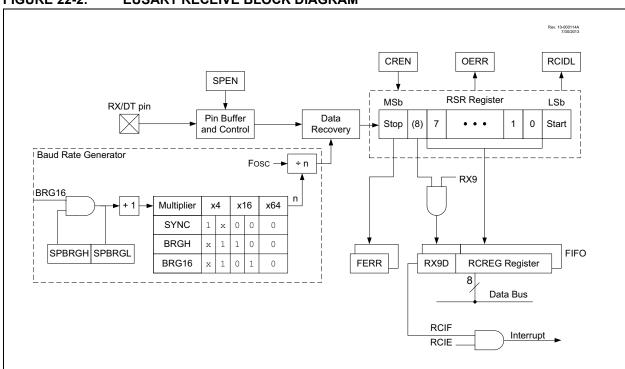

## FIGURE 22-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- · Transmit Status and Control (TXSTA)

- · Receive Status and Control (RCSTA)

- · Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

## FIGURE 22-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

## FIGURE 22-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

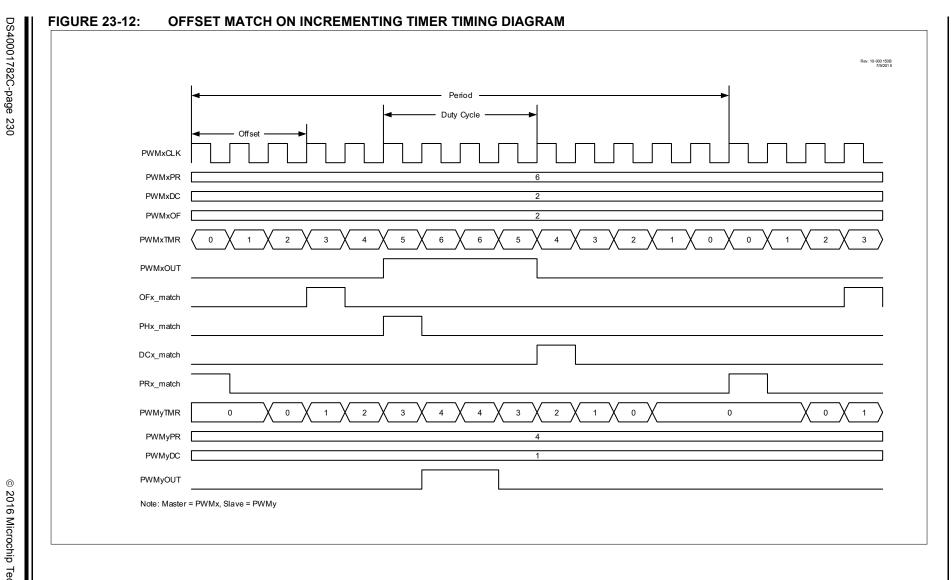

#### REGISTER 23-6: PWMxOFCON: PWM OFFSET TRIGGER SOURCE SELECT REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0            | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|--------------------|-----|-----|---------|---------|

| _     | OFM     | <1:0>   | OFO <sup>(1)</sup> | _   | _   | OFS     | <1:0>   |

| bit 7 |         |         |                    |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '0'

bit 6-5 **OFM<1:0>:** Offset Mode Select bits

11 = Continuous Slave Run mode with Immediate Reset and synchronized start, when the selected Offset Trigger occurs.

10 = One-shot Slave Run mode with synchronized start, when the selected Offset Trigger occurs 01 = Independent Slave Run mode with synchronized start, when the selected Offset Trigger occurs

00 = Independent Run mode

bit 4 **OFO:** Offset Match Output Control bit

If MODE<1:0> = 11 (PWM Center-Aligned mode):

1 = OFx\_match occurs on counter match when counter decrementing, (second match)

0 = OFx\_match occurs on counter match when counter incrementing, (first match)

<u>If MODE<1:0> = 00</u>,  $01\underline{\text{ or }}10\underline{\text{ (all other modes)}}$ :

bit is ignored

bit 3-2 **Unimplemented:** Read as '0'

bit 1-0 **OFS<1:0>:** Offset Trigger Source Select bits

11 = OF4\_match<sup>(1)</sup>

10 = OF3\_match<sup>(1)</sup>

01 = OF2\_match<sup>(1)</sup>

00 = OF1\_match<sup>(1)</sup>

Note 1: The OF match corresponding to the PWM used becomes reserved.

## 24.10 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep, provided that the CWG module is enabled, the input source is active, and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, the CPU will go idle during Sleep, but the CWG will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

## 24.11 Configuring the CWG

The following steps illustrate how to properly configure the CWG to ensure a synchronous start:

- Ensure that the TRIS control bits corresponding to CWGxA and CWGxB are set so that both are configured as inputs.

- 2. Clear the GxEN bit, if not already cleared.

- Set desired dead-band times with the CWGxDBR and CWGxDBF registers.

- 4. Setup the following controls in CWGxCON2 auto-shutdown register:

- · Select desired shutdown source.

- Select both output overrides to the desired levels (this is necessary even if not using auto-shutdown because start-up will be from a shutdown state).

- Set the GxASE bit and clear the GxARSEN bit

- Select the desired input source using the CWGxCON1 register.

- Configure the following controls in CWGxCON0 register:

- · Select desired clock source.

- Select the desired output polarities.

- 7. Set the GxEN bit.

- 8. Clear TRIS control bits corresponding to CWGxA and CWGxB to be used to configure those pins as outputs.

- If auto-restart is to be used, set the GxARSEN bit and the GxASE bit will be cleared automatically. Otherwise, clear the GxASE bit to start the CWG.

#### 24.11.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the GxASDLA and GxASDLB bits of the CWGxCON1 register (Register 24-3). GxASDLA controls the CWG1A override level and GxASDLB controls the CWG1B override level. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not apply to the override level.

#### 24.11.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to have resume operation:

- · Software controlled

- · Auto-restart

The restart method is selected with the GxARSEN bit of the CWGxCON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 24-5 and Figure 24-6.

#### 24.11.2.1 Software Controlled Restart

When the GxARSEN bit of the CWGxCON2 register is cleared, the CWG must be restarted after an auto-shut-down event by software.

Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the GxASE bit will remain set. The overrides will remain in effect until the first rising edge event after the GxASE bit is cleared. The CWG will then resume operation.

#### 24.11.2.2 Auto-Restart

When the GxARSEN bit of the CWGxCON2 register is set, the CWG will restart from the auto-shutdown state automatically.

The GxASE bit will clear automatically when all shutdown sources go low. The overrides will remain in effect until the first rising edge event after the GxASE bit is cleared. The CWG will then resume operation.

TABLE 26-3: ENHANCED MID-RANGE INSTRUCTION SET

| Mnemonic, |      | Description                                          |          |          | 14-Bit ( | Opcode   | )    | Status   | Natas                                        |

|-----------|------|------------------------------------------------------|----------|----------|----------|----------|------|----------|----------------------------------------------|

| Oper      | ands | Description                                          | Cycles   | MSb      |          |          | LSb  | Affected | Notes                                        |

|           |      | BYTE-ORIENTED FILE REGIS                             | TER OPE  | RATIO    | NS       |          |      |          |                                              |

| ADDWF     | f, d | Add W and f                                          | 1        | 00       | 0111     | dfff     | ffff | C, DC, Z | 2                                            |

| ADDWFC    | f, d | Add with Carry W and f                               | 1        | 11       | 1101     | dfff     | ffff | C, DC, Z | 2                                            |

| ANDWF     | f, d | AND W with f                                         | 1        | 00       | 0101     | dfff     | ffff | Z        | 2                                            |

| ASRF      | f, d | Arithmetic Right Shift                               | 1        | 11       | 0111     | dfff     | ffff | C, Z     | 2                                            |

| LSLF      | f, d | Logical Left Shift                                   | 1        | 11       | 0101     | dfff     | ffff | C, Z     | 2                                            |

| LSRF      | f, d | Logical Right Shift                                  | 1        | 11       | 0110     | dfff     | ffff | C, Z     | 2                                            |

| CLRF      | f    | Clear f                                              | 1        | 0.0      | 0001     | lfff     | ffff | Z        | 2                                            |

| CLRW      | _    | Clear W                                              | 1        | 00       | 0001     | 0000     | 00xx | Z        |                                              |

| COMF      | f, d | Complement f                                         | 1        | 00       | 1001     | dfff     | ffff | Z        | 2                                            |

| DECF      | f, d | Decrement f                                          | 1        | 0.0      | 0011     | dfff     | ffff | Z        | 2                                            |

| INCF      | f, d | Increment f                                          | 1        | 0.0      | 1010     | dfff     | ffff | Z        | 2                                            |

| IORWF     | f, d | Inclusive OR W with f                                | 1        | 0.0      | 0100     | dfff     | ffff | Z        | 2                                            |

| MOVF      | f, d | Move f                                               | 1        | 00       | 1000     | dfff     | ffff | Z        | 2                                            |

| MOVWF     | f    | Move W to f                                          | 1        | 00       | 0000     | 1fff     |      |          | 2                                            |

| RLF       | f, d | Rotate Left f through Carry                          | 1        | 0.0      | 1101     | dfff     | ffff | С        | 2                                            |

| RRF       | f, d | Rotate Right f through Carry                         | 1        | 0.0      |          | dfff     |      | С        | 2                                            |

| SUBWF     | f, d | Subtract W from f                                    | 1        | 0.0      | 0010     | dfff     | ffff | C, DC, Z | 2                                            |

| SUBWFB    | f, d | Subtract with Borrow W from f                        | 1        | 11       |          | dfff     |      | C, DC, Z | 2                                            |

| SWAPF     | f, d | Swap nibbles in f                                    | 1        | 00       | 1110     | dfff     | ffff | 0,20,2   | 2                                            |

| XORWF     | f. d | Exclusive OR W with f                                | 1        | 0.0      | 0110     | dfff     | ffff | Z        | 2                                            |

|           | -,   | BYTE ORIENTED SKIP O                                 | PERATION | ONS      |          |          |      | <u> </u> | <u>                                     </u> |

| DECFSZ    | f, d | Decrement f, Skip if 0                               | 1(2)     | 0.0      | 1011     | dfff     | ffff |          | 1, 2                                         |

| INCFSZ    | f, d | Increment f, Skip if 0                               | 1(2)     | 00       | 1111     | dfff     | ffff |          | 1, 2                                         |

|           | I.   | BIT-ORIENTED FILE REGIST                             | ER OPER  | RATION   | S        |          |      |          |                                              |

| BCF       | f, b | Bit Clear f                                          | 1        | 01       | 00bb     | bfff     | ffff |          | 2                                            |

| BSF       | f, b | Bit Set f                                            | 1        | 01       | 01bb     | bfff     | ffff |          | 2                                            |

|           |      | BIT-ORIENTED SKIP O                                  | PERATIO  | NS       |          | <u>I</u> | I.   |          |                                              |

| BTFSC     | f, b | Bit Test f, Skip if Clear                            | 1 (2)    | 01       | 10bb     | bfff     | ffff |          | 1, 2                                         |

| BTFSS     | f, b | Bit Test f, Skip if Set                              | 1 (2)    | 01       | 11bb     | bfff     | ffff |          | 1, 2                                         |

| 330       | -, ~ | LITERAL OPERA                                        |          | <u> </u> |          | ~        |      | <u> </u> | ı ·, <del>-</del>                            |

| ADDLW     | k    | Add literal and W                                    | 1        | 11       | 1110     | kkkk     | kkkk | C, DC, Z |                                              |

| ANDLW     | k    | AND literal with W                                   | 1        | 11       | 1001     | kkkk     |      | Z Z      |                                              |

| IORLW     | k    | Inclusive OR literal with W                          | 1        | 11       | 1000     | kkkk     |      | Z        |                                              |

| MOVLB     | k    | Move literal to BSR                                  | 1        | 00       | 0000     | 001k     |      |          |                                              |

| MOVLP     | k    | Move literal to PCLATH                               | 1        | 11       | 0001     | 1kkk     |      |          |                                              |

| MOVLW     | k    | Move literal to W                                    | 1        | 11       | 0000     | kkkk     |      |          |                                              |

| SUBLW     | k    | Subtract W from literal                              | 1        | 11       | 1100     | kkkk     |      | C, DC, Z |                                              |

| XORLW     | k    | Exclusive OR literal with W                          | 1        | 11       |          | kkkk     |      | Z        |                                              |

|           |      | m Counter (PC) is modified, or a conditional test is | . ·      |          |          |          |      |          |                                              |

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>2:</sup> If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVIW ++FSRn<br>[ label ] MOVIWFSRn<br>[ label ] MOVIW FSRn++<br>[ label ] MOVIW FSRn<br>[ label ] MOVIW k[FSRn]                                                                                                                 |

| Operands:        | $\begin{split} & n \in [0,1] \\ & mm \in [00,01,10,11] \\ & -32 \le k \le 31 \end{split}$                                                                                                                                                  |

| Operation:       | INDFn → W Effective address is determined by • FSR + 1 (preincrement) • FSR - 1 (predecrement) • FSR + k (relative offset) After the Move, the FSR value will be either: • FSR + 1 (all increments) • FSR - 1 (all decrements) • Unchanged |

| Status Affected: | Z                                                                                                                                                                                                                                          |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description: This instruction is used to move data

between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h - FFFFh. Incrementing/decrementing it beyond these bounds will cause it to

wrap-around.

## MOVLB Move literal to BSR

| Syntax: | [ label ] MOVLB | k |

|---------|-----------------|---|

|---------|-----------------|---|

$\label{eq:continuous} \begin{array}{ll} \text{Operands:} & 0 \leq k \leq 31 \\ \\ \text{Operation:} & k \rightarrow \text{BSR} \\ \\ \text{Status Affected:} & \text{None} \end{array}$

Description: The 5-bit literal 'k' is loaded into the

Bank Select Register (BSR).

| MOVLP            | Move literal to PCLATH                                    |  |  |  |  |  |

|------------------|-----------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] MOVLP k                                         |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 127$                                       |  |  |  |  |  |

| Operation:       | $k \rightarrow PCLATH$                                    |  |  |  |  |  |

| Status Affected: | None                                                      |  |  |  |  |  |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register. |  |  |  |  |  |

|                  |                                                           |  |  |  |  |  |

| MOVLW            | Move literal to W                                                                         |

|------------------|-------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVLW k                                                                           |

| Operands:        | $0 \leq k \leq 255$                                                                       |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction W = 0x5A                                                                |

| MOVWF            | Move W to f                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVWF f                                                                               |

| Operands:        | $0 \leq f \leq 127$                                                                             |

| Operation:       | $(W) \rightarrow (f)$                                                                           |

| Status Affected: | None                                                                                            |

| Description:     | Move data from W register to register 'f'.                                                      |

| Words:           | 1                                                                                               |

| Cycles:          | 1                                                                                               |

| Example:         | MOVWF OPTION_REG                                                                                |

|                  | Before Instruction  OPTION_REG = 0xFF  W = 0x4F  After Instruction  OPTION_REG = 0x4F  W = 0x4F |

## **TABLE 27-6: THERMAL CHARACTERISTICS**

Standard Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym.      | Characteristic                         | Тур.  | Units | Conditions                                               |

|---------------|-----------|----------------------------------------|-------|-------|----------------------------------------------------------|

| TH01          | θЈА       | Thermal Resistance Junction to Ambient | 70    | °C/W  | 14-pin PDIP package                                      |

|               |           |                                        | 95.3  | °C/W  | 14-pin SOIC package                                      |

|               |           |                                        | 100   | °C/W  | 14-pin TSSOP package                                     |

|               |           |                                        | 31.8  | °C/W  | 16-pin UQFN 4x4mm package                                |

|               |           |                                        | 62.2  | °C/W  | 20-pin PDIP package                                      |

|               |           |                                        | 77.7  | °C/W  | 20-pin SOIC package                                      |

|               |           |                                        | 87.3  | °C/W  | 20-pin SSOP package                                      |

|               |           |                                        | 32.8  | °C/W  | 20-pin UQFN 4x4mm package                                |

| TH02          | θJC       | Thermal Resistance Junction to Case    | 32.75 | °C/W  | 14-pin PDIP package                                      |

|               |           |                                        | 31    | °C/W  | 14-pin SOIC package                                      |

|               |           |                                        | 24.4  | °C/W  | 14-pin TSSOP package                                     |

|               |           |                                        | 24.4  | °C/W  | 16-pin UQFN 4x4mm package                                |

|               |           |                                        | 27.5  | °C/W  | 20-pin PDIP package                                      |

|               |           |                                        | 23.1  | °C/W  | 20-pin SOIC package                                      |

|               |           |                                        | 31.1  | °C/W  | 20-pin SSOP package                                      |

|               |           |                                        | 27.4  | °C/W  | 20-pin UQFN 4x4mm package                                |

| TH03          | TJMAX     | Maximum Junction Temperature           | 150   | °C    |                                                          |

| TH04          | PD        | Power Dissipation                      | _     | W     | PD = PINTERNAL + PI/O                                    |

| TH05          | PINTERNAL | Internal Power Dissipation             | _     | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| TH06          | Pı/o      | I/O Power Dissipation                  | _     | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07          | PDER      | Derated Power                          | _     | W     | PDER = PDMAX (TJ - TA)/θJA <sup>(2)</sup>                |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

<sup>2:</sup> TA = Ambient Temperature; TJ = Junction Temperature

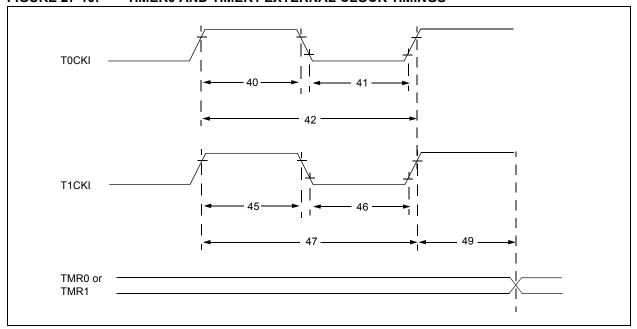

FIGURE 27-10: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 27-12: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |           |                           |                  |                |              |      |        |       |                     |

|---------------------------------------------------------|-----------|---------------------------|------------------|----------------|--------------|------|--------|-------|---------------------|

| Param.<br>No.                                           | Sym.      |                           | Characteristic   |                | Min.         | Тур† | Max.   | Units | Conditions          |

| 40*                                                     | Тт0Н      | T0CKI High F              | Pulse Width      | No Prescaler   | 0.5 Tcy + 20 | _    | _      | ns    |                     |

|                                                         |           |                           |                  | With Prescaler | 10           | _    | _      | ns    |                     |

| 41*                                                     | TT0L      | T0CKI Low F               | Pulse Width      | No Prescaler   | 0.5 Tcy + 20 | _    | _      | ns    |                     |

|                                                         |           |                           |                  | With Prescaler | 10           | _    | _      | ns    |                     |

| 42*                                                     | Тт0Р      | T0CKI Period              | d                | ·              |              | _    | _      | ns    | N = prescale value  |

| 45*                                                     | T⊤1H      | T1CKI High                | Synchronous, N   | No Prescaler   | 0.5 Tcy + 20 | _    | -      | ns    |                     |

|                                                         |           | Time                      | Synchronous, v   | vith Prescaler | 15           | _    | _      | ns    |                     |

|                                                         |           |                           | Asynchronous     |                | 30           | _    | _      | ns    |                     |

| 46*                                                     | TT1L      | T1CKI Low                 | Synchronous, N   | No Prescaler   | 0.5 Tcy + 20 | _    | _      | ns    |                     |

|                                                         |           | Time                      | Synchronous, v   | vith Prescaler | 15           | _    | _      | ns    |                     |

|                                                         |           |                           | Asynchronous     |                | 30           | _    | _      | ns    |                     |

| 47*                                                     | Тт1Р      | T1CKI Input<br>Period     | Synchronous      | Synchronous    |              | _    | _      | ns    | N = prescale value  |

|                                                         |           |                           | Asynchronous     |                | 60           | _    | _      | ns    |                     |

| 49*                                                     | TCKEZTMR1 | Delay from E<br>Increment | xternal Clock Ed | dge to Timer   | 2 Tosc       | _    | 7 Tosc | _     | Timers in Sync mode |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## **TABLE 27-14: ADC CONVERSION REQUIREMENTS**

| Standard Operating Conditions (unless otherwise stated) |      |                                                                 |      |                           |      |       |                                              |  |  |

|---------------------------------------------------------|------|-----------------------------------------------------------------|------|---------------------------|------|-------|----------------------------------------------|--|--|

| Param.<br>No.                                           | Sym. | Characteristic                                                  | Min. | Typ†                      | Max. | Units | Conditions                                   |  |  |

| AD130*                                                  | TAD  | ADC Clock Period (TADC)                                         | 1.0  | _                         | 6.0  | μS    | Fosc-based                                   |  |  |

|                                                         |      | ADC Internal FRC Oscillator Period (TFRC)                       | 1.0  | 2.0                       | 6.0  | μS    | ADCS<2:0> = $\times$ 11 (ADC FRC mode)       |  |  |

| AD131                                                   | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _    | 11                        | _    | TAD   | Set GO/DONE bit to conversion complete       |  |  |

| AD132*                                                  | TACQ | Acquisition Time                                                | _    | 5.0                       | _    | μS    |                                              |  |  |

| AD133*                                                  | THCD | Holding Capacitor Disconnect Time                               | _    | 1/2 TAD<br>1/2 TAD + 1TCY | _    |       | Fosc-based<br>ADCS<2:0> = x11 (ADC FRC mode) |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: The ADRES register may be read on the following TcY cycle.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

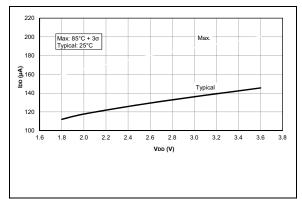

**FIGURE 28-13:** IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16LF1574/5/8/9 Only.

FIGURE 28-14: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16F1574/5/8/9 Only.

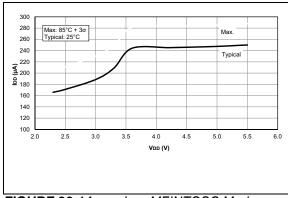

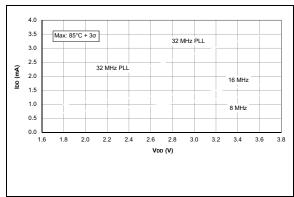

FIGURE 28-15: IDD Typical, HFINTOSC Mode, PIC16LF1574/5/8/9 Only.

FIGURE 28-16: IDD Maximum, HFINTOSC Mode, PIC16LF1574/5/8/9 Only.

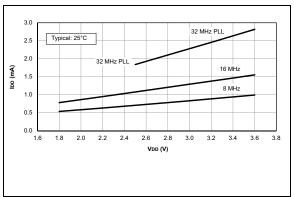

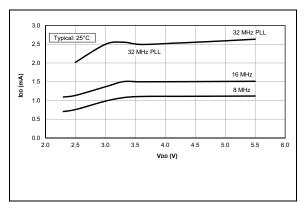

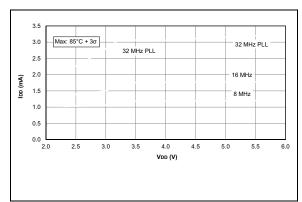

FIGURE 28-17: IDD Typical, HFINTOSC Mode, PIC16F1574/5/8/9 Only.

FIGURE 28-18: IDD Maximum, HFINTOSC Mode, PIC16F1574/5/8/9 Only.

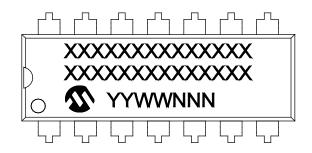

## 30.0 PACKAGING INFORMATION

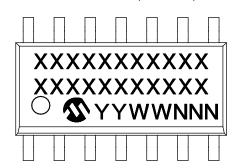

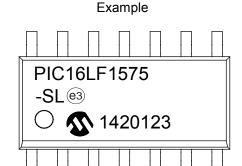

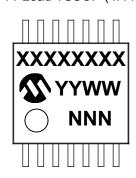

## 30.1 Package Marking Information

14-Lead PDIP (300 mil)

PIC16LF1574 -P @3 1420123

Example

14-Lead SOIC (3.90 mm)

14-Lead TSSOP (4.4 mm)

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

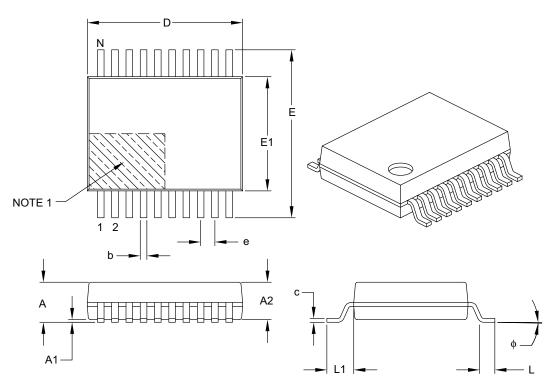

## 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units      |      |          | MILLIMETERS |  |  |  |

|--------------------------|------------|------|----------|-------------|--|--|--|

| Dimens                   | ion Limits | MIN  | NOM      | MAX         |  |  |  |

| Number of Pins           | N          |      | 20       |             |  |  |  |

| Pitch                    | е          |      | 0.65 BSC |             |  |  |  |

| Overall Height           | Α          | _    | _        | 2.00        |  |  |  |

| Molded Package Thickness | A2         | 1.65 | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1         | 0.05 | _        | _           |  |  |  |

| Overall Width            | Е          | 7.40 | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1         | 5.00 | 5.30     | 5.60        |  |  |  |

| Overall Length           | D          | 6.90 | 7.20     | 7.50        |  |  |  |

| Foot Length              | L          | 0.55 | 0.75     | 0.95        |  |  |  |

| Footprint                | 1.25 REF   |      |          |             |  |  |  |

| Lead Thickness           | С          | 0.09 | _        | 0.25        |  |  |  |

| Foot Angle               | 0°         | 4°   | 8°       |             |  |  |  |

| Lead Width               | b          | 0.22 | _        | 0.38        |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B