## Microchip Technology - PIC16F1575-E/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | LINbus, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1575-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Analog Peripherals**

- 10-Bit Analog-to-Digital Converter (ADC):

- Up to 12 external channels

- Conversion available during Sleep

- Two Comparators:

- Low-Power/High-Speed modes

- Fixed Voltage Reference at (non)inverting input(s)

- Comparator outputs externally accessible

- Synchronization with Timer1 clock source

- Software hysteresis enable

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- Voltage Reference:

TABLE 1:

- Fixed Voltage Reference with 1.024V, 2.048V and 4.096V output levels

## **Clocking Structure**

- Precision Internal Oscillator:

- Factory calibrated ±1%, typical

- Software-selectable clock speeds from 31 kHz to 32 MHz

- · External Oscillator Block with:

- Two external clock modes up to 32 MHz

- Digital Oscillator Input Available

Program Flash Memory Memory 8-Bit/16-Bit Timers SRAM (bytes) Data Sheet Index I0-Bit ADC (ch) Comparators **I6-Bit PWM** Bit DAC Debug<sup>(1)</sup> (Kwords) Pins (Kbytes) EUSART Program Flash CWG PPS Device <u>0</u> Data PIC12(L)F1571 1.75 2/4(2) 128 6 1 3 4 1 1 0 Ν Ι (A) 1 2/4(2) PIC12(L)F1572 (A) 2 3.5 256 6 1 3 4 1 1 1 Ν L 2/5(3)PIC16(L)F1574 12 2 (B) 4 7 512 4 8 1 1 1 Y Т 2/5(3) PIC16(L)F1575 8 14 1024 12 2 4 8 1 1 1 Y I (B) 2/5<sup>(3)</sup> PIC16(L)F1578 (B) 4 7 512 18 2 4 12 1 1 1 Y L 2/5(3) PIC16(L)F1579 8 14 18 2 12 1 Y (B) 1024 4 1 1 Т

**Note 1:** I – Debugging integrated on chip.

2: Three additional 16-bit timers available when not using the 16-bit PWM outputs.

PIC12(L)F1571/2 AND PIC16(L)F1574/5/8/9 FAMILY TYPES

3: Four additional 16-bit timers available when not using the 16-bit PWM outputs.

#### **Data Sheet Index:**

- A) DS-40001723 PIC12(L)F1571/2 Data Sheet, 8-Pin Flash, 8-bit MCU with High-Precision 16-bit PWM

- B) Future Release PIC16(L)F1574/5/8/9 Data Sheet, 8-Pin Flash, 8-bit MCU with High-Precision 16-bit PWM

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

#### TABLE 2: PACKAGES

| Packages      | PDIP | SOIC | TSSOP | SSOP | UQFN |

|---------------|------|------|-------|------|------|

| PIC16(L)F1574 | •    | •    | •     |      | •    |

| PIC16(L)F1575 | •    | •    | •     |      | •    |

| PIC16(L)F1578 | •    | •    |       | •    | •    |

| PIC16(L)F1579 | •    | •    |       | •    | •    |

Note: Pin details are subject to change.

| Name                                                  | Function | Input<br>Type | Output<br>Type | Description                             |

|-------------------------------------------------------|----------|---------------|----------------|-----------------------------------------|

| RA0/AN0/C1IN+/DAC1OUT/                                | RA0      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

| ICSPDAT                                               | AN0      | AN            | _              | ADC Channel input.                      |

|                                                       | C1IN+    | AN            | _              | Comparator positive input.              |

|                                                       | DAC1OUT  | _             | AN             | Digital-to-Analog Converter output.     |

|                                                       | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                         |

| RA1/AN1/VREF+/C1IN0-/C2IN0-/                          | RA1      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

| ICSPCLK                                               | AN1      | AN            | _              | ADC Channel input.                      |

|                                                       | VREF+    | AN            | _              | Voltage Reference input.                |

|                                                       | C1IN0-   | AN            | _              | Comparator negative input.              |

|                                                       | C2IN0-   | AN            | —              | Comparator negative input.              |

|                                                       | ICSPCLK  | ST            | _              | ICSP Programming Clock.                 |

| RA2/AN2/T0CKI <sup>(1)</sup> /CWG1IN <sup>(1)</sup> / | RA2      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

| INT <sup>(1)</sup>                                    | AN2      | AN            | _              | ADC Channel input.                      |

|                                                       | TOCKI    | TTL/ST        | _              | Timer0 clock input.                     |

|                                                       | CWG1IN   | TTL/ST        | _              | CWG complementary input.                |

|                                                       | INT      | TTL/ST        | _              | External interrupt.                     |

| RA3/VPP/MCLR                                          | RA3      | TTL/ST        | _              | General purpose input with IOC and WPU. |

|                                                       | VPP      | HV            | —              | Programming voltage.                    |

|                                                       | MCLR     | ST            | _              | Master Clear with internal pull-up.     |

| RA4/AN3/T1G <sup>(1)</sup> /CLKOUT                    | RA4      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

|                                                       | AN3      | AN            | _              | ADC Channel input.                      |

|                                                       | T1G      | TTL/ST        | _              | Timer1 Gate input.                      |

|                                                       | CLKOUT   | —             | CMOS           | Fosc/4 output.                          |

| RA5/CLKIN/T1CKI <sup>(1)</sup>                        | RA5      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

|                                                       | CLKIN    | CMOS          | _              | External clock input (EC mode).         |

|                                                       | T1CKI    | TTL/ST        | _              | Timer1 clock input.                     |

| RB4/AN10                                              | RB4      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

|                                                       | AN10     | AN            | _              | ADC Channel input.                      |

| RB5/AN11/RX <sup>(1)</sup>                            | RB5      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

|                                                       | AN11     | AN            | _              | ADC Channel input.                      |

|                                                       | RX       | ST            | _              | USART asynchronous input.               |

| RB6                                                   | RB6      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

| RB7/CK                                                | RB7      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

| -                                                     | СК       | ST            | CMOS           | USART synchronous clock.                |

| RC0/AN4/C2IN+                                         | RC0      | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU. |

|                                                       | AN4      | AN            | _              | ADC Channel input.                      |

|                                                       | C2IN+    | AN            | <u> </u>       | Comparator positive input.              |

TABLE 1-3: PIC16(L)F1578/9 PINOUT DESCRIPTION

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C levels

HV = High Voltage

XTAL = Crystal

Levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-1.

3: These USART functions are bidirectional. The output pin selections must be the same as the input pin selections.

## 3.2.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.2.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | JDEX                |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

|                   |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

## 3.2.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH operator will set bit<7> if a label points to a location in program memory.

## EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constant | s             |                               |

|----------|---------------|-------------------------------|

| DW       | DATA0         | ;First constant               |

| DW       | DATA1         | ;Second constant              |

| DW       | DATA2         |                               |

| DW       | DATA3         |                               |

| my_funct | ion           |                               |

| ; LOT    | S OF CODE     |                               |

| MOVLW    | DATA_INDEX    |                               |

| ADDLW    | LOW constant  | s                             |

| MOVWF    | FSR1L         |                               |

| MOVLW    | HIGH constan  | nts;MSb is set                |

|          |               | automatically                 |

| MOVWF    | FSR1H         |                               |

| BTFSC    | STATUS, C     | <pre>;carry from ADDLW?</pre> |

| INCF     | FSR1H,f       | ;yes                          |

| MOVIW    | 0[FSR1]       |                               |

| ;THE PRO | GRAM MEMORY I | S IN W                        |

|          |               |                               |

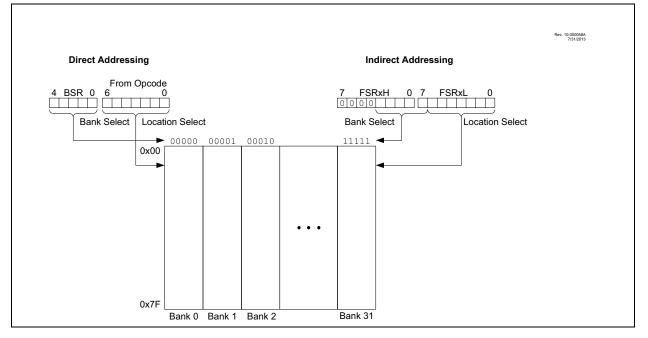

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

### FIGURE 3-10: TRADITIONAL DATA MEMORY MAP

| U-0              | R-0/q                                                     | R-q/q                                                                               | R-0/q            | R-0/q          | R-q/q            | R-0/q            | R-0/q        |  |  |

|------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|----------------|------------------|------------------|--------------|--|--|

| —                | PLLR                                                      | OSTS                                                                                | HFIOFR           | HFIOFL         | MFIOFR           | LFIOFR           | HFIOFS       |  |  |

| bit 7            |                                                           |                                                                                     |                  |                |                  |                  | bit C        |  |  |

|                  |                                                           |                                                                                     |                  |                |                  |                  |              |  |  |

| Legend:          |                                                           |                                                                                     |                  |                |                  |                  |              |  |  |

| R = Readable     | e bit                                                     | W = Writable                                                                        | bit              | U = Unimpler   | nented bit, reac | l as '0'         |              |  |  |

| u = Bit is unc   | hanged                                                    | x = Bit is unkr                                                                     | nown             | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is set | t                                                         | '0' = Bit is cle                                                                    | ared             | q = Condition  | al               |                  |              |  |  |

|                  |                                                           |                                                                                     |                  |                |                  |                  |              |  |  |

| bit 7            | •                                                         | ted: Read as '                                                                      | 0'               |                |                  |                  |              |  |  |

| bit 6            | PLLR 4x PLL                                               | •                                                                                   |                  |                |                  |                  |              |  |  |

|                  | 1 = 4x PLLi<br>0 = 4x PLLi                                |                                                                                     |                  |                |                  |                  |              |  |  |

| bit 5            |                                                           | ) = 4x PLL is not ready<br>DSTS: Oscillator Start-up Timer Status bit               |                  |                |                  |                  |              |  |  |

|                  |                                                           | 1 = Running from the clock defined by the FOSC<1:0> bits of the Configuration Words |                  |                |                  |                  |              |  |  |

|                  | 0 = Running from an internal oscillator (FOSC<1:0> = 0.0) |                                                                                     |                  |                |                  |                  |              |  |  |

| bit 4            | HFIOFR: Hig                                               | HFIOFR: High-Frequency Internal Oscillator Ready bit                                |                  |                |                  |                  |              |  |  |

|                  | 1 = HFINTOSC is ready                                     |                                                                                     |                  |                |                  |                  |              |  |  |

|                  | 0 = HFINTOSC is not ready                                 |                                                                                     |                  |                |                  |                  |              |  |  |

| bit 3            | •                                                         | HFIOFL: High-Frequency Internal Oscillator Locked bit                               |                  |                |                  |                  |              |  |  |

|                  | 1 = HFINTOSC is at least 2% accurate                      |                                                                                     |                  |                |                  |                  |              |  |  |

| bit 2            |                                                           | = HFINTOSC is not 2% accurate                                                       |                  |                |                  |                  |              |  |  |

|                  |                                                           | IFIOFR: Medium-Frequency Internal Oscillator Ready bit                              |                  |                |                  |                  |              |  |  |

|                  | 1 = MFINTOSC is ready<br>0 = MFINTOSC is not ready        |                                                                                     |                  |                |                  |                  |              |  |  |

| bit 1            | LFIOFR: Low                                               | LFIOFR: Low-Frequency Internal Oscillator Ready bit                                 |                  |                |                  |                  |              |  |  |

|                  | 1 = LFINTOS                                               | 1 = LFINTOSC is ready                                                               |                  |                |                  |                  |              |  |  |

|                  | 0 = LFINTOS                                               | SC is not ready                                                                     |                  |                |                  |                  |              |  |  |

| bit 0            | HFIOFS: Hig                                               | h-Frequency Ir                                                                      | ternal Oscillato | or Stable bit  |                  |                  |              |  |  |

|                  |                                                           | SC is at least 0                                                                    |                  |                |                  |                  |              |  |  |

|                  | 0 = HFINTO                                                | SC is not 0.5%                                                                      | accurate         |                |                  |                  |              |  |  |

## REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

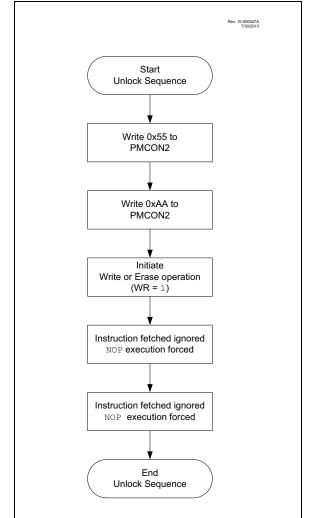

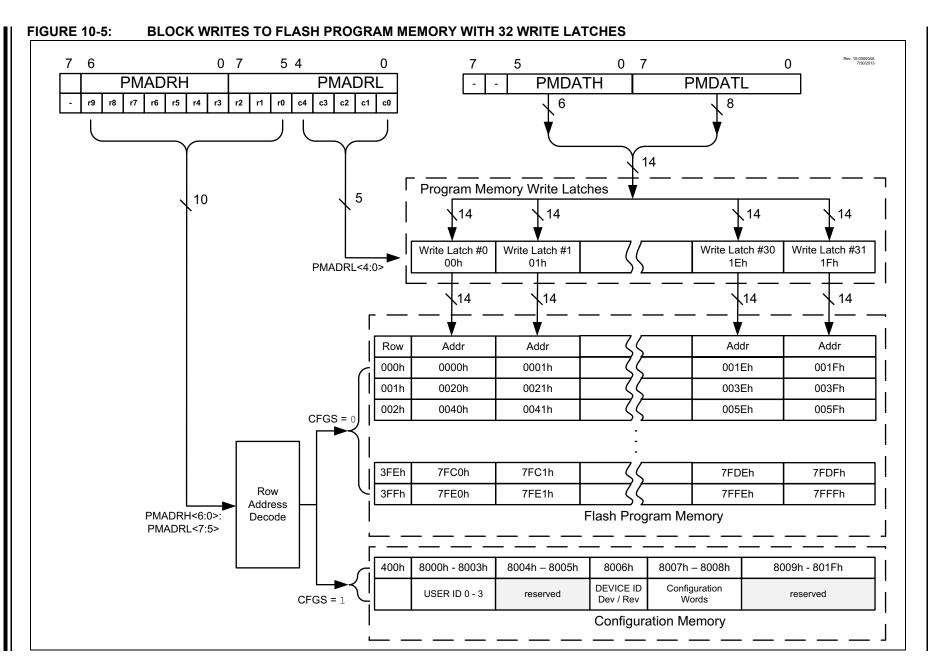

#### 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to user IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

## FIGURE 10-3: FLASH PROGRAM

### MEMORY UNLOCK SEQUENCE FLOWCHART

PIC16(L)F1574/5/8/9

## 13.0 INTERRUPT-ON-CHANGE

The PORTA, PORTB<sup>(1)</sup> AND PORTC pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- · Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

Note 1: PORTB available on PIC16(L)F1578/9 only.

## 13.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 13.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

## 13.3 Interrupt Flags

The IOCAFx, IOCBFx and IOCCFx bits located in the IOCAF, IOCBF and IOCCF registers, respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx, IOCBFx and IOCCFx bits.

## 13.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx, IOCBFx and IOCCFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

## 13.6 Register Definitions: Interrupt-on-Change Control

#### **REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER**

| U-0               | U-0                             | R/W-0/0            | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------------------|---------------------------------|--------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|

| _                 | _                               | IOCAP5             | IOCAP4                                                | IOCAP3                             | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7             |                                 |                    |                                                       | -                                  |         |         | bit 0   |

|                   |                                 |                    |                                                       |                                    |         |         |         |

| Legend:           |                                 |                    |                                                       |                                    |         |         |         |

| R = Readable bit  |                                 | W = Writable bi    | t                                                     | U = Unimplemented bit, read as '0' |         |         |         |

| u = Bit is unchan | is unchanged x = Bit is unknown |                    | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |

| '1' = Bit is set  |                                 | '0' = Bit is clear | ed                                                    |                                    |         |         |         |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

## 14.3 Register Definitions: FVR Control

| R/W-0/0              | R-q/q                                                                                                                                                                                                                                                                                                                                 | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0/0              | R/W-0/0                     | R/W-0/0                | R/W-0/0 | R/W-0/0              |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|------------------------|---------|----------------------|--|

| FVREN <sup>(1)</sup> | FVRRDY <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                 | TSEN <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                       | TSRNG <sup>(3)</sup> | CDAFV                       | ′R<1:0> <sup>(1)</sup> | ADFVR   | <1:0> <sup>(1)</sup> |  |

| bit 7                |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                             |                        |         | bit                  |  |

|                      |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                             |                        |         |                      |  |

| Legend:              |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                             |                        |         |                      |  |

| R = Readable         |                                                                                                                                                                                                                                                                                                                                       | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |                             | mented bit, read       |         |                      |  |

| u = Bit is unc       | 0                                                                                                                                                                                                                                                                                                                                     | x = Bit is unk                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |                             | at POR and BO          |         | other Resets         |  |

| '1' = Bit is set     | :                                                                                                                                                                                                                                                                                                                                     | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                                                                                                                          | ared                 | q = Value de                | pends on condit        | ion     |                      |  |

| bit 7                | 1 = Fixed Vo                                                                                                                                                                                                                                                                                                                          | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                                                                                                                                                                                                                                                                                                                                                                                        | e is enabled         | bit <sup>(1)</sup>          |                        |         |                      |  |

| bit 6                | 1 = Fixed Vo                                                                                                                                                                                                                                                                                                                          | ed Voltage Re<br>Itage Referenc<br>Itage Referenc                                                                                                                                                                                                                                                                                                                                                                                                         | e output is rea      |                             | enabled                |         |                      |  |

| bit 5                | 1 = Tempera                                                                                                                                                                                                                                                                                                                           | <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup><br>1 = Temperature Indicator is enabled<br>0 = Temperature Indicator is disabled                                                                                                                                                                                                                                                                                                             |                      |                             |                        |         |                      |  |

| bit 4                | 1 = VOUT = V                                                                                                                                                                                                                                                                                                                          | perature Indica<br>′DD - 4V⊤ (Higł<br>′DD - 2V⊤ (Low                                                                                                                                                                                                                                                                                                                                                                                                      | Range)               | election bit <sup>(3)</sup> |                        |         |                      |  |

| bit 3-2              | 11 = Compara<br>10 = Compara<br>01 = Compara                                                                                                                                                                                                                                                                                          | <ul> <li>0 = VOUT = VDD - 2VT (Low Range)</li> <li>CDAFVR&lt;1:0&gt;: Comparator FVR Buffer Gain Selection bits<sup>(1)</sup></li> <li>11 = Comparator FVR Buffer Gain is 4x, with output VCDAFVR = 4x VFVR<sup>(4)</sup></li> <li>10 = Comparator FVR Buffer Gain is 2x, with output VCDAFVR = 2x VFVR<sup>(4)</sup></li> <li>01 = Comparator FVR Buffer Gain is 1x, with output VCDAFVR = 1x VFVR</li> <li>00 = Comparator FVR Buffer is off</li> </ul> |                      |                             |                        |         |                      |  |

| bit 1-0              | <b>ADFVR&lt;1:0&gt;:</b> ADC FVR Buffer Gain Selection bit <sup>(1)</sup><br>11 = ADC FVR Buffer Gain is 4x, with output VADFVR = 4x VFVR <sup>(4)</sup><br>10 = ADC FVR Buffer Gain is 2x, with output VADFVR = 2x VFVR <sup>(4)</sup><br>01 = ADC FVR Buffer Gain is 1x, with output VADFVR = 1x VFVR<br>00 = ADC FVR Buffer is off |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                             |                        |         |                      |  |

| inę                  | To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by cle<br>ng the Buffer Gain Selection bits.                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                             |                        |         |                      |  |

## **REGISTER 14-1:** FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

- 2: FVRRDY is always '1' for the PIC16F1574/5/8/9 devices.

- 3: See Section 15.0 "Temperature Indicator Module" for additional information.

- 4: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR>1:0> |       | ADFVF | R<1:0> | 149                 |

**Legend:** Shaded cells are unused by the Fixed Voltage Reference module.

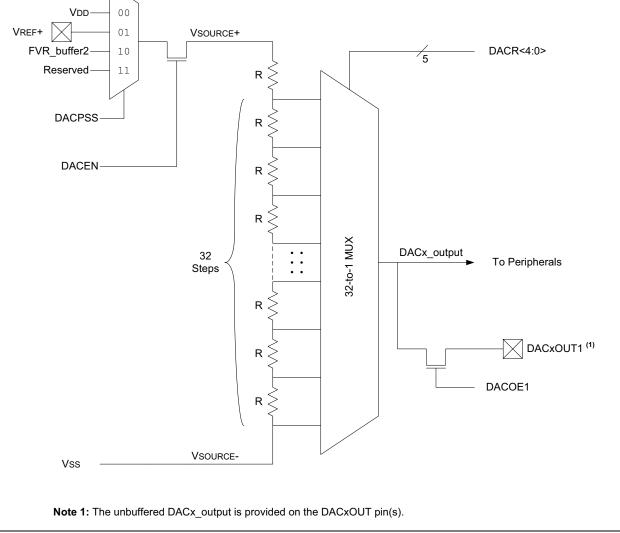

#### 17.0 **5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE**

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The positive input source (VSOURCE+) of the DAC can be connected to:

- · External VREF+ pin

- · VDD supply voltage

- FVR\_buffer1

**FIGURE 17-1:**

The negative input source (VSOURCE-) of the DAC can be connected to:

Vss

The output of the DAC (DACx\_output) can be selected as a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- DACxOUT1 pin

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACxCON0 register.

Rev. 10-000026B 9/6/2013

#### VDD 00 VREF+ 01 VSOURCE+

DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

## 20.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 20.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 20.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 20.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 20.5 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

## 20.5.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register. When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 20-3 for timing details.

## TABLE 20-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| 1          | 0      | 0   | Counts           |

| 1          | 0      | 1   | Holds Count      |

| 1          | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 20.5.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 20-4. Source selection is controlled by the T1GSS<1:0> bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

#### TABLE 20-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 00    | Timer1 Gate pin (T1G)                                                 |

| 01    | Overflow of Timer0 (T0_overflow)<br>(TMR0 increments from FFh to 00h) |

| 10    | Comparator 1 Output (C1OUT_sync) <sup>(1)</sup>                       |

| 11    | Comparator 2 Output (C2OUT_sync) <sup>(1)</sup>                       |

Note 1: Optionally synchronized comparator output.

## 21.5 Register Definitions: Timer2 Control

|                          | R/W-0/0            | R/W-0/0                                                                          | R/W-0/0         | R/W-0/0        | R/W-0/0           | R/W-0/0        | R/W-0/0      |  |  |  |  |

|--------------------------|--------------------|----------------------------------------------------------------------------------|-----------------|----------------|-------------------|----------------|--------------|--|--|--|--|

| _                        |                    | T2OUTI                                                                           | PS<3:0>         |                | TMR2ON            | T2CKF          | PS<1:0>      |  |  |  |  |

| bit 7                    |                    |                                                                                  |                 |                |                   | I              | bit          |  |  |  |  |

|                          |                    |                                                                                  |                 |                |                   |                |              |  |  |  |  |

| Legend:                  |                    |                                                                                  |                 |                |                   |                |              |  |  |  |  |

| R = Readable bit W = Wri |                    |                                                                                  | bit             | U = Unimple    | emented bit, read | 1 as '0'       |              |  |  |  |  |

| u = Bit is und           | changed            | x = Bit is unkr                                                                  | nown            | -n/n = Value   | at POR and BO     | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is se          | et                 | '0' = Bit is cle                                                                 | ared            |                |                   |                |              |  |  |  |  |

| L:1 7                    |                    | unte de De e d'ans (                                                             | 0'              |                |                   |                |              |  |  |  |  |

| bit 7                    | -                  | Unimplemented: Read as '0'<br>T2OUTPS<3:0>: Timer2 Output Postscaler Select bits |                 |                |                   |                |              |  |  |  |  |

| bit 6-3                  | 0000 = 1:1         |                                                                                  | ilput Posiscale | er Select bits |                   |                |              |  |  |  |  |

|                          | 0000 = 1.1         |                                                                                  |                 |                |                   |                |              |  |  |  |  |

|                          | 0010 = 1:3         |                                                                                  |                 |                |                   |                |              |  |  |  |  |

|                          | 0011 = 1:4         |                                                                                  |                 |                |                   |                |              |  |  |  |  |

|                          | 0100 <b>= 1</b> :5 | Postscaler                                                                       |                 |                |                   |                |              |  |  |  |  |

|                          | 0101 = 1:6         | Postscaler                                                                       |                 |                |                   |                |              |  |  |  |  |

|                          | 0110 <b>= 1</b> :7 |                                                                                  |                 |                |                   |                |              |  |  |  |  |

|                          | 0111 = 1:8         |                                                                                  |                 |                |                   |                |              |  |  |  |  |

|                          | 1000 = 1:9         |                                                                                  |                 |                |                   |                |              |  |  |  |  |

|                          |                    | ) Postscaler                                                                     |                 |                |                   |                |              |  |  |  |  |

|                          |                    | 1010 = 1:11 Postscaler<br>1011 = 1:12 Postscaler                                 |                 |                |                   |                |              |  |  |  |  |

|                          |                    | 3 Postscaler                                                                     |                 |                |                   |                |              |  |  |  |  |

|                          |                    | 4 Postscaler                                                                     |                 |                |                   |                |              |  |  |  |  |

|                          |                    | 5 Postscaler                                                                     |                 |                |                   |                |              |  |  |  |  |

|                          | 1111 <b>= 1:16</b> | 6 Postscaler                                                                     |                 |                |                   |                |              |  |  |  |  |

| bit 2                    | TMR2ON: 1          | Fimer2 On bit                                                                    |                 |                |                   |                |              |  |  |  |  |

|                          | 1 = Timer2         | is on                                                                            |                 |                |                   |                |              |  |  |  |  |

|                          | 0 = Timer2         | is off                                                                           |                 |                |                   |                |              |  |  |  |  |

| bit 1-0                  | T2CKPS<1           | :0>: Timer2 Cloc                                                                 | k Prescale Se   | lect bits      |                   |                |              |  |  |  |  |

|                          | 00 = Presca        | aler is 1                                                                        |                 |                |                   |                |              |  |  |  |  |

|                          | 01 = Presca        | aler is 4                                                                        |                 |                |                   |                |              |  |  |  |  |

|                          | 10 = Presca        | aler is 16                                                                       |                 |                |                   |                |              |  |  |  |  |

|                          | 11 = Presca        | aler is 64                                                                       |                 |                |                   |                |              |  |  |  |  |

|                          |                    |                                                                                  |                 |                |                   |                |              |  |  |  |  |

| <b>FABLE 21-</b> 1       | I: SUIVIIVIA       | RY OF REGIS                                                                      | 1 EKS ASSU      |                | H HIMERZ          |                |              |  |  |  |  |

## REGISTER 21-1: T2CON: TIMER2 CONTROL REGISTER

| Name   | Bit 7                             | Bit 6           | Bit 5        | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-----------------------------------|-----------------|--------------|-------|-------|--------|--------|--------|---------------------|

| INTCON | GIE                               | PEIE            | TMR0IE       | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1   | TMR1GIE                           | ADIE            | RCIE         | TXIE  | —     | _      | TMR2IE | TMR1IE | 87                  |

| PIR1   | TMR1GIF                           | ADIF            | RCIF         | TXIF  | —     | —      | TMR2IF | TMR1IF | 90                  |

| PR2    | R2 Timer2 Module Period Register  |                 |              |       |       |        |        |        | 189*                |

| T2CON  | - T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |                 |              |       |       |        |        |        | 191                 |

| TMR2   | Holding Reg                       | ister for the 8 | -bit TMR2 Co | unt   |       |        |        |        | 189*                |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

Note 1: PIC16(L)F1575 only.

#### 22.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 22-3 contains the formulas for determining the baud rate. Example 22-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 22-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

#### EXAMPLE 22-1: CALCULATING BAUD **RATE ERROR**

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Fosc Desired Baud Rate =  $\frac{1}{64([SPBRGH:SPBRGL] + 1)}$ Solving for SPBRGH:SPBRGL: FOSC  $X = \frac{Desired Baud Rate}{-1}$ 64 16000000 = [25.042] = 25 Calculated Baud Rate =  $\frac{10000000}{64(25+1)}$ 16000000 = 9615  $Error = \frac{Calc. Baud Rate - Desired}{Baud Rate}$ Desired Baud Rate  $= \frac{(9615 - 9600)}{2000} = 0.16\%$

9600

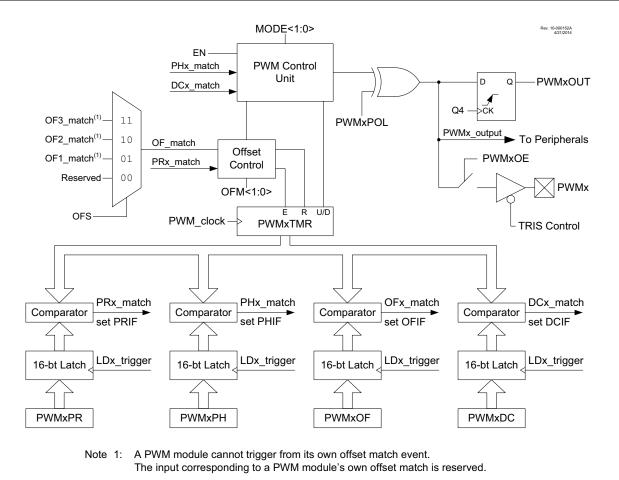

## 23.0 16-BIT PULSE-WIDTH MODULATION (PWM) MODULE

The Pulse-Width Modulation (PWM) module generates a pulse width modulated signal determined by the phase, duty cycle, period, and offset event counts that are contained in the following registers:

- PWMxPH register

- PWMxDC register

- PWMxPR register

- PWMxOF register

Figure 23-1 shows a simplified block diagram of the PWM operation.

Each PWM module has four modes of operation:

- Standard

- · Set On Match

- Toggle On Match

- · Center-Aligned

For a more detailed description of each PWM mode, refer to **Section 23.2** "**PWM Modes**".

Each PWM module has four offset modes:

- Independent Run

- · Slave Run with Synchronous Start

- · One-Shot Slave with Synchronous Start

- Continuous Run Slave with Synchronous Start and Timer Reset

Using the offset modes, each PWM module can offset its waveform relative to any other PWM module in the same device. For a more detailed description of the offset modes refer to **Section 23.3 "Offset Modes"**.

Every PWM module has a configurable reload operation to ensure all event count buffers change at the end of a period thereby avoiding signal glitches. Figure 23-2 shows a simplified block diagram of the reload operation. For a more detailed description of the reload operation, refer to Section **Section 23.4 "Reload Operation"**.

## FIGURE 23-1: 16-BIT PWM BLOCK DIAGRAM

## 27.2 Standard Operating Conditions

The standard operating conditions for any device are defined as:  $V \text{DDMIN} \leq V \text{DD} \leq V \text{DDMAX}$ Operating Voltage: Operating Temperature: TA MIN  $\leq$  TA  $\leq$  TA MAX VDD — Operating Supply Voltage<sup>(1)</sup> PIC16LF1574/5/8/9 PIC16F1574/5/8/9 TA — Operating Ambient Temperature Range Industrial Temperature TA MIN.....--40°C **Extended Temperature** Ta MIN.....--40°C

Note 1: See Parameter D001, DS Characteristics: Supply Voltage.

### TABLE 27-14: ADC CONVERSION REQUIREMENTS

| Param.<br>No. | Sym. | Characteristic                                                     | Min. | Тур†                      | Max. | Units | Conditions                                   |

|---------------|------|--------------------------------------------------------------------|------|---------------------------|------|-------|----------------------------------------------|

| AD130*        | Tad  | ADC Clock Period (TADC)                                            | 1.0  | _                         | 6.0  | μS    | Fosc-based                                   |

|               |      | ADC Internal FRC Oscillator Period (TFRC)                          | 1.0  | 2.0                       | 6.0  | μS    | ADCS<2:0> = x11 (ADC FRC mode)               |

| AD131         | TCNV | Conversion Time<br>(not including Acquisition Time) <sup>(1)</sup> | —    | 11                        | —    | TAD   | Set GO/DONE bit to conversion complete       |

| AD132*        | TACQ | Acquisition Time                                                   | _    | 5.0                       | _    | μS    |                                              |

| AD133*        | Тнср | Holding Capacitor Disconnect Time                                  | _    | 1/2 TAD<br>1/2 TAD + 1TCY | _    |       | Fosc-based<br>ADCS<2:0> = x11 (ADC FRC mode) |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not † tested.

Note 1: The ADRES register may be read on the following TCY cycle.

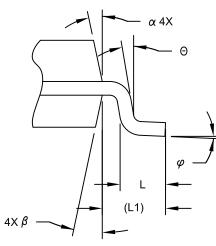

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | Units | N        | MILLIMETERS |      |  |  |  |

|--------------------------|-------|----------|-------------|------|--|--|--|

| Dimension Lir            | nits  | MIN      | NOM         | MAX  |  |  |  |

| Number of Pins           | N     |          | 14          |      |  |  |  |

| Pitch                    | е     |          | 1.27 BSC    |      |  |  |  |

| Overall Height           | A     | -        | -           | 1.75 |  |  |  |

| Molded Package Thickness | A2    | 1.25     | -           | -    |  |  |  |

| Standoff §               | A1    | 0.10     | -           | 0.25 |  |  |  |

| Overall Width            | E     | 6.00 BSC |             |      |  |  |  |

| Molded Package Width     | E1    | 3.90 BSC |             |      |  |  |  |

| Overall Length           | D     | 8.65 BSC |             |      |  |  |  |

| Chamfer (Optional)       | h     | 0.25     | -           | 0.50 |  |  |  |

| Foot Length              | L     | 0.40     | -           | 1.27 |  |  |  |

| Footprint                | L1    | 1.04 REF |             |      |  |  |  |

| Lead Angle               | Θ     | 0°       | -           | -    |  |  |  |

| Foot Angle               | φ     | 0°       | -           | 8°   |  |  |  |

| Lead Thickness           | c     | 0.10     | -           | 0.25 |  |  |  |

| Lead Width               | b     | 0.31     | -           | 0.51 |  |  |  |

| Mold Draft Angle Top     | α     | 5°       | -           | 15°  |  |  |  |

| Mold Draft Angle Bottom  | β     | 5°       | -           | 15°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

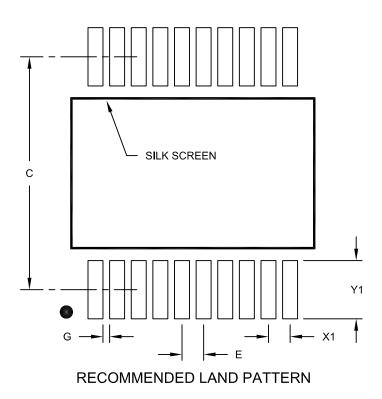

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N   | MILLIMETERS |      |      |  |  |

|--------------------------|-----|-------------|------|------|--|--|

| Dimension                | MIN | NOM         | MAX  |      |  |  |

| Contact Pitch            | E   | 0.65 BSC    |      |      |  |  |

| Contact Pad Spacing      | С   |             | 7.20 |      |  |  |

| Contact Pad Width (X20)  | X1  |             |      | 0.45 |  |  |

| Contact Pad Length (X20) | Y1  |             |      | 1.75 |  |  |

| Distance Between Pads    | G   | 0.20        |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A