Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Betano                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1575-e-st |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIN ALLOCATION TABLES

| 0/1                | 14-Pin PDIP/SOIC/TSSOP | 16-Pin UQFN | ADC                   | Reference | Comparator    | Timers               | MWG     | EUSART              | CWG                   | Interrupt               | Pull-up | Basic    |

|--------------------|------------------------|-------------|-----------------------|-----------|---------------|----------------------|---------|---------------------|-----------------------|-------------------------|---------|----------|

| RA0                | 13                     | 12          | AN0                   | DAC10UT1  | C1IN+         | _                    | —       | -                   | —                     | IOC                     | Y       | ICSPDAT  |

| RA1                | 12                     | 11          | AN1                   | VREF+     | C1IN0-/C2IN0- | _                    | _       | _                   | —                     | IOC                     | Y       | ICSPCLK  |

| RA2                | 11                     | 10          | AN2                   | —         | _             | T0CKI <sup>(1)</sup> | —       | -                   | CWG1IN <sup>(1)</sup> | INT <sup>(1)</sup> /IOC | Υ       | —        |

| RA3                | 4                      | 3           | -                     | _         | -             |                      | _       |                     | —                     | IOC                     | Υ       | MCLR/VPP |

| RA4                | 3                      | 2           | AN3                   | -         | _             | T1G <sup>(1)</sup>   | _       | _                   | _                     | IOC                     | Υ       | CLKOUT   |

| RA5                | 2                      | 1           | _                     | _         | _             | T1CKI <sup>(1)</sup> | —       |                     | —                     | IOC                     | Υ       | CLKIN    |

| RC0                | 10                     | 9           | AN4                   | —         | C2IN+         | -                    | —       | -                   | —                     | IOC                     | Y       | —        |

| RC1                | 9                      | 8           | AN5                   | —         | C1IN1-/C2IN1- | -                    | —       |                     | —                     | IOC                     | Υ       | —        |

| RC2                | 8                      | 7           | AN6                   | —         | C1IN2-/C2IN2- | -                    | —       | -                   | —                     | IOC                     | Υ       | —        |

| RC3                | 7                      | 6           | AN7                   | —         | C1IN3-/C2IN3- |                      | —       | I                   | —                     | IOC                     | Υ       | —        |

| RC4                | 6                      | 5           | ADCACT <sup>(1)</sup> | _         | -             | _                    | _       | CK <sup>(1)</sup>   | _                     | IOC                     | Υ       | _        |

| RC5                | 5                      | 4           | _                     | _         | _             | _                    | _       | RX <sup>(1,3)</sup> | _                     | IOC                     | Υ       | _        |

| Vdd                | 1                      | 16          | _                     | _         | -             | _                    | _       | _                   | _                     | _                       | -       | Vdd      |

| Vss                | 14                     | 13          | _                     | _         | _             | _                    | _       | _                   | _                     | _                       | -       | Vss      |

|                    | —                      | —           | _                     | _         | C1OUT         | -                    | PWM10UT | DT <sup>(3)</sup>   | CWG1A                 | —                       | —       | _        |

| OUT <sup>(2)</sup> | —                      | —           | _                     | —         | C2OUT         |                      | PWM2OUT | СК                  | CWG1B                 | —                       | —       | —        |

| 001.7              | —                      | _           | _                     | —         | _             |                      | PWM3OUT | ΤX                  | —                     | —                       | —       | _        |

|                    | —                      | —           | _                     | _         |               | _                    | PWM4OUT | _                   | _                     | _                       | —       | —        |

#### TABLE 3: 14/16-PIN ALLOCATION TABLE (PIC16(L)F1574/5)

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS Input Selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS Output Selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

# TABLE OF CONTENTS

| 9.0       Watchdog Timer (WDT)       97         10.0       Flash Program Memory Control       101         11.0       I/O Ports       117         11.0       Peripheral Pin Select (PPS) Module       135         11.1       Interrupt-On-Change       141         14.0       Fixed Voltage Reference (FVR)       147         15.0       Interrupt-On-Change       141         14.0       Fixed Voltage Reference (FVR)       147         15.0       Temperature Indicator Module       152         16.0       Analog-to-Digital Converter (DAC) Module       152         17.0       Timer0 Module       166         18.0       Comparator Module       169         19.0       Timer1 Module with Gate Control.       176         10.1       Timer2 Module       189         21.0       Timer1 Module with Gate Control.       179         11.0       Timer2 Module       220         22.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)       192         23.0       16-bit Pulse-Width Modulation (PWM) Module       220         24.0       Complementary Waveform Generator (CWG) Module       220         25.0       In-Circuit Serial Programming™ (ICSP™)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.0   | Device Overview                                                           | 10    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------|-------|

| 4.0       Device Configuration       55         5.0       Oscillator Module       61         0.       Resets       73         7.0       Interrupts       81         8.0       Power-Down Mode (Sleep)       94         9.0       Watchdog Timer (WDT)       97         10.0       Flash Program Memory Control       101         11.0       I/O Ports       101         11.0       I/O Ports       117         12.0       Peripheral Pin Select (PPS) Module       135         13.0       Interrupt-On-Change       141         14.1       Fixed Voltage Reference (FVR)       141         15.0       Temperature Indicator Module       150         16.0       Analog-to-Digital Converter (ADC) Module       152         17.0       5-Bit Digital-to-Analog Converter (DAC) Module       169         19.0       Timer 0 Module       169         19.0       Timer 1 Module with Gate Control       176         10.1       Timer 2 Module       189         20.1       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)       192         21.0       Timer 2 Module       260         21.0       In-circuit Serial Programming ™ (ICSP ™) </td <td>2.0</td> <td>Enhanced Mid-Range CPU</td> <td> 17</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.0   | Enhanced Mid-Range CPU                                                    | 17    |

| 5.0       Oscillator Module       61         6.0       Resets       73         7       Interrupts       81         8.0       Power-Down Mode (Sleep)       94         9.0       Watchdog Timer (WDT)       97         10.0       Flash Program Memory Control       101         110       I/O Ports       117         12.0       Peripheral Pin Select (PPS) Module       135         13.0       Interrupt-On-Change       141         14.0       Fixed Voltage Reference (FVR)       141         15.0       Temperature Indicator Module       150         16.0       Analog-to-Digital Converter (ADC) Module       150         17.0       5-Bit Digital-to-Analog Converter (DAC) Module       166         18.0       Comparator Module       169         19.0       Timer1 Module with Gate Control.       179         21.0       Timer2 Module       189         22.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)       192         23.0       16-bit Pulse-Width Modulation (PWM) Module       220         24.0       Complementary Waveform Generator (CWG) Module       246         25.0       Instruction Set Summary       258                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.0   | Memory Organization                                                       | 19    |

| 6.0Resets737.0Interrupts818.0Power-Down Mode (Sleep)949.0Watchdog Timer (WDT)9710.0Flash Program Memory Control10111.0I/O Ports11712.0Peripheral Pin Select (PPS) Module13513.0Interrupt-On-Change14114.1Fixed Voltage Reference (FVR)14715.0Temperature Indicator Module15016.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer Of Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PVM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instructions Set Summary26027.0Electrical Specifications27428.0D cand AC Characteristics Graphs and Charts39829.0Development Support312310.Packaging Information318The Microchip Website339339Customer Support339312339339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.0   | Device Configuration                                                      | 55    |

| 7.0       Interrupts       81         8.0       Power-Down Mode (Sleep)       94         9.0       Watchdog Timer (WDT)       97         10.0       Flash Program Memory Control       101         11.0       I/O Ports       117         12.0       Peripheral Pin Select (PPS) Module       135         13.0       Interrupt-On-Change       141         14.0       Fixed Voltage Reference (FVR)       147         15.0       Temperature Indicator Module       152         16.0       Analog-to-Digital Converter (ADC) Module       152         17.0       5-Bit Digital-to-Analog Converter (DAC) Module       166         18.0       Comparator Module       169         19.0       Timer0 Module       176         0.0       Timer1 Module with Gate Control.       179         10.0       Timer2 Module       189         22.0       Enhanced Universal Synchronous Receiver Transmitter (EUSART)       192         23.0       16-bit Pulse-Widt Modulation (PWM) Module       220         24.0       Complementary Waveform Generator (CWG) Module       246         25.0       In-Circuit Serial Programming™ (ICSP™)       258         26.0       Instruction Set Summary       258                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.0   | Oscillator Module                                                         | 61    |

| 8.0       Power-Down Mode (Sleep)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6.0   | Resets                                                                    | 73    |

| 9.0       Watchdog Timer (WDT)       97         10.0       Flash Program Memory Control       101         11.0       I/O Ports       117         11.0       Peripheral Pin Select (PPS) Module       135         13.0       Interrupt-On-Change       141         14.0       Fixed Voltage Reference (FVR)       147         15.0       Temperature Indicator Module       150         16.0       Analog-to-Digital Converter (ADC) Module       152         17.0       5-Bit Digital-to-Analog Converter (DAC) Module       166         18.0       Comparator Module       169         19.0       Timer0 Module       179         10.0       Timer1 Module with Gate Control.       179         10.1       Timer2 Module       189         21.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)       192         19.1       Timer2 Module       220         22.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)       192         23.0       16-bit Pulse-Width Modulation (PWM) Module       220         24.0       Complementary Waveform Generator (CWG) Module       226         25.0       In-Circuit Serial Programming ™ (ICSP™)       258         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7.0   | Interrupts                                                                | 81    |

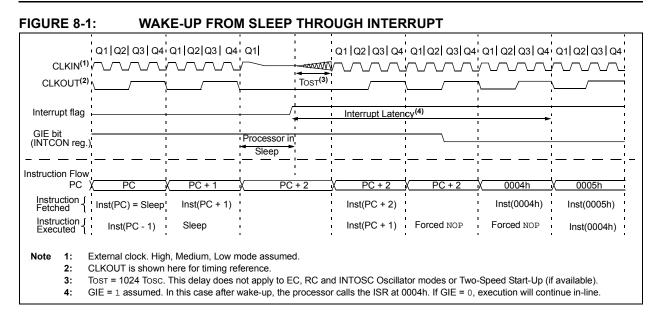

| 10.0       Flash Program Memory Control       101         11.0       I/O Ports       117         11.0       Peripheral Pin Select (PPS) Module       135         11.1       Temperature In Select (PPS) Module       135         11.1       Fixed Voltage Reference (FVR)       141         14.0       Fixed Voltage Reference (FVR)       147         15.0       Temperature Indicator Module       150         16.0       Analog-to-Digital Converter (ADC) Module       152         17.0       5-Bit Digital-to-Analog Converter (DAC) Module       166         18.0       Comparator Module       169         19.0       Timer0 Module       176         20.0       Timer1 Module with Gate Control       176         21.0       Timer2 Module       189         22.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)       192         23.0       16-bit Pulse-Width Modulation (PWM) Module       220         24.0       Complementary Waveform Generator (CWG) Module       220         25.0       In-Circuit Serial Programming ™ (ICSP™)       258         26.0       Instruction Set Summary       258         26.0       Instruction Set Summary       260         27.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8.0   | Power-Down Mode (Sleep)                                                   | 94    |

| 11.0       I/O Ports       117         12.0       Peripheral Pin Select (PPS) Module       135         13.0       Interrupt-On-Change       141         14.0       Fixed Voltage Reference (FVR)       147         14.0       Fixed Voltage Reference (FVR)       147         15.0       Temperature Indicator Module       150         16.0       Analog-to-Digital Converter (ADC) Module       152         17.0       5-Bit Digital-to-Analog Converter (DAC) Module       166         18.0       Comparator Module       166         18.0       Comparator Module       166         19.0       Timer0 Module       176         20.1       Timer1 Module with Gate Control       179         21.0       Timer2 Module       189         22.0       Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)       192         23.0       16-bit Pulse-Width Modulation (PWM) Module       220         24.0       Complementary Waveform Generator (CWG) Module       246         25.0       In-Circuit Serial Programming™ (ICSP™)       258         26.0       Instruction Set Summary       260         27.0       Electrical Specifications       374         28.0       DC and AC Charact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9.0   | Watchdog Timer (WDT)                                                      | 97    |

| 12.0       Peripheral Pin Select (PPS) Module       135         13.0       Interrupt-On-Change       141         14.0       Fixed Voltage Reference (FVR)       147         15.0       Temperature Indicator Module       150         16.0       Analog-to-Digital Converter (ADC) Module       152         17.0       5-Bit Digital-to-Analog Converter (DAC) Module       166         18.0       Comparator Module       169         19.0       Timer0 Module       176         20.0       Timer1 Module with Gate Control       179         21.0       Timer2 Module       189         22.0       In-bit Pulse-Width Modulation (PWM) Module       220         23.0       16-bit Pulse-Width Modulation (PWM) Module       220         24.0       Complementary Waveform Generator (CWG) Module       246         25.0       In-Circuit Serial Programming™ (ICSP™)       258         26.0       Instruction Set Summary       260         27.0       Electrical Specifications       274         26.0       Characteristics Graphs and Charts       398         29.0       Development Support       312         30.0       Packaging Information       316         312       On Packaging Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10.0  | Flash Program Memory Control                                              | . 101 |

| 13.0Interrupt-On-Change14114.0Fixed Voltage Reference (FVR)14714.0Fixed Voltage Reference (FVR)14715.0Temperature Indicator Module15016.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27420.0Characteristics Graphs and Charts39829.0Development Support316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Change Notification Service339Customer Support339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11.0  |                                                                           |       |

| 14.0Fixed Voltage Reference (FVR)14715.0Temperature Indicator Module15016.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module16920.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support.316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12.0  | Peripheral Pin Select (PPS) Module                                        | . 135 |

| 15.0Temperature Indicator Module15016.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module17920.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13.0  | Interrupt-On-Change                                                       | . 141 |

| 16.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Packaging Information316Appendix A: Data Sheet Revision History338Customer Change Notification Service339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14.0  | Fixed Voltage Reference (FVR)                                             | . 147 |

| 17.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26827.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support.31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15.0  | Temperature Indicator Module                                              | . 150 |

| 18.0Comparator Module16919.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support.311230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16.0  | Analog-to-Digital Converter (ADC) Module                                  | . 152 |

| 19.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History339Customer Change Notification Service339Customer Support339Customer Support339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17.0  | 5-Bit Digital-to-Analog Converter (DAC) Module                            | . 166 |

| 20.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18.0  | Comparator Module                                                         | . 169 |

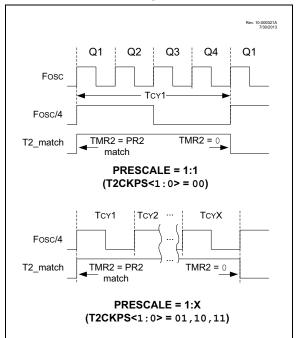

| 21.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19.0  | Timer0 Module                                                             | . 176 |

| 22.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20.0  | Timer1 Module with Gate Control                                           | . 179 |

| 23.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                           |       |

| 24.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | . 192 |

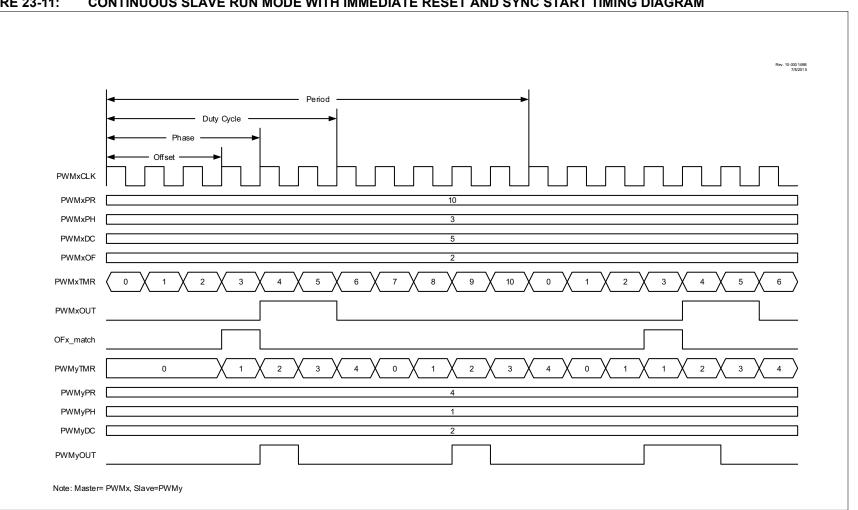

| 25.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23.0  | 16-bit Pulse-Width Modulation (PWM) Module                                | . 220 |

| 26.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24.0  | Complementary Waveform Generator (CWG) Module                             | . 246 |

| 27.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25.0  | In-Circuit Serial Programming™ (ICSP™)                                    | . 258 |

| 28.0       DC and AC Characteristics Graphs and Charts       398         29.0       Development Support       312         30.0       Packaging Information       316         Appendix A: Data Sheet Revision History       338         The Microchip Website       339         Customer Change Notification Service       339         Customer Support       339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26.0  | Instruction Set Summary                                                   | . 260 |

| 29.0       Development Support       312         30.0       Packaging Information       316         Appendix A: Data Sheet Revision History       338         The Microchip Website       339         Customer Change Notification Service       339         Customer Support       339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27.0  | Electrical Specifications                                                 | . 274 |

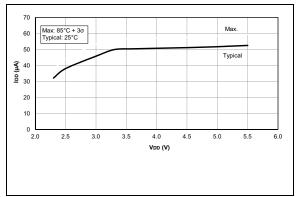

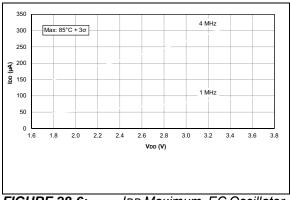

| 30.0       Packaging Information       316         Appendix A: Data Sheet Revision History       338         The Microchip Website       339         Customer Change Notification Service       339         Customer Support       339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28.0  |                                                                           |       |

| Appendix A: Data Sheet Revision History       338         The Microchip Website       339         Customer Change Notification Service       339         Customer Support       339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29.0  | Development Support                                                       | . 312 |

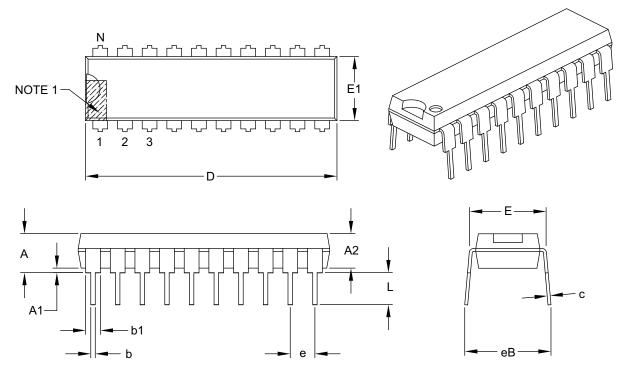

| The Microchip Website                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30.0  | Packaging Information                                                     | . 316 |

| Customer Change Notification Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                           |       |

| Customer Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                                           |       |