Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1575-i-st |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 3-7:PIC16(L)F1574/8 MEMORY MAP, BANKS 8-15

|              | BANK 8                       |      | BANK 9                       |      | BANK 10                      |      | BANK 11                      |      | BANK 12                      |      | BANK 13                      |      | BANK 14                      |      | BANK 15                      |

|--------------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|

| 400h         | Core Registers               | 480h | Core Registers               | 500h | Core Registers               | 580h | Core Registers               | 600h | Core Registers               | 680h | Core Registers               | 700h | Core Registers               | 780h | Core Registers               |

| 40Bh         | (Table 3-2)                  | 48Bh | (Table 3-2)                  | 50Bh | (Table 3-2)                  | 58Bh | (Table 3-2)                  | 60Bh | (Table 3-2)                  | 68Bh | (Table 3-2)                  | 70Bh | (Table 3-2)                  | 78Bh | (Table 3-2)                  |

| 40Bh<br>40Ch |                              | 48Ch |                              | 50Bh |                              | 58Ch |                              | 60Ch | _                            | 68Ch | _                            | 70Bh |                              | 78Ch | _                            |

| 40Ch<br>40Dh |                              | 48Ch |                              | 50Ch |                              | 58Dh |                              | 60Ch |                              | 68Dh |                              | 70Ch |                              | 78Dh |                              |

| 40Dh<br>40Eh | _                            | 48Eh |                              | 50Eh |                              | 58Eh |                              | 60Eh |                              | 68Eh | _                            | 70Dh |                              | 78Eh | _                            |

| 40Eh         | _                            | 48Fh | _                            | 50En | _                            | 58Fh | _                            | 60Eh |                              | 68Fh | _                            | 70En |                              | 78Fh | _                            |

| 401 h        | _                            | 490h | _                            | 510h | _                            | 590h | _                            | 610h |                              | 690h | _                            | 710h |                              | 790h | _                            |

| 411h         | _                            | 491h | _                            | 511h | _                            | 591h | _                            | 611h |                              | 691h | CWG1DBR                      | 711h |                              | 791h | _                            |

| 412h         | _                            | 492h | _                            | 512h | _                            | 592h | _                            | 612h |                              | 692h | CWG1DBF                      | 712h | _                            | 792h |                              |

| 413h         | _                            | 493h | _                            | 513h | _                            | 593h | _                            | 613h | _                            | 693h | CWG1CON0                     | 713h | _                            | 793h | _                            |

| 414h         | _                            | 494h | _                            | 514h | _                            | 594h | _                            | 614h | _                            | 694h | CWG1CON1                     | 714h | _                            | 794h |                              |

| 415h         | _                            | 495h | _                            | 515h | _                            | 595h | _                            | 615h | _                            | 695h | CWG1CON2                     | 715h | _                            | 795h | _                            |

| 416h         | _                            | 496h | _                            | 516h | _                            | 596h | _                            | 616h | _                            | 696h | _                            | 716h | _                            | 796h |                              |

| 417h         | _                            | 497h | —                            | 517h | —                            | 597h | —                            | 617h | _                            | 697h | _                            | 717h | —                            | 797h | _                            |

| 418h         | _                            | 498h | _                            | 518h | _                            | 598h | _                            | 618h | _                            | 698h | _                            | 718h | _                            | 798h |                              |

| 419h         | _                            | 499h | _                            | 519h | _                            | 599h | _                            | 619h | _                            | 699h | _                            | 719h | _                            | 799h | _                            |

| 41Ah         | _                            | 49Ah | _                            | 51Ah | _                            | 59Ah | _                            | 61Ah | —                            | 69Ah | _                            | 71Ah | —                            | 79Ah |                              |

| 41Bh         | —                            | 49Bh | —                            | 51Bh | —                            | 59Bh | —                            | 61Bh | —                            | 69Bh | —                            | 71Bh | —                            | 79Bh |                              |

| 41Ch         | —                            | 49Ch | —                            | 51Ch | —                            | 59Ch | —                            | 61Ch |                              | 69Ch | —                            | 71Ch | _                            | 79Ch | _                            |

| 41Dh         | —                            | 49Dh | —                            | 51Dh | —                            | 59Dh | —                            | 61Dh | _                            | 69Dh | _                            | 71Dh |                              | 79Dh | _                            |

| 41Eh         | —                            | 49Eh | _                            | 51Eh | —                            | 59Eh | _                            | 61Eh | —                            | 69Eh | —                            | 71Eh | _                            | 79Eh | _                            |

| 41Fh         | —                            | 49Fh | _                            | 51Fh | _                            | 59Fh | _                            | 61Fh |                              | 69Fh | —                            | 71Fh |                              | 79Fh | _                            |

| 420h         |                              | 4A0h |                              | 520h |                              | 5A0h |                              | 620h |                              | 6A0h |                              | 720h |                              | 7A0h |                              |

|              | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |

| 46Fh         |                              | 4EFh |                              | 56Fh |                              | 5EFh |                              | 66Fh |                              | 6EFh |                              | 76Fh |                              | 7EFh |                              |

| 470h         |                              | 4F0h |                              | 570h |                              | 5F0h |                              | 670h |                              | 6F0h |                              | 770h |                              | 7F0h |                              |

|              | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |

| 47Fh         |                              | 4FFh |                              | 57Fh |                              | 5FFh |                              | 67Fh |                              | 6FFh |                              | 77Fh |                              | 7FFh |                              |

Legend: = Unimplemented data memory locations, read as '0'

### TABLE 3-10: PIC16(L)F1574/5/8/9 MEMORY MAP, BANKS 24-31

|      | BANK 24                       |      | BANK 25                       |      | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                       |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| C00h | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2) | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2) |

| C0Bh | (10010 0 2)                   | C8Bh | (10010 0 2)                   | D0Bh | (10510 0 2)                   | D8Bh | (10010 0 2)                   | E0Bh | (10010 0 2)                   | E8Bh | (10010 0 2)                   | F0Bh | (10010 0 2)                   | F8Bh | (10010 0 2)                   |

| C0Ch | _                             | C8Ch | _                             | D0Ch | —                             | D8Ch |                               | E0Ch |                               | E8Ch |                               | F0Ch | _                             | F8Ch |                               |

| C0Dh |                               | C8Dh | _                             | D0Dh | —                             |      |                               |      |                               |      |                               | F0Dh | _                             |      |                               |

| C0Eh |                               | C8Eh |                               | D0Eh | —                             |      |                               |      |                               |      |                               | F0Eh | —                             |      |                               |

| C0Fh | —                             | C8Fh | _                             | D0Fh | —                             |      |                               |      |                               |      |                               | F0Fh | _                             |      |                               |

| C10h | —                             | C90h | _                             | D10h | —                             |      |                               |      |                               |      |                               | F10h | _                             |      |                               |

| C11h | —                             | C91h | _                             | D11h | _                             |      |                               |      |                               |      |                               | F11h | _                             |      |                               |

| C12h | —                             | C92h | _                             | D12h | _                             |      |                               |      |                               |      |                               | F12h | _                             |      |                               |

| C13h |                               | C93h |                               | D13h | —                             |      |                               |      |                               |      |                               | F13h | —                             |      |                               |

| C14h | —                             | C94h |                               | D14h | —                             |      |                               |      |                               |      |                               | F14h | —                             |      |                               |

| C15h | —                             | C95h |                               | D15h | —                             |      |                               |      |                               |      |                               | F15h | —                             |      |                               |

| C16h | —                             | C96h | _                             | D16h | _                             |      |                               |      |                               |      |                               | F16h | _                             |      |                               |

| C17h | —                             | C97h | _                             | D17h | _                             |      |                               |      |                               |      |                               | F17h | _                             |      |                               |

| C18h | _                             | C98h | —                             | D18h | —                             |      | See Table 3-11                |      | See Table 3-12                |      | See Table 3-12                | F18h |                               |      | See Table 3-13                |

| C19h |                               | C99h | _                             | D19h | _                             |      |                               |      |                               |      |                               | F19h | _                             |      |                               |

| C1Ah |                               | C9Ah | _                             | D1Ah | _                             |      |                               |      |                               |      |                               | F1Ah | _                             |      |                               |

| C1Bh |                               | C9Bh | _                             | D1Bh | _                             |      |                               |      |                               |      |                               | F1Bh | _                             |      |                               |

| C1Ch |                               | C9Ch | _                             | D1Ch | —                             |      |                               |      |                               |      |                               | F1Ch | —                             |      |                               |

| C1Dh |                               | C9Dh | —                             | D1Dh | —                             |      |                               |      |                               |      |                               | F1Dh | —                             |      |                               |

| C1Eh |                               | C9Eh | —                             | D1Eh | —                             |      |                               |      |                               |      |                               | F1Eh | _                             |      |                               |

| C1Fh | _                             | C9Fh | _                             | D1Fh | _                             |      |                               |      |                               |      |                               | F1Fh |                               |      |                               |

| C20h |                               | CA0h |                               | D20h |                               |      |                               |      |                               |      |                               | F20h |                               |      |                               |

|      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      |                               |      |                               |      |                               |      | Unimplemented<br>Read as '0'  |      |                               |

| C6Fh |                               | CEFh |                               | D6Fh |                               | DEFh |                               | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                               |

| C70h |                               | CF0h |                               | D70h |                               | DF0h |                               | E70h |                               | EF0h |                               | F70h |                               | FF0h |                               |

|      | Accesses<br>70h – 7Fh         |

|      | -                             | CFFh | 7011-7111                     | D7Fh | /011 - /111                   | DFFh | 7011-7111                     | E7Fh | 701-711                       | EFFh | -                             | F7Fh | 7011-7111                     | FFFh | /011-/111                     |

| CFFh |                               | OFFN |                               | חדוט |                               | DEEU |                               |      |                               |      |                               |      |                               | LLLU |                               |

Legend: = Unimplemented data memory locations, read as '0'

### TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY

| Address | Name                 | Bit 7                             | Bit 6              | Bit 5          | Bit 4           | Bit 3                   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------|-----------------------------------|--------------------|----------------|-----------------|-------------------------|--------|--------|--------|----------------------|---------------------------------|

| Bank 0  |                      |                                   |                    |                |                 |                         |        |        |        |                      |                                 |

| 00Ch    | PORTA                | _                                 | _                  | RA5            | RA4             | RA3                     | RA2    | RA1    | RA0    | xx xxxx              | xx xxxx                         |

| 00Dh    | PORTB <sup>(1)</sup> | RB7                               | RB6                | RB5            | RB4             | —                       | —      |        | —      | xxxx                 | xxxx                            |

| 00Eh    | PORTC                | RC7 <sup>(1)</sup>                | RC6 <sup>(1)</sup> | RC5            | RC4             | RC3                     | RC2    | RC1    | RC0    | xxxx xxxx            | xxxx xxxx                       |

| 00Fh    | —                    | Unimplemen                        | implemented        |                |                 |                         |        |        |        |                      | _                               |

| 010h    | —                    | Unimplemen                        | nted               |                | _               | _                       |        |        |        |                      |                                 |

| 011h    | PIR1                 | TMR1GIF                           | ADIF               | RCIF           | TXIF            | —                       | —      | TMR2IF | TMR1IF | 000000               | 000000                          |

| 012h    | PIR2                 | _                                 | C2IF               | C1IF           | _               | —                       | —      | _      | —      | -00                  | -00                             |

| 013h    | PIR3                 | PWM4IF                            | PWM3IF             | PWM2IF         | PWM1IF          | —                       | —      | _      | —      | 0000                 | 0000                            |

| 014h    | —                    |                                   |                    |                |                 |                         |        |        |        | —                    | —                               |

| 015h    | TMR0                 | Holding Reg                       | ister for the 8    | 3-bit Timer0 ( | Count           |                         |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| 016h    | TMR1L                | Holding Reg                       | ister for the l    | _east Signific | ant Byte of the | 16-bit TMR1 Co          | ount   |        |        | xxxx xxxx            | uuuu uuuu                       |

| 017h    | TMR1H                | Holding Reg                       | ister for the I    | Most Significa | ant Byte of the | 16-bit TMR1 Co          | unt    |        |        | xxxx xxxx            | uuuu uuuu                       |

| 018h    | T1CON                | TMR1C                             | S<1:0>             | T1CK           | PS<1:0>         | —                       | T1SYNC | _      | TMR10N | 0000 -0-0            | uuuu -u-u                       |

| 019h    | T1GCON               | TMR1GE                            | T1GPOL             | T1GTM          | T1GSPM          | T <u>1GGO</u> /<br>DONE | T1GVAL | T1GS   | S<1:0> | 0000 0x00            | uuuu uxuu                       |

| 01Ah    | TMR2                 | Timer2 Mod                        | ule Register       |                |                 |                         |        |        |        | 0000 0000            | 0000 0000                       |

| 01Bh    | PR2                  | Timer2 Period Register            |                    |                |                 |                         |        |        |        | 1111 1111            | 1111 1111                       |

| 01Ch    | T2CON                | - T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |                    |                |                 |                         |        |        |        | -000 0000            | -000 0000                       |

| 01Dh    | _                    | Unimplemented                     |                    |                |                 |                         |        |        |        | _                    | _                               |

| 01Eh    | —                    | Unimplemer                        | Unimplemented      |                |                 |                         |        |        |        |                      |                                 |

| 01Fh    | —                    | Unimplemer                        | nted               |                |                 |                         |        |        |        | _                    | _                               |

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

## TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address            | Name                   | Bit 7                | Bit 6                | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------------------|------------------------|----------------------|----------------------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| Bank 4             |                        |                      |                      |       |       |       |       |       |       |                      |                                 |

| 20Ch               | WPUA                   |                      | _                    | WPUA5 | WPUA4 | WPUA3 | WPUA2 | WPUA1 | WPUA0 | 11 1111              | 11 1111                         |

| 20Dh               | WPUB <sup>(1)</sup>    | WPUB7                | WPUB6                | WPUB5 | WPUB4 | _     | —     | —     | _     | 1111                 | 1111                            |

| 20Eh               | WPUC                   | WPUC7 <sup>(1)</sup> | WPUC6 <sup>(1)</sup> | WPUC5 | WPUC4 | WPUC3 | WPUC2 | WPUC1 | WPUC0 | 1111 1111            | 1111 1111                       |

| 20Fh<br>to<br>21Fh | _                      | Unimplemer           | nimplemented         |       |       |       |       |       |       |                      | —                               |

| Bank 5             |                        |                      |                      |       |       |       |       |       |       |                      |                                 |

| 28Ch               | ODCONA                 |                      | _                    | ODA5  | ODA4  | _     | ODA2  | ODA1  | ODA0  | 00 -000              | 00 -000                         |

| 28Dh               | ODCONB <sup>(1)</sup>  | ODB7                 | ODB6                 | ODB5  | ODB4  | _     | —     | —     | _     | 0000                 | 0000                            |

| 28Eh               | ODCONC                 | ODC7 <sup>(1)</sup>  | ODC6 <sup>(1)</sup>  | ODC5  | ODC4  | ODC3  | ODC2  | ODC1  | ODC0  | 0000 0000            | 0000 0000                       |

| 28Fh<br>to<br>29Fh | _                      | Unimplemer           | nted                 |       |       |       |       |       |       | _                    | _                               |

| Bank 6             |                        |                      |                      |       |       |       |       |       |       |                      |                                 |

| 30Ch               | SLRCONA                |                      | _                    | SLRA5 | SLRA4 | _     | SLRA2 | SLRA1 | SLRA0 | 11 -111              | 11 -111                         |

| 30Dh               | SLRCONB <sup>(1)</sup> | SLRB7                | SLRB6                | SLRB5 | SLRB4 | _     | —     | —     | _     | 1111                 | 1111                            |

| 30Eh               | SLRCONC                | SLRC7 <sup>(1)</sup> | SLRC6 <sup>(1)</sup> | SLRC5 | SLRC4 | SLRC3 | SLRC2 | SLRC1 | SLRC0 | 1111 1111            | 1111 1111                       |

| 30Fh<br>to<br>31Fh | _                      | Unimplemer           | nted                 |       |       |       |       |       |       | _                    | —                               |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Note 1: PIC16(L)F1578/9 only.

2: PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

| U-0              | R-0/q                                  | R-q/q                                                                                      | R-0/q             | R-0/q           | R-q/q             | R-0/q            | R-0/q        |  |  |

|------------------|----------------------------------------|--------------------------------------------------------------------------------------------|-------------------|-----------------|-------------------|------------------|--------------|--|--|

| —                | PLLR                                   | OSTS                                                                                       | HFIOFR            | HFIOFL          | MFIOFR            | LFIOFR           | HFIOFS       |  |  |

| bit 7            |                                        |                                                                                            |                   |                 |                   |                  | bit C        |  |  |

|                  |                                        |                                                                                            |                   |                 |                   |                  |              |  |  |

| Legend:          |                                        |                                                                                            |                   |                 |                   |                  |              |  |  |

| R = Readable     | e bit                                  | W = Writable                                                                               | bit               | U = Unimpler    | nented bit, reac  | l as '0'         |              |  |  |

| u = Bit is unc   | hanged                                 | x = Bit is unkr                                                                            | nown              | -n/n = Value a  | at POR and BO     | R/Value at all o | other Resets |  |  |

| '1' = Bit is set | t                                      | '0' = Bit is cle                                                                           | ared              | q = Condition   | al                |                  |              |  |  |

|                  |                                        |                                                                                            |                   |                 |                   |                  |              |  |  |

| bit 7            | •                                      | ted: Read as '                                                                             | 0'                |                 |                   |                  |              |  |  |

| bit 6            | PLLR 4x PLL                            | •                                                                                          |                   |                 |                   |                  |              |  |  |

|                  | 1 = 4x PLLi<br>0 = 4x PLLi             |                                                                                            |                   |                 |                   |                  |              |  |  |

| bit 5            |                                        | <ul> <li>4x PLL is not ready</li> <li>STS: Oscillator Start-up Timer Status bit</li> </ul> |                   |                 |                   |                  |              |  |  |

|                  |                                        | •                                                                                          |                   | FOSC<1.0>1      | oits of the Confi | guration Word    | s            |  |  |

|                  |                                        | from an intern                                                                             |                   |                 |                   | guiation word    | 5            |  |  |

| bit 4            | HFIOFR: Hig                            | h-Frequency Ir                                                                             | iternal Oscillate | or Ready bit    |                   |                  |              |  |  |

|                  | 1 = HFINTO                             |                                                                                            |                   |                 |                   |                  |              |  |  |

|                  | 0 = HFINTO                             | SC is not ready                                                                            | 1                 |                 |                   |                  |              |  |  |

| bit 3            | •                                      | h-Frequency In                                                                             |                   | or Locked bit   |                   |                  |              |  |  |

|                  |                                        | SC is at least 2<br>SC is not 2% a                                                         |                   |                 |                   |                  |              |  |  |

| bit 2            |                                        |                                                                                            |                   | illator Roady b | i+                |                  |              |  |  |

|                  |                                        | dium-Frequend                                                                              | y memai Osc       | illator Ready D | it.               |                  |              |  |  |

|                  |                                        | 1 = MFINTOSC is ready<br>0 = MFINTOSC is not ready                                         |                   |                 |                   |                  |              |  |  |

| bit 1            | LFIOFR: Low                            | LFIOFR: Low-Frequency Internal Oscillator Ready bit                                        |                   |                 |                   |                  |              |  |  |

|                  | 1 = LFINTOS                            | SC is ready                                                                                |                   | -               |                   |                  |              |  |  |

|                  | 0 = LFINTOS                            | SC is not ready                                                                            |                   |                 |                   |                  |              |  |  |

| bit 0            | HFIOFS: Hig                            | h-Frequency Ir                                                                             | ternal Oscillato  | or Stable bit   |                   |                  |              |  |  |

|                  | 1 = HFINTOSC is at least 0.5% accurate |                                                                                            |                   |                 |                   |                  |              |  |  |

|                  | 0 = HFINTO                             | SC is not 0.5%                                                                             | accurate          |                 |                   |                  |              |  |  |

### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

### 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 6.1.1 POWER-UP TIMER (PWRT)

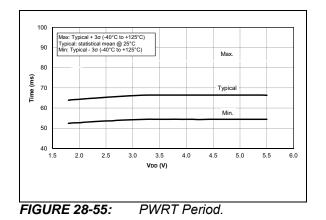

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

### 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- · BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 1.0        | 37     | Awake       | Active   | Waits for BOR ready (BORRDY = 1)                                    |

| 10         | 10 X   |             | Disabled |                                                                     |

| 0.1        | 1      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 01         | 0      | х           | Disabled | Begins immediately (BORRDY = x)                                     |

| 00         | Х      | Х           | Disabled |                                                                     |

#### TABLE 6-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

| U-0              | U-0       | R/W-x/u           | R/W-x/u | U-0                                | R/W-x/u        | R/W-x/u          | R/W-x/u     |  |  |

|------------------|-----------|-------------------|---------|------------------------------------|----------------|------------------|-------------|--|--|

| —                | _         | LATA5             | LATA4   | —                                  | LATA2          | LATA1            | LATA0       |  |  |

| bit 7            |           |                   |         |                                    |                |                  | bit 0       |  |  |

|                  |           |                   |         |                                    |                |                  |             |  |  |

| Legend:          |           |                   |         |                                    |                |                  |             |  |  |

| R = Readable b   | oit       | W = Writable      | bit     | U = Unimplemented bit, read as '0' |                |                  |             |  |  |

| u = Bit is uncha | anged     | x = Bit is unkr   | nown    | -n/n = Value a                     | at POR and BOF | R/Value at all o | ther Resets |  |  |

| '1' = Bit is set |           | '0' = Bit is clea | ared    |                                    |                |                  |             |  |  |

|                  |           |                   |         |                                    |                |                  |             |  |  |

| bit 7-6          | Unimpleme | nted: Read as '   | כ'      |                                    |                |                  |             |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 5-4 | LATA<5:4>: RA<5:4> Output Latch Value bits <sup>(1)</sup> |

- bit 3 Unimplemented: Read as '0'

- bit 2-0 LATA<2:0>: RA<2:0> Output Latch Value bits<sup>(1)</sup>

- **Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

### REGISTER 11-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|---------|-----|---------|---------|---------|

| —     | —   |     | ANSA4   | _   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ANSA4: Analog Select between Analog or Digital Function on pins RA4, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul>                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to                                                                                                                                                                                                           |

allow external control of the voltage on the pin.

| R/W-0/0                                 | R/W-0/0             | R/W-0/0            | R/W-0/0 | R/W-0/0         | R/W-0/0            | R/W-0/0             | R/W-0/0 |

|-----------------------------------------|---------------------|--------------------|---------|-----------------|--------------------|---------------------|---------|

| ODC7 <sup>(1)</sup>                     | ODC6 <sup>(1)</sup> | ODC5               | ODC4    | ODC3            | ODC2               | ODC1                | ODC0    |

| bit 7                                   |                     |                    |         |                 |                    |                     | bit 0   |

|                                         |                     |                    |         |                 |                    |                     |         |

| Legend:                                 |                     |                    |         |                 |                    |                     |         |

| R = Readable bit                        | t                   | W = Writable bi    | t       | U = Unimpleme   | ented bit, read as | '0'                 |         |

| u = Bit is unchanged x = Bit is unknown |                     |                    |         | -n/n = Value at | POR and BOR/V      | alue at all other I | Resets  |

| '1' = Bit is set                        |                     | '0' = Bit is clear | ed      |                 |                    |                     |         |

### REGISTER 11-22: ODCONC: PORTC OPEN DRAIN CONTROL REGISTER

bit 7-0

ODC<7:0>: PORTC Open-Drain Enable bits<sup>(1)</sup>

For RC<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

**Note 1:** ODC<7:6> are available on PIC16(L)F1578/9 only.

### REGISTER 11-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| SLRC7 <sup>(1)</sup> | SLRC6 <sup>(1)</sup> | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7                | •                    |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits<sup>(1)</sup> For RC<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

Note 1: SLRC<7:6> are available on PIC16(L)F1578/9 only.

### REGISTER 11-24: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| R/W-1/1                | R/W-1/1                | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|------------------------|------------------------|---------|---------|---------|---------|---------|---------|

| INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7                  |                        |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits<sup>(1)</sup>

For RC<7:0> pins, respectively

1 = ST input used for port reads and interrupt-on-change

0 = TTL input used for port reads and interrupt-on-change

Note 1: INLVLC<7:6> are available on PIC16(L)F1578/9 only.

### 12.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

**Note:** The I<sup>2</sup>C default input pins are I<sup>2</sup>C and SMBus compatible and are the only pins on the device with this compatibility.

### 12.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 12-1.

EXAMPLE 12-1: PPS LOCK/UNLOCK SEQUENCE

| the second destruction with a            |

|------------------------------------------|

| ; suspend interrupts                     |

| bcf INTCON,GIE                           |

| ; BANKSEL PPSLOCK ; set bank             |

| ; required sequence, next 5 instructions |

| movlw 0x55                               |

| movwf PPSLOCK                            |

| movlw 0xAA                               |

| movwf PPSLOCK                            |

| ; Set PPSLOCKED bit to disable writes or |

| ; Clear PPSLOCKED bit to enable writes   |

| bsf PPSLOCK, PPSLOCKED                   |

| ; restore interrupts                     |

| bsf INTCON,GIE                           |

|                                          |

### 12.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

### 12.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

### 12.7 Effects of a Reset

A device Power-On-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in Table 12-1.

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3         | Bit 2     | Bit 1    | Bit 0     | Register<br>on page |  |

|-----------------------|-------|-------|-------|-------|---------------|-----------|----------|-----------|---------------------|--|

| PPSLOCK               |       | _     | _     | _     | —             | _         | —        | PPSLOCKED | 138                 |  |

| INTPPS                |       | _     | _     |       | INTPPS<4:0>   |           |          |           |                     |  |

| TOCKIPPS              |       | _     | _     |       | T0CKIPPS<4:0> |           |          |           |                     |  |

| T1CKIPPS              |       | _     | _     |       |               | T1CKIPPS< | 4:0>     |           | 137                 |  |

| T1GPPS                |       | _     | _     |       |               | T1GPPS<4  | :0>      |           | 137                 |  |

| CWG1INPPS             |       | _     | _     |       | C             | WG1INPPS  | <4:0>    |           | 137                 |  |

| RXPPS                 |       | _     | _     |       |               | RXPPS<4   | 0>       |           | 137                 |  |

| CKPPS                 |       | _     | _     |       |               | CKPPS<4   | 0>       |           | 137                 |  |

| ADCACTPPS             |       | _     | _     |       | А             | DCACTPPS  | <4:0>    |           | 137                 |  |

| RA0PPS                |       | _     | _     | _     |               | RAOF      | PPS<3:0> |           | 137                 |  |

| RA1PPS                |       | —     | _     | —     |               | RA1F      | PPS<3:0> |           | 137                 |  |

| RA2PPS                |       | _     | _     | _     |               | RA2F      | PPS<3:0> |           | 137                 |  |

| RA4PPS                |       | _     | _     | _     |               | RA4F      | PPS<3:0> |           | 137                 |  |

| RA5PPS                |       | _     | _     | _     |               | RA5F      | PPS<3:0> |           | 137                 |  |

| RB4PPS <sup>(1)</sup> |       | _     | _     | _     |               | RB4F      | PPS<3:0> |           | 137                 |  |

| RB5PPS <sup>(1)</sup> |       | _     | _     | _     |               | RB5F      | PPS<3:0> |           | 137                 |  |

| RB6PPS <sup>(1)</sup> |       | _     | _     | _     |               | RB6F      | PPS<3:0> |           | 137                 |  |

| RB7PPS <sup>(1)</sup> |       | _     | _     | _     |               | RB7F      | PPS<3:0> |           | 137                 |  |

| RC0PPS                |       | _     | _     | _     |               | RCOF      | PPS<3:0> |           | 137                 |  |

| RC1PPS                |       | _     | _     | _     |               | RC1F      | PPS<3:0> |           | 137                 |  |

| RC2PPS                |       | _     | _     | _     |               | RC2F      | PPS<3:0> |           | 137                 |  |

| RC3PPS                |       | —     | _     | —     | — RC3PPS<3:0> |           |          |           |                     |  |

| RC4PPS                | _     | _     | —     | _     |               | RC4       | PPS<3:0> |           | 137                 |  |

| RC5PPS                | _     | —     | —     | —     | RC5PPS<3:0>   |           |          |           |                     |  |

| RC6PPS <sup>(1)</sup> |       | —     | —     | —     |               | RC6       | PPS<3:0> |           | 137                 |  |

| RC7PPS <sup>(1)</sup> | —     | _     | —     | _     |               | RC7F      | PPS<3:0> |           | 137                 |  |

### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

**Note 1:** PIC16(L)F1578/9 only.

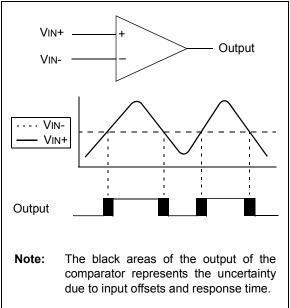

#### FIGURE 18-2: SINGLE COMPARATOR

### 18.2 Comparator Control

The comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- Output selection

- Output polarity

- Speed/Power selection

- Hysteresis enable

- · Output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

### 18.2.2 COMPARATOR POSITIVE INPUT SELECTION

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC1\_output

- FVR\_buffer2

- Vss

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

## 18.2.3 COMPARATOR NEGATIVE INPUT SELECTION

The CxNCH<2:0> bits of the CMxCON0 register direct one of the input sources to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog<br>input, the appropriate bits must be set in<br>the ANSEL register and the correspond- |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

|       | ing TRIS bits must also be set to disable                                                                                      |

|       | the output drivers.                                                                                                            |

### 18.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

The synchronous comparator output signal (CxOUT\_sync) is available to the following peripheral(s):

- Analog-to-Digital Converter (ADC)

- Timer1

The asynchronous comparator output signal (CxOUT\_async) is available to the following peripheral(s):

Complementary Waveform Generator (CWG)

Note: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

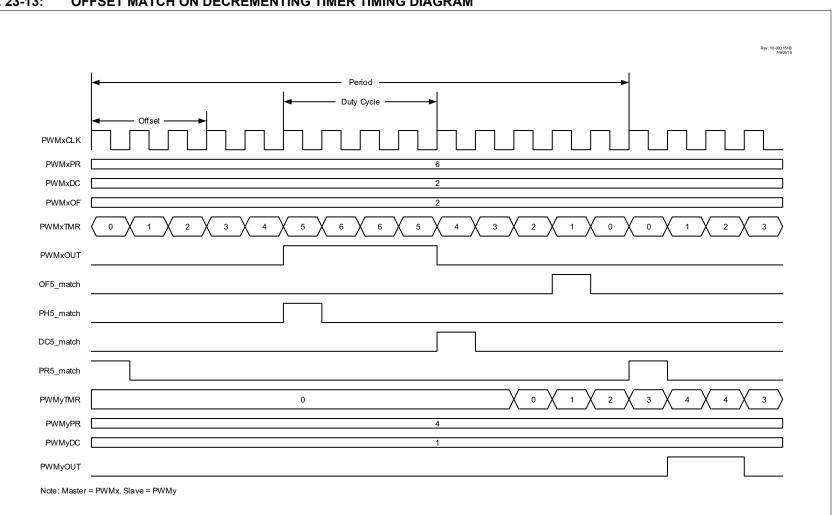

### 23.2 PWM Modes

PWM Modes are selected with MODE<1:0> bits of the PWMxCON register (Register 23-1).

In all PWM modes an offset match event can also be used to synchronize the PWMxTMR in three offset modes. See **Section 23.3 "Offset Modes"** for more information.

### 23.2.1 STANDARD MODE

The Standard mode (MODE = 00) selects a single phase PWM output. The PWM output in this mode is determined by when the period, duty cycle, and phase counts match the PWMxTMR value. The start of the duty cycle occurs on the phase match and the end of the duty cycle occurs on the duty cycle match. The period match resets the timer. The offset match can also be used to synchronize the PWMxTMR in the offset modes. See **Section 23.3 "Offset Modes"** for more information.

Equation 23-1 is used to calculate the PWM period in Standard mode.

Equation 23-2 is used to calculate the PWM duty-cycle ratio in Standard mode.

### EQUATION 23-1: PWM PERIOD IN STANDARD MODE

$$Period = \frac{(PWMxPR + 1) \cdot Prescale}{PWMxCLK}$$

## EQUATION 23-2: PWM DUTY CYCLE IN STANDARD MODE

$$Duty Cycle = \frac{(PWMxDC - PWMxPH)}{PWMxPR + 1}$$

A detailed timing diagram for Standard mode is shown in Figure 23-4.

### 23.2.2 SET ON MATCH MODE

The Set On Match mode (MODE = 01) generates an active output when the phase count matches the PWMxTMR value. The output stays active until the OUT bit of the PWMxCON register is cleared or the PWM module is disabled. The duty cycle count has no effect in this mode. The period count only determines the maximum PWMxTMR value above which no phase matches can occur.

The PWMxOUT bit can be used to set or clear the output of the PWM in this mode. Writes to this bit will take place on the next rising edge of the PWM\_clock after the bit is written.

A detailed timing diagram for Set On Match is shown in Figure 23-5.

### 23.2.3 TOGGLE ON MATCH MODE

The Toggle On Match mode (MODE = 10) generates a 50% duty cycle PWM with a period twice as long as that computed for the standard PWM mode. Duty cycle count has no effect in this mode. The phase count determines how many PWMxTMR periods after a period event the output will toggle.

Writes to the OUT bit of the PWMxCON register will have no effect in this mode.

A detailed timing diagram for Toggle On Match is shown in Figure 23-6.

### 23.2.4 CENTER-ALIGNED MODE

The Center-Aligned mode (MODE = 11) generates a PWM waveform that is centered in the period. In this mode the period is two times the PWMxPR count. The PWMxTMR counts up to the period value then counts back down to 0. The duty cycle count determines both the start and end of the active PWM output. The start of the duty cycle occurs at the match event when PWMxTMR is incrementing and the duty cycle ends at the match event when PWMxTMR is decrementing. The incrementing match value is the period count minus the duty cycle count. The decrementing match value is the incrementing match value plus 1.

Equation 23-3 is used to calculate the PWM period in Center-Aligned mode.

### EQUATION 23-3: PWM PERIOD IN CENTER-ALIGNED MODE

$$Period = \frac{(PWMxPR + 1) \cdot Prescale \cdot 2}{PWMxCLK}$$

Equation 23-4 is used to calculate the PWM duty cycle ratio in Center-Aligned mode

### EQUATION 23-4: PWM DUTY CYCLE IN CENTER-ALIGNED MODE

$$Duty Cycle = \frac{PWMxDC \cdot 2}{(PWMxPR + 1) \cdot 2}$$

Writes to PWMxOUT will have no effect in this mode.

A detailed timing diagram for Center-Aligned mode is shown in Figure 23-7.

## FIGURE 23-13:

PIC16(L)F1574/5/8/9

| Name       | Bit 7 | Bit 6 | Bit 5               | Bit 4 | Bit 3    | Bit 2  | Bit 1 | Bit 0 | Register<br>on Page |

|------------|-------|-------|---------------------|-------|----------|--------|-------|-------|---------------------|

| PWM3CLKCON | _     |       | PS<2:0> — — CS<1:0> |       |          |        |       |       |                     |

| PWM3LDCON  | LDA   | LDT   | —                   | —     | _        | _      | LDS   | <1:0> | 236                 |

| PWM30FC0N  | _     | OFM   | <1:0>               | OFO   | _        | _      | OFS   | <1:0> | 237                 |

| PWM4PHL    |       | •     |                     | P     | H<7:0>   |        | •     |       | 238                 |

| PWM4PHH    |       |       |                     | PI    | H<15:8>  |        |       |       | 238                 |

| PWM4DCL    |       |       |                     | D     | C<7:0>   |        |       |       | 239                 |

| PWM4DCH    |       |       |                     | D     | C<15:8>  |        |       |       | 239                 |

| PWM4PRL    |       |       |                     | P     | 'R<7:0>  |        |       |       | 240                 |

| PWM4PRH    |       |       |                     | PI    | R<15:8>  |        |       |       | 240                 |

| PWM40FL    |       |       |                     | C     | )F<7:0>  |        |       |       | 241                 |

| PWM40FH    |       |       |                     | 0     | F<15:8>  |        |       |       | 241                 |

| PWM4TMRL   |       |       |                     | TN    | /IR<7:0> |        |       |       | 242                 |

| PWM4TMRH   |       |       |                     | TN    | IR<15:8> |        |       |       | 242                 |

| PWM4CON    | EN    | _     | OUT                 | POL   | MODE     | E<1:0> |       | —     | 233                 |

| PWM4INTE   | _     | _     | _                   | _     | OFIE     | PHIE   | DCIE  | PRIE  | 234                 |

| PWM4INTF   |       | —     | _                   | —     | OFIF     | PHIF   | DCIF  | PRIF  | 234                 |

| PWM4CLKCON | _     |       | PS<2:0>             | •     | _        | _      | CS<   | :1:0> | 235                 |

| PWM4LDCON  | LDA   | LDT   | —                   | —     | _        | _      | LDS   | <1:0> | 236                 |

| PWM40FCON  | _     | OFM   | <1:0>               | OFO   | _        | _      | OFS   | <1:0> | 237                 |

### TABLE 23-2: SUMMARY OF REGISTERS ASSOCIATED WITH PWM (CONTINUED)

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PWM.

### TABLE 23-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3       | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------------|----------|---------|---------|---------------------|

|         | 13:8 | -       | —       | -        | —         | CLKOUTEN BOREN |          | N<1:0>  | —       | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |                | -        | FOSC    | C<1:0>  | 56                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

## PIC16(L)F1574/5/8/9

## REGISTER 24-4: CWGxDBR: COMPLEMENTARY WAVEFORM GENERATOR (CWGx) RISING DEAD-BAND COUNT REGISTER

|                 | DEP       | D-BAND COUL                                                            | NI REGIST | =R                             |                  |                  |              |  |  |  |

|-----------------|-----------|------------------------------------------------------------------------|-----------|--------------------------------|------------------|------------------|--------------|--|--|--|

| U-0             | U-0       | R/W-x/u                                                                | R/W-x/u   | R/W-x/u                        | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |  |  |

| _               | _         |                                                                        |           | CWGxD                          | BR<5:0>          |                  |              |  |  |  |

| bit 7           |           |                                                                        |           |                                |                  |                  | bit 0        |  |  |  |

| Legend:         |           |                                                                        |           |                                |                  |                  |              |  |  |  |

| R = Readabl     | le bit    | W = Writable                                                           | bit       | U = Unimpler                   | nented bit, read | l as '0'         |              |  |  |  |

| u = Bit is und  | changed   | x = Bit is unkr                                                        | nown      | -n/n = Value a                 | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is se | et        | '0' = Bit is clea                                                      | ared      | q = Value depends on condition |                  |                  |              |  |  |  |

|                 |           |                                                                        |           |                                |                  |                  |              |  |  |  |

| bit 7-6         | Unimplem  | ented: Read as '                                                       | 0'        |                                |                  |                  |              |  |  |  |

| bit 5-0         | 11 1111 = | <b>R&lt;5:0&gt;:</b> Complem<br>= 63-64 counts of<br>= 62-63 counts of | dead band | orm Generator                  | (CWGx) Rising    | Counts           |              |  |  |  |

|                 | •         |                                                                        |           |                                |                  |                  |              |  |  |  |

|                 | •         |                                                                        |           |                                |                  |                  |              |  |  |  |

|                 | •         |                                                                        |           |                                |                  |                  |              |  |  |  |

|                 | 00 0010=  | = 2-3 counts of de                                                     | ad band   |                                |                  |                  |              |  |  |  |

# REGISTER 24-5: CWGxDBF: COMPLEMENTARY WAVEFORM GENERATOR (CWGx) FALLING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   |         |         | CWGxD   | BF<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-6 | Unimplemented: Read as '0'                                                 |

|---------|----------------------------------------------------------------------------|

| bit 5-0 | CWGxDBF<5:0>: Complementary Waveform Generator (CWGx) Falling Counts       |

|         | 11 1111 = 63-64 counts of dead band<br>11 1110 = 62-63 counts of dead band |

|         |                                                                            |

|         | •                                                                          |

- •

- •

- 00 0010 = 2-3 counts of dead band

00 0001 = 1-2 counts of dead band 00 0000 = 0 counts of dead band

- 00 0001 = 1-2 counts of dead band

- 00 0000 = 0 counts of dead band. Dead-band generation is bypassed.

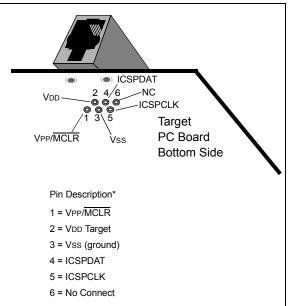

### 25.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>™</sup> refer to the "*PIC16(L)F157x Memory Programming Specification*" (DS40001766).

### 25.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

### 25.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5** "**MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

### 25.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 25-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 25-2.

\*

### TABLE 27-8: OSCILLATOR PARAMETERS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                          |                    |      |      |      |       |                                    |  |

|---------------|---------------------------------------------------------|----------------------------------------------------------|--------------------|------|------|------|-------|------------------------------------|--|

| Param.<br>No. | Sym. Characteristic                                     |                                                          | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                         |  |