Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1575t-i-st |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 2: PACKAGES

| Packages      | PDIP | SOIC | TSSOP | SSOP | UQFN |

|---------------|------|------|-------|------|------|

| PIC16(L)F1574 | •    | •    | •     |      | •    |

| PIC16(L)F1575 | •    | •    | •     |      | •    |

| PIC16(L)F1578 | •    | •    |       | •    | •    |

| PIC16(L)F1579 | •    | •    |       | •    | •    |

Note: Pin details are subject to change.

### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

### 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See section **Section 3.5 "Stack"** for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 26.0** "Instruction Set Summary" for more details.

### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

### REGISTER 3-1: STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to **Section 26.0 "Instruction Set Summary"**).

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and <u>Digit</u> Borrow out bits, respectively, in subtraction.

| U-0                                     | U-0 | U-0               | R-1/q | R-1/q                                                 | R/W-0/u | R/W-0/u           | R/W-0/u          |  |  |

|-----------------------------------------|-----|-------------------|-------|-------------------------------------------------------|---------|-------------------|------------------|--|--|

|                                         | _   | —                 | TO    | PD                                                    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |

| bit 7                                   |     |                   |       |                                                       |         |                   | bit 0            |  |  |

|                                         |     |                   |       |                                                       |         |                   |                  |  |  |

| Legend:                                 |     |                   |       |                                                       |         |                   |                  |  |  |

| R = Readable b                          | oit | W = Writable I    | bit   | U = Unimplemented bit, read as '0'                    |         |                   |                  |  |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | iown  | -n/n = Value at POR and BOR/Value at all other Resets |         |                   |                  |  |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared  | q = Value depends on condition                        |         |                   |                  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                               |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                             |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1: | For $\overline{\text{Borrow}}$ the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

|    |      | BANK5          |      | BANK6          |      | BANK7          |

|----|------|----------------|------|----------------|------|----------------|

|    | 280h |                | 300h |                | 380h |                |

| rs |      | Core Registers |      | Core Registers |      | Core Registers |

|    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |

|    | 28Bh |                | 30Bh |                | 38Bh |                |

|    | 28Ch | ODCONA         | 30Ch | SLRCONA        | 38Ch | INLVLA         |

|    | 28Dh | _              | 30Dh | _              | 38Dh | _              |

|    | 28Eh | ODCONC         | 30Eh | SLRCONC        | 38Eh | INLVLC         |

|    | 28Fh | _              | 30Fh | _              | 38Fh | _              |

|    | 290h | _              | 310h | _              | 390h | _              |

|    | 291h | _              | 311h | _              | 391h | IOCAP          |

|    | 292h | _              | 312h | _              | 392h | IOCAN          |

|    | 293h | _              | 313h | _              | 393h | IOCAF          |

|    | 294h | _              | 314h | _              | 394h | _              |

|    | 295h | _              | 315h | _              | 395h | _              |

|    | 296h | _              | 316h | _              | 396h | _              |

|    | 297h | _              | 317h | _              | 397h | IOCCP          |

|    | 298h |                | 318h | _              | 398h | IOCCN          |

|    | 299h | _              | 319h | _              | 399h | IOCCF          |

|    | 29Ah | _              | 31Ah | _              | 39Ah | _              |

|    | 29Bh | _              | 31Bh | _              | 39Bh | _              |

|    | 29Ch |                | 31Ch |                | 39Ch | _              |

|    | 29Dh | _              | 31Dh | _              | 39Dh | _              |

|    | 20Fh |                | 2456 |                | 2056 |                |

\_

General Purpose Register 80 Bytes

Accesses 70h – 7Fh

#### TABLE 3-4: PIC16(L)F1575 MEMORY MAP, BANKS 0-7 BANK0 BANK1

BANK2

| 000h |                                            | 080h |                                            | 100h |                                            | 180h |                                            | 200h |                                            | 280h |                                            | 300h |                                            | 380h |   |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|---|

|      | Core Registers                             |      | C |

|      | (Table 3-2)                                |      |   |

| 00Bh |                                            | 08Bh |                                            | 10Bh |                                            | 18Bh |                                            | 20Bh |                                            | 28Bh |                                            | 30Bh |                                            | 38Bh |   |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                                     | 20Ch | WPUA                                       | 28Ch | ODCONA                                     | 30Ch | SLRCONA                                    | 38Ch |   |

| 00Dh | —                                          | 08Dh | —                                          | 10Dh | —                                          | 18Dh | _                                          | 20Dh | _                                          | 28Dh | _                                          | 30Dh | —                                          | 38Dh |   |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | ANSELC                                     | 20Eh | WPUC                                       | 28Eh | ODCONC                                     | 30Eh | SLRCONC                                    | 38Eh |   |

| 00Fh | —                                          | 08Fh | —                                          | 10Fh | —                                          | 18Fh |                                            | 20Fh | _                                          | 28Fh | —                                          | 30Fh | —                                          | 38Fh |   |

| 010h | —                                          | 090h | —                                          | 110h | —                                          | 190h | —                                          | 210h | —                                          | 290h | _                                          | 310h | —                                          | 390h |   |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | CM1CON0                                    | 191h | PMADRL                                     | 211h | —                                          | 291h | _                                          | 311h | —                                          | 391h |   |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | CM1CON1                                    | 192h | PMADRH                                     | 212h | —                                          | 292h | _                                          | 312h | —                                          | 392h |   |

| 013h | PIR3                                       | 093h | PIE3                                       | 113h | CM2CON0                                    | 193h | PMDATL                                     | 213h | _                                          | 293h | —                                          | 313h | —                                          | 393h |   |

| 014h | —                                          | 094h | —                                          | 114h | CM2CON1                                    | 194h | PMDATH                                     | 214h | _                                          | 294h | —                                          | 314h | —                                          | 394h |   |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h | CMOUT                                      | 195h | PMCON1                                     | 215h | _                                          | 295h | —                                          | 315h | —                                          | 395h |   |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | BORCON                                     | 196h | PMCON2                                     | 216h | _                                          | 296h | —                                          | 316h | —                                          | 396h |   |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | VREGCON <sup>(1)</sup>                     | 217h | —                                          | 297h | —                                          | 317h | —                                          | 397h |   |

| 018h | T1CON                                      | 098h | OSCTUNE                                    | 118h | DACCON0                                    | 198h | —                                          | 218h | —                                          | 298h | —                                          | 318h | _                                          | 398h |   |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | DACCON1                                    | 199h | RCREG                                      | 219h | —                                          | 299h | _                                          | 319h | _                                          | 399h |   |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah | —                                          | 19Ah | TXREG                                      | 21Ah | —                                          | 29Ah | —                                          | 31Ah | —                                          | 39Ah |   |

| 01Bh | PR2                                        | 09Bh | ADRESL                                     | 11Bh | —                                          | 19Bh | SPBRGL                                     | 21Bh | —                                          | 29Bh | —                                          | 31Bh | —                                          | 39Bh |   |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch | —                                          | 19Ch | SPBRGH                                     | 21Ch | _                                          | 29Ch | —                                          | 31Ch | —                                          | 39Ch |   |

| 01Dh | —                                          | 09Dh | ADCON0                                     | 11Dh | —                                          | 19Dh | RCSTA                                      | 21Dh | _                                          | 29Dh | _                                          | 31Dh | —                                          | 39Dh |   |

| 01Eh | —                                          | 09Eh | ADCON1                                     | 11Eh | —                                          | 19Eh | TXSTA                                      | 21Eh | _                                          | 29Eh | —                                          | 31Eh | —                                          | 39Eh |   |

| 01Fh | —                                          | 09Fh | ADCON2                                     | 11Fh | —                                          | 19Fh | BAUDCON                                    | 21Fh | —                                          | 29Fh | —                                          | 31Fh | —                                          | 39Fh |   |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h |                                            | 3A0h |   |

|      | General<br>Purpose<br>Register<br>80 Bytes |      |   |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                            | 3EFh |   |

| 070h |                                            | 0F0h |                                            | 170h |                                            | 1F0h |                                            | 270h |                                            | 2F0h |                                            | 370h |                                            | 3F0h |   |

|      | Common RAM                                 |      | Accesses<br>70h – 7Fh                      |      |   |

| 07Fh |                                            | 0FFh |                                            | 17Fh |                                            | 1FFh |                                            | 27Fh |                                            | 2FFh |                                            | 37Fh |                                            | 3FFh |   |

|      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |   |

BANK3

BANK4

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1575.

DS40001782C-page 26

| TABLE 3            |                       |                        |                       |         |         | ARY (CONT |         |         |         |                      | Value on            |

|--------------------|-----------------------|------------------------|-----------------------|---------|---------|-----------|---------|---------|---------|----------------------|---------------------|

| Address            | Name                  | Bit 7                  | Bit 6                 | Bit 5   | Bit 4   | Bit 3     | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | all other<br>Resets |

| Bank 7             |                       |                        |                       |         |         |           |         |         |         |                      |                     |

| 38Ch               | INLVLA                |                        | —                     | INLVLA5 | INLVLA4 | INLVLA3   | INLVLA2 | INLVLA1 | INLVLA0 | 11 1111              | 11 1111             |

| 38Dh               | INLVLB <sup>(1)</sup> | INLVLB7                | INLVLB6               | INLVLB5 | INLVLB4 | —         | _       | —       | —       | 1111                 | 1111                |

| 38Eh               | INLVLC                | INLVLC7 <sup>(1)</sup> | INLVLC6(1)            | INLVLC5 | INLVLC4 | INLVLC3   | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111            | 1111 1111           |

| 38Fh<br>to<br>390h | _                     | Unimpleme              | nted                  |         |         |           |         |         |         | -                    | —                   |

| 391h               | IOCAP                 | _                      | _                     | IOCAP5  | IOCAP4  | IOCAP3    | IOCAP2  | IOCAP1  | IOCAP0  | 00 0000              | 00 0000             |

| 392h               | IOCAN                 | _                      | _                     | IOCAN5  | IOCAN4  | IOCAN3    | IOCAN2  | IOCAN1  | IOCAN0  | 00 0000              | 00 0000             |

| 393h               | IOCAF                 | _                      | _                     | IOCAF5  | IOCAF4  | IOCAF3    | IOCAF2  | IOCAF1  | IOCAF0  | 00 0000              | 00 0000             |

| 394h               | IOCBP <sup>(1)</sup>  | IOCBP7                 | IOCBP6                | IOCBP5  | IOCBP4  | —         | _       | —       | —       | 0000                 | 00                  |

| 395h               | IOCBN <sup>(1)</sup>  | IOCBN7                 | IOCBN6                | IOCBN5  | IOCBN4  | —         | _       | —       | —       | 0000                 | 00                  |

| 396h               | IOCBF <sup>(1)</sup>  | IOCBF7                 | IOCBF6                | IOCBF5  | IOCBF4  | —         | _       | —       | —       | 0000                 | 00                  |

| 397h               | IOCCP                 | IOCCP7 <sup>(1)</sup>  | IOCCP6 <sup>(1)</sup> | IOCCP5  | IOCCP4  | IOCCP3    | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000            | 0000 0000           |

| 398h               | IOCCN                 | IOCCN7 <sup>(1)</sup>  | IOCCN6 <sup>(1)</sup> | IOCCN5  | IOCCN4  | IOCCN3    | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000            | 0000 0000           |

| 399h               | IOCCF                 | IOCCF7 <sup>(1)</sup>  | IOCCF6 <sup>(1)</sup> | IOCCF5  | IOCCF4  | IOCCF3    | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000            | 0000 0000           |

| 39Ah<br>to<br>39Fh | _                     | Unimpleme              | Jnimplemented —       |         |         |           |         |         |         | —                    |                     |

| Bank 8             |                       |                        |                       |         |         |           |         |         |         |                      |                     |

| 40Ch<br>to<br>41Fh | _                     | Unimpleme              | nted                  |         |         |           |         |         |         | _                    | _                   |

| Bank 9             |                       |                        |                       |         |         |           |         |         |         |                      |                     |

|                    | -                     |                        |                       |         |         |           |         |         |         | 1                    |                     |

####

to 49Fh

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3:

Unimplemented, read as '1'.

48Ch

Unimplemented

# 5.5 Register Definitions: Oscillator Control

| R/W-0/0          | R/W-0/0                                                                                                       | R/W-1/1                                                                                                                                                                                                                   | R/W-1/1                            | R/W-1/1         | U-0                | R/W-0/0         | R/W-0/0      |

|------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|--------------------|-----------------|--------------|

| SPLLEN           |                                                                                                               | IRCF                                                                                                                                                                                                                      | <3:0>                              |                 | _                  | SCS             | <1:0>        |

| bit 7            |                                                                                                               |                                                                                                                                                                                                                           |                                    |                 |                    |                 | bit 0        |

|                  |                                                                                                               |                                                                                                                                                                                                                           |                                    |                 |                    |                 |              |

| Legend:          |                                                                                                               |                                                                                                                                                                                                                           | .,                                 |                 |                    |                 |              |

| R = Readable     |                                                                                                               | W = Writable I                                                                                                                                                                                                            |                                    | •               | nented bit, rea    |                 |              |

| u = Bit is uncha | anged                                                                                                         | x = Bit is unkn                                                                                                                                                                                                           |                                    | -n/n = Value a  | at POR and BC      | OR/Value at all | other Resets |

| '1' = Bit is set |                                                                                                               | '0' = Bit is clea                                                                                                                                                                                                         | ared                               |                 |                    |                 |              |

| bit 7            | If PLLEN in C<br>SPLLEN bit i                                                                                 |                                                                                                                                                                                                                           | ords = <u>1:</u><br>_L is always e | nabled (subject | t to oscillator re | equirements)    |              |

| bit 6-3          | 1111 = 16 M<br>1110 = 8 M<br>1101 = 4 M<br>1100 = 2 M<br>1011 = 1 M<br>1010 = 500<br>1001 = 250<br>1000 = 125 | Hz or 32 MHz H<br>Hz HF<br>Hz HF<br>kHz HF <sup>(1)</sup><br>kHz HF <sup>(1)</sup><br>kHz HF <sup>(1)</sup><br>kHz MF (defau<br>kHz MF<br>kHz MF<br>kHz MF<br>kHz MF<br>5 kHz MF<br>25 kHz HF <sup>(1)</sup><br>25 kHz MF | IF (see <b>Secti</b> e             | on 5.2.2.1 "HFI | NTOSC")            |                 |              |

| bit 2            | Unimplemer                                                                                                    | nted: Read as '                                                                                                                                                                                                           | )'                                 |                 |                    |                 |              |

| bit 1-0          | 1x = Internal<br>01 = Reserve                                                                                 | System Clock Se<br>oscillator block<br>ed<br>etermined by Fe                                                                                                                                                              |                                    | Configuration W | Vords.             |                 |              |

| Note 1: Dup      | licate frequen                                                                                                | cv derived from                                                                                                                                                                                                           | HFINTOSC.                          |                 |                    |                 |              |

### REGISTER 5-1: OSCCON: OSCILLATOR CONTROL REGISTER

# 6.3 Register Definitions: BOR Control

# REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-Out Reset Enable bit                                          |

|---------|--------------------------------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words = 01:                                          |

|         | 1 = BOR Enabled                                                                      |

|         | 0 = BOR Disabled                                                                     |

|         | If BOREN <1:0> in Configuration Words <u>≠ 01</u> :                                  |

|         | SBOREN is read/write, but has no effect on the BOR                                   |

| bit 6   | BORFS: Brown-Out Reset Fast Start bit <sup>(1)</sup>                                 |

|         | If BOREN <1:0> = 10 (Disabled in Sleep) or BOREN<1:0> = 01 (Under software control): |

|         | 1 = Band gap is forced on always (covers sleep/wake-up/operating cases)              |

|         | 0 = Band gap operates normally, and may turn off                                     |

|         | <u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u>    |

|         | BORFS is Read/Write, but has no effect.                                              |

| bit 5-1 | Unimplemented: Read as '0'                                                           |

| bit 0   | BORRDY: Brown-Out Reset Circuit Ready Status bit                                     |

|         | 1 = The Brown-out Reset circuit is active                                            |

|         | 0 = The Brown-out Reset circuit is inactive                                          |

| Note di | DODEN 41/02 hits are leasted in Canfiguration Wards                                  |

#### **Note 1:** BOREN<1:0> bits are located in Configuration Words.

| U-0             | R/W-0/0            | R/W-0/0           | U-0             | U-0                                | U-0            | U-0              | U-0         |  |  |  |

|-----------------|--------------------|-------------------|-----------------|------------------------------------|----------------|------------------|-------------|--|--|--|

|                 | C2IE               | C1IE              | —               | —                                  | —              |                  | —           |  |  |  |

| bit 7           |                    |                   |                 |                                    |                |                  | bit 0       |  |  |  |

|                 |                    |                   |                 |                                    |                |                  |             |  |  |  |

| Legend:         |                    |                   |                 |                                    |                |                  |             |  |  |  |

| R = Readab      | le bit             | W = Writable      | bit             | U = Unimplemented bit, read as '0' |                |                  |             |  |  |  |

| u = Bit is un   | changed            | x = Bit is unkr   | nown            | -n/n = Value                       | at POR and BOI | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is se | et                 | '0' = Bit is clea | ared            |                                    |                |                  |             |  |  |  |

|                 |                    |                   |                 |                                    |                |                  |             |  |  |  |

| bit 7           | Unimplemen         | ted: Read as '    | כ'              |                                    |                |                  |             |  |  |  |

| bit 6           | C2IE: Compa        | rator C2 Interru  | upt Enable bit  |                                    |                |                  |             |  |  |  |

|                 |                    | the Comparato     |                 |                                    |                |                  |             |  |  |  |

|                 | 0 = Disables       | the Comparato     | or C2 interrupt |                                    |                |                  |             |  |  |  |

| bit 5           | C1IE: Compa        | rator C1 Interru  | upt Enable bit  |                                    |                |                  |             |  |  |  |

|                 |                    | the Comparato     |                 |                                    |                |                  |             |  |  |  |

|                 | 0 = Disables       | the Comparato     | or C1 interrupt |                                    |                |                  |             |  |  |  |

| bit 4-0         | Unimplemen         | ted: Read as '    | כ'              |                                    |                |                  |             |  |  |  |

|                 |                    |                   |                 |                                    |                |                  |             |  |  |  |

| Note: E         | Bit PEIE of the IN | TCON register     | must be         |                                    |                |                  |             |  |  |  |

|                 | et to enable any p | •                 |                 |                                    |                |                  |             |  |  |  |

# REGISTER 7-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

© 2016 Microchip Technology Inc.

| U-0            | U-0                                                              | R/W-1/1                              | R/W-1/1 | U-0                                                  | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |

|----------------|------------------------------------------------------------------|--------------------------------------|---------|------------------------------------------------------|---------|---------|---------|--|

| _              | —                                                                | SLRA5                                | SLRA4   | —                                                    | SLRA2   | SLRA1   | SLRA0   |  |

| bit 7          |                                                                  |                                      |         |                                                      |         |         | bit 0   |  |

| Legend:        |                                                                  |                                      |         |                                                      |         |         |         |  |

| •              | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                      |         |                                                      |         |         |         |  |

| u = Bit is ur  | Bit is unchanged x = Bit is unknown                              |                                      | nown    | -n/n = Value at POR and BOR/Value at all other Reset |         |         |         |  |

| '1' = Bit is s | set                                                              | '0' = Bit is cle                     | ared    |                                                      |         |         |         |  |

|                |                                                                  |                                      |         |                                                      |         |         |         |  |

| bit 7-6        | Unimplemen                                                       | ited: Read as '                      | 0'      |                                                      |         |         |         |  |

| bit 5-4        |                                                                  | PORTA Slew F                         |         | its                                                  |         |         |         |  |

|                |                                                                  | pins, respectiv                      | •       |                                                      |         |         |         |  |

|                | •                                                                | slew rate is limit<br>slews at maxim |         |                                                      |         |         |         |  |

| bit 3          |                                                                  | ited: Read as '                      |         |                                                      |         |         |         |  |

| bit 2-0        | -                                                                | PORTA Slew F                         |         | its                                                  |         |         |         |  |

|                |                                                                  | pins, respectiv                      |         |                                                      |         |         |         |  |

|                | 1 = Port pin s                                                   | slew rate is limit                   | ed      |                                                      |         |         |         |  |

|                | 0 = Port pin s                                                   | lews at maxim                        | um rate |                                                      |         |         |         |  |

|                |                                                                  |                                      |         |                                                      |         |         |         |  |

# REGISTER 11-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

# REGISTER 11-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1                | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|------------------------|---------|---------|---------|

| —     | —   | INLVLA5 | INLVLA4 | INLVLA3 <sup>(1)</sup> | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7 |     |         |         |                        |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 5-0

INLVLA<5:0>: PORTA Input Level Select bits

- For RA<5:0> pins, respectively

- 1 = ST input used for port reads and interrupt-on-change

0 = TTL input used for port reads and interrupt-on-change

**Note 1:** The INLVLA3 bit selects the input type on this pin only when the MCLR function is not selected. When the MCLR function is selected, the input type for this pin will be ST.

# 11.4 Register Definitions: PORTB

### REGISTER 11-9: PORTB: PORTB REGISTER

| R/W-x/u            | R/W-x/u                   | R/W-x/u           | R/W-x/u        | U-0                                                   | U-0 | U-0 | U-0   |  |

|--------------------|---------------------------|-------------------|----------------|-------------------------------------------------------|-----|-----|-------|--|

| RB7                | RB6                       | RB5               | RB4            |                                                       | _   | _   |       |  |

|                    | IND0                      | RB5               | 1104           | _                                                     |     |     |       |  |

| bit 7              |                           |                   |                |                                                       |     |     | bit ( |  |

|                    |                           |                   |                |                                                       |     |     |       |  |

| Legend:            |                           |                   |                |                                                       |     |     |       |  |

| R = Readable bit W |                           | W = Writable bit  |                | U = Unimplemented bit, read as '0'                    |     |     |       |  |

| u = Bit is un      | changed                   | x = Bit is unkne  | own            | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |

| '1' = Bit is se    | et                        | '0' = Bit is clea | red            |                                                       |     |     |       |  |

|                    |                           |                   |                |                                                       |     |     |       |  |

| bit 7-4            | <b>RB&lt;7:4&gt;</b> : PO | RTB General Pu    | irpose I/O Pin | bits <sup>(1)</sup>                                   |     |     |       |  |

|                    | 1 = Port pin is           | <u>&gt;</u> Vін   |                |                                                       |     |     |       |  |

|                    | 0 = Port pin is           | <u>&lt;</u> VIL   |                |                                                       |     |     |       |  |

| hit 3_0            | Unimplement               | tod. Bead as '0'  |                |                                                       |     |     |       |  |

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

### REGISTER 11-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | TRISB<7:4>: PORTB Tri-State Control bits          |

|---------|---------------------------------------------------|

|         | 1 = PORTB pin configured as an input (tri-stated) |

|         | 0 = PORTB pin configured as an output             |

|         |                                                   |

bit 3-0 Unimplemented: Read as '0'

### REGISTER 11-11: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| LATB7   | LATB6   | LATB5   | LATB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 LATB<7:4>: PORTB Output Latch Value bits<sup>(1)</sup>

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

| REGISTER 13-4: | IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER <sup>(1)</sup> |

|----------------|------------------------------------------------------------------------|

|----------------|------------------------------------------------------------------------|

| R/W-0/0                               | R/W-0/0 | R/W-0/0           | R/W-0/0 | U-0                                | U-0            | U-0                 | U-0   |  |  |

|---------------------------------------|---------|-------------------|---------|------------------------------------|----------------|---------------------|-------|--|--|

| IOCBP7                                | IOCBP6  | IOCBP5            | IOCBP4  | _                                  | —              | —                   | —     |  |  |

| bit 7                                 |         |                   |         |                                    |                |                     | bit 0 |  |  |

|                                       |         |                   |         |                                    |                |                     |       |  |  |

| Legend:                               |         |                   |         |                                    |                |                     |       |  |  |

| R = Readable bi                       | t       | W = Writable bit  | :       | U = Unimplemented bit, read as '0' |                |                     |       |  |  |

| u = Bit is unchar                     | nged    | x = Bit is unknow | wn      | -n/n = Value at                    | POR and BOR/Va | lue at all other Re | esets |  |  |

| '1' = Bit is set '0' = Bit is cleared |         |                   |         |                                    |                |                     |       |  |  |

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

### REGISTER 13-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER<sup>(1)</sup>

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 |

|-------------|---------|---------|---------|-----|-----|-----|-----|

| IOCBN7      | IOCBN6  | IOCBN5  | IOCBN4  | —   | _   | _   | —   |

| bit 7 bit 0 |         |         |         |     |     |     |     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 **IOCBN<7:4>**: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

- bit 3-0 Unimplemented: Read as '0'

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

### REGISTER 13-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER<sup>(1)</sup>

| R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0   |

|------------|------------|------------|------------|-----|-----|-----|-------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | —   | —   | —   | —     |

| bit 7      | -          |            |            |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | IOCBF<7:4>: Interrupt-on-Change PORTB Flag bits                                                      |

|---------|------------------------------------------------------------------------------------------------------|

|         | 1 = An enabled change was detected on the associated pin.                                            |

|         | Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was |

|         | detected on RBx.                                                                                     |

|         | 0 = No change was detected, or the user cleared the detected change.                                 |

|         |                                                                                                      |

bit 3-0 Unimplemented: Read as '0'

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

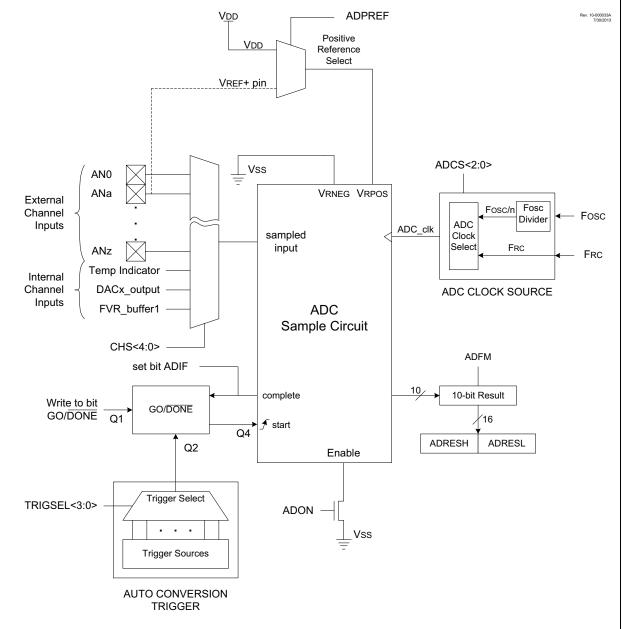

# 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC. The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

| ADC Clock Period (TAD) |               | Device Frequency (Fosc) |            |            |            |            |  |

|------------------------|---------------|-------------------------|------------|------------|------------|------------|--|

| ADC<br>Clock<br>Source | ADCS<2:0<br>> | 20 MHz                  | 16 MHz     | 8 MHz      | 4 MHz      | 1 MHz      |  |

| Fosc/2                 | 000           | 100 ns                  | 125 ns     | 250 ns     | 500 ns     | 2.0 μs     |  |

| Fosc/4                 | 100           | 200 ns                  | 250 ns     | 500 ns     | 1.0 μs     | 4.0 μs     |  |

| Fosc/8                 | 001           | 400 ns                  | 500 ns     | 1.0 μs     | 2.0 μs     | 8.0 μs     |  |

| Fosc/16                | 101           | 800 ns                  | 1.0 μs     | 2.0 μs     | 4.0 μs     | 16.0 μs    |  |

| Fosc/32                | 010           | 1.6 μs                  | 2.0 μs     | 4.0 μs     | 8.0 μs     | 32.0 μs    |  |

| Fosc/64                | 110           | 3.2 μs                  | 4.0 μs     | 8.0 μs     | 16.0 μs    | 64.0 μs    |  |

| FRC                    | x11           | 1.0-6.0 μs              | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs |  |

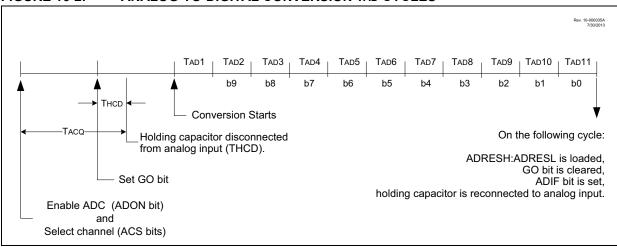

### TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range, (see TAD parameter). The TAD period when using the FOSC-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

### FIGURE 16-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

# 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACxCON1 register.

The DAC output voltage can be determined by using Equation 17-1.

# 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 27-16.

# 17.3 DAC Voltage Reference Output

The unbuffered DAC voltage can be output to the DACxOUTn pin(s) by setting the respective DACOEn bit(s) of the DACxCON0 register. Selecting the DAC reference voltage for output on either DACxOUTn pin automatically overrides the digital output buffer, the weak pull-up and digital input threshold detector functions of that pin.

Reading the DACxOUTn pin when it has been configured for DAC reference voltage output will always return a '0'.

**Note:** The unbuffered DAC output (DACxOUTn) is not intended to drive an external load.

# 17.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACxCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 17.5 Effects of a Reset

A device Reset affects the following:

- DACx is disabled.

- DACx output voltage is removed from the DACxOUTn pin(s).

- The DACR<4:0> range select bits are cleared.

### EQUATION 17-1: DAC OUTPUT VOLTAGE

### <u>IF DACEN = 1</u>

$$DACx\_output = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE-$$

**Note:** See the DACxCON0 register for the available VSOURCE+ and VSOURCE- selections.

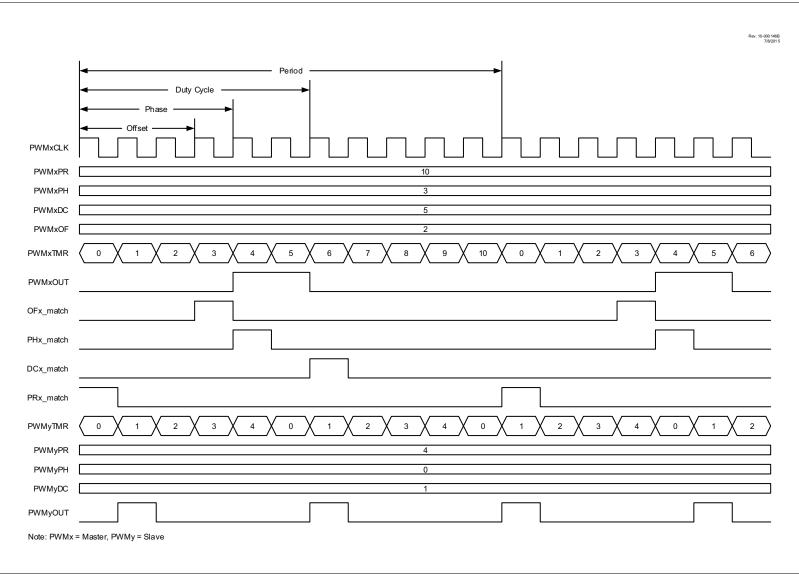

### FIGURE 23-8: INDEPENDENT RUN MODE TIMING DIAGRAM

PIC16(L)F1574/5/8/9

# TABLE 27-5: MEMORY PROGRAMMING SPECIFICATIONS

| Param.<br>No. | Sym.   | Characteristic                               | Min.   | Тур† | Max.   | Units | Conditions                                                           |

|---------------|--------|----------------------------------------------|--------|------|--------|-------|----------------------------------------------------------------------|

|               |        | Program Memory<br>Programming Specifications |        |      |        |       |                                                                      |

| D110          | VIHH   | Voltage on MCLR/VPP pin                      | 8.0    |      | 9.0    | V     | (Note 2)                                                             |

| D111          | IDDP   | Supply Current during<br>Programming         | _      | —    | 10     | mA    |                                                                      |

| D112          | VBE    | VDD for Bulk Erase                           | 2.7    |      | VDDMAX | V     |                                                                      |

| D113          | VPEW   | VDD for Write or Row Erase                   | VDDMIN |      | VDDMAX | V     |                                                                      |

| D114          | IPPPGM | Current on MCLR/VPP during<br>Erase/Write    | -      | 1.0  | —      | mA    |                                                                      |

| D115          | IDDPGM | Current on VDD during<br>Erase/Write         | —      | 5.0  | —      | mA    |                                                                      |

|               |        | Program Flash Memory                         |        |      |        |       |                                                                      |

| D121          | Eр     | Cell Endurance                               | 10K    | —    | —      | E/W   | -40°C ≤ TA ≤ +85°C<br>(Note 1)                                       |

| D122          | Vprw   | VDD for Read/Write                           | VDDMIN | —    | VDDMAX | V     |                                                                      |

| D123          | Tiw    | Self-timed Write Cycle Time                  | _      | 2    | 2.5    | ms    |                                                                      |

| D124          | TRETD  | Characteristic Retention                     | —      | 40   | _      | Year  | Provided no other specifications are violated                        |

| D125          | EHEFC  | High-Endurance Flash Cell                    | 100K   | _    | —      | E/W   | $0^{\circ}C \le TA \le +60^{\circ}C$ , lower byte last 128 addresses |

### Standard Operating Conditions (unless otherwise stated)

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Self-write and Block Erase.

**2**: Required only if single-supply programming is disabled.

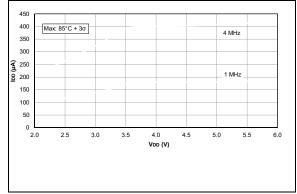

FIGURE 28-7: IDD Typical, EC Oscillator, Medium Power Mode, PIC16F1574/5/8/9 Only.

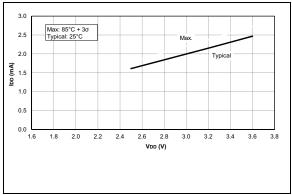

FIGURE 28-8: IDD Maximum, EC Oscillator, Medium Power Mode, PIC16F1574/5/8/9 Only.

FIGURE 28-9: IDD Typical, EC Oscillator, High-Power Mode, Fosc = 32 kHz, PIC16LF1574/5/8/9 Only.

**FIGURE 28-10:** IDD Typical, EC Oscillator, High-Power Mode, Fosc = 32 kHz, PIC16F1574/5/8/9 Only.

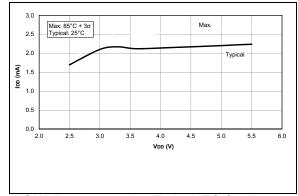

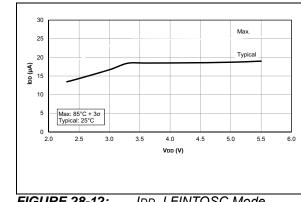

FIGURE 28-12: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16F1574/5/8/9 Only.

12 (**V**rl) 10 8 Typical 4 2 0 3.4 3.6 1.8 2.0 2.2 2.4 2.6 2.8 3.0 3.2 3.8 1.6 VDD (V) FIGURE 28-11: IDD, LFINTOSC Mode,

Max.

Fosc = 31 kHz, PIC16LF1574/5/8/9 Only.

18

16

14

Max: 85°C + 3o Typical: 25°C

# 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |          |      |  |  |

|-------------------------|-------------|-----------|----------|------|--|--|

| Dimension               | MIN         | NOM       | MAX      |      |  |  |

| Number of Terminals     | N           | 20        |          |      |  |  |

| Pitch                   | е           |           | 0.50 BSC |      |  |  |

| Overall Height          | Α           | 0.45      | 0.50     | 0.55 |  |  |

| Standoff                | A1          | 0.00      | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.127 REF |          |      |  |  |

| Overall Width           | E           | 4.00 BSC  |          |      |  |  |

| Exposed Pad Width       | E2          | 2.60      | 2.70     | 2.80 |  |  |

| Overall Length          | D           | 4.00 BSC  |          |      |  |  |

| Exposed Pad Length      | D2          | 2.60      | 2.70     | 2.80 |  |  |

| Terminal Width          | b           | 0.20      | 0.25     | 0.30 |  |  |

| Terminal Length         | L           | 0.30      | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | K           | 0.20      | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-255A Sheet 2 of 2

# APPENDIX A: DATA SHEET REVISION HISTORY

# **Revision A (2/2015)**

Initial release of this document.

# **Revision B (09/2015)**

Added Section 5.4: Clock Switching Before Sleep.

Updated Low-Power Features and Memory sections on cover page.

Updated Examples 3-2 and 16-1; Figures 8-1, 22-1, and 23-8 through 23-13; Registers 8-1, 23-6, 24-2, and 24-3; Sections 8.2.2, 16.2.6, 22.0, 23.3.3, 24.9.1.2, 24.11.1 and 27.1; and Tables 27-1, 27-2, 27-3, 27-8 and 27-11.

# **Revision C (01/2016)**

Added graphs to chapter "DC and AC Characteristics Graphs and Charts". Other minor corrections.