# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | LINbus, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1578-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Analog Peripherals**

- 10-Bit Analog-to-Digital Converter (ADC):

- Up to 12 external channels

- Conversion available during Sleep

- Two Comparators:

- Low-Power/High-Speed modes

- Fixed Voltage Reference at (non)inverting input(s)

- Comparator outputs externally accessible

- Synchronization with Timer1 clock source

- Software hysteresis enable

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- Voltage Reference:

TABLE 1:

- Fixed Voltage Reference with 1.024V, 2.048V and 4.096V output levels

# **Clocking Structure**

- Precision Internal Oscillator:

- Factory calibrated ±1%, typical

- Software-selectable clock speeds from 31 kHz to 32 MHz

- · External Oscillator Block with:

- Two external clock modes up to 32 MHz

- Digital Oscillator Input Available

Program Flash Memory Memory 8-Bit/16-Bit Timers SRAM (bytes) Data Sheet Index I0-Bit ADC (ch) Comparators **I6-Bit PWM** Bit DAC Debug<sup>(1)</sup> (Kwords) Pins (Kbytes) EUSART Program Flash CWG PPS Device <u>0</u> Data PIC12(L)F1571 1.75 2/4(2) 128 6 1 3 4 1 1 0 Ν Ι (A) 1 2/4(2) PIC12(L)F1572 (A) 2 3.5 256 6 1 3 4 1 1 1 Ν L 2/5(3)PIC16(L)F1574 12 2 (B) 4 7 512 4 8 1 1 1 Y Т 2/5(3) PIC16(L)F1575 8 14 1024 12 2 4 8 1 1 1 Y I (B) 2/5<sup>(3)</sup> PIC16(L)F1578 (B) 4 7 512 18 2 4 12 1 1 1 Y L 2/5(3) PIC16(L)F1579 8 14 18 2 12 1 Y (B) 1024 4 1 1 Т

**Note 1:** I – Debugging integrated on chip.

2: Three additional 16-bit timers available when not using the 16-bit PWM outputs.

PIC12(L)F1571/2 AND PIC16(L)F1574/5/8/9 FAMILY TYPES

3: Four additional 16-bit timers available when not using the 16-bit PWM outputs.

#### **Data Sheet Index:**

- A) DS-40001723 PIC12(L)F1571/2 Data Sheet, 8-Pin Flash, 8-bit MCU with High-Precision 16-bit PWM

- B) Future Release PIC16(L)F1574/5/8/9 Data Sheet, 8-Pin Flash, 8-bit MCU with High-Precision 16-bit PWM

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

## 1.1 Register and Bit Naming Conventions

#### 1.1.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.1.2 BIT NAMES

There are two variants for bit names:

- Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

#### 1.1.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is *RegisterName*bits.*ShortName*. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

#### 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

#### COG1CON0bits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

#### Example 1:

MOVLW ~(1<<G1MD1) ANDWF COG1CON0,F MOVLW 1<<G1MD2 | 1<<G1MD0 IORWF COG1CON0,F

#### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

#### 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

#### 1.1.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

#### 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

|    |      | BANK5          |      | BANK6          |      | BANK7          |

|----|------|----------------|------|----------------|------|----------------|

|    | 280h |                | 300h |                | 380h |                |

| rs |      | Core Registers |      | Core Registers |      | Core Registers |

|    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |

|    | 28Bh |                | 30Bh |                | 38Bh |                |

|    | 28Ch | ODCONA         | 30Ch | SLRCONA        | 38Ch | INLVLA         |

|    | 28Dh | _              | 30Dh | _              | 38Dh | _              |

|    | 28Eh | ODCONC         | 30Eh | SLRCONC        | 38Eh | INLVLC         |

|    | 28Fh | _              | 30Fh | _              | 38Fh | _              |

|    | 290h | _              | 310h | _              | 390h | _              |

|    | 291h | _              | 311h | _              | 391h | IOCAP          |

|    | 292h | _              | 312h | _              | 392h | IOCAN          |

|    | 293h | _              | 313h | _              | 393h | IOCAF          |

|    | 294h | _              | 314h | _              | 394h | _              |

|    | 295h | _              | 315h | _              | 395h | _              |

|    | 296h | _              | 316h | _              | 396h | _              |

|    | 297h | _              | 317h | _              | 397h | IOCCP          |

|    | 298h |                | 318h | _              | 398h | IOCCN          |

|    | 299h | _              | 319h | _              | 399h | IOCCF          |

|    | 29Ah | _              | 31Ah | _              | 39Ah | _              |

|    | 29Bh | _              | 31Bh | _              | 39Bh | _              |

|    | 29Ch |                | 31Ch |                | 39Ch | _              |

|    | 29Dh | _              | 31Dh | _              | 39Dh | _              |

|    | 20Fh |                | 2456 |                | 2056 |                |

\_

General Purpose Register 80 Bytes

Accesses 70h – 7Fh

#### TABLE 3-4: PIC16(L)F1575 MEMORY MAP, BANKS 0-7 BANK0 BANK1

BANK2

| 000h |                                            | 080h |                                            | 100h |                                            | 180h |                                            | 200h |                                            | 280h |                                            | 300h |                                            | 380h |   |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|---|

|      | Core Registers                             |      | C |

|      | (Table 3-2)                                |      |   |

| 00Bh |                                            | 08Bh |                                            | 10Bh |                                            | 18Bh |                                            | 20Bh |                                            | 28Bh |                                            | 30Bh |                                            | 38Bh |   |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                                     | 20Ch | WPUA                                       | 28Ch | ODCONA                                     | 30Ch | SLRCONA                                    | 38Ch |   |

| 00Dh | —                                          | 08Dh | —                                          | 10Dh | —                                          | 18Dh | _                                          | 20Dh | _                                          | 28Dh | _                                          | 30Dh | —                                          | 38Dh |   |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | ANSELC                                     | 20Eh | WPUC                                       | 28Eh | ODCONC                                     | 30Eh | SLRCONC                                    | 38Eh |   |

| 00Fh | —                                          | 08Fh | —                                          | 10Fh | —                                          | 18Fh |                                            | 20Fh | _                                          | 28Fh | —                                          | 30Fh | —                                          | 38Fh |   |

| 010h | —                                          | 090h | —                                          | 110h | —                                          | 190h | —                                          | 210h | —                                          | 290h | _                                          | 310h | —                                          | 390h |   |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | CM1CON0                                    | 191h | PMADRL                                     | 211h | —                                          | 291h | _                                          | 311h | —                                          | 391h |   |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | CM1CON1                                    | 192h | PMADRH                                     | 212h | —                                          | 292h | _                                          | 312h | —                                          | 392h |   |

| 013h | PIR3                                       | 093h | PIE3                                       | 113h | CM2CON0                                    | 193h | PMDATL                                     | 213h | _                                          | 293h | —                                          | 313h | —                                          | 393h |   |

| 014h | —                                          | 094h | —                                          | 114h | CM2CON1                                    | 194h | PMDATH                                     | 214h | _                                          | 294h | —                                          | 314h | —                                          | 394h |   |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h | CMOUT                                      | 195h | PMCON1                                     | 215h | _                                          | 295h | —                                          | 315h | —                                          | 395h |   |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | BORCON                                     | 196h | PMCON2                                     | 216h | _                                          | 296h | —                                          | 316h | —                                          | 396h |   |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | VREGCON <sup>(1)</sup>                     | 217h | —                                          | 297h | —                                          | 317h | —                                          | 397h |   |

| 018h | T1CON                                      | 098h | OSCTUNE                                    | 118h | DACCON0                                    | 198h | —                                          | 218h | —                                          | 298h | —                                          | 318h | _                                          | 398h |   |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | DACCON1                                    | 199h | RCREG                                      | 219h | —                                          | 299h | _                                          | 319h | _                                          | 399h |   |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah | —                                          | 19Ah | TXREG                                      | 21Ah | —                                          | 29Ah | —                                          | 31Ah | —                                          | 39Ah |   |

| 01Bh | PR2                                        | 09Bh | ADRESL                                     | 11Bh | —                                          | 19Bh | SPBRGL                                     | 21Bh | —                                          | 29Bh | —                                          | 31Bh | —                                          | 39Bh |   |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch | —                                          | 19Ch | SPBRGH                                     | 21Ch | _                                          | 29Ch | —                                          | 31Ch | _                                          | 39Ch |   |

| 01Dh | —                                          | 09Dh | ADCON0                                     | 11Dh | —                                          | 19Dh | RCSTA                                      | 21Dh | _                                          | 29Dh | _                                          | 31Dh | —                                          | 39Dh |   |

| 01Eh | —                                          | 09Eh | ADCON1                                     | 11Eh | —                                          | 19Eh | TXSTA                                      | 21Eh | _                                          | 29Eh | —                                          | 31Eh | —                                          | 39Eh |   |

| 01Fh | —                                          | 09Fh | ADCON2                                     | 11Fh | —                                          | 19Fh | BAUDCON                                    | 21Fh | —                                          | 29Fh | —                                          | 31Fh | —                                          | 39Fh |   |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h |                                            | 3A0h |   |

|      | General<br>Purpose<br>Register<br>80 Bytes |      |   |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                            | 3EFh |   |

| 070h |                                            | 0F0h |                                            | 170h |                                            | 1F0h |                                            | 270h |                                            | 2F0h |                                            | 370h |                                            | 3F0h |   |

|      | Common RAM                                 |      | Accesses<br>70h – 7Fh                      |      |   |

| 07Fh |                                            | 0FFh |                                            | 17Fh |                                            | 1FFh |                                            | 27Fh |                                            | 2FFh |                                            | 37Fh |                                            | 3FFh |   |

|      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |   |

BANK3

BANK4

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1575.

DS40001782C-page 26

# TABLE 3-5: PIC16(L)F1578 MEMORY MAP, BANKS 0-7

|       | BANK0                         |        | ,<br>BANK1                    |      | BANK2                         |      | BANK3                         |       | BANK4                         |        | BANK5                         |                      | BANK6                                      |        | BANK7                         |

|-------|-------------------------------|--------|-------------------------------|------|-------------------------------|------|-------------------------------|-------|-------------------------------|--------|-------------------------------|----------------------|--------------------------------------------|--------|-------------------------------|

| 000h  | Core Registers<br>(Table 3-2) | 080h   | Core Registers<br>(Table 3-2) | 100h | Core Registers<br>(Table 3-2) | 180h | Core Registers<br>(Table 3-2) | 200h  | Core Registers<br>(Table 3-2) | 280h   | Core Registers<br>(Table 3-2) | 300h                 | Core Registers<br>(Table 3-2)              | 380h   | Core Registers<br>(Table 3-2) |

| 00Bh  |                               | 08Bh   |                               | 10Bh |                               | 18Bh |                               | 20Bh  |                               | 28Bh   |                               | 30Bh                 |                                            | 38Bh   |                               |

| 00Ch  | PORTA                         | 08Ch   | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch  | WPUA                          | 28Ch   | ODCONA                        | 30Ch                 | SLRCONA                                    | 38Ch   | INLVLA                        |

| 00Dh  | PORTB                         | 08Dh   | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh  | WPUB                          | 28Dh   | ODCONB                        | 30Dh                 | SLRCONB                                    | 38Dh   | INLVLB                        |

| 00Eh  | PORTC                         | 08Eh   | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh  | WPUC                          | 28Eh   | ODCONC                        | 30Eh                 | SLRCONC                                    | 38Eh   | INLVLC                        |

| 00Fh  | _                             | 08Fh   | -                             | 10Fh | _                             | 18Fh | _                             | 20Fh  | _                             | 28Fh   | _                             | 30Fh                 | _                                          | 38Fh   | —                             |

| 010h  | _                             | 090h   | -                             | 110h | _                             | 190h | _                             | 210h  | _                             | 290h   | _                             | 310h                 | _                                          | 390h   | —                             |

| 011h  | PIR1                          | 091h   | PIE1                          | 111h | CM1CON0                       | 191h | PMADRL                        | 211h  | —                             | 291h   | —                             | 311h                 | —                                          | 391h   | IOCAP                         |

| 012h  | PIR2                          | 092h   | PIE2                          | 112h | CM1CON1                       | 192h | PMADRH                        | 212h  | —                             | 292h   | —                             | 312h                 | —                                          | 392h   | IOCAN                         |

| 013h  | PIR3                          | 093h   | PIE3                          | 113h | CM2CON0                       | 193h | PMDATL                        | 213h  | _                             | 293h   | _                             | 313h                 | —                                          | 393h   | IOCAF                         |

| 014h  | —                             | 094h   | —                             | 114h | CM2CON1                       | 194h | PMDATH                        | 214h  | _                             | 294h   | _                             | 314h                 | —                                          | 394h   | IOCBP                         |

| 015h  | TMR0                          | 095h   | OPTION_REG                    | 115h | CMOUT                         | 195h | PMCON1                        | 215h  | _                             | 295h   | _                             | 315h                 | —                                          | 395h   | IOCBN                         |

| 016h  | TMR1L                         | 096h   | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h  | _                             | 296h   | _                             | 316h                 |                                            | 396h   | IOCBF                         |

| 017h  | TMR1H                         | 097h   | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(1)</sup>        | 217h  | _                             | 297h   | _                             | 317h                 | _                                          | 397h   | IOCCP                         |

| 018h  | T1CON                         | 098h   | OSCTUNE                       | 118h | DACCON0                       | 198h | —                             | 218h  | —                             | 298h   | —                             | 318h                 | —                                          | 398h   | IOCCN                         |

| 019h  | T1GCON                        | 099h   | OSCCON                        | 119h | DACCON1                       | 199h | RCREG                         | 219h  | _                             | 299h   | _                             | 319h                 | —                                          | 399h   | IOCCF                         |

| 01Ah  | TMR2                          | 09Ah   | OSCSTAT                       | 11Ah | —                             | 19Ah | TXREG                         | 21Ah  | —                             | 29Ah   | —                             | 31Ah                 |                                            | 39Ah   | —                             |

| 01Bh  | PR2                           | 09Bh   | ADRESL                        | 11Bh | —                             | 19Bh | SPBRGL                        | 21Bh  | —                             | 29Bh   | —                             | 31Bh                 |                                            | 39Bh   | —                             |

| 01Ch  | T2CON                         | 09Ch   | ADRESH                        | 11Ch | —                             | 19Ch | SPBRGH                        | 21Ch  | —                             | 29Ch   | —                             | 31Ch                 | _                                          | 39Ch   | —                             |

| 01Dh  | —                             | 09Dh   | ADCON0                        | 11Dh | —                             | 19Dh | RCSTA                         | 21Dh  | —                             | 29Dh   | —                             | 31Dh                 | —                                          | 39Dh   | —                             |

| 01Eh  |                               | 09Eh   | ADCON1                        | 11Eh | —                             | 19Eh | TXSTA                         | 21Eh  | _                             | 29Eh   | _                             | 31Eh                 |                                            | 39Eh   | —                             |

| 01Fh  | _                             | 09Fh   | ADCON2                        | 11Fh | _                             | 19Fh | BAUDCON                       | 21Fh  | _                             | 29Fh   | _                             | 31Fh                 | _                                          | 39Fh   | _                             |

| 020h  | General<br>Purpose            | 0A0h   | General<br>Purpose            | 120h | General<br>Purpose            | 1A0h | General<br>Purpose            | 220h  | General<br>Purpose            | 2A0h   | General<br>Purpose            | 320h<br>32Fh<br>330h | General<br>Purpose<br>Register<br>16 Bytes | 3A0h   | Unimplemented<br>Read as '0'  |

| 06Fh  | Register<br>80 Bytes          | 0EFh   | Register<br>80 Bytes          | 16Fh | Register<br>80 Bytes          | 1EFh | Register<br>80 Bytes          | 26Fh  | Register<br>80 Bytes          | 2EFh   | Register<br>80 Bytes          | 36Fh                 | Unimplemented<br>Read as '0'               | 3EFh   | Read as 0                     |

| 070h  |                               | 0F0h   |                               | 170h |                               | 1F0h |                               | 270h  |                               | 2F0h   |                               | 370h                 |                                            | 3F0h   |                               |

| 0.011 | Common RAM                    | 5. 611 | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         | 2.011 | Accesses<br>70h – 7Fh         | 2. 011 | Accesses<br>70h – 7Fh         | 0.011                | Accesses<br>70h – 7Fh                      | 5. 0.1 | Accesses<br>70h – 7Fh         |

| 07Fh  |                               | 0FFh   |                               | 17Fh |                               | 1FFh |                               | 27Fh  |                               | 2FFh   |                               | 37Fh                 |                                            | 3FFh   |                               |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1578.

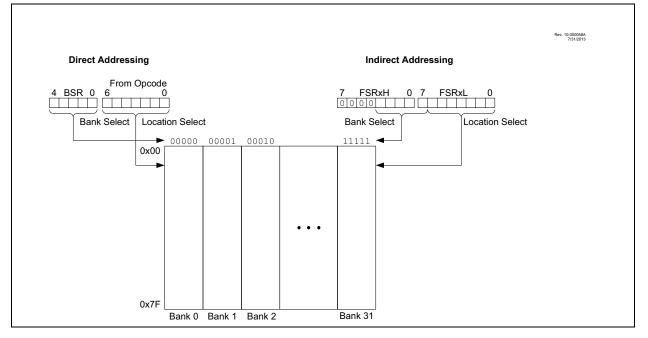

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

#### FIGURE 3-10: TRADITIONAL DATA MEMORY MAP

# PIC16(L)F1574/5/8/9

| FIGURE 5-3:            | INTERNAL OSCILLATOR SWITCH TIMING                              |

|------------------------|----------------------------------------------------------------|

| \$#\$KTO\$C            |                                                                |

| HFINTOSC/              | Craviliana Onlay <sup>(9)</sup> 2 cycle Syre. Running          |

| LFINTOSC               |                                                                |

| IRCF <3:0>             | $\neq 0$ $= 0$                                                 |

| System Clock           |                                                                |

| 88989709C              | LENYXXXX (WET enabled)                                         |

| HFINTOSC/<br>MENNECOSC |                                                                |

| LFINTOSC               |                                                                |

| IRCF <3:0>             | $\neq 0$ $\chi = 0$                                            |

| System Clock           |                                                                |

| SINTORC                | MFINYOSC/MFINYOSC<br>URINTOSO hims off unless WOT is enabled   |

| 1989090                |                                                                |

| HFRATOSO/<br>SAFINTOSO |                                                                |

|                        |                                                                |

| System Clock           |                                                                |

| Note () See            | Table 5-1, "Craditutor Switching Dalays" for more information. |

# 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to Section 8.0 "Power-Down Mode (Sleep)" for more details.

# 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

# 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|-------|--------|---------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE | TMR0IF | INTF    | IOCIF  | 86                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA   |        | PS<2:0> |        | 178                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | _     | _      | TMR2IE  | TMR1IE | 87                  |

| PIE2       | _       | C2IE   | C1IE   | _      | _     | _      | _       | _      | 88                  |

| PIE3       | PWM4IE  | PWM3IE | PWM2IE | PWM1IE | _     | _      | _       | _      | 89                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | _     | _      | TMR2IF  | TMR1IF | 90                  |

| PIR2       |         | C2IF   | C1IF   |        |       |        |         |        | 91                  |

| PIR3       | PWM4IF  | PWM3IF | PWM2IF | PWM1IF | _     | _      | _       | _      | 92                  |

TABLE 7-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

| U-1           | R/W-0/0             | R/W-0/0                                   | R/W/HC-0/0            | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0           | R/S/HC-0/0           | R/S/HC-0/0       |

|---------------|---------------------|-------------------------------------------|-----------------------|---------------------------|-------------------|----------------------|------------------|

| (1)           | CFGS                | LWLO <sup>(3)</sup>                       | FREE                  | WRERR                     | WREN              | WR                   | RD               |

| bit 7         |                     |                                           |                       |                           |                   |                      | bit (            |

| Legend:       |                     |                                           |                       |                           |                   |                      |                  |

| R = Reada     | able bit            | W = Writable b                            | it                    | U = Unimpleme             | nted bit, read as | s 'O'                |                  |

|               | n only be set       | x = Bit is unkno                          |                       | •                         | -                 | √alue at all other Ⅰ | Resets           |

| '1' = Bit is  | set                 | '0' = Bit is clea                         | red                   | HC = Bit is clear         |                   |                      |                  |

| <b>h</b> :+ 7 |                     | tod. Dood on (1)                          |                       |                           |                   |                      |                  |

| bit 7         | -                   | ted: Read as '1'                          |                       |                           |                   |                      |                  |

| bit 6         | •                   | guration Select bit<br>Configuration, Use |                       | ID Registers              |                   |                      |                  |

|               |                     | Flash program me                          |                       | ID Registers              |                   |                      |                  |

| bit 5         | LWLO: Load          | Write Latches On                          | ly bit <sup>(3)</sup> |                           |                   |                      |                  |

|               |                     | addressed progra                          | •                     | e latch is loaded/ι       | pdated on the     | next WR comman       | d                |

|               |                     | ressed program m                          | •                     | h is loaded/update        | ed and a write of | all program mem      | ory write latche |

|               |                     | itiated on the nex                        |                       |                           |                   |                      |                  |

| bit 4         | •                   | am Flash Erase E                          |                       |                           |                   |                      |                  |

|               |                     | s an erase operati<br>s an write operatio |                       |                           | rdware cleared    | upon completion)     |                  |

| bit 3         |                     | gram/Erase Error                          |                       |                           |                   |                      |                  |

|               |                     | n indicates an im                         |                       | or erase sequend          | e attempt or te   | rmination (bit is s  | et automatical   |

|               |                     | et attempt (write '                       | ,                     | ,                         |                   |                      |                  |

|               | 0 = The prog        | gram or erase ope                         | ration completed      | d normally.               |                   |                      |                  |

| bit 2         | •                   | am/Erase Enable                           |                       |                           |                   |                      |                  |

|               | •                   | rogram/erase cyc<br>programming/eras      |                       | lach                      |                   |                      |                  |

| bit 1         | WR: Write Co        | 0 0                                       | ing of program i      | 10311                     |                   |                      |                  |

|               |                     | a program Flash                           | orogram/erase o       | peration                  |                   |                      |                  |

|               |                     | ration is self-timed                      | 0                     | •                         | re once operatio  | on is complete.      |                  |

|               |                     | bit can only be se                        | , ,                   |                           |                   |                      |                  |

|               | 0 = Program         | /erase operation                          | to the Flash is co    | omplete and inact         | ive.              |                      |                  |

| bit 0         | RD: Read Co         |                                           |                       |                           |                   |                      |                  |

|               |                     | a program Flash r                         | ead. Read takes       | s one cycle. RD is        | cleared in hard   | lware. The RD bit    | can only be se   |

|               | •                   | red) in software.<br>t initiate a prograr | n Flash read.         |                           |                   |                      |                  |

| Note 1:       | Unimplemented bit   |                                           |                       |                           |                   |                      |                  |

| 2:            | The WRERR bit is    |                                           | by hardware whe       | en a program mer          | nory write or era | ase operation is st  | arted (WR = 1    |

| 3:            | The LWLO bit is igr | -                                         | -                     |                           | -                 | •                    |                  |

# REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

| ADC Clock              | Period (TAD) | Device Frequency (Fosc) |            |            |            |            |  |  |  |  |

|------------------------|--------------|-------------------------|------------|------------|------------|------------|--|--|--|--|

| ADC<br>Clock<br>Source |              | 20 MHz                  | 16 MHz     | 8 MHz      | 4 MHz      | 1 MHz      |  |  |  |  |

| Fosc/2                 | 000          | 100 ns                  | 125 ns     | 250 ns     | 500 ns     | 2.0 μs     |  |  |  |  |

| Fosc/4                 | 100          | 200 ns                  | 250 ns     | 500 ns     | 1.0 μs     | 4.0 μs     |  |  |  |  |

| Fosc/8                 | 001          | 400 ns                  | 500 ns     | 1.0 μs     | 2.0 μs     | 8.0 μs     |  |  |  |  |

| Fosc/16                | 101          | 800 ns                  | 1.0 μs     | 2.0 μs     | 4.0 μs     | 16.0 μs    |  |  |  |  |

| Fosc/32                | 010          | 1.6 μs                  | 2.0 μs     | 4.0 μs     | 8.0 μs     | 32.0 μs    |  |  |  |  |

| Fosc/64                | 110          | 3.2 μs                  | 4.0 μs     | 8.0 μs     | 16.0 μs    | 64.0 μs    |  |  |  |  |

| FRC                    | x11          | 1.0-6.0 μs              | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs |  |  |  |  |

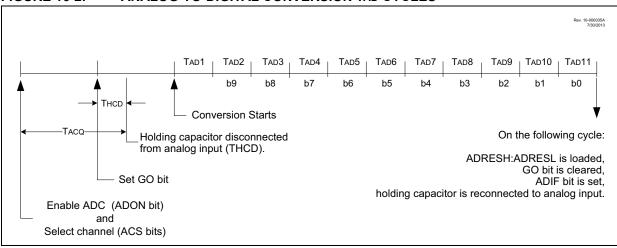

#### TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range, (see TAD parameter). The TAD period when using the FOSC-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

#### FIGURE 16-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 18.2.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 18-2 shows the output state versus input conditions, including polarity control.

TABLE 18-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 18.2.6 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the Normal Speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

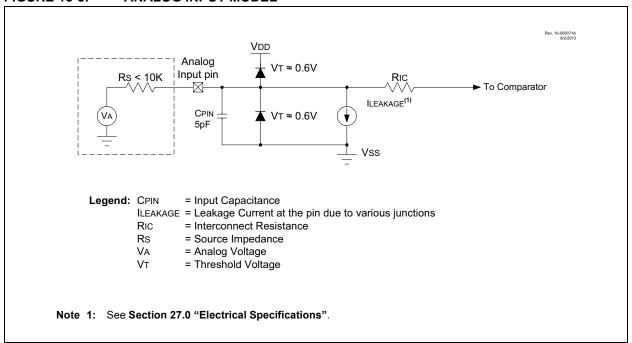

## 18.3 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward-biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

# 21.5 Register Definitions: Timer2 Control

| U-0               | R/W-0/0                    | R/W-0/0                                 | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0         | R/W-0/0      |

|-------------------|----------------------------|-----------------------------------------|-----------------|----------------|------------------|-----------------|--------------|

| —                 |                            | T2OUT                                   | PS<3:0>         |                | TMR2ON           | T2CKF           | PS<1:0>      |

| bit 7             |                            |                                         |                 |                |                  |                 | bit          |

|                   |                            |                                         |                 |                |                  |                 |              |

| Legend:           |                            |                                         |                 |                |                  |                 |              |

| R = Readable      | e bit                      | W = Writable                            | bit             | U = Unimple    | emented bit, rea | d as '0'        |              |

| u = Bit is unc    | hanged                     | x = Bit is unki                         | nown            | -n/n = Value   | at POR and BO    | OR/Value at all | other Resets |

| '1' = Bit is set  | :                          | '0' = Bit is cle                        | ared            |                |                  |                 |              |

| L:1 7             |                            | utada Daradara (                        | 01              |                |                  |                 |              |

| bit 7             | -                          | nted: Read as '                         |                 | v Coloct bito  |                  |                 |              |

| bit 6-3           | 0000 = 1:1                 | <b>3:0&gt;:</b> Timer2 Οι<br>Destacelor | ilput Posiscale | er Select bits |                  |                 |              |

|                   | 0000 = 1.11                |                                         |                 |                |                  |                 |              |

|                   | 0010 = 1:3                 |                                         |                 |                |                  |                 |              |

|                   | 0011 = <b>1</b> :4         |                                         |                 |                |                  |                 |              |

|                   | 0100 <b>= 1:5  </b>        | Postscaler                              |                 |                |                  |                 |              |

|                   | 0101 <b>= 1:6  </b>        | Postscaler                              |                 |                |                  |                 |              |

|                   | 0110 <b>= 1:7  </b>        |                                         |                 |                |                  |                 |              |

|                   | 0111 = 1:8                 |                                         |                 |                |                  |                 |              |

|                   | 1000 = 1:9 I               |                                         |                 |                |                  |                 |              |

|                   | 1001 = 1:10<br>1010 = 1:11 |                                         |                 |                |                  |                 |              |

|                   | 1010 = 1.11                |                                         |                 |                |                  |                 |              |

|                   | 1100 = 1.12                |                                         |                 |                |                  |                 |              |

|                   | 1101 = 1:14                |                                         |                 |                |                  |                 |              |

|                   | 1110 = 1:15                |                                         |                 |                |                  |                 |              |

|                   | 1111 <b>= 1:16</b>         | Postscaler                              |                 |                |                  |                 |              |

| bit 2             | TMR2ON: T                  | imer2 On bit                            |                 |                |                  |                 |              |

|                   | 1 = Timer2                 | is on                                   |                 |                |                  |                 |              |

|                   | 0 = Timer2                 | is off                                  |                 |                |                  |                 |              |

| bit 1-0           | T2CKPS<1:                  | 0>: Timer2 Cloc                         | k Prescale Se   | lect bits      |                  |                 |              |

|                   | 00 = Presca                | ller is 1                               |                 |                |                  |                 |              |

|                   | 01 = Presca                | ller is 4                               |                 |                |                  |                 |              |

|                   | 10 = Presca                | ller is 16                              |                 |                |                  |                 |              |

|                   | 11 = Presca                | ller is 64                              |                 |                |                  |                 |              |

| <b>TABLE 21-1</b> | : SUMMAF                   | RY OF REGIS                             | TERS ASSO       |                | TH TIMER2        |                 |              |

|                   |                            |                                         |                 |                |                  |                 |              |

# REGISTER 21-1: T2CON: TIMER2 CONTROL REGISTER

| Name   | Bit 7       | Bit 6           | Bit 5                           | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------------|-----------------|---------------------------------|-------|-------|--------|--------|--------|---------------------|

| INTCON | GIE         | PEIE            | TMR0IE                          | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1   | TMR1GIE     | ADIE            | RCIE                            | TXIE  | —     | _      | TMR2IE | TMR1IE | 87                  |

| PIR1   | TMR1GIF     | ADIF            | RCIF                            | TXIF  | —     | —      | TMR2IF | TMR1IF | 90                  |

| PR2    | Timer2 Modu | ule Period Re   | gister                          |       |       |        |        |        | 189*                |

| T2CON  | _           |                 | T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |       |       |        |        |        | 191                 |

| TMR2   | Holding Reg | ister for the 8 | -bit TMR2 Co                    | unt   |       |        |        |        | 189*                |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

Note 1: PIC16(L)F1575 only.

| TABLE 22-3: | <b>BAUD RATE FORMULAS</b> |

|-------------|---------------------------|

|-------------|---------------------------|

|      | Configuration Bi | ts   |                     | Baud Rate Formula |

|------|------------------|------|---------------------|-------------------|

| SYNC | BRG16            | BRGH | BRG/EUSART Mode     | Baud Kale Formula |

| 0    | 0                | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |

| 0    | 0                | 1    | 8-bit/Asynchronous  |                   |

| 0    | 1                | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |

| 0    | 1                | 1    | 16-bit/Asynchronous |                   |

| 1    | 0                | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |

| 1    | 1                | x    | 16-bit/Synchronous  |                   |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair.

| TABLE 22-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

| Name    | Bit 7     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|-----------|----------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUDCON | ABDOVF    | RCIDL    | _     | SCKP  | BRG16 |       | WUE   | ABDEN | 204                 |

| RCSTA   | SPEN      | RX9      | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 203                 |

| SPBRGL  |           | BRG<7:0> |       |       |       |       |       | 205*  |                     |

| SPBRGH  | BRG<15:8> |          |       |       |       | 205*  |       |       |                     |

| TXSTA   | CSRC      | TX9      | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 202                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

| U-0                                                                                                                                                                                       | U-0    | U-0               | U-0 | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|-----|-----------------|-------------------|------------------|-----------|

| _                                                                                                                                                                                         | _      | _                 | —   | OFIE            | PHIE              | DCIE             | PRIE      |

| bit 7                                                                                                                                                                                     |        |                   |     |                 |                   |                  | bit 0     |

| [                                                                                                                                                                                         |        |                   |     |                 |                   |                  |           |

| Legend:                                                                                                                                                                                   |        |                   |     |                 |                   |                  |           |

| R = Readable                                                                                                                                                                              | e bit  | W = Writable b    | it  | U = Unimpleme   | ented bit, read a | is '0'           |           |

| u = Bit is unc                                                                                                                                                                            | hanged | x = Bit is unkno  | own | -n/n = Value at | POR and BOR       | Value at all oth | er Resets |

| '1' = Bit is set                                                                                                                                                                          | t      | '0' = Bit is clea | red |                 |                   |                  |           |

| bit 7-4       Unimplemented: Read as '0'         bit 3       OFIE: Offset Interrupt Enable bit         1 = Interrupt CPU on Offset Match         0 = Do not interrupt CPU on Offset Match |        |                   |     |                 |                   |                  |           |

| bit 2 PHIE: Phase Interrupt Enable bit<br>1 = Interrupt CPU on Phase Match<br>0 = Do not Interrupt CPU on Phase Match                                                                     |        |                   |     |                 |                   |                  |           |

| bit 1 DCIE: Duty Cycle Interrupt Enable bit<br>1 = Interrupt CPU on Duty Cycle Match<br>0 = Do not interrupt CPU on Duty Cycle Match                                                      |        |                   | h   |                 |                   |                  |           |

| bit 0 PRIE: Period Interrupt Enable bit<br>1 = Interrupt CPU on Period Match<br>0 = Do not interrupt CPU on Period Match                                                                  |        |                   |     |                 |                   |                  |           |

# **REGISTER 23-2: PWMxINTE: PWM INTERRUPT ENABLE REGISTER**

#### REGISTER 23-3: PWMxINTF: PWM INTERRUPT REQUEST REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|------------|------------|------------|------------|

|       |     | _   | _   | OFIF       | PHIF       | DCIF       | PRIF       |

| bit 7 | •   |     |     | •          | •          |            | bit 0      |

| Legend:                     |                      |                                                       |

|-----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by hard | dware                | HS = Bit is set by hardware                           |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged        | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set            | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                                           |

|---------|----------------------------------------------------------------------|

| bit 3   | OFIF: Offset Interrupt Flag bit <sup>(1)</sup>                       |

|         | 1 = Offset Match Event occurred                                      |

|         | 0 = Offset Match Event did not occur                                 |

| bit 2   | PHIF: Phase Interrupt Flag bit <sup>(1)</sup>                        |

|         | 1 = Phase Match Event occurred                                       |

|         | 0 = Phase Match Event did not occur                                  |

| bit 1   | DCIF: Duty Cycle Interrupt Flag bit <sup>(1)</sup>                   |

|         | 1 = Duty Cycle Match Event occurred                                  |

|         | 0 = Duty Cycle Match Event did not occur                             |

| bit 0   | PRIF: Period Interrupt Flag bit <sup>(1)</sup>                       |

|         | 1 = Period Match Event occurred                                      |

|         | 0 = Period Match Event did not occur                                 |

| Note 1: | Bit is forced clear by hardware while module is disabled (EN = $0$ ) |

Bit is forced clear by hardware while module is disabled (EN = 0).

# **REGISTER 23-15: PWMxTMRH: PWMx TIMER HIGH REGISTER**

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | TMR     | <15:8>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | oit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 TMR<15:8>: PWM Timer High bits Upper eight bits of PWM timer counter

#### **REGISTER 23-16: PWMxTMRL: PWMx TIMER LOW REGISTER**

| R/W-x/u  | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------|---------|---------|---------|---------|---------|---------|---------|

| TMR<7:0> |         |         |         |         |         |         |         |

| bit 7    |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMR<7:0>: PWM Timer Low bits Lower eight bits of PWM timer counter

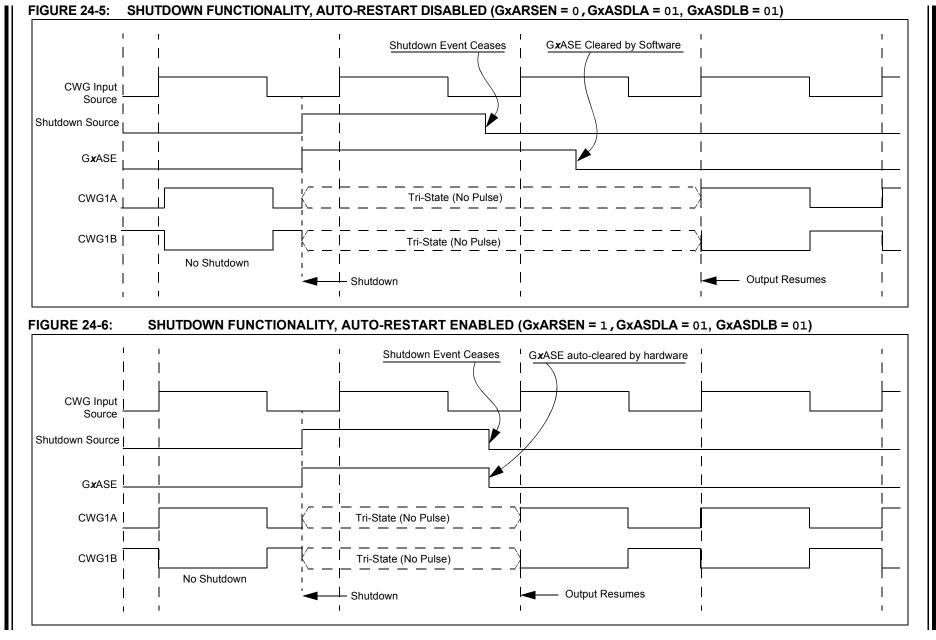

# 24.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces a complementary waveform with dead-band delay from a selection of input sources.

The CWG module has the following features:

- · Selectable dead-band clock source control

- · Selectable input sources

- · Output enable control

- · Output polarity control

- Dead-band control with independent 6-bit rising and falling edge dead-band counters

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

# 24.1 Fundamental Operation

The CWG generates two output waveforms from the selected input source.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 24.5 "Dead-Band Control"**. A typical operating waveform, with dead band, generated from a single input signal is shown in Figure 24-2.

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 24.9 "Auto-Shutdown Control"**.

#### 24.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the G1CS0 bit of the CWGxCON0 register (Register 24-1).

# 24.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources in Table 24-1.

| TABLE 24-1: | SELECTABLE INPUT |

|-------------|------------------|

|             | SOURCES          |

| Source Peripheral | Signal Name |  |

|-------------------|-------------|--|

| CWG input pin     | CWGxIN pin  |  |

| Comparator C1     | C1OUT_sync  |  |

| Comparator C2     | C2OUT_sync  |  |

| PWM1              | PWM1_output |  |

| PWM2              | PWM2_output |  |

| PWM3              | PWM3_output |  |

| PWM4              | PWM4_output |  |

The input sources are selected using the GxIS<2:0> bits in the CWGxCON1 register (Register 24-2).

# 24.4 Output Control

Immediately after the CWG module is enabled, the complementary drive is configured with both CWGxA and CWGxB drives cleared.

#### 24.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the GxPOLA and GxPOLB bits of the CWGxCON0 register.

© 2016 Microchip Technology Inc

PIC16(L)F1574/5/8/9

# PIC16(L)F1574/5/8/9

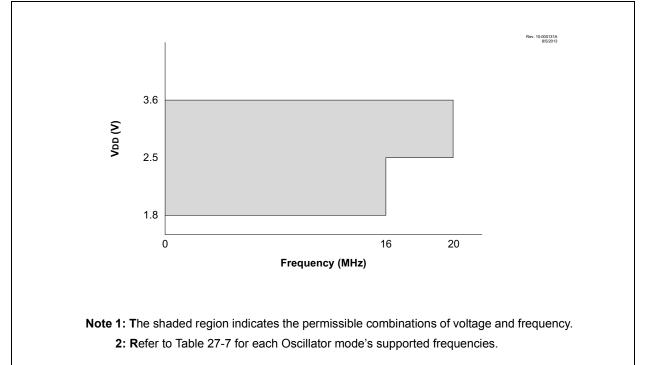

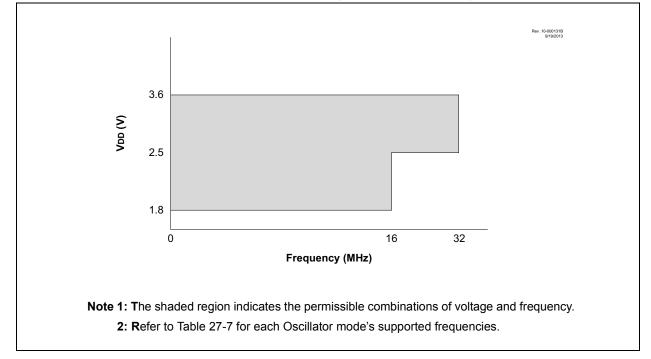

#### FIGURE 27-2: VOLTAGE FREQUENCY GRAPH, -40°C ≤ TA ≤ +125°C, PIC16LF1574/5/8/9 ONLY

# Package Marking Information (Continued)

16-Lead UQFN (4x4x0.5mm) Example • XXXXX XXXXXX YXXXXX YXXXX PIC16 PIN 1-PIN 1-LF1575 ML @3 410017 WNNN

| Legend | XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

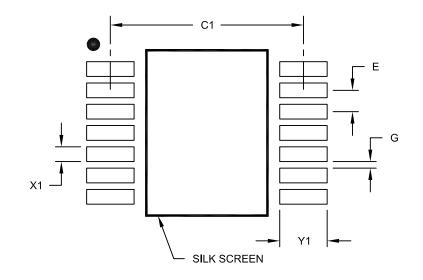

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension                | MIN         | NOM      | MAX  |      |

| Contact Pitch            | E           | 0.65 BSC |      |      |

| Contact Pad Spacing      | C1          |          | 5.90 |      |

| Contact Pad Width (X14)  | X1          |          |      | 0.45 |

| Contact Pad Length (X14) | Y1          |          |      | 1.45 |

| Distance Between Pads    | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A