# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | LINbus, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1579-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| Address            | Name        | Bit 7      | Bit 6        | Bit 5            | Bit 4         | Bit 3       | Bit 2         | Bit 1    | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------------------|-------------|------------|--------------|------------------|---------------|-------------|---------------|----------|-----------|----------------------|---------------------------------|

| Bank 27            | (Continued) |            |              |                  |               |             |               |          |           |                      |                                 |

| DC9h               | PWM4TMRL    |            |              |                  | -             | TMR<7:0>    |               |          |           | xxxx xxxx            | uuuu uuuu                       |

| DCAh               | PWM4TMRH    |            |              |                  | Т             | MR<15:8>    |               |          |           | xxxx xxxx            | uuuu uuuu                       |

| DCBh               | PWM4CON     | EN         | —            | OUT              | POL           | MODE        | E<1:0>        | _        | —         | 0000 00              | 0000 00                         |

| DCCh               | PWM4INTE    | —          | —            | —                | —             | OFIE        | PHIE          | DCIE     | PRIE      | 000                  | 000                             |

| DCDh               | PWM4INTF    | —          | —            | —                | —             | OFIF        | PHIF          | DCIF     | PRIF      | 000                  | 000                             |

| DCEh               | PWM4CLKCON  | —          |              | PS<2:0>          |               | _           | —             | CS∢      | <1:0>     | -000 -000            | -00000                          |

| DCFh               | PWM4LDCON   | LDA        | LDT          | —                | —             | —           | —             | LDS      | <1:0>     | 00000                | 0000                            |

| DD0h               | PWM40FCON   | —          | OFM          | <1:0>            | OFO           | _           | —             | OFS      | <1:0>     | -000 -000            | -00000                          |

| DD1h<br>to<br>DEFh | _           | Unimplemer | nimplemented |                  |               |             |               |          | _         |                      |                                 |

| Bank 28            |             |            |              |                  |               |             |               |          |           |                      |                                 |

| E0Ch               |             |            |              |                  |               |             |               |          |           |                      |                                 |

| E0Eh               | -           | Unimplemen | ited         |                  |               |             |               |          |           | —                    | _                               |

| E0Fh               | PPSLOCK     | —          | —            | _                | —             | _           | _             | —        | PPSLOCKED | 0                    | 0                               |

| E10h               | INTPPS      | _          | _            | _                |               | •           | INTPPS<4:0>   |          |           | 0 0010               | u uuuu                          |

| E11h               | TOCKIPPS    | _          | _            | _                |               |             | T0CKIPPS<4:0> | >        |           | 0 0010               | u uuuu                          |

| E12h               | T1CKIPPS    | _          | _            | _                |               |             | T1CKIPPS<4:0> | <b>`</b> |           | 0 0101               | u uuuu                          |

| E13h               | T1GPPS      | _          | _            | _                |               | T1GPPS<4:0> |               |          |           | 0 0100               | u uuuu                          |

| E14h               | CWG1INPPS   | _          | _            | _                | CWGINPPS<4:0> |             |               |          |           | 0 0010               | u uuuu                          |

| E15h               | RXPPS       | _          | _            | _                |               |             |               |          |           | 1 0101               | u uuuu                          |

| E16h               | CKPPS       | _          | _            | _                | CKPPS<4:0>    |             |               |          |           | 1 0101               | u uuuu                          |

| E17h               | ADCACTPPS   | _          | _            | - ADCACTPPS<4:0> |               |             |               |          | 1 0101    | u uuuu               |                                 |

| E18h<br>to<br>E6Fh | _           | Unimplemer | nted         |                  |               |             |               |          |           | —                    | _                               |

#### TABLE 3-15: SPECIAL EUNCTION DEGISTED SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

DS40001782C-page 45

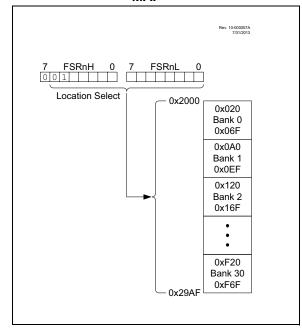

#### 3.6.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

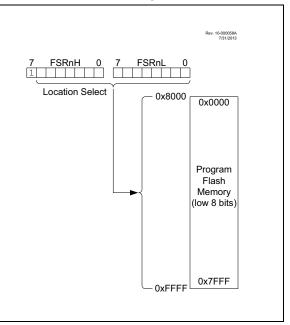

#### 3.6.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSb of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

#### 6.4 Low-Power Brown-Out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) operates like the BOR to detect low voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit ( $\overline{\text{BOR}}$ ) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR voltage threshold (VLPBOR) has a wider tolerance than the BOR (VBOR), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN = 00) or disabled in Sleep mode (BOREN = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

#### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

#### 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

#### TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| х     | 1   | Enabled  |

#### 6.5.1 MCLR ENABLED

When  $\overline{\text{MCLR}}$  is enabled and the pin is held low, the device is held in Reset. The  $\overline{\text{MCLR}}$  pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

#### **Note:** A Reset does not drive the MCLR pin low.

#### 6.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.1 "PORTA Registers"** for more information.

#### 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register are changed to indicate the WDT Reset. See **Section 9.0 "Watchdog Timer (WDT)"** for more information.

#### 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

#### 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 3.5.2 "Overflow/Underflow Reset"** for more information.

#### 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

#### 6.10 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overline{\text{PWRTE}}$  bit of Configuration Words.

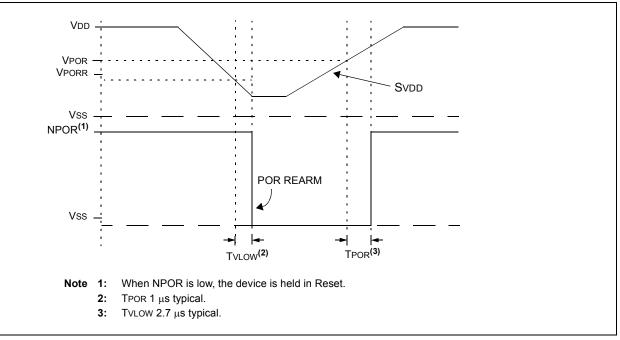

#### 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 5.0 "Oscillator Module"** for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 FOSC cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

|                       | D 0/0                                          | D 0/0                 | D 0/0                  | 11.0           |                   | 11.0             |             |

|-----------------------|------------------------------------------------|-----------------------|------------------------|----------------|-------------------|------------------|-------------|

| R-0/0                 | R-0/0                                          | R-0/0                 | R-0/0                  | U-0            | U-0               | U-0              | U-0         |

| PWM4IF <sup>(1)</sup> | PWM3IF <sup>(1)</sup>                          | PWM2IF <sup>(1)</sup> | PWM1IF <sup>(1)</sup>  | —              | —                 | —                | _           |

| bit 7                 |                                                |                       |                        |                |                   |                  | bit 0       |

|                       |                                                |                       |                        |                |                   |                  |             |

| Legend:               |                                                |                       |                        |                |                   |                  |             |

| R = Readable          | bit                                            | W = Writable          | bit                    | U = Unimpler   | mented bit, read  | as '0'           |             |

| u = Bit is unch       | nanged                                         | x = Bit is unkr       | nown                   | -n/n = Value   | at POR and BOI    | R/Value at all o | ther Resets |

| '1' = Bit is set      |                                                | '0' = Bit is cle      | ared                   |                |                   |                  |             |

|                       |                                                |                       |                        |                |                   |                  |             |

| bit 7                 | PWM4IF: PW                                     | /M4 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt i                                | is pending            |                        |                |                   |                  |             |

|                       | 0 = Interrupt                                  | is not pending        |                        |                |                   |                  |             |

| bit 6                 | PWM3IF: PW                                     | /M3 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt                                  | is pending            |                        |                |                   |                  |             |

|                       | 0 = Interrupt                                  | is not pending        |                        |                |                   |                  |             |

| bit 5                 | PWM2IF: PW                                     | /M2 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt                                  |                       |                        |                |                   |                  |             |

|                       | 0 = Interrupt is not pending                   |                       |                        |                |                   |                  |             |

| bit 4                 | PWM1IF: PWM1 Interrupt Flag bit <sup>(1)</sup> |                       |                        |                |                   |                  |             |

|                       | 1 = Interrupt is pending                       |                       |                        |                |                   |                  |             |

|                       | 0 = Interrupt is not pending                   |                       |                        |                |                   |                  |             |

| bit 3-0               | Unimplemen                                     | nted: Read as '       | 0'                     |                |                   |                  |             |

| Note 1. Th            | oso hits aro roa                               | d only Thoy m         | ust be cleared         | l by addragain | a the Flee regist | ora inaida tha n | aadula      |

#### REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

- Note 1: These bits are read-only. They must be cleared by addressing the Flag registers inside the module.

- 2: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### 9.6 Register Definitions: Watchdog Control

| U-0             | U-0                                  | R/W-0/0                                                        | R/W-1/1        | R/W-0/0           | R/W-1/1        | R/W-1/1  | R/W-0/0      |

|-----------------|--------------------------------------|----------------------------------------------------------------|----------------|-------------------|----------------|----------|--------------|

| _               | —                                    |                                                                |                | WDTPS<4:0>        |                |          | SWDTEN       |

| oit 7           |                                      |                                                                |                |                   |                |          | bit (        |

| .egend:         |                                      |                                                                |                |                   |                |          |              |

| R = Readable    | e bit                                | W = Writable                                                   | bit            | U = Unimpleme     | ented bit, rea | d as '0' |              |

| ı = Bit is unc  |                                      | x = Bit is unkr                                                | nown           | -n/n = Value at   |                |          | other Resets |

| 1' = Bit is set | •                                    | '0' = Bit is clea                                              | ared           |                   |                |          |              |

|                 |                                      |                                                                |                |                   |                |          |              |

| it 7-6          | -                                    | <b>nted:</b> Read as '<br><b>)&gt;:</b> Watchdog Ti            |                | alaat hita(1)     |                |          |              |

| oit 5-1         |                                      | -                                                              | Ther Period S  | elect bits, ,     |                |          |              |

|                 |                                      | Prescale Rate                                                  |                | interval (1:22)   |                |          |              |

|                 | 11111 = R                            | eserved. Results                                               |                | intervar (1.52)   |                |          |              |

|                 | •                                    |                                                                |                |                   |                |          |              |

|                 | •                                    |                                                                |                |                   |                |          |              |

|                 | 10011 = R                            | eserved. Results                                               | s in minimum   | interval (1:32)   |                |          |              |

|                 | 10010 = <b>1</b> :                   | 8388608 (2 <sup>23</sup> ) (                                   | Interval 256s  | nominal)          |                |          |              |

|                 | 10001 = <b>1</b> :                   | 4194304 (2 <sup>22</sup> ) (                                   | Interval 128s  | nominal)          |                |          |              |

|                 | 10000 = <b>1</b> :                   | 2097152 (2 <sup>21</sup> ) (1<br>1048576 (2 <sup>20</sup> ) (1 | Interval 64s r | iominal)          |                |          |              |

|                 | 01111 <b>= 1</b> :                   | 1048576 (2 <sup>20</sup> ) (1                                  | Interval 32s r | nominal)          |                |          |              |

|                 | 01110 = 1:                           | 524288 (2 <sup>19</sup> ) (In                                  | iterval 16s no | ominal)           |                |          |              |

|                 |                                      | 262144 (2 <sup>18</sup> ) (In<br>131072 (2 <sup>17</sup> ) (In |                |                   |                |          |              |

|                 |                                      | 65536 (Interval                                                |                | ,                 |                |          |              |

|                 |                                      | 32768 (Interval                                                |                |                   |                |          |              |

|                 |                                      | 16384 (Interval                                                |                | nal)              |                |          |              |

|                 |                                      | 8192 (Interval 2                                               |                |                   |                |          |              |

|                 |                                      | 4096 (Interval 1                                               |                |                   |                |          |              |

|                 |                                      | 2048 (Interval 6                                               |                |                   |                |          |              |

|                 |                                      | 1024 (Interval 3                                               |                | •                 |                |          |              |

|                 |                                      | 512 (Interval 16<br>256 (Interval 8 r                          |                |                   |                |          |              |

|                 |                                      | 128 (Interval 4 r                                              |                |                   |                |          |              |

|                 |                                      | 64 (Interval 2 m                                               | ,              |                   |                |          |              |

|                 |                                      | 32 (Interval 1 m                                               | ,              |                   |                |          |              |

| oit O           | SWDTEN: S                            | Software Enable/                                               | Disable for V  | Vatchdog Timer bi | it             |          |              |

|                 | <u>If WDTE&lt;1:</u> (               | )> = 1x:                                                       |                | ·                 |                |          |              |

|                 | This bit is ig                       | nored.                                                         |                |                   |                |          |              |

|                 | If WDTE<1:                           |                                                                |                |                   |                |          |              |

|                 | 1 = WDT is                           |                                                                |                |                   |                |          |              |

|                 | 0 = WDT is<br><u>If WDTE&lt;1:</u> ( |                                                                |                |                   |                |          |              |

|                 |                                      |                                                                |                |                   |                |          |              |

#### REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

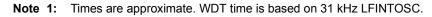

#### FIGURE 10-2: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL PMADRL

; Select Bank for PMCON registers

PROG_ADDR_LO

MOVLW

;

MOVWF

PMADRL

; Store LSB of address

PROG_ADDR_HI

MOVLW

;

MOVWF

PMADRH

; Store MSB of address

BCF

PMCON1,CFGS

; Do not select Configuration Space

BSF

PMCON1,RD

; Initiate read

NOP

; Ignored (Figure 10-2)

NOP

; Ignored (Figure 10-2)

MOVF

PMDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO

; Store in user location

; Get MSB of word

PMDATH,W

MOVF

MOVWF

PROG_DATA_HI

; Store in user location

```

| R/W-1/1                                                                                                                                                                                                                                                                                                         | R/W-1/1                                                                                                                                                                                                                                                                                                                         | U-0               | U-0  | R/W-1/1                                               | R/W-1/1          | R/W-1/1  | R/W-1/1 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|-------------------------------------------------------|------------------|----------|---------|--|--|

| ANSC7 <sup>(2)</sup>                                                                                                                                                                                                                                                                                            | ANSC6 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                            |                   | _    | ANSC3                                                 | ANSC2            | ANSC1    | ANSC0   |  |  |

| bit 7                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                 |                   |      |                                                       |                  |          | bit C   |  |  |

|                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                 |                   |      |                                                       |                  |          |         |  |  |

| Legend:                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                 |                   |      |                                                       |                  |          |         |  |  |

| R = Readable                                                                                                                                                                                                                                                                                                    | bit                                                                                                                                                                                                                                                                                                                             | W = Writable      | bit  | U = Unimpler                                          | nented bit, read | d as '0' |         |  |  |

| u = Bit is unch                                                                                                                                                                                                                                                                                                 | = Bit is unchanged x = Bit is unknown                                                                                                                                                                                                                                                                                           |                   | nown | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |  |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                 | '0' = Bit is clea | ared |                                                       |                  |          |         |  |  |

| bit 7-6 <b>ANSC&lt;7:6&gt;</b> : Analog Select between Analog or Digital Function on pins RC<7:6>, respectively <sup>(1, 2)</sup><br>0 = Digital I/O. Pin is assigned to port or digital special function.<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> . Digital input buffer disabled. |                                                                                                                                                                                                                                                                                                                                 |                   |      |                                                       |                  |          |         |  |  |

| bit 5-4                                                                                                                                                                                                                                                                                                         | 5-4 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |                   |      |                                                       |                  |          |         |  |  |

| bit 3-0                                                                                                                                                                                                                                                                                                         | <ul> <li>ANSC&lt;3:0&gt;: Analog Select between Analog or Digital Function on pins RC&lt;3:0&gt;, respectively<sup>(1)</sup></li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |                   |      |                                                       |                  |          |         |  |  |

| Note 1: Wh                                                                                                                                                                                                                                                                                                      | <b>lote 1:</b> When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to                                                                                                                                                                                                          |                   |      |                                                       |                  |          |         |  |  |

allow external control of the voltage on the pin. 2: ANSC<7:6> are available on PIC16(L)F1578/9 only.

#### REGISTER 11-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| WPUC7 <sup>(3)</sup> | WPUC6 <sup>(3)</sup> | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(3)</sup>

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

3: WPUC<7:6> are available on PIC16(L)F1578/9 only.

#### **16.1 ADC Configuration**

When configuring and using the ADC the following functions must be considered:

- Port configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- · Result formatting

#### 16.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 11.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

#### 16.1.2 CHANNEL SELECTION

There are up to 15 channel selections available:

- AN<7:0> pins (PIC16(L)F1574/5 only)

- AN<11:0> pins (PIC16(L)F1578/9 only)

- Temperature Indicator

- DAC1\_output

- FVR\_buffer1

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay (TACQ) is required before starting the next conversion. Refer to **Section 16.2.6 "ADC Conversion Procedure"** for more information.

#### 16.1.3 ADC VOLTAGE REFERENCE

The ADC module uses a positive and a negative voltage reference. The positive reference is labeled ref+ and the negative reference is labeled ref-.

The positive voltage reference (ref+) is selected by the ADPREF bits in the ADCON1 register. The positive voltage reference source can be:

- VREF+ pin

- Vdd

- FVR\_buffer1

The negative voltage reference (ref-) source is:

Vss

#### 16.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- · FRC (internal RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 16-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 27.0 "Electrical Specifications"** for more information. Table 16-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 16.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

#### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. Performing the ADC conversion during Sleep can reduce system noise. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 AUTO-CONVERSION TRIGGER

The auto-conversion trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The auto-conversion trigger source is selected with the TRIGSEL<3:0> bits of the ADCON2 register.

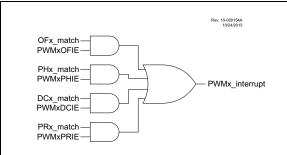

Using the auto-conversion trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met. The PWM module can trigger the ADC in two ways, directly through the PWMx\_OF\_match or through the interrupts generated by all four match signals. See Section 23.0 "16-bit Pulse-Width Modulation (PWM) Module". If the interrupts are chosen, each enabled interrupt in PWMxINTE will trigger a conversion. Refer to Figure 16-4 for more information.

See Table 16-2 for auto-conversion sources.

#### TABLE 16-2: AUTO-CONVERSION SOURCES

| Source Peripheral | Signal Name    |

|-------------------|----------------|

| Timer0            | T0_overflow    |

| Timer1            | T1_overflow    |

| Timer2            | T2_match       |

| Comparator C1     | C1OUT_sync     |

| Comparator C2     | C2OUT_sync     |

| PWM1              | PWM1_OF_match  |

| PWM1              | PWM1_interrupt |

| PWM2              | PWM2_OF_match  |

| PWM2              | PWM2_interrupt |

| PWM3              | PWM3_OF_match  |

| PWM3              | PWM3_interrupt |

| PWM4              | PWM4_OF_match  |

| PWM4              | PWM4_interrupt |

| ADC Trigger       | ADCACT         |

| CWG Input Pin     | CWGIN          |

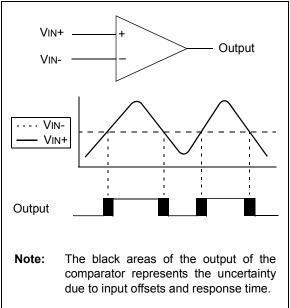

#### FIGURE 18-2: SINGLE COMPARATOR

#### 18.2 Comparator Control

The comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- · Output selection

- Output polarity

- Speed/Power selection

- · Hysteresis enable

- Output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR POSITIVE INPUT SELECTION

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC1\_output

- FVR\_buffer2

- Vss

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

### 18.2.3 COMPARATOR NEGATIVE INPUT SELECTION

The CxNCH<2:0> bits of the CMxCON0 register direct one of the input sources to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog<br>input, the appropriate bits must be set in<br>the ANSEL register and the correspond- |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

|       | ing TRIS bits must also be set to disable                                                                                      |

|       | the output drivers.                                                                                                            |

#### 18.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

The synchronous comparator output signal (CxOUT\_sync) is available to the following peripheral(s):

- Analog-to-Digital Converter (ADC)

- Timer1

The asynchronous comparator output signal (CxOUT\_async) is available to the following peripheral(s):

Complementary Waveform Generator (CWG)

Note: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### REGISTER 23-11: PWMxPRH: PWMx PERIOD COUNT HIGH REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | PR<     | :15:8>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **PR<15:8>**: PWM Period High bits Upper eight bits of PWM period count

#### REGISTER 23-12: PWMxPRL: PWMx PERIOD COUNT LOW REGISTER

| R/W-x/u   | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| PR<7:0>   |         |         |         |         |         |         |         |

| bit 7 bit |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PR<7:0>**: PWM Period Low bits Lower eight bits of PWM period count

#### 24.10 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep, provided that the CWG module is enabled, the input source is active, and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, the CPU will go idle during Sleep, but the CWG will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### 24.11 Configuring the CWG

The following steps illustrate how to properly configure the CWG to ensure a synchronous start:

- 1. Ensure that the TRIS control bits corresponding to CWGxA and CWGxB are set so that both are configured as inputs.

- 2. Clear the GxEN bit, if not already cleared.

- 3. Set desired dead-band times with the CWGxDBR and CWGxDBF registers.

- 4. Setup the following controls in CWGxCON2 auto-shutdown register:

- · Select desired shutdown source.

- Select both output overrides to the desired levels (this is necessary even if not using auto-shutdown because start-up will be from a shutdown state).

- Set the GxASE bit and clear the GxARSEN bit.

- 5. Select the desired input source using the CWGxCON1 register.

- 6. Configure the following controls in CWGxCON0 register:

- · Select desired clock source.

- Select the desired output polarities.

- 7. Set the GxEN bit.

- Clear TRIS control bits corresponding to CWGxA and CWGxB to be used to configure those pins as outputs.

- If auto-restart is to be used, set the GxARSEN bit and the GxASE bit will be cleared automatically. Otherwise, clear the GxASE bit to start the CWG.

#### 24.11.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the GxASDLA and GxASDLB bits of the CWGxCON1 register (Register 24-3). GxASDLA controls the CWG1A override level and GxASDLB controls the CWG1B override level. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not apply to the override level.

#### 24.11.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to have resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the GxARSEN bit of the CWGxCON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 24-5 and Figure 24-6.

#### 24.11.2.1 Software Controlled Restart

When the GxARSEN bit of the CWGxCON2 register is cleared, the CWG must be restarted after an auto-shut-down event by software.

Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the GxASE bit will remain set. The overrides will remain in effect until the first rising edge event after the GxASE bit is cleared. The CWG will then resume operation.

#### 24.11.2.2 Auto-Restart

When the GxARSEN bit of the CWGxCON2 register is set, the CWG will restart from the auto-shutdown state automatically.

The GxASE bit will clear automatically when all shutdown sources go low. The overrides will remain in effect until the first rising edge event after the GxASE bit is cleared. The CWG will then resume operation.

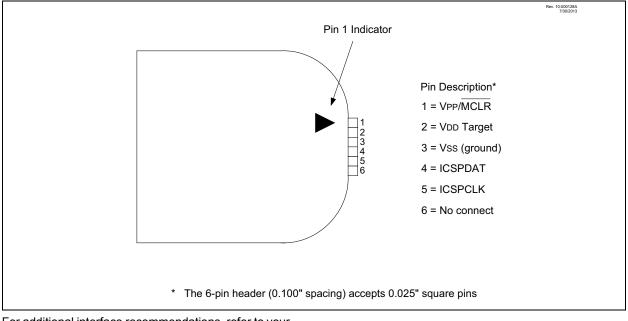

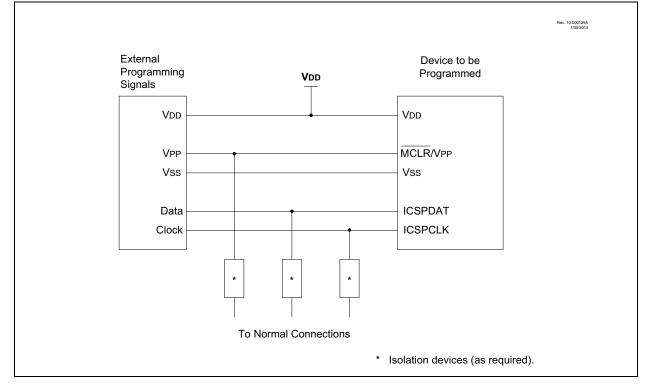

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 25-3 for more information.

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                               |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                          |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                        |

| Operands:        | None                                                                                                                                                  |

| Operation:       | $TOS\toPC$                                                                                                                                            |

| Status Affected: | None                                                                                                                                                  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |

| RETLW            | Return with literal in W                                                                                                           | RLF              | Deteta Left fithrough Correc                                                                                                                                                      |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                           |                  | Rotate Left f through Carry                                                                                                                                                       |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                  | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                          |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                       | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                |  |  |  |

| Status Affected: | None                                                                                                                               | Operation:       | See description below                                                                                                                                                             |  |  |  |

| Description:     | The W register is loaded with the 8-bit                                                                                            | Status Affected: | С                                                                                                                                                                                 |  |  |  |

| Description.     | literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is |  |  |  |

| Words:           | 1                                                                                                                                  |                  | stored back in register 'f'.                                                                                                                                                      |  |  |  |

| Cycles:          | 2                                                                                                                                  |                  | C Register f                                                                                                                                                                      |  |  |  |

| Example:         | CALL TABLE;W contains table                                                                                                        | Words:           | 1                                                                                                                                                                                 |  |  |  |

|                  | ;offset value<br>• ;W now has table value                                                                                          | Cycles:          | 1                                                                                                                                                                                 |  |  |  |

| TABLE            | •                                                                                                                                  | Example:         | RLF REG1,0                                                                                                                                                                        |  |  |  |

|                  | •                                                                                                                                  |                  | Before Instruction                                                                                                                                                                |  |  |  |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table                                                                                      |                  | REG1 = 1110 0110                                                                                                                                                                  |  |  |  |

|                  | RETLW k2 ;                                                                                                                         |                  | C = 0                                                                                                                                                                             |  |  |  |

|                  | •                                                                                                                                  |                  | After Instruction<br>REG1 = 1110 0110                                                                                                                                             |  |  |  |

|                  | •                                                                                                                                  |                  | $\begin{array}{rcl} \text{REG1} &=& 1110 & 0110 \\ \text{W} &=& 1100 & 1100 \end{array}$                                                                                          |  |  |  |

|                  | •<br>RETLW kn ; End of table                                                                                                       |                  | C = 1                                                                                                                                                                             |  |  |  |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                             |                  |                                                                                                                                                                                   |  |  |  |

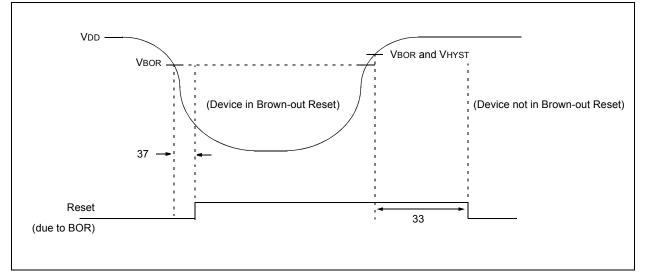

## TABLE 27-11:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET PARAMETERS

| Standa        | Standard Operating Conditions (unless otherwise stated) |                                                          |      |      |      |       |                                                       |  |  |

|---------------|---------------------------------------------------------|----------------------------------------------------------|------|------|------|-------|-------------------------------------------------------|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                                           | Min. | Тур† | Max. | Units | Conditions                                            |  |  |

| 30            | ТмсL                                                    | MCLR Pulse Width (low)                                   | 2    | _    | _    | μS    |                                                       |  |  |

| 31            | TWDTLP                                                  | Low-Power Watchdog Timer<br>Time-out Period              | 10   | 16   | 27   | ms    | VDD = 3.3V-5V,<br>1:512 Prescaler used                |  |  |

| 32            | Tost                                                    | Oscillator Start-up Timer Period <sup>(1)</sup>          | _    | 1024 | _    | Tosc  |                                                       |  |  |

| 33*           | TPWRT                                                   | Power-up Timer Period                                    | 40   | 65   | 140  | ms    | PWRTE = 0                                             |  |  |

| 34*           | Tioz                                                    | I/O high-impedance from MCLR Low or Watchdog Timer Reset |      |      | 2.0  | μS    |                                                       |  |  |

| 35            | VBOR                                                    | Brown-out Reset Voltage <sup>(2)</sup>                   | 2.55 | 2.70 | 2.85 | V     | BORV = 0                                              |  |  |

|               |                                                         |                                                          | 2.35 | 2.45 | 2.58 | V     | BORV = 1                                              |  |  |

|               |                                                         |                                                          | 1.80 | 1.90 | 2.05 | V     | (PIC16F1574/5/8/9)<br>BORV = 1<br>(PIC16LF1574/5/8/9) |  |  |

| 36*           | VHYST                                                   | Brown-out Reset Hysteresis                               | 0    | 25   | 60   | mV    | $-40^{\circ}C \le TA \le +85^{\circ}C$                |  |  |

| 37*           | TBORDC                                                  | Brown-out Reset DC Response Time                         | 1    | 16   | 35   | μS    | $V \text{DD} \leq V \text{BOR}$                       |  |  |

| 38            | VLPBOR                                                  | Low-Power Brown-Out Reset Voltage                        | 1.8  | 2.1  | 2.5  | V     | LPBOR = 1                                             |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

2: To ensure these voltage tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

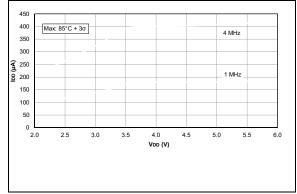

FIGURE 28-7: IDD Typical, EC Oscillator, Medium Power Mode, PIC16F1574/5/8/9 Only.

FIGURE 28-8: IDD Maximum, EC Oscillator, Medium Power Mode, PIC16F1574/5/8/9 Only.

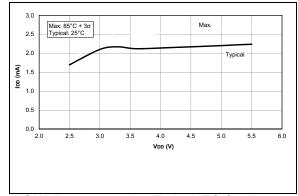

**FIGURE 28-9:** IDD Typical, EC Oscillator, High-Power Mode, Fosc = 32 kHz, PIC16LF1574/5/8/9 Only.

**FIGURE 28-10:** IDD Typical, EC Oscillator, High-Power Mode, Fosc = 32 kHz, PIC16F1574/5/8/9 Only.

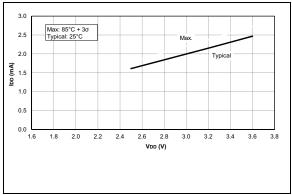

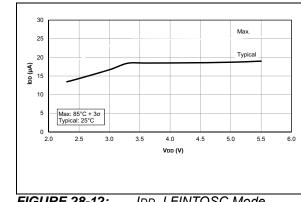

FIGURE 28-12: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16F1574/5/8/9 Only.

12 (**V**rl) 10 8 Typical 4 2 0 3.4 3.6 1.8 2.0 2.2 2.4 2.6 2.8 3.0 3.2 3.8 1.6 VDD (V) FIGURE 28-11: IDD, LFINTOSC Mode,

Max.

Fosc = 31 kHz, PIC16LF1574/5/8/9 Only.

18

16

14

Max: 85°C + 3o Typical: 25°C

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15