#### Microchip Technology - PIC16F1579-E/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1579-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| Address            | Name        | Bit 7      | Bit 6          | Bit 5           | Bit 4       | Bit 3    | Bit 2         | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------------------|-------------|------------|----------------|-----------------|-------------|----------|---------------|-------|-----------|----------------------|---------------------------------|

| Bank 27            | (Continued) |            |                |                 |             |          |               |       |           |                      |                                 |

| DC9h               | PWM4TMRL    |            |                |                 | -           | TMR<7:0> |               |       |           | xxxx xxxx            | uuuu uuuu                       |

| DCAh               | PWM4TMRH    |            |                |                 | Т           | MR<15:8> |               |       |           | xxxx xxxx            | uuuu uuuu                       |

| DCBh               | PWM4CON     | EN         | —              | OUT             | POL         | MODE     | E<1:0>        | _     | —         | 0000 00              | 0000 00                         |

| DCCh               | PWM4INTE    | —          | —              | —               | —           | OFIE     | PHIE          | DCIE  | PRIE      | 000                  | 000                             |

| DCDh               | PWM4INTF    | —          | —              | —               | —           | OFIF     | PHIF          | DCIF  | PRIF      | 000                  | 000                             |

| DCEh               | PWM4CLKCON  | —          |                | PS<2:0>         |             | _        | —             | CS∢   | <1:0>     | -000 -000            | -00000                          |

| DCFh               | PWM4LDCON   | LDA        | LDT            | —               | —           | —        | —             | LDS   | <1:0>     | 00000                | 0000                            |

| DD0h               | PWM40FCON   | —          | OFM            | <1:0>           | OFO         | _        | —             | OFS   | <1:0>     | -000 -000            | -00000                          |

| DD1h<br>to<br>DEFh | _           | Unimplemer | nimplemented   |                 |             |          |               |       | _         |                      |                                 |

| Bank 28            |             |            |                |                 |             |          |               |       |           |                      |                                 |

| E0Ch               |             |            |                |                 |             |          |               |       |           |                      |                                 |

| E0Eh               | -           | Unimplemen | ited           |                 |             |          |               |       |           | —                    | _                               |

| E0Fh               | PPSLOCK     | —          | —              | _               | —           | _        | _             | —     | PPSLOCKED | 0                    | 0                               |

| E10h               | INTPPS      | _          | _              | _               |             | •        | INTPPS<4:0>   |       |           | 0 0010               | u uuuu                          |

| E11h               | TOCKIPPS    | _          | _              | _               |             |          | T0CKIPPS<4:0> | >     |           | 0 0010               | u uuuu                          |

| E12h               | T1CKIPPS    | _          | _              | _               |             |          |               |       |           | 0 0101               | u uuuu                          |

| E13h               | T1GPPS      | _          | _              | _               | T1GPPS<4:0> |          |               |       |           | 0 0100               | u uuuu                          |

| E14h               | CWG1INPPS   | _          | _              | — CWGINPPS<4:0> |             |          |               |       | 0 0010    | u uuuu               |                                 |

| E15h               | RXPPS       | _          | _              |                 |             |          |               |       | 1 0101    | u uuuu               |                                 |

| E16h               | CKPPS       | _          | _              | — — CKPPS<4:0>  |             |          |               |       | 1 0101    | u uuuu               |                                 |

| E17h               | ADCACTPPS   | _          | ADCACTPPS<4:0> |                 |             |          |               |       | 1 0101    | u uuuu               |                                 |

| E18h<br>to<br>E6Fh | _           | Unimplemer | nimplemented   |                 |             |          |               |       | —         | _                    |                                 |

#### TABLE 3-15: SPECIAL EUNCTION DEGISTED SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

DS40001782C-page 45

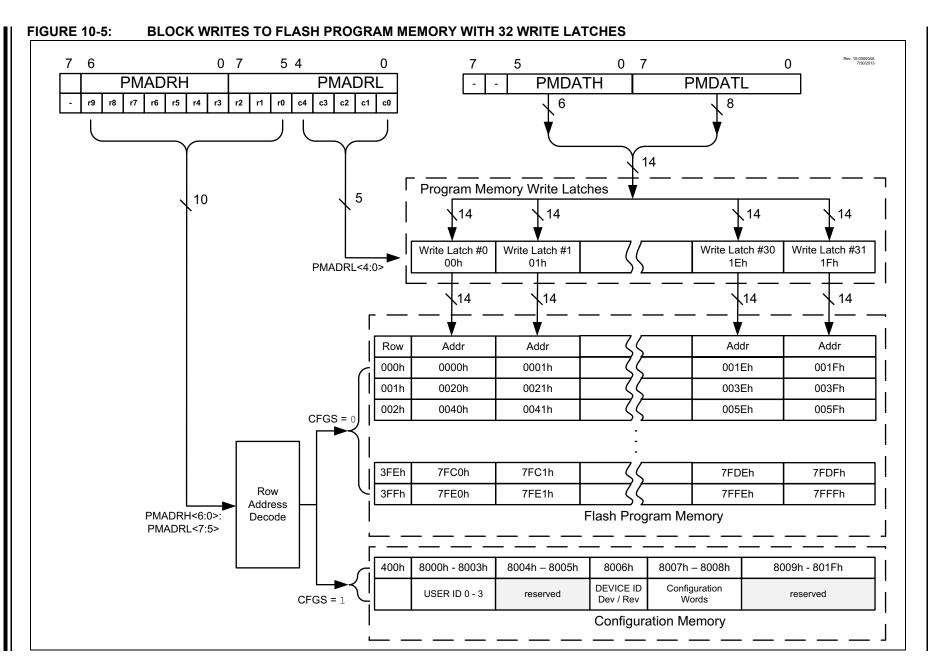

#### 4.2 Register Definitions: Configuration Words

#### R/P-1 U-1 U-1 R/P-1 R/P-1 U-1 BOREN<1:0>(1) CLKOUTEN bit 13 bit 8 R/P-1 R/P-1 R/P-1 **R/P-1 R/P-1 R/P-1** U-1 R/P-1 CP(2) PWRTE<sup>(1)</sup> MCLRE WDTE<1:0> FOSC<1:0> bit 7 bit 0 Legend: R = Readable bit P = Programmable bit U = Unimplemented bit, read as '1' '0' = Bit is cleared '1' = Bit is set n = Value when blank or after Bulk Erase bit 13-12 Unimplemented: Read as '1' bit 11 **CLKOUTEN:** Clock Out Enable bit 1 = OFF - CLKOUT function is disabled. I/O or oscillator function on CLKOUT pin 0 = ON - CLKOUT function is enabled on CLKOUT pin bit 10-9 BOREN<1:0>: Brown-out Reset Enable bits<sup>(1)</sup> - Brown-out Reset enabled. The SBOREN bit is ignored. 11 = ON 10 = SLEEP - Brown-out Reset enabled while running and disabled in Sleep. The SBOREN bit is ignored. 01 = SBODEN- Brown-out Reset controlled by the SBOREN bit in the BORCON register 00 = OFF- Brown-out Reset disabled. The SBOREN bit is ignored. bit 8 Unimplemented: Read as '1' CP: Flash Program Memory Code Protection bit<sup>(2)</sup> bit 7 1 = OFF – Code protection off. Program Memory can be read and written. 0 = ON - Code protection on. Program Memory cannot be read or written externally. bit 6 MCLRE: MCLR/VPP Pin Function Select bit If LVP bit = 1 (ON): This bit is ignored. MCLR/VPP pin function is MCLR; Weak pull-up enabled. If LVP bit = 0 (OFF): $1 = ON - \overline{MCLR}/VPP$ pin function is $\overline{MCLR}$ ; Weak pull-up enabled. 0 = OFF – MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of pin's WPU control bit. **PWRTE:** Power-up Timer Enable bit<sup>(1)</sup> bit 5 1 = OFF-PWRT disabled 0 = ON - PWRT enabled WDTE<1:0>: Watchdog Timer Enable bit bit 4-3 - WDT enabled. SWDTEN is ignored. 11 = ON 10 = SLEEP - WDT enabled while running and disabled in Sleep. SWDTEN is ignored. 01 = SWDTEN-WDT controlled by the SWDTEN bit in the WDTCON register 00 = OFF - WDT disabled. SWDTEN is ignored. bit 2 Unimplemented: Read as '1' bit 1-0 FOSC<1:0>: Oscillator Selection bits 11 = ECH - External Clock, High-Power mode: CLKI on CLKI - External Clock, Medium Power mode: CLKI on CLKI 10 = ECM01 = ECL- External Clock, Low-Power mode: CLKI on CLKI 00 = INTOSC-I/O function on CLKI Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer. Once enabled, code-protect can only be disabled by bulk erasing the device. 2:

#### **REGISTER 4-1: CONFIGURATION WORD 1**

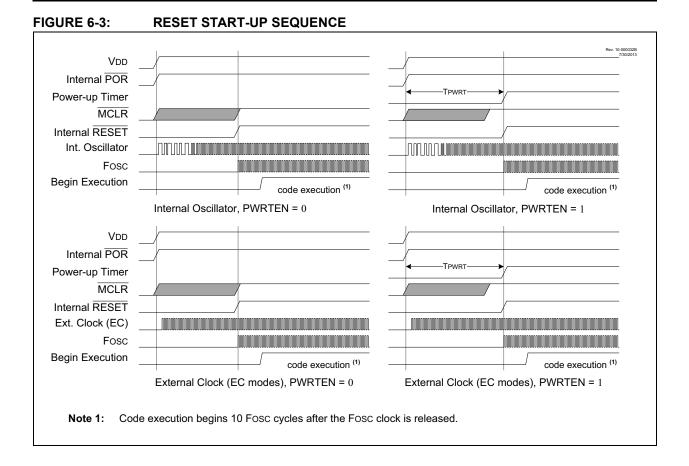

#### 5.2.2.7 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<1:0> = 00).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<1:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

#### 5.2.2.8 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-3). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-3 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables of **Section 27.0 "Electrical Specifications"**.

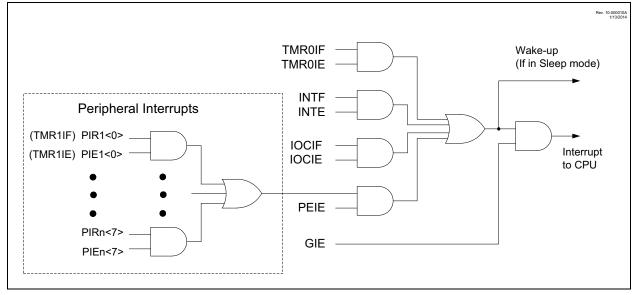

## 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

PIC16(L)F1574/5/8/9

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | R<1:0> | ADFV  | २<1:0> | 118                 |

Legend: Shaded cells are unused by the temperature indicator module.

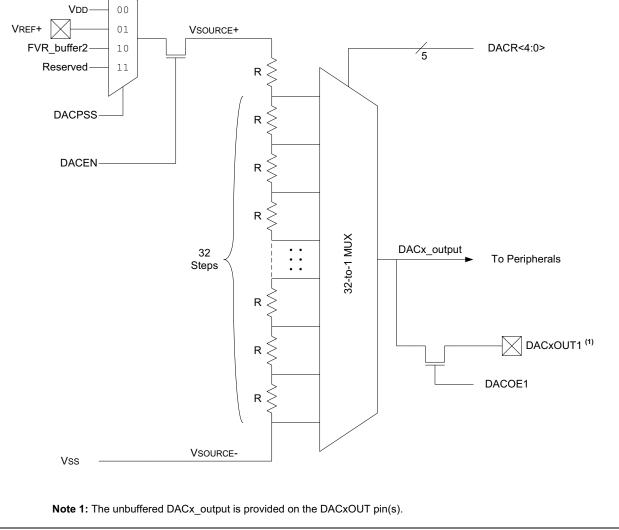

#### 17.0 **5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE**

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The positive input source (VSOURCE+) of the DAC can be connected to:

- · External VREF+ pin

- · VDD supply voltage

- FVR\_buffer1

**FIGURE 17-1:**

The negative input source (VSOURCE-) of the DAC can be connected to:

Vss

The output of the DAC (DACx\_output) can be selected as a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- DACxOUT1 pin

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACxCON0 register.

Rev. 10-000026B 9/6/2013

#### VDD 00 VREF+ 01 VSOURCE+

DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

### 21.5 Register Definitions: Timer2 Control

| U-0               | R/W-0/0                  | R/W-0/0                                        | R/W-0/0         | R/W-0/0        | R/W-0/0         | R/V        | V-0/0       | R/W-0/0      |  |  |

|-------------------|--------------------------|------------------------------------------------|-----------------|----------------|-----------------|------------|-------------|--------------|--|--|

|                   |                          | T2OUT                                          | PS<3:0>         |                | TMR2ON          |            | T2CKP       | S<1:0>       |  |  |

| oit 7             |                          |                                                |                 |                |                 | •          |             | bit          |  |  |

|                   |                          |                                                |                 |                |                 |            |             |              |  |  |

| Legend:           |                          |                                                |                 |                |                 |            |             |              |  |  |

| R = Readabl       | e bit                    | W = Writable                                   | bit             | U = Unimple    | emented bit, re | ead as '0' |             |              |  |  |

| u = Bit is und    | hanged                   | x = Bit is unk                                 | nown            | -n/n = Value   | at POR and I    | 30R/Valu   | ie at all o | other Resets |  |  |

| '1' = Bit is se   | t                        | '0' = Bit is cle                               | ared            |                |                 |            |             |              |  |  |

|                   |                          |                                                |                 |                |                 |            |             |              |  |  |

| bit 7             | -                        | ented: Read as '                               |                 |                |                 |            |             |              |  |  |

| bit 6-3           | T2OUTPS<                 | 3:0>: Timer2 Ou                                | utput Postscale | er Select bits |                 |            |             |              |  |  |

|                   | 0000 = 1:1               |                                                |                 |                |                 |            |             |              |  |  |

|                   |                          | 0001 = 1:2 Postscaler                          |                 |                |                 |            |             |              |  |  |

|                   |                          | 0010 = 1:3 Postscaler                          |                 |                |                 |            |             |              |  |  |

|                   |                          | 0011 = 1:4 Postscaler                          |                 |                |                 |            |             |              |  |  |

|                   |                          | 0100 = 1:5 Postscaler                          |                 |                |                 |            |             |              |  |  |

|                   |                          | 0101 = 1:6 Postscaler<br>0110 = 1:7 Postscaler |                 |                |                 |            |             |              |  |  |

|                   | 0110 = 1.7<br>0111 = 1:8 |                                                |                 |                |                 |            |             |              |  |  |

|                   | 1000 = 1:9               |                                                |                 |                |                 |            |             |              |  |  |

|                   |                          | ) Postscaler                                   |                 |                |                 |            |             |              |  |  |

|                   |                          | l Postscaler                                   |                 |                |                 |            |             |              |  |  |

|                   |                          | 1011 = 1:12 Postscaler                         |                 |                |                 |            |             |              |  |  |

|                   |                          | 3 Postscaler                                   |                 |                |                 |            |             |              |  |  |

|                   |                          | 4 Postscaler                                   |                 |                |                 |            |             |              |  |  |

|                   | 1110 <b>= 1:15</b>       | 5 Postscaler                                   |                 |                |                 |            |             |              |  |  |

|                   | 1111 <b>= 1:16</b>       | 6 Postscaler                                   |                 |                |                 |            |             |              |  |  |

| bit 2             | TMR2ON: T                | Fimer2 On bit                                  |                 |                |                 |            |             |              |  |  |

|                   | 1 = Timer2               | is on                                          |                 |                |                 |            |             |              |  |  |

|                   | 0 = Timer2               | is off                                         |                 |                |                 |            |             |              |  |  |

| bit 1-0           | T2CKPS<1                 | :0>: Timer2 Cloo                               | ck Prescale Se  | elect bits     |                 |            |             |              |  |  |

|                   | 00 = Presca              | aler is 1                                      |                 |                |                 |            |             |              |  |  |

|                   | 01 = Presca              | aler is 4                                      |                 |                |                 |            |             |              |  |  |

|                   | 10 = Presca              | aler is 16                                     |                 |                |                 |            |             |              |  |  |

|                   | 11 = Presca              | aler is 64                                     |                 |                |                 |            |             |              |  |  |

| <b>TABLE 21-1</b> | : SUMMAI                 |                                                | TERS ASSO       |                | TH TIMER2       |            |             |              |  |  |

|                   |                          |                                                |                 |                |                 |            |             | Registe      |  |  |

| NI a constant     |                          |                                                | D14 4           | D14.0          | D:4 0           | D:4 4      |             |              |  |  |

### REGISTER 21-1: T2CON: TIMER2 CONTROL REGISTER

| Name   | Bit 7                                     | Bit 6               | Bit 5  | Bit 4 | Bit 3 | Bit 2       | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------------------------------------------|---------------------|--------|-------|-------|-------------|--------|--------|---------------------|

| INTCON | GIE                                       | PEIE                | TMR0IE | INTE  | IOCIE | TMR0IF      | INTF   | IOCIF  | 86                  |

| PIE1   | TMR1GIE                                   | ADIE                | RCIE   | TXIE  | -     | _           | TMR2IE | TMR1IE | 87                  |

| PIR1   | TMR1GIF                                   | ADIF                | RCIF   | TXIF  | -     | —           | TMR2IF | TMR1IF | 90                  |

| PR2    | Timer2 Module Period Register             |                     |        |       |       |             |        | 189*   |                     |

| T2CON  | _                                         | T2OUTPS<3:0> TMR2ON |        |       |       | T2CKPS<1:0> |        | 191    |                     |

| TMR2   | Holding Register for the 8-bit TMR2 Count |                     |        |       |       |             |        | 189*   |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

Note 1: PIC16(L)F1575 only.

| R/W-0/0          | R-1/1                                                                                                                                            | U-0                                                | R/W-0/0          | R/W-0/0         | U-0           | R/W-0/0           | R/W-0/0      |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|-----------------|---------------|-------------------|--------------|--|--|--|--|--|

| ABDOVF           | RCIDL                                                                                                                                            |                                                    | SCKP             | BRG16           | _             | WUE               | ABDEN        |  |  |  |  |  |

| bit 7            | •                                                                                                                                                |                                                    |                  |                 |               | ·                 | bit (        |  |  |  |  |  |

|                  |                                                                                                                                                  |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

| Legend:          |                                                                                                                                                  |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

| R = Readable     | bit                                                                                                                                              | W = Writable                                       | e bit            | U = Unimplem    |               |                   |              |  |  |  |  |  |

| u = Bit is unch  | anged                                                                                                                                            | x = Bit is unl                                     | known            | -n/n = Value at | POR and BC    | DR/Value at all o | other Resets |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                  | '0' = Bit is cl                                    | eared            |                 |               |                   |              |  |  |  |  |  |

| bit 7            |                                                                                                                                                  | Auto-Baud Dete                                     | ect Overflow bit |                 |               |                   |              |  |  |  |  |  |

| Sit I            | Asynchrono                                                                                                                                       |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  |                                                                                                                                                  | ud timer overflo                                   | owed             |                 |               |                   |              |  |  |  |  |  |

|                  |                                                                                                                                                  | ud timer did no                                    | t overflow       |                 |               |                   |              |  |  |  |  |  |

|                  | Synchronou<br>Don't care                                                                                                                         | Synchronous mode:                                  |                  |                 |               |                   |              |  |  |  |  |  |

| bit 6            |                                                                                                                                                  | ceive Idle Flag b                                  | oit              |                 |               |                   |              |  |  |  |  |  |

|                  |                                                                                                                                                  | RCIDL: Receive Idle Flag bit<br>Asynchronous mode: |                  |                 |               |                   |              |  |  |  |  |  |

|                  | 1 = Receiver is idle                                                                                                                             |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | 0 = Start bit has been received and the receiver is receiving<br>Synchronous mode:                                                               |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | Don't care                                                                                                                                       | is mode.                                           |                  |                 |               |                   |              |  |  |  |  |  |

| bit 5            | Unimpleme                                                                                                                                        | ented: Read as                                     | ·'0'             |                 |               |                   |              |  |  |  |  |  |

| bit 4            | SCKP: Synchronous Clock Polarity Select bit                                                                                                      |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | Asynchronous mode:                                                                                                                               |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | <ul> <li>1 = Transmit inverted data to the TX/CK pin</li> <li>0 = Transmit non-inverted data to the TX/CK pin</li> </ul>                         |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | Synchronous mode:                                                                                                                                |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | <ul> <li>1 = Data is clocked on rising edge of the clock</li> <li>0 = Data is clocked on falling edge of the clock</li> </ul>                    |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

| bit 3            | BRG16: 16-                                                                                                                                       | -bit Baud Rate                                     | Generator bit    |                 |               |                   |              |  |  |  |  |  |

|                  |                                                                                                                                                  | Baud Rate Generaud Rate Gener                      |                  |                 |               |                   |              |  |  |  |  |  |

| bit 2            | Unimpleme                                                                                                                                        | ented: Read as                                     | ʻ0'              |                 |               |                   |              |  |  |  |  |  |

| bit 1            | WUE: Wake                                                                                                                                        | e-up Enable bit                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | Asynchronous mode:                                                                                                                               |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | 1 = Receiver is waiting for a falling edge. No character will be received, RCIF bit will be set. WUE w<br>automatically clear after RCIF is set. |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  |                                                                                                                                                  | 0 = Receiver is operating normally                 |                  |                 |               |                   |              |  |  |  |  |  |

|                  | Synchronous mode:<br>Don't care                                                                                                                  |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

| bit 0            |                                                                                                                                                  | ito-Baud Detect                                    | t Enable bit     |                 |               |                   |              |  |  |  |  |  |

|                  |                                                                                                                                                  |                                                    |                  |                 |               |                   |              |  |  |  |  |  |

|                  | -                                                                                                                                                |                                                    | de is enabled (c | lears when auto | -baud is com  | nplete)           |              |  |  |  |  |  |

|                  | 0 = Auto-Ba                                                                                                                                      | aud Detect mod                                     |                  |                 |               | -                 |              |  |  |  |  |  |

|                  | Synchronou                                                                                                                                       | <u>is mode</u> :                                   |                  |                 |               |                   |              |  |  |  |  |  |

| DIT U            | Asynchrono<br>1 = Auto-Ba<br>0 = Auto-Ba                                                                                                         | ous mode:<br>aud Detect mod<br>aud Detect mod      | de is enabled (c | lears when auto | o-baud is com | nplete)           |              |  |  |  |  |  |

#### REGISTER 22-3: BAUDCON: BAUD RATE CONTROL REGISTER

#### 22.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 22.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 22.5.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 22.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

## TABLE 22-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|-------|--------|-------|-------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL | —      | SCKP  | BRG16 | _      | WUE    | ABDEN  | 204                 |

| INTCON  | GIE                           | PEIE  | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1    | TMR1GIE                       | ADIE  | RCIE   | TXIE  | _     | _      | TMR2IE | TMR1IE | 87                  |

| PIR1    | TMR1GIF                       | ADIF  | RCIF   | TXIF  | —     | _      | TMR2IF | TMR1IF | 90                  |

| RCSTA   | SPEN                          | RX9   | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 203                 |

| TXREG   | EUSART Transmit Data Register |       |        |       |       |        |        | 194*   |                     |

| TXSTA   | CSRC                          | TX9   | TXEN   | SYNC  | SENDB | BRGH   | TRMT   | TX9D   | 202                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave transmission.

\* Page provides register information.

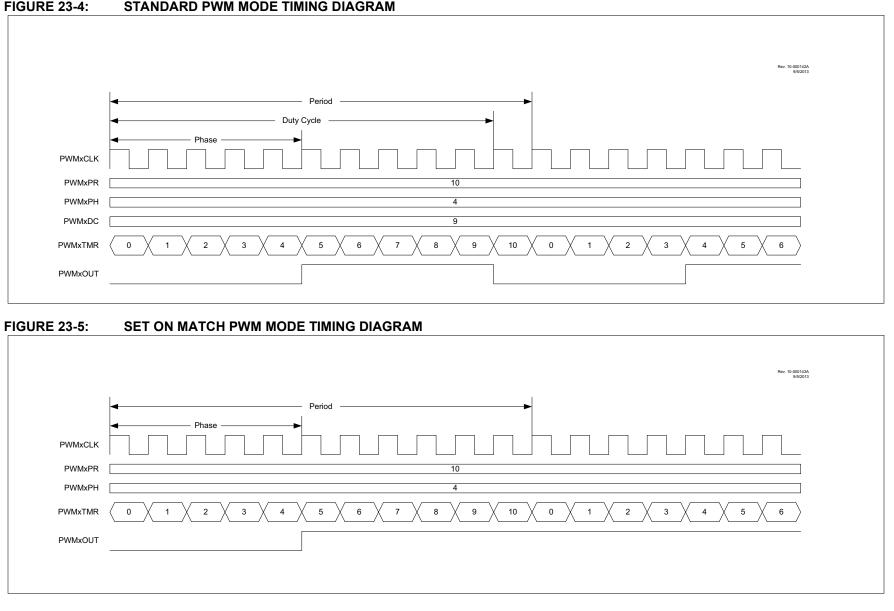

## FIGURE 23-4:

#### STANDARD PWM MODE TIMING DIAGRAM

PIC16(L)F1574/5/8/9

### 26.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 26-3 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

#### 26.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

## TABLE 26-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| n     | FSR or INDF number. (0-1)                                                                                                                                                            |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                          |

# TABLE 26-2:ABBREVIATIONDESCRIPTIONS

| Field | Description     |  |  |  |

|-------|-----------------|--|--|--|

| PC    | Program Counter |  |  |  |

| TO    | Time-Out bit    |  |  |  |

| С     | Carry bit       |  |  |  |

| DC    | Digit Carry bit |  |  |  |

| Z     | Zero bit        |  |  |  |

| PD    | Power-Down bit  |  |  |  |

# PIC16(L)F1574/5/8/9

| CALL             | Call Subroutine                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                   |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                      |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<6:3>) → PC<14:11>                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                      |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| CLRWDT       | Clear Watchdog Timer                                                                                                              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:      | [ <i>label</i> ] CLRWDT                                                                                                           |

| Operands:    | None                                                                                                                              |

| Operation:   | $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$ $\overline{TO, PD}$ |

| Description: | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT.<br>Status bits TO and PD are set.  |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                  |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                 |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                  |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                                                                                           |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{•} \ &\text{FSR + 1 (preincrement)} \\ &\text{•} \ &\text{FSR - 1 (predecrement)} \\ &\text{•} \ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will be} \\ &\text{either:} \\ &\text{•} \ &\text{FSR + 1 (all increments)} \\ &\text{•} \ &\text{FSR - 1 (all decrements)} \\ &\text{•} \ &\text{Unchanged} \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

> **Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

#### MOVLB Move literal to BSR

Description:

| Syntax:          | [ <i>label</i> ]MOVLB k                                              |

|------------------|----------------------------------------------------------------------|

| Operands:        | $0 \leq k \leq 31$                                                   |

| Operation:       | $k \rightarrow BSR$                                                  |

| Status Affected: | None                                                                 |

| Description:     | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP            | Move literal to PCLATH                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]MOVLP k                                                                                   |

| Operands:        | $0 \le k \le 127$                                                                                         |

| Operation:       | $k \rightarrow PCLATH$                                                                                    |

| Status Affected: | None                                                                                                      |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register.                                                 |

| MOVLW            | Move literal to W                                                                                         |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                                  |

| Operands:        | $0 \le k \le 255$                                                                                         |

| Operation:       | $k \rightarrow (W)$                                                                                       |

| Status Affected: | None                                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W reg-<br>ister. The "don't cares" will assemble as '0's.            |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | MOVLW 0x5A                                                                                                |

|                  | After Instruction<br>W = 0x5A                                                                             |

|                  |                                                                                                           |

| MOVWF            | Move W to f                                                                                               |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                  |

| Operands:        | $0 \le f \le 127$                                                                                         |

| Operation:       | $(W) \to (f)$                                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to register<br>f'.                                                              |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | MOVWF OPTION_REG                                                                                          |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                 |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                      |

| Operands:        | $0 \le k \le 255$                                                                                             |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                              |

| Operands:        | $5 \le f \le 7$                                                                                                                                      |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |  |  |

## TABLE 27-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup> (CONTINUED)

| PIC16LF1  | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |                                  |          |       |        |          |            |                                    |  |

|-----------|-------------------------------------------------------------------------|----------------------------------|----------|-------|--------|----------|------------|------------------------------------|--|

| PIC16F157 | 74/5/8/9                                                                | Low-Power Sleep Mode, VREGPM = 1 |          |       |        |          |            |                                    |  |

| Param.    |                                                                         |                                  | <b>T</b> | Max.  | Max.   | L lucito | Conditions |                                    |  |

| No.       | Device Characteristics                                                  | Min.                             | Тур†     | +85°C | +125°C | Units    | Vdd        | Note                               |  |

| D027      |                                                                         | —                                | 5        | 22    | 25     | μA       | 1.8        | Comparator,                        |  |

|           |                                                                         | _                                | 5        | 23    | 27     | μA       | 3.0        | CxSP = 0                           |  |

| D027      |                                                                         | _                                | 15       | 23    | 25     | μA       | 2.3        | Comparator,                        |  |

|           |                                                                         | _                                | 17       | 27    | 29     | μA       | 3.0        | CxSP = 0                           |  |

|           |                                                                         | —                                | 19       | 28    | 30     | μA       | 5.0        |                                    |  |

| D028A     |                                                                         | _                                | 23       | 41    | 42     | μA       | 1.8        | Comparator,                        |  |

|           |                                                                         | —                                | 25       | 42    | 44     | μΑ       | 3.0        | Normal Power, CxSP = 1<br>(Note 1) |  |

| D028A     |                                                                         |                                  | 33       | 55    | 56     | μA       | 2.3        | Comparator,                        |  |

|           |                                                                         |                                  | 34       | 59    | 60     | μA       | 3.0        | Normal Power, $CxSP = 1$           |  |

|           |                                                                         | _                                | 36       | 60    | 61     | μA       | 5.0        | VREGPM = 1 (Note 1)                |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral ∆ current can be determined by subtracting the base IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC clock source is FRC.

\*

#### TABLE 27-15: COMPARATOR SPECIFICATIONS<sup>(1)</sup>

| Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |                      |                                           |      |      |      |       |                           |  |

|-------------------------------------------------------------------------|----------------------|-------------------------------------------|------|------|------|-------|---------------------------|--|

| Param.<br>No.                                                           | Sym.                 | Characteristics                           | Min. | Тур. | Max. | Units | Comments                  |  |

| CM01                                                                    | VIOFF                | Input Offset Voltage                      |      | ±7.5 | ±60  | mV    | CxSP = 1,<br>VICM = VDD/2 |  |

| CM02                                                                    | VICM                 | Input Common Mode Voltage                 | 0    |      | Vdd  | V     |                           |  |

| CM03                                                                    | CMRR                 | Common Mode Rejection Ration              | _    | 50   | _    | dB    |                           |  |

| CM04A                                                                   |                      | Response Time Rising Edge                 | _    | 400  | 800  | ns    | CxSP = 1                  |  |

| CM04B                                                                   | TRESP <sup>(2)</sup> | Response Time Falling Edge                | _    | 200  | 400  | ns    | CxSP = 1                  |  |

| CM04C                                                                   |                      | Response Time Rising Edge                 | _    | 1200 | _    | ns    | CxSP = 0                  |  |

| CM04D                                                                   |                      | Response Time Falling Edge                | _    | 550  | _    | ns    | CxSP = 0                  |  |

| CM05*                                                                   | Тмс2о∨               | Comparator Mode Change to<br>Output Valid | _    | —    | 10   | μS    |                           |  |

| CM06                                                                    | CHYSTER              | Comparator Hysteresis                     |      | 25   |      | mV    | CxHYS = 1,<br>CxSP = 1    |  |

\* These parameters are characterized but not tested.

Note 1: See Section 28.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

2: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

## TABLE 27-16: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS<sup>(1)</sup>

| Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |      |                              |      |        |       |       |          |  |

|-------------------------------------------------------------------------|------|------------------------------|------|--------|-------|-------|----------|--|

| Param.<br>No.                                                           | Sym. | Characteristics              | Min. | Тур.   | Max.  | Units | Comments |  |

| DAC01*                                                                  | CLSB | Step Size                    | —    | VDD/32 | _     | V     |          |  |

| DAC02*                                                                  | CACC | Absolute Accuracy            | —    | —      | ± 1/2 | LSb   |          |  |

| DAC03*                                                                  | CR   | Unit Resistor Value (R)      | —    | 5K     | _     | Ω     |          |  |

| DAC04*                                                                  | CST  | Settling Time <sup>(2)</sup> | _    | —      | 10    | μS    |          |  |

\* These parameters are characterized but not tested.

Note 1: See Section 28.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

**2:** Settling time measured while DACR<4:0> transitions from '0000' to '1111'.

# PIC16(L)F1574/5/8/9

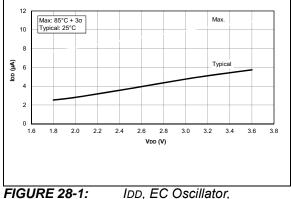

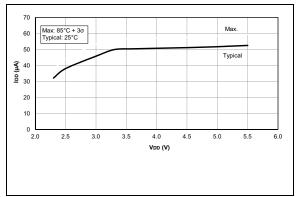

FIGURE 28-1: IDD, EC Oscillato Low-Power Mode, Fosc = 32 kHz, PIC16LF1574/5/8/9 Only.

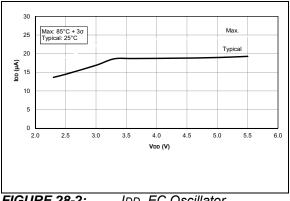

FIGURE 28-2: IDD, EC Oscillator, Low-Power Mode, Fosc = 32 kHz, PIC16F1574/5/8/9 Only.

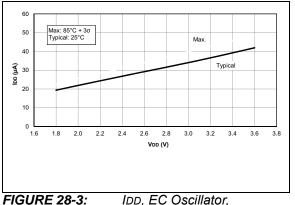

Low-Power Mode, Fosc = 500 kHz, PIC16LF1574/5/8/9 Only.

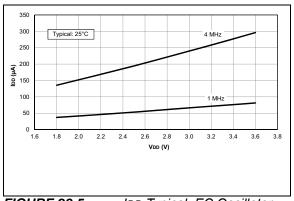

FIGURE 28-5:IDD Typical, EC Oscillator,Medium Power Mode, PIC16LF1574/5/8/9 Only.

FIGURE 28-4: IDD, EC Oscillator, Low-Power Mode, Fosc = 500 kHz, PIC16F1574/5/8/9 Only.

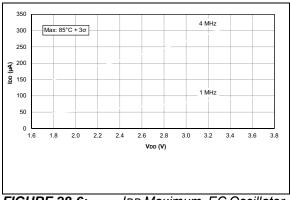

FIGURE 28-6: IDD Maximum, EC Oscillator, Medium Power Mode, PIC16LF1574/5/8/9 Only.