Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 14KB (8K × 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1579-i-gz |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

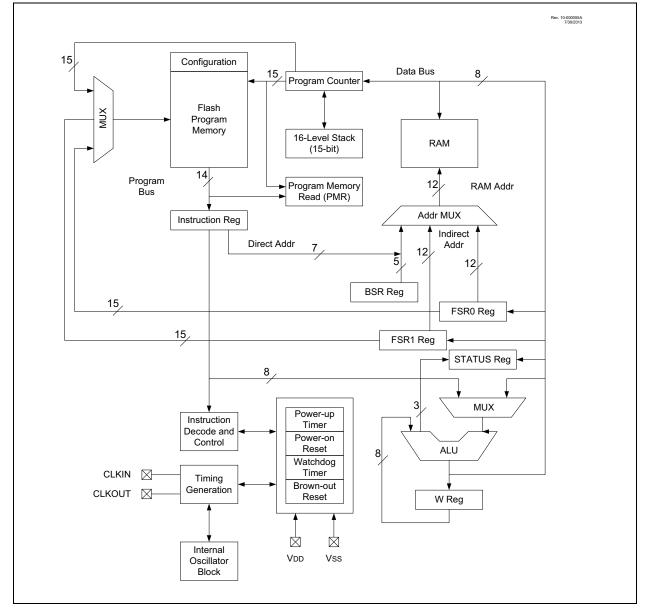

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

FIGURE 2-1: CORE BLOCK DIAGRAM

- Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

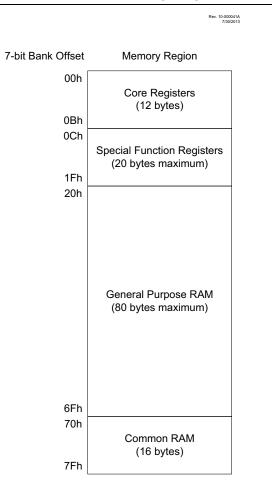

#### 3.3.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.3.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.3.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2** "Linear Data Memory" for more information.

#### 3.3.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### 3.3.5 DEVICE MEMORY MAPS

The memory maps are as shown in Table 3-3 through Table 3-13.

# FIGURE 3-3: BANKI

#### BANKED MEMORY PARTITIONING

#### TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address  | Name            | Bit 7         | Bit 6                                      | Bit 5        | Bit 4           | Bit 3          | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------|-----------------|---------------|--------------------------------------------|--------------|-----------------|----------------|--------|---------|--------|----------------------|---------------------------------|

| Bank 31  |                 |               |                                            |              |                 |                |        |         |        |                      |                                 |

| F8Ch     | —               | Unimpleme     | nted                                       |              |                 |                |        |         |        | -                    | —                               |

| <br>FE3h |                 |               |                                            |              |                 |                |        |         |        |                      |                                 |

| FE4h     | STATUS_<br>SHAD | _             | —                                          | —            | _               | _              | Z_SHAD | DC_SHAD | C_SHAD | xxx                  | uuu                             |

| FE5h     | WREG_<br>SHAD   | Working Re    | gister Shadov                              | N            |                 |                |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FE6h     | BSR_<br>SHAD    | —             | —                                          | —            | Bank Select R   | egister Shadow | 1      |         |        | x xxxx               | u uuuu                          |

| FE7h     | PCLATH_<br>SHAD | —             | Program Counter Latch High Register Shadow |              |                 |                |        |         |        |                      | uuuu uuuu                       |

| FE8h     | FSR0L_<br>SHAD  | Indirect Data | a Memory Ad                                | dress 0 Low  | Pointer Shadov  | N              |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FE9h     | FSR0H_<br>SHAD  | Indirect Date | a Memory Ad                                | dress 0 High | n Pointer Shado | W              |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEAh     | FSR1L_<br>SHAD  | Indirect Data | a Memory Ad                                | dress 1 Low  | Pointer Shadov  | N              |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEBh     | FSR1H_<br>SHAD  | Indirect Data | a Memory Ad                                | dress 1 High | n Pointer Shado | W              |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FECh     | —               | Unimpleme     | nted                                       |              |                 |                |        |         |        | -                    | —                               |

| FEDh     | STKPTR          | —             | —                                          | —            | Current Stack   | Pointer        |        |         |        | 1 1111               | 1 1111                          |

| FEEh     | TOSL            | Top-of-Stack  | k Low byte                                 |              |                 |                |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| FEFh     | TOSH            | _             | — Top-of-Stack High byte                   |              |                 |                |        |         |        |                      | -uuu uuuu                       |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.Note 1: PIC16(L)F1578/9 only.

2: PIC16F1574/5/8/9 only.

**3:** Unimplemented, read as '1'.

#### 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | х  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is set on POR                                         |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

#### TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

#### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

#### 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to Section 8.0 "Power-Down Mode (Sleep)" for more details.

#### 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

#### 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

PIC16(L)F1574/5/8/9

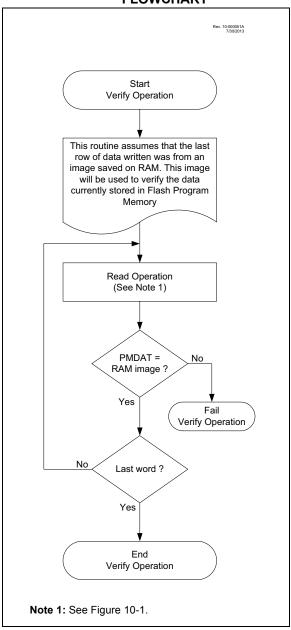

#### 10.5 Write Verify

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

| R/W-1/1                                                                                                                                                                                                                                                                                                      | R/W-1/1              | U-0               | U-0              | R/W-1/1                                                                  | R/W-1/1          | R/W-1/1        | R/W-1/1                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|------------------|--------------------------------------------------------------------------|------------------|----------------|----------------------------|--|--|

| ANSC7 <sup>(2)</sup>                                                                                                                                                                                                                                                                                         | ANSC6 <sup>(2)</sup> |                   | _                | ANSC3                                                                    | ANSC2            | ANSC1          | ANSC0                      |  |  |

| bit 7                                                                                                                                                                                                                                                                                                        |                      |                   |                  |                                                                          |                  |                | bit C                      |  |  |

|                                                                                                                                                                                                                                                                                                              |                      |                   |                  |                                                                          |                  |                |                            |  |  |

| Legend:                                                                                                                                                                                                                                                                                                      |                      |                   |                  |                                                                          |                  |                |                            |  |  |

| R = Readable                                                                                                                                                                                                                                                                                                 | bit                  | W = Writable      | bit              | U = Unimpler                                                             | nented bit, read | d as '0'       |                            |  |  |

| u = Bit is unch                                                                                                                                                                                                                                                                                              | nanged               | x = Bit is unkr   | nown             | -n/n = Value a                                                           | at POR and BC    | R/Value at all | other Resets               |  |  |

| '1' = Bit is set                                                                                                                                                                                                                                                                                             |                      | '0' = Bit is clea | ared             |                                                                          |                  |                |                            |  |  |

| bit 7-6                                                                                                                                                                                                                                                                                                      | 0 = Digital I/       | O. Pin is assigr  | ned to port or o | og or Digital Fu<br>digital special fu<br>og input <sup>(1)</sup> . Digi | inction.         |                | ectively <sup>(1, 2)</sup> |  |  |

| bit 5-4                                                                                                                                                                                                                                                                                                      | Unimplemen           | nted: Read as '   | 0'               |                                                                          |                  |                |                            |  |  |

| bit 3-0 <b>ANSC&lt;3:0&gt;</b> : Analog Select between Analog or Digital Function on pins RC<3:0>, respectively <sup>(1)</sup><br>0 = Digital I/O. Pin is assigned to port or digital special function.<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> . Digital input buffer disabled. |                      |                   |                  |                                                                          |                  |                |                            |  |  |

| Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to                                                                                                                                                                                              |                      |                   |                  |                                                                          |                  |                |                            |  |  |

allow external control of the voltage on the pin. 2: ANSC<7:6> are available on PIC16(L)F1578/9 only.

#### REGISTER 11-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| WPUC7 <sup>(3)</sup> | WPUC6 <sup>(3)</sup> | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(3)</sup>

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

3: WPUC<7:6> are available on PIC16(L)F1578/9 only.

#### 18.4 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section 27.0 "Electrical Specifications"** for more information.

#### 18.5 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 20.5 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 18.5.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from the Cx comparator can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 18-2) and the Timer1 Block Diagram (Figure 20-1) for more information.

#### 18.6 Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- · CxON and CxPOL bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

| Note: | Although a comparator is disabled, an      |

|-------|--------------------------------------------|

|       | interrupt can be generated by changing     |

|       | the output polarity with the CxPOL bit of  |

|       | the CMxCON0 register, or by switching      |

|       | the comparator on or off with the CxON bit |

|       | of the CMxCON0 register.                   |

#### 18.7 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 27.0 "Electrical Specifications"** for more details.

## 18.8 Register Definitions: Comparator Control

| R/W-0/0         | R-0/0           | U-0                                                                             | R/W-0/0                            | U-0             | R/W-1/1          | R/W-0/0        | R/W-0/0      |  |  |  |  |  |  |

|-----------------|-----------------|---------------------------------------------------------------------------------|------------------------------------|-----------------|------------------|----------------|--------------|--|--|--|--|--|--|

| CxON            | CxOUT           | _                                                                               | CxPOL                              | _               | CxSP             | CxHYS          | CxSYNC       |  |  |  |  |  |  |

| bit 7           |                 |                                                                                 |                                    |                 |                  |                | bit (        |  |  |  |  |  |  |

|                 |                 |                                                                                 |                                    |                 |                  |                |              |  |  |  |  |  |  |

| Legend:         |                 |                                                                                 |                                    |                 |                  |                |              |  |  |  |  |  |  |

| R = Readabl     |                 | W = Writable                                                                    | bit                                | •               | mented bit, read |                |              |  |  |  |  |  |  |

| u = Bit is und  | changed         | x = Bit is unk                                                                  | nown                               | -n/n = Value    | at POR and BC    | R/Value at all | other Resets |  |  |  |  |  |  |

| '1' = Bit is se | t               | '0' = Bit is cle                                                                | eared                              |                 |                  |                |              |  |  |  |  |  |  |

| bit 7           | CxON: Com       | parator Enable                                                                  | bit                                |                 |                  |                |              |  |  |  |  |  |  |

|                 |                 | ator is enabled ator is disabled                                                | and consumes                       | s no active pov | ver              |                |              |  |  |  |  |  |  |

| bit 6           |                 |                                                                                 |                                    |                 | -                |                |              |  |  |  |  |  |  |

|                 |                 | <b>CxOUT:</b> Comparator Output bit<br><u>If CxPOL = 1 (inverted polarity):</u> |                                    |                 |                  |                |              |  |  |  |  |  |  |

|                 | 1 = CxVP < CxVN |                                                                                 |                                    |                 |                  |                |              |  |  |  |  |  |  |

|                 | 0 = CxVP > CxVN |                                                                                 |                                    |                 |                  |                |              |  |  |  |  |  |  |

|                 |                 | If CxPOL = 0 (non-inverted polarity):                                           |                                    |                 |                  |                |              |  |  |  |  |  |  |

|                 | 1 = CxVP >      |                                                                                 |                                    |                 |                  |                |              |  |  |  |  |  |  |

|                 | 0 = CxVP <      |                                                                                 |                                    |                 |                  |                |              |  |  |  |  |  |  |

| bit 5           | -               | nted: Read as                                                                   |                                    |                 |                  |                |              |  |  |  |  |  |  |

| bit 4           |                 | CxPOL: Comparator Output Polarity Select bit                                    |                                    |                 |                  |                |              |  |  |  |  |  |  |

|                 |                 | tor output is in                                                                |                                    |                 |                  |                |              |  |  |  |  |  |  |

|                 | -               | ator output is n                                                                |                                    |                 |                  |                |              |  |  |  |  |  |  |

| bit 3           | Unimpleme       | nted: Read as                                                                   | '0'                                |                 |                  |                |              |  |  |  |  |  |  |

| bit 2           |                 | •                                                                               | Power Select b                     |                 |                  |                |              |  |  |  |  |  |  |

|                 |                 |                                                                                 | ormal power, hig<br>w-power, low-s |                 |                  |                |              |  |  |  |  |  |  |

| bit 1           | CxHYS: Con      | nparator Hyste                                                                  | resis Enable bi                    | t               |                  |                |              |  |  |  |  |  |  |

|                 |                 | ator hysteresis                                                                 |                                    |                 |                  |                |              |  |  |  |  |  |  |

|                 |                 | ator hysteresis                                                                 |                                    |                 |                  |                |              |  |  |  |  |  |  |

| bit 0           | CxSYNC: Co      | omparator Out                                                                   | out Synchronou                     | is Mode bit     |                  |                |              |  |  |  |  |  |  |

|                 |                 |                                                                                 |                                    |                 | onous to chang   | es on Timer1   | clock source |  |  |  |  |  |  |

|                 |                 |                                                                                 | falling edge of                    |                 |                  | ,              |              |  |  |  |  |  |  |

|                 |                 |                                                                                 | Fimer1 and I/O                     |                 |                  |                |              |  |  |  |  |  |  |

#### **REGISTER 18-1:** CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

#### 20.6 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

**Note:** The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 20.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- · TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the  $\overline{\text{T1SYNC}}$  bit setting.

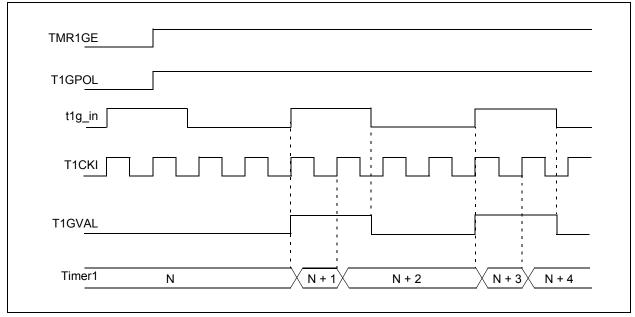

#### FIGURE 20-3: TIMER1 GATE ENABLE MODE

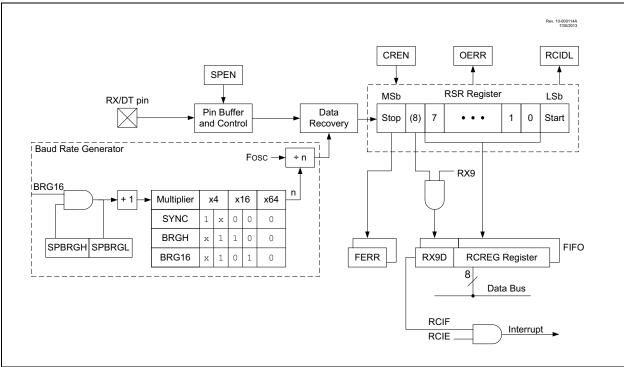

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

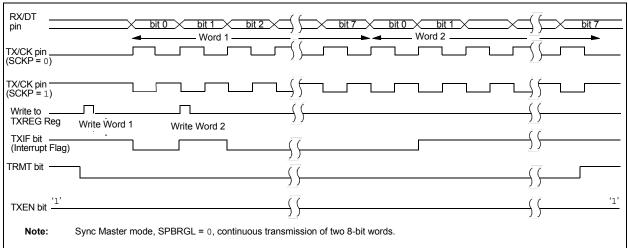

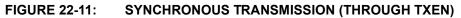

#### FIGURE 22-10: SYNCHRONOUS TRANSMISSION

# TABLE 22-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |  |  |

|---------|-------------------------------|-----------|--------|-------|-------|--------|--------|--------|---------------------|--|--|

| BAUDCON | ABDOVF                        | RCIDL     | —      | SCKP  | BRG16 | —      | WUE    | ABDEN  | 204                 |  |  |

| INTCON  | GIE                           | PEIE      | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |  |  |

| PIE1    | TMR1GIE                       | ADIE      | RCIE   | TXIE  | _     | —      | TMR2IE | TMR1IE | 87                  |  |  |

| PIR1    | TMR1GIF                       | ADIF      | RCIF   | TXIF  | _     | —      | TMR2IF | TMR1IF | 90                  |  |  |

| RCSTA   | SPEN                          | RX9       | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 203                 |  |  |

| SPBRGL  |                               |           |        | BRG   | <7:0> |        |        |        | 205*                |  |  |

| SPBRGH  |                               | BRG<15:8> |        |       |       |        |        |        |                     |  |  |

| TXREG   | EUSART Transmit Data Register |           |        |       |       |        |        |        |                     |  |  |

| TXSTA   | CSRC                          | TX9       | TXEN   | SYNC  | SENDB | BRGH   | TRMT   | TX9D   | 202                 |  |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission.

\* Page provides register information.

| U-0                                                                                                                                  | U-0                                                         | U-0                                                                      | U-0                   | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0   |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|-----------------|-------------------|------------------|-----------|

| _                                                                                                                                    | _                                                           | _                                                                        | —                     | OFIE            | PHIE              | DCIE             | PRIE      |

| bit 7                                                                                                                                |                                                             |                                                                          |                       |                 |                   |                  | bit 0     |

| [                                                                                                                                    |                                                             |                                                                          |                       |                 |                   |                  |           |

| Legend:                                                                                                                              |                                                             |                                                                          |                       |                 |                   |                  |           |

| R = Readable                                                                                                                         | e bit                                                       | W = Writable b                                                           | it                    | U = Unimpleme   | ented bit, read a | is '0'           |           |

| u = Bit is unc                                                                                                                       | hanged                                                      | x = Bit is unkno                                                         | own                   | -n/n = Value at | POR and BOR       | Value at all oth | er Resets |

| '1' = Bit is set                                                                                                                     | t                                                           | '0' = Bit is clea                                                        | red                   |                 |                   |                  |           |

| bit 7-4<br>bit 3                                                                                                                     | <b>OFIE</b> : Offset I<br>1 = Interrupt (<br>0 = Do not int | ed: Read as '0'<br>nterrupt Enable<br>CPU on Offset M<br>errupt CPU on 0 | latch<br>Offset Match |                 |                   |                  |           |

| bit 2                                                                                                                                | 1 = Interrupt C                                             | Interrupt Enable<br>CPU on Phase N<br>errupt CPU on N                    | /latch                |                 |                   |                  |           |

| bit 1 DCIE: Duty Cycle Interrupt Enable bit<br>1 = Interrupt CPU on Duty Cycle Match<br>0 = Do not interrupt CPU on Duty Cycle Match |                                                             |                                                                          |                       |                 |                   |                  |           |

| bit 0                                                                                                                                | 1 = Interrupt (                                             | Interrupt Enable<br>CPU on Period I<br>errupt CPU on I                   | Match                 |                 |                   |                  |           |

#### **REGISTER 23-2: PWMxINTE: PWM INTERRUPT ENABLE REGISTER**

#### REGISTER 23-3: PWMxINTF: PWM INTERRUPT REQUEST REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|------------|------------|------------|------------|

|       |     | _   | _   | OFIF       | PHIF       | DCIF       | PRIF       |

| bit 7 | •   |     |     | •          | •          |            | bit 0      |

| Legend:                    |                      |                                                       |  |  |  |  |

|----------------------------|----------------------|-------------------------------------------------------|--|--|--|--|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |  |  |  |  |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is unchanged       | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is set           | '0' = Bit is cleared |                                                       |  |  |  |  |

| bit 7-4 | Unimplemented: Read as '0'                                           |

|---------|----------------------------------------------------------------------|

| bit 3   | OFIF: Offset Interrupt Flag bit <sup>(1)</sup>                       |

|         | 1 = Offset Match Event occurred                                      |

|         | 0 = Offset Match Event did not occur                                 |

| bit 2   | PHIF: Phase Interrupt Flag bit <sup>(1)</sup>                        |

|         | 1 = Phase Match Event occurred                                       |

|         | 0 = Phase Match Event did not occur                                  |

| bit 1   | DCIF: Duty Cycle Interrupt Flag bit <sup>(1)</sup>                   |

|         | 1 = Duty Cycle Match Event occurred                                  |

|         | 0 = Duty Cycle Match Event did not occur                             |

| bit 0   | PRIF: Period Interrupt Flag bit <sup>(1)</sup>                       |

|         | 1 = Period Match Event occurred                                      |

|         | 0 = Period Match Event did not occur                                 |

| Note 1: | Bit is forced clear by hardware while module is disabled (EN = $0$ ) |

Bit is forced clear by hardware while module is disabled (EN = 0).

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                        |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                 |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                      |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                             |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow$ (W)                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                              |

| Operands:        | $5 \le f \le 7$                                                                                                                                      |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

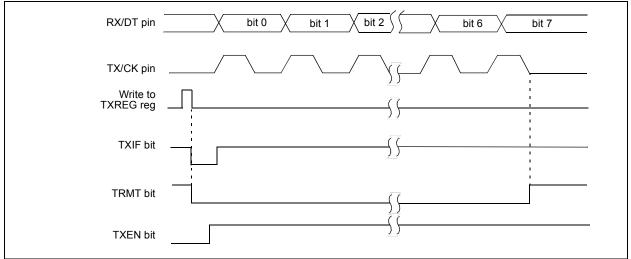

## TABLE 27-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |      |                                         |      |      |      |       |                      |  |

|---------------------------------------------------------|------|-----------------------------------------|------|------|------|-------|----------------------|--|

| Param.<br>No.                                           | Sym. | Characteristic                          | Min. | Тур† | Max. | Units | Conditions           |  |

| OS01                                                    | Fosc | External CLKIN Frequency <sup>(1)</sup> | DC   | —    | 0.5  | MHz   | External Clock (ECL) |  |

|                                                         |      |                                         | DC   | —    | 4    | MHz   | External Clock (ECM) |  |

|                                                         |      |                                         | DC   | —    | 20   | MHz   | External Clock (ECH) |  |

| OS02                                                    | Tosc | External CLKIN Period <sup>(1)</sup>    | 50   | —    | 8    | ns    | External Clock (EC)  |  |

| OS03                                                    | Тсү  | Instruction Cycle Time <sup>(1)</sup>   | 200  | TCY  | DC   | ns    | Tcy = 4/Fosc         |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

# PIC16(L)F1574/5/8/9

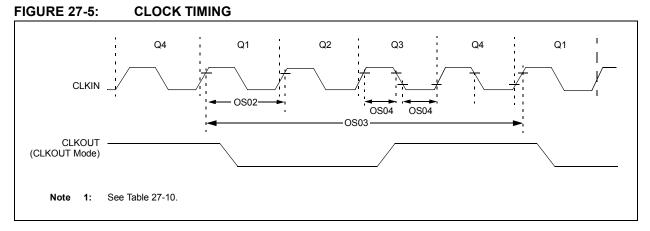

**FIGURE 28-37:** Voh vs. Ioh Over Temperature, VDD = 3.0V.

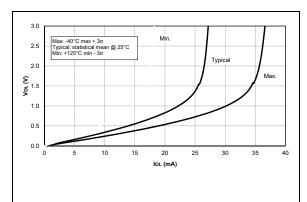

FIGURE 28-38: VOL vs. IOL Over Temperature, VDD = 3.0V.

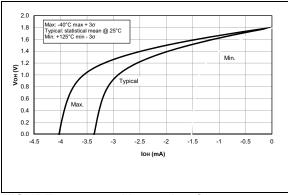

FIGURE 28-39: Voн vs. Ioн Over Temperature, Vod = 1.8V, PIC16LF1574/5/8/9 Only.

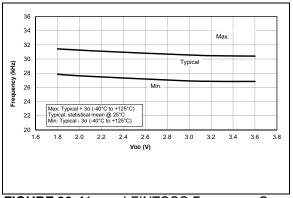

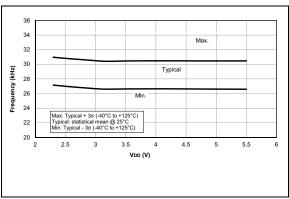

FIGURE 28-41: LFINTOSC Frequency Over VDD and Temperature, PIC16LF1574/5/8/9 Only.

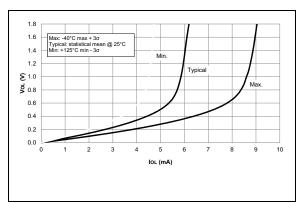

**FIGURE 28-40:** VoL vs. IoL Over Temperature, VDD = 1.8V, PIC16LF1574/5/8/9 Only.

FIGURE 28-42: LFINTOSC Frequency Over VDD and Temperature, PIC16F1574/5/8/9 Only.

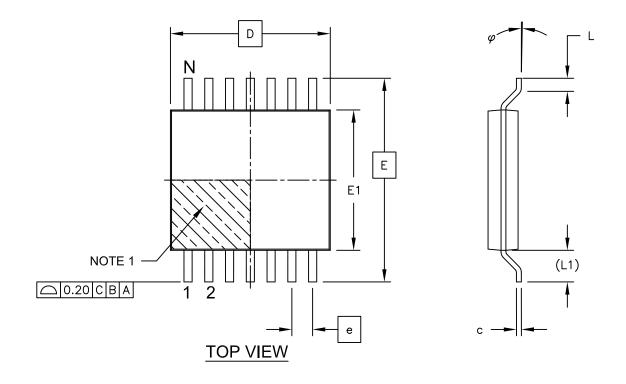

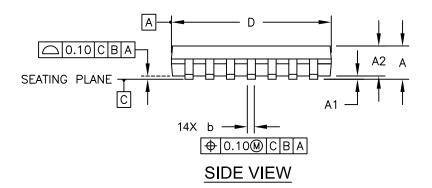

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |  |

|--------------------------|-------------|----------|------|------|--|

| Dimension                | Limits      | MIN      | NOM  | MAX  |  |

| Number of Pins           | N           | 14       |      |      |  |

| Pitch                    | е           | 0.65 BSC |      |      |  |

| Overall Height           | А           | I        | -    | 1.20 |  |

| Molded Package Thickness | A2          | 0.80     | 1.00 | 1.05 |  |

| Standoff                 | A1          | 0.05     | -    | 0.15 |  |

| Overall Width            | E           | 6.40 BSC |      |      |  |

| Molded Package Width     | E1          | 4.30     | 4.40 | 4.50 |  |

| Molded Package Length    | D           | 4.90     | 5.00 | 5.10 |  |

| Foot Length              | L           | 0.45     | 0.60 | 0.75 |  |

| Footprint                | (L1)        | 1.00 REF |      |      |  |

| Foot Angle               | φ           | 0°       | -    | 8°   |  |

| Lead Thickness           | С           | 0.09     | -    | 0.20 |  |

| Lead Width               | b           | 0.19     | -    | 0.30 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2

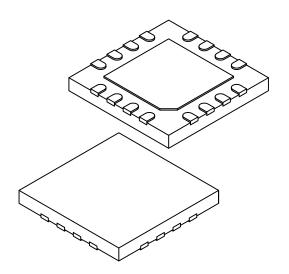

#### 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |          |      |  |  |

|-------------------------|-------------|-----------|----------|------|--|--|

| Dimension               | Limits      | MIN       | NOM      | MAX  |  |  |

| Number of Pins          | N           |           | 16       |      |  |  |

| Pitch                   | е           |           | 0.65 BSC |      |  |  |

| Overall Height          | Α           | 0.45      | 0.50     | 0.55 |  |  |

| Standoff                | A1          | 0.00      | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.127 REF |          |      |  |  |

| Overall Width           | E           | 4.00 BSC  |          |      |  |  |

| Exposed Pad Width       | E2          | 2.50      | 2.60     | 2.70 |  |  |

| Overall Length          | D           | 4.00 BSC  |          |      |  |  |

| Exposed Pad Length      | D2          | 2.50      | 2.60     | 2.70 |  |  |

| Terminal Width          | b           | 0.25      | 0.30     | 0.35 |  |  |

| Terminal Length         | L           | 0.30      | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | К           | 0.20      | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-257A Sheet 2 of 2