# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | LINbus, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1579-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.2.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | JDEX                |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

|                   |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

# 3.2.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH operator will set bit<7> if a label points to a location in program memory.

# EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constant | s             |                               |

|----------|---------------|-------------------------------|

| DW       | DATA0         | ;First constant               |

| DW       | DATA1         | ;Second constant              |

| DW       | DATA2         |                               |

| DW       | DATA3         |                               |

| my_funct | ion           |                               |

| ; LOT    | S OF CODE     |                               |

| MOVLW    | DATA_INDEX    |                               |

| ADDLW    | LOW constant  | s                             |

| MOVWF    | FSR1L         |                               |

| MOVLW    | HIGH constan  | nts;MSb is set                |

|          |               | automatically                 |

| MOVWF    | FSR1H         |                               |

| BTFSC    | STATUS, C     | <pre>;carry from ADDLW?</pre> |

| INCF     | FSR1H,f       | ;yes                          |

| MOVIW    | 0[FSR1]       |                               |

| ;THE PRO | GRAM MEMORY I | S IN W                        |

|          |               |                               |

# TABLE 3-6: PIC16(L)F1579 MEMORY MAP, BANKS 0-7

|              | BANK0                                      | •            | ,<br>BANK1                                 |              | BANK2                                      |              | BANK3                                      |              | BANK4                                      |              | BANK5                                      |              | BANK6                                      |              | BANK7                                      |

|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|

| 000h         | Core Registers<br>(Table 3-2)              | 080h         | Core Registers<br>(Table 3-2)              | 100h         | Core Registers<br>(Table 3-2)              | 180h         | Core Registers<br>(Table 3-2)              | 200h         | Core Registers<br>(Table 3-2)              | 280h         | Core Registers<br>(Table 3-2)              | 300h         | Core Registers<br>(Table 3-2)              | 380h         | Core Registers<br>(Table 3-2)              |

| 00Bh         |                                            | 08Bh         |                                            | 10Bh         |                                            | 18Bh         |                                            | 20Bh         |                                            | 28Bh         |                                            | 30Bh         |                                            | 38Bh         |                                            |

| 00Ch         | PORTA                                      | 08Ch         | TRISA                                      | 10Ch         | LATA                                       | 18Ch         | ANSELA                                     | 20Ch         | WPUA                                       | 28Ch         | ODCONA                                     | 30Ch         | SLRCONA                                    | 38Ch         | INLVLA                                     |

| 00Dh         | PORTB                                      | 08Dh         | TRISB                                      | 10Dh         | LATB                                       | 18Dh         | ANSELB                                     | 20Dh         | WPUB                                       | 28Dh         | ODCONB                                     | 30Dh         | SLRCONB                                    | 38Dh         | INLVLB                                     |

| 00Eh         | PORTC                                      | 08Eh         | TRISC                                      | 10Eh         | LATC                                       | 18Eh         | ANSELC                                     | 20Eh         | WPUC                                       | 28Eh         | ODCONC                                     | 30Eh         | SLRCONC                                    | 38Eh         | INLVLC                                     |

| 00Fh         | —                                          | 08Fh         | _                                          | 10Fh         | —                                          | 18Fh         | _                                          | 20Fh         | —                                          | 28Fh         |                                            | 30Fh         |                                            | 38Fh         | —                                          |

| 010h         | —                                          | 090h         | -                                          | 110h         | —                                          | 190h         | —                                          | 210h         | —                                          | 290h         | —                                          | 310h         | —                                          | 390h         | —                                          |

| 011h         | PIR1                                       | 091h         | PIE1                                       | 111h         | CM1CON0                                    | 191h         | PMADRL                                     | 211h         | —                                          | 291h         | —                                          | 311h         | —                                          | 391h         | IOCAP                                      |

| 012h         | PIR2                                       | 092h         | PIE2                                       | 112h         | CM1CON1                                    | 192h         | PMADRH                                     | 212h         | —                                          | 292h         | —                                          | 312h         | —                                          | 392h         | IOCAN                                      |

| 013h         | PIR3                                       | 093h         | PIE3                                       | 113h         | CM2CON0                                    | 193h         | PMDATL                                     | 213h         | —                                          | 293h         |                                            | 313h         |                                            | 393h         | IOCAF                                      |

| 014h         | —                                          | 094h         | _                                          | 114h         | CM2CON1                                    | 194h         | PMDATH                                     | 214h         | —                                          | 294h         |                                            | 314h         |                                            | 394h         | IOCBP                                      |

| 015h         | TMR0                                       | 095h         | OPTION_REG                                 | 115h         | CMOUT                                      | 195h         | PMCON1                                     | 215h         | —                                          | 295h         | —                                          | 315h         | —                                          | 395h         | IOCBN                                      |

| 016h         | TMR1L                                      | 096h         | PCON                                       | 116h         | BORCON                                     | 196h         | PMCON2                                     | 216h         | —                                          | 296h         | _                                          | 316h         | _                                          | 396h         | IOCBF                                      |

| 017h         | TMR1H                                      | 097h         | WDTCON                                     | 117h         | FVRCON                                     | 197h         | VREGCON <sup>(1)</sup>                     | 217h         | _                                          | 297h         | _                                          | 317h         | _                                          | 397h         | IOCCP                                      |

| 018h         | T1CON                                      | 098h         | OSCTUNE                                    | 118h         | DACCON0                                    | 198h         | _                                          | 218h         |                                            | 298h         |                                            | 318h         |                                            | 398h         | IOCCN                                      |

| 019h         | T1GCON                                     | 099h         | OSCCON                                     | 119h         | DACCON1                                    | 199h         | RCREG                                      | 219h         | _                                          | 299h         | —                                          | 319h         | —                                          | 399h         | IOCCF                                      |

| 01Ah         | TMR2                                       | 09Ah         | OSCSTAT                                    | 11Ah         | _                                          | 19Ah         | TXREG                                      | 21Ah         | _                                          | 29Ah         | —                                          | 31Ah         | —                                          | 39Ah         | _                                          |

| 01Bh         | PR2                                        | 09Bh         | ADRESL                                     | 11Bh         | _                                          | 19Bh         | SPBRGL                                     | 21Bh         | _                                          | 29Bh         | _                                          | 31Bh         | _                                          | 39Bh         | _                                          |

| 01Ch         | T2CON                                      | 09Ch         | ADRESH                                     | 11Ch         | —                                          | 19Ch         | SPBRGH                                     | 21Ch         | —                                          | 29Ch         |                                            | 31Ch         |                                            | 39Ch         | —                                          |

| 01Dh         | —                                          | 09Dh         | ADCON0                                     | 11Dh         | —                                          | 19Dh         | RCSTA                                      | 21Dh         | —                                          | 29Dh         | —                                          | 31Dh         | —                                          | 39Dh         | —                                          |

| 01Eh         | —                                          | 09Eh         | ADCON1                                     | 11Eh         | —                                          | 19Eh         | TXSTA                                      | 21Eh         | —                                          | 29Eh         | —                                          | 31Eh         | —                                          | 39Eh         | —                                          |

| 01Fh         | _                                          | 09Fh         | ADCON2                                     | 11Fh         | _                                          | 19Fh         | BAUDCON                                    | 21Fh         | _                                          | 29Fh         | _                                          | 31Fh         | _                                          | 39Fh         | _                                          |

| 020h         |                                            | 0A0h         |                                            | 120h         |                                            | 1A0h         |                                            | 220h         |                                            | 2A0h         |                                            | 320h         |                                            | 3A0h         |                                            |

|              | General<br>Purpose<br>Register<br>80 Bytes |

| 06Fh         |                                            | 0EFh         |                                            | 16Fh         |                                            | 1EFh         |                                            | 26Fh         |                                            | 2EFh         |                                            | 36Fh         |                                            | 3EFh         |                                            |

| 070h<br>07Fh | Common RAM                                 | 0F0h<br>0FFh | Accesses<br>70h – 7Fh                      | 170h<br>17Fh | Accesses<br>70h – 7Fh                      | 1F0h<br>1FFh | Accesses<br>70h – 7Fh                      | 270h<br>27Fh | Accesses<br>70h – 7Fh                      | 2F0h<br>2FFh | Accesses<br>70h – 7Fh                      | 370h<br>37Fh | Accesses<br>70h – 7Fh                      | 3F0h<br>3FFh | Accesses<br>70h – 7Fh                      |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1579.

| TABLE 3-15: | SPECIAL FUNCTION REGISTER SUMMARY ( | (CONTINUED) | ) |

|-------------|-------------------------------------|-------------|---|

|-------------|-------------------------------------|-------------|---|

| Address | Name                 | Bit 7                 | Bit 6                 | Bit 5    | Bit 4    | Bit 3     | Bit 2        | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------|-----------------------|-----------------------|----------|----------|-----------|--------------|---------|---------|----------------------|---------------------------------|

| Bank 1  |                      |                       |                       |          |          |           |              |         |         |                      |                                 |

| 08Ch    | TRISA                | _                     | _                     | TRISA5   | TRISA4   | (3)       | TRISA2       | TRISA1  | TRISA0  | 11 1111              | 11 1111                         |

| 08Dh    | TRISB <sup>(1)</sup> | TRISB7                | TRISB6                | TRISB5   | TRISB4   | —         | —            | —       | —       | 1111                 | 1111                            |

| 08Eh    | TRISC                | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4   | TRISC3    | TRISC2       | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

| 08Fh    | —                    | Unimplemen            | nted                  |          |          |           |              |         |         | _                    | _                               |

| 090h    | —                    | Unimplemen            | nted                  |          |          |           |              |         |         | _                    | _                               |

| 091h    | PIE1                 | TMR1GIE               | ADIE                  | RCIE     | TXIE     | —         | —            | TMR2IE  | TMR1IE  | 000000               | 000000                          |

| 092h    | PIE2                 | _                     | C2IE                  | C1IE     | —        | —         | —            | —       | _       | -00                  | -00                             |

| 093h    | PIE3                 | PWM4IE                | PWM3IE                | PWM2IE   | PWM1IE   | —         | —            | —       | _       | 0000                 | 0000                            |

| 094h    | —                    |                       |                       |          |          |           |              |         |         | —                    | —                               |

| 095h    | OPTION_REG           | WPUEN                 | INTEDG                | TMR0CS   | TMR0SE   | PSA       |              | PS<2:0> |         | 1111 1111            | 1111 1111                       |

| 096h    | PCON                 | STKOVF                | STKUNF                | _        | RWDT     | RMCLR     | RI           | POR     | BOR     | 00-1 11qq            | qq-q qquu                       |

| 097h    | WDTCON               | _                     | _                     |          |          | WDTPS<4:0 | >            |         | SWDTEN  | 01 0110              | 01 0110                         |

| 098h    | OSCTUNE              | _                     | _                     |          |          | TU        | N<5:0>       |         |         | 00 0000              | 00 0000                         |

| 099h    | OSCCON               | SPLLEN                |                       | IRO      | CF<3:0>  |           | _            | SCS     | <1:0>   | 0011 1-00            | 0011 1-00                       |

| 09Ah    | OSCSTAT              | _                     | PLLR                  | OSTS     | HFIOFR   | HFIOFL    | MFIOFR       | LFIOFR  | HFIOFS  | -0q0 0q00            | -ববর বরবর                       |

| 09Bh    | ADRESL               | ADC Result            | Register Lov          | v        |          |           |              |         |         |                      | uuuu uuuu                       |

| 09Ch    | ADRESH               | ADC Result            | Register Hig          |          |          |           |              |         |         | xxxx xxxx            | uuuu uuuu                       |

| 09Dh    | ADCON0               | _                     |                       |          | CHS<4:0> | <b>`</b>  | GO/DONE ADON |         |         | -000 0000            | -000 0000                       |

| 09Eh    | ADCON1               | ADFM                  |                       | ADCS<2:0 | >        | —         | _            | ADPRE   | EF<1:0> | 000000               | 000000                          |

| 09Fh    | ADCON2               |                       | TRIGS                 | SEL<3:0> |          | _         | _            | _       | _       | 0000                 | 0000                            |

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3:

Unimplemented, read as '1'.

| Address            | Name        | Bit 7          | Bit 6            | Bit 5   | Bit 4 | Bit 3    | Bit 2         | Bit 1    | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------------------|-------------|----------------|------------------|---------|-------|----------|---------------|----------|-----------|----------------------|---------------------------------|

| Bank 27            | (Continued) |                |                  |         |       |          |               |          |           |                      |                                 |

| DC9h               | PWM4TMRL    |                |                  |         | -     | TMR<7:0> |               |          |           | xxxx xxxx            | uuuu uuuu                       |

| DCAh               | PWM4TMRH    |                |                  |         | Т     | MR<15:8> |               |          |           | xxxx xxxx            | uuuu uuuu                       |

| DCBh               | PWM4CON     | EN             | —                | OUT     | POL   | MODE     | E<1:0>        | _        | —         | 0000 00              | 0000 00                         |

| DCCh               | PWM4INTE    | —              | —                | —       | —     | OFIE     | PHIE          | DCIE     | PRIE      | 000                  | 000                             |

| DCDh               | PWM4INTF    | —              | —                | —       | —     | OFIF     | PHIF          | DCIF     | PRIF      | 000                  | 000                             |

| DCEh               | PWM4CLKCON  | —              |                  | PS<2:0> |       | _        | —             | CS∢      | <1:0>     | -000 -000            | -00000                          |

| DCFh               | PWM4LDCON   | LDA            | LDT              | —       | —     | —        | —             | LDS      | <1:0>     | 00000                | 0000                            |

| DD0h               | PWM40FCON   | —              | OFM              | <1:0>   | OFO   | _        | —             | OFS      | <1:0>     | -000 -000            | -00000                          |

| DD1h<br>to<br>DEFh | _           | Unimplemented  |                  |         |       |          |               |          |           | _                    |                                 |

| Bank 28            |             |                |                  |         |       |          |               |          |           |                      |                                 |

| E0Ch               |             |                |                  |         |       |          |               |          |           |                      |                                 |

| E0Eh               | -           | Unimplemen     | ited             |         |       |          |               |          |           | —                    | _                               |

| E0Fh               | PPSLOCK     | —              | —                | _       | —     | _        | _             | —        | PPSLOCKED | 0                    | 0                               |

| E10h               | INTPPS      | _              | _                | _       |       | •        | INTPPS<4:0>   |          |           | 0 0010               | u uuuu                          |

| E11h               | TOCKIPPS    | _              | _                | _       |       |          | T0CKIPPS<4:0> | >        |           | 0 0010               | u uuuu                          |

| E12h               | T1CKIPPS    | _              | _                | _       |       |          | T1CKIPPS<4:0> | <b>`</b> |           | 0 0101               | u uuuu                          |

| E13h               | T1GPPS      | _              | _                | _       |       |          | T1GPPS<4:0>   |          |           | 0 0100               | u uuuu                          |

| E14h               | CWG1INPPS   | _              | _                | _       |       |          | CWGINPPS<4:0  | >        |           | 0 0010               | u uuuu                          |

| E15h               | RXPPS       |                |                  |         |       |          |               |          | 1 0101    | u uuuu               |                                 |

| E16h               | CKPPS       | _              | — — — CKPPS<4:0> |         |       |          |               |          |           | 1 0101               | u uuuu                          |

| E17h               | ADCACTPPS   | ADCACTPPS<4:0> |                  |         |       |          |               |          | 1 0101    | u uuuu               |                                 |

| E18h<br>to<br>E6Fh | _           | Unimplemer     | nted             |         |       |          |               |          |           | —                    | _                               |

# TABLE 3-15: SPECIAL EUNCTION DEGISTED SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

DS40001782C-page 45

# 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

# 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- · BOR is always off

Refer to Table 6-1 for more information.

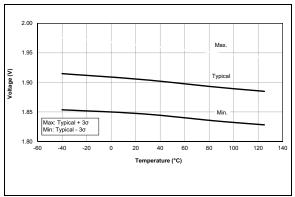

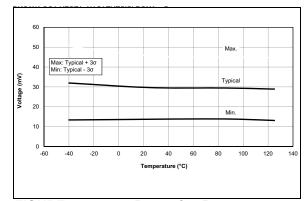

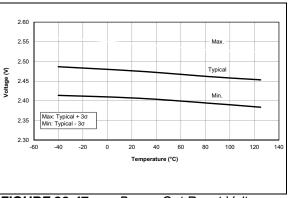

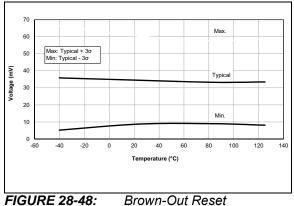

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 1.0        | 37     | Awake       | Active   | Waits for BOR ready (BORRDY = 1)                                    |

| 10         | Х      | Sleep       | Disabled |                                                                     |

| 0.1        | 1      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 01         | 0      | х           | Disabled | Begins immediately (BORRDY = x)                                     |

| 00         | Х      | Х           | Disabled |                                                                     |

#### TABLE 6-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

# 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

# 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

# 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

|                       | D 0/0                 | D 0/0                 | D 0/0                  | 11.0           |                   | 11.0             |             |

|-----------------------|-----------------------|-----------------------|------------------------|----------------|-------------------|------------------|-------------|

| R-0/0                 | R-0/0                 | R-0/0                 | R-0/0                  | U-0            | U-0               | U-0              | U-0         |

| PWM4IF <sup>(1)</sup> | PWM3IF <sup>(1)</sup> | PWM2IF <sup>(1)</sup> | PWM1IF <sup>(1)</sup>  | —              | —                 | —                | _           |

| bit 7                 |                       |                       |                        |                |                   |                  | bit 0       |

|                       |                       |                       |                        |                |                   |                  |             |

| Legend:               |                       |                       |                        |                |                   |                  |             |

| R = Readable          | bit                   | W = Writable          | bit                    | U = Unimpler   | mented bit, read  | as '0'           |             |

| u = Bit is unch       | nanged                | x = Bit is unkr       | nown                   | -n/n = Value   | at POR and BOI    | R/Value at all o | ther Resets |

| '1' = Bit is set      |                       | '0' = Bit is cle      | ared                   |                |                   |                  |             |

|                       |                       |                       |                        |                |                   |                  |             |

| bit 7                 | PWM4IF: PW            | /M4 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt i       | is pending            |                        |                |                   |                  |             |

|                       | 0 = Interrupt         | is not pending        |                        |                |                   |                  |             |

| bit 6                 | PWM3IF: PW            | /M3 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt         | is pending            |                        |                |                   |                  |             |

|                       | 0 = Interrupt         | is not pending        |                        |                |                   |                  |             |

| bit 5                 | PWM2IF: PW            | /M2 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt         |                       |                        |                |                   |                  |             |

|                       | 0 = Interrupt         | is not pending        |                        |                |                   |                  |             |

| bit 4                 | PWM1IF: PW            | /M1 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt         | is pending            |                        |                |                   |                  |             |

|                       | 0 = Interrupt         | is not pending        |                        |                |                   |                  |             |

| bit 3-0               | Unimplemen            | nted: Read as '       | 0'                     |                |                   |                  |             |

| Note 1. Th            | oso hits aro roa      | d only Thoy m         | ust be cleared         | l by addragain | a the Flee regist | ora inaida tha n | aadula      |

# REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

- Note 1: These bits are read-only. They must be cleared by addressing the Flag registers inside the module.

- 2: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

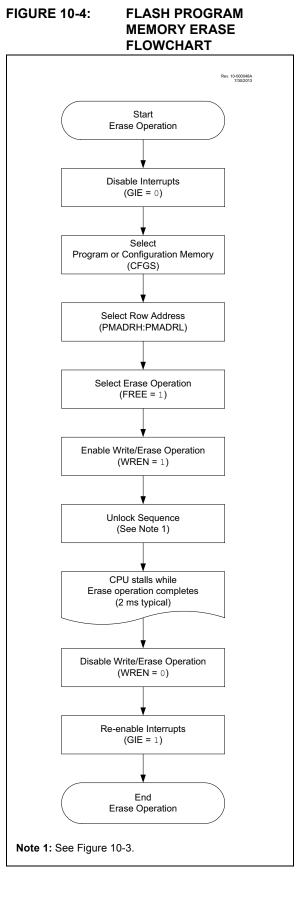

# 10.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

See Example 10-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

| U-1           | R/W-0/0             | R/W-0/0                                   | R/W/HC-0/0            | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0           | R/S/HC-0/0           | R/S/HC-0/0       |

|---------------|---------------------|-------------------------------------------|-----------------------|---------------------------|-------------------|----------------------|------------------|

| (1)           | CFGS                | LWLO <sup>(3)</sup>                       | FREE                  | WRERR                     | WREN              | WR                   | RD               |

| bit 7         |                     |                                           |                       |                           |                   |                      | bit (            |

| Legend:       |                     |                                           |                       |                           |                   |                      |                  |

| R = Reada     | able bit            | W = Writable b                            | it                    | U = Unimpleme             | nted bit, read as | s 'O'                |                  |

|               | n only be set       | x = Bit is unkno                          |                       | •                         | -                 | √alue at all other Ⅰ | Resets           |

| '1' = Bit is  | set                 | '0' = Bit is clea                         | red                   | HC = Bit is clear         |                   |                      |                  |

| <b>h</b> :+ 7 |                     | tod. Dood on (1)                          |                       |                           |                   |                      |                  |

| bit 7         | -                   | ted: Read as '1'                          |                       |                           |                   |                      |                  |

| bit 6         | •                   | guration Select bit<br>Configuration, Use |                       | ID Registers              |                   |                      |                  |

|               |                     | Flash program me                          |                       | ID Registers              |                   |                      |                  |

| bit 5         | LWLO: Load          | Write Latches On                          | ly bit <sup>(3)</sup> |                           |                   |                      |                  |

|               |                     | addressed progra                          | •                     | e latch is loaded/ι       | pdated on the     | next WR comman       | d                |

|               |                     | ressed program m                          | •                     | h is loaded/update        | ed and a write of | all program mem      | ory write latche |

|               |                     | itiated on the nex                        |                       |                           |                   |                      |                  |

| bit 4         | •                   | am Flash Erase E                          |                       |                           |                   |                      |                  |

|               |                     | s an erase operati<br>s an write operatio |                       |                           | rdware cleared    | upon completion)     |                  |

| bit 3         |                     | gram/Erase Error                          |                       |                           |                   |                      |                  |

|               |                     | n indicates an im                         |                       | or erase sequend          | e attempt or te   | rmination (bit is s  | et automatical   |

|               |                     | et attempt (write '                       | ,                     | ,                         |                   |                      |                  |

|               | 0 = The prog        | gram or erase ope                         | ration completed      | d normally.               |                   |                      |                  |

| bit 2         | •                   | am/Erase Enable                           |                       |                           |                   |                      |                  |

|               | •                   | rogram/erase cyc<br>programming/eras      |                       | lach                      |                   |                      |                  |

| bit 1         | WR: Write Co        | 0 0                                       | ing of program i      | 10311                     |                   |                      |                  |

|               |                     | a program Flash                           | orogram/erase o       | peration                  |                   |                      |                  |

|               |                     | ration is self-timed                      | 0                     | •                         | re once operatio  | on is complete.      |                  |

|               |                     | bit can only be se                        | , ,                   |                           |                   |                      |                  |

|               | 0 = Program         | /erase operation                          | to the Flash is co    | omplete and inact         | ive.              |                      |                  |

| bit 0         | RD: Read Co         |                                           |                       |                           |                   |                      |                  |

|               |                     | a program Flash r                         | ead. Read takes       | s one cycle. RD is        | cleared in hard   | lware. The RD bit    | can only be se   |

|               | •                   | red) in software.<br>t initiate a prograr | n Flash read.         |                           |                   |                      |                  |

| Note 1:       | Unimplemented bit   |                                           |                       |                           |                   |                      |                  |

| 2:            | The WRERR bit is    |                                           | by hardware whe       | en a program mer          | nory write or era | ase operation is st  | arted (WR = 1    |

| 3:            | The LWLO bit is igr | -                                         | -                     |                           | -                 | •                    |                  |

# REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

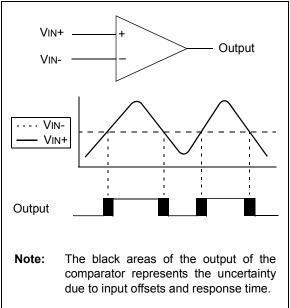

#### FIGURE 18-2: SINGLE COMPARATOR

# 18.2 Comparator Control

The comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- Output selection

- Output polarity

- Speed/Power selection

- Hysteresis enable

- · Output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR POSITIVE INPUT SELECTION

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC1\_output

- FVR\_buffer2

- Vss

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

# 18.2.3 COMPARATOR NEGATIVE INPUT SELECTION

The CxNCH<2:0> bits of the CMxCON0 register direct one of the input sources to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog<br>input, the appropriate bits must be set in<br>the ANSEL register and the correspond- |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

|       | ing TRIS bits must also be set to disable                                                                                      |

|       | the output drivers.                                                                                                            |

### 18.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

The synchronous comparator output signal (CxOUT\_sync) is available to the following peripheral(s):

- Analog-to-Digital Converter (ADC)

- Timer1

The asynchronous comparator output signal (CxOUT\_async) is available to the following peripheral(s):

Complementary Waveform Generator (CWG)

Note: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

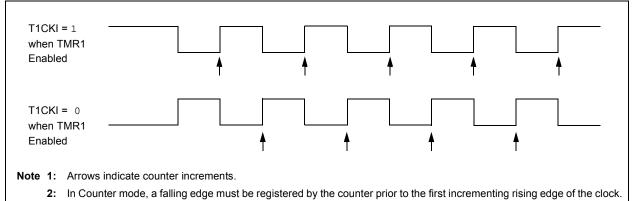

# 20.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 20.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

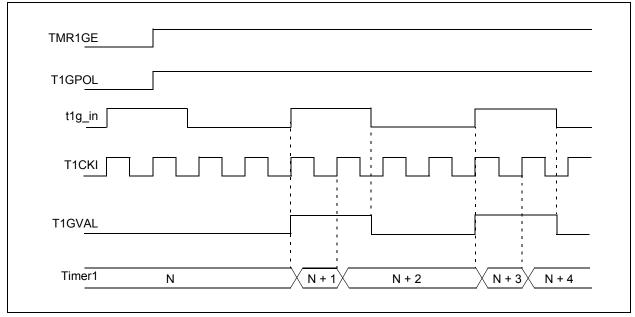

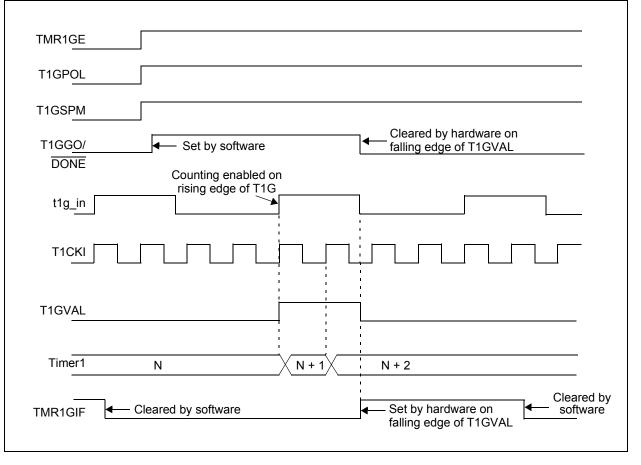

# 20.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 20-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

#### 20.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 20-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 20-6 for timing details.

# 20.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

# 20.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

# 20.6 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

**Note:** The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 20.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- · TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the  $\overline{\text{T1SYNC}}$  bit setting.

# FIGURE 20-3: TIMER1 GATE ENABLE MODE

# PIC16(L)F1574/5/8/9

# FIGURE 20-4: TIMER1 GATE TOGGLE MODE

| TMR1GE                                               |                                            |

|------------------------------------------------------|--------------------------------------------|

| T1GPOL                                               |                                            |

| T1GTM                                                |                                            |

| t1g_in                                               |                                            |

|                                                      |                                            |

| T1GVAL                                               |                                            |

| Timer 1 N $\sqrt{N+1}\sqrt{N+2}\sqrt{N+3}\sqrt{N+4}$ | $\sqrt{N+5}\sqrt{N+6}\sqrt{N+7}\sqrt{N+8}$ |

# FIGURE 20-5: TIMER1 GATE SINGLE-PULSE MODE

# 21.5 Register Definitions: Timer2 Control

|                 | R/W-0/0               | R/W-0/0                      | R/W-0/0         | R/W-0/0        | R/W-0/0           | R/W-0/0        | R/W-0/0      |  |  |  |

|-----------------|-----------------------|------------------------------|-----------------|----------------|-------------------|----------------|--------------|--|--|--|

| _               |                       | T2OUTI                       | PS<3:0>         |                | TMR2ON            | T2CKF          | PS<1:0>      |  |  |  |

| bit 7           |                       |                              |                 |                |                   | I              | bit          |  |  |  |

|                 |                       |                              |                 |                |                   |                |              |  |  |  |

| Legend:         |                       |                              |                 |                |                   |                |              |  |  |  |

| R = Readabl     | le bit                | W = Writable                 | bit             | U = Unimple    | emented bit, read | 1 as '0'       |              |  |  |  |

| u = Bit is und  | changed               | x = Bit is unkr              | nown            | -n/n = Value   | at POR and BO     | R/Value at all | other Resets |  |  |  |

| '1' = Bit is se | et                    | '0' = Bit is cle             | ared            |                |                   |                |              |  |  |  |

| L:1 7           |                       | unte de De e d'ans (         | 0'              |                |                   |                |              |  |  |  |

| bit 7           | -                     | ented: Read as '             |                 | v Calaat hita  |                   |                |              |  |  |  |

| bit 6-3         | 0000 = 1:1            | 3:0>: Timer2 Ou              | ilput Posiscale | er Select bits |                   |                |              |  |  |  |

|                 | 0000 = 1.1            |                              |                 |                |                   |                |              |  |  |  |

|                 | 0010 = 1:3            |                              |                 |                |                   |                |              |  |  |  |

|                 |                       | 0011 = 1:4 Postscaler        |                 |                |                   |                |              |  |  |  |

|                 | 0100 <b>= 1</b> :5    | Postscaler                   |                 |                |                   |                |              |  |  |  |

|                 | 0101 = 1:6 Postscaler |                              |                 |                |                   |                |              |  |  |  |

|                 | 0110 <b>= 1</b> :7    |                              |                 |                |                   |                |              |  |  |  |

|                 | 0111 = 1:8            |                              |                 |                |                   |                |              |  |  |  |

|                 | 1000 = 1:9            |                              |                 |                |                   |                |              |  |  |  |

|                 |                       | ) Postscaler<br>I Postscaler |                 |                |                   |                |              |  |  |  |

|                 |                       | 2 Postscaler                 |                 |                |                   |                |              |  |  |  |

|                 |                       | 3 Postscaler                 |                 |                |                   |                |              |  |  |  |

|                 |                       | 4 Postscaler                 |                 |                |                   |                |              |  |  |  |

|                 |                       | 5 Postscaler                 |                 |                |                   |                |              |  |  |  |

|                 | 1111 <b>= 1:16</b>    | 6 Postscaler                 |                 |                |                   |                |              |  |  |  |

| bit 2           | TMR2ON: 1             | Fimer2 On bit                |                 |                |                   |                |              |  |  |  |

|                 | 1 = Timer2 is on      |                              |                 |                |                   |                |              |  |  |  |

|                 | 0 = Timer2            | is off                       |                 |                |                   |                |              |  |  |  |

| bit 1-0         | T2CKPS<1              | :0>: Timer2 Cloc             | k Prescale Se   | lect bits      |                   |                |              |  |  |  |

|                 | 00 = Presca           | aler is 1                    |                 |                |                   |                |              |  |  |  |

|                 | 01 = Presca           | aler is 4                    |                 |                |                   |                |              |  |  |  |

|                 | 10 = Presca           | aler is 16                   |                 |                |                   |                |              |  |  |  |

|                 | 11 = Presca           | aler is 64                   |                 |                |                   |                |              |  |  |  |

|                 |                       |                              |                 |                |                   |                |              |  |  |  |

| TABLE 21-1      | I: SUIVIIVIA          | RY OF REGIS                  | 1 EKS ASSU      |                | H HIMERZ          |                |              |  |  |  |

# REGISTER 21-1: T2CON: TIMER2 CONTROL REGISTER

| Name   | Bit 7                         | Bit 6                           | Bit 5        | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------------------------------|---------------------------------|--------------|-------|-------|--------|--------|--------|---------------------|

| INTCON | GIE                           | PEIE                            | TMR0IE       | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1   | TMR1GIE                       | ADIE                            | RCIE         | TXIE  | —     | _      | TMR2IE | TMR1IE | 87                  |

| PIR1   | TMR1GIF                       | ADIF                            | RCIF         | TXIF  | —     | —      | TMR2IF | TMR1IF | 90                  |

| PR2    | Timer2 Module Period Register |                                 |              |       |       |        |        |        |                     |

| T2CON  | _                             | T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |              |       |       |        |        | 191    |                     |

| TMR2   | Holding Reg                   | ister for the 8                 | -bit TMR2 Co | unt   |       |        |        |        | 189*                |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

Note 1: PIC16(L)F1575 only.

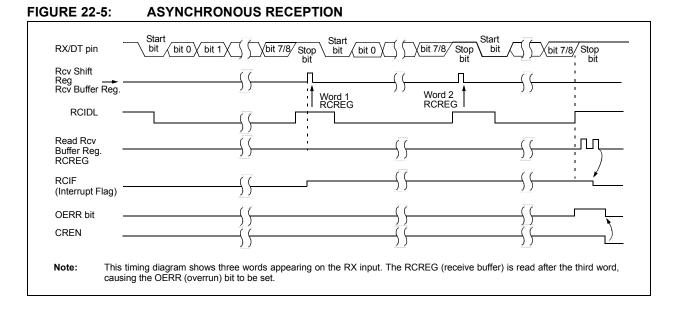

### 22.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

# 22.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 22.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 22.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

#### 22.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 22.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | PH<     | 15:8>          |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | mented bit, read | d as '0'       |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

# REGISTER 23-7: PWMxPHH: PWMx PHASE COUNT HIGH REGISTER

bit 7-0 **PH<15:8>**: PWM Phase High bits Upper eight bits of PWM phase count

### REGISTER 23-8: PWMxPHL: PWMx PHASE COUNT LOW REGISTER

| R/W-x/u   | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|--|

| PH<7:0>   |         |         |         |         |         |         |         |  |  |

| bit 7 bit |         |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PH<7:0>**: PWM Phase Low bits Lower eight bits of PWM phase count

Г

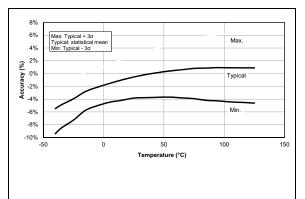

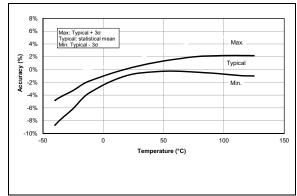

# 27.3 DC Characteristics

# TABLE 27-1:SUPPLY VOLTAGE

| PIC16LF       | 1574/5/8/9 | 1                                             | Standard Operating Conditions (unless otherwise stated) |       |                      |        |                                                                                                                                                                                    |  |  |  |  |  |

|---------------|------------|-----------------------------------------------|---------------------------------------------------------|-------|----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIC16F1       | 574/5/8/9  |                                               |                                                         |       |                      |        |                                                                                                                                                                                    |  |  |  |  |  |

| Param.<br>No. | Sym.       | Characteristic                                | Min.                                                    | Тур†  | Max.                 | Units  | Conditions                                                                                                                                                                         |  |  |  |  |  |

| D001          | Vdd        | Supply Voltage                                |                                                         |       |                      |        |                                                                                                                                                                                    |  |  |  |  |  |

|               |            |                                               | VDDMIN<br>1.8<br>2.5                                    |       | VDDMAX<br>3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≤ 32 MHz <b>(Note 3)</b>                                                                                                                                     |  |  |  |  |  |

| D001          |            |                                               | 2.3<br>2.5                                              | _     | 5.5<br>5.5           | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≤ 32 MHz <b>(Note 3)</b>                                                                                                                                     |  |  |  |  |  |

| D002*         | Vdr        | RAM Data Retention Voltage <sup>(1)</sup>     |                                                         |       |                      |        |                                                                                                                                                                                    |  |  |  |  |  |

|               |            |                                               | 1.5                                                     | —     | _                    | V      | Device in Sleep mode                                                                                                                                                               |  |  |  |  |  |

| D002*         |            |                                               | 1.7                                                     | -     | _                    | V      | Device in Sleep mode                                                                                                                                                               |  |  |  |  |  |

| D002A*        | VPOR       | Power-on Reset Release Voltage <sup>(2)</sup> |                                                         |       |                      |        |                                                                                                                                                                                    |  |  |  |  |  |

|               |            |                                               |                                                         | 1.6   | —                    | V      |                                                                                                                                                                                    |  |  |  |  |  |

| D002A*        |            |                                               |                                                         | 1.6   | —                    | V      |                                                                                                                                                                                    |  |  |  |  |  |

| D002B*        | VPORR*     | Power-on Reset Rearm Voltage <sup>(2)</sup>   |                                                         |       |                      |        |                                                                                                                                                                                    |  |  |  |  |  |

|               |            |                                               |                                                         | 0.8   | —                    | V      |                                                                                                                                                                                    |  |  |  |  |  |

| D002B*        |            |                                               |                                                         | 1.5   | —                    | V      |                                                                                                                                                                                    |  |  |  |  |  |

| D003          | VFVR       | Fixed Voltage Reference Voltage               | _                                                       | 1.024 | _                    | V      | $-40^{\circ}C \leq TA \leq +85^{\circ}C$                                                                                                                                           |  |  |  |  |  |