Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1579-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16(L)F1574/5/8/9

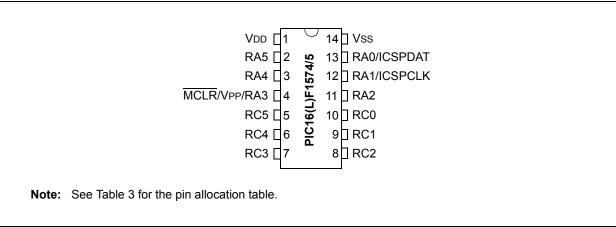

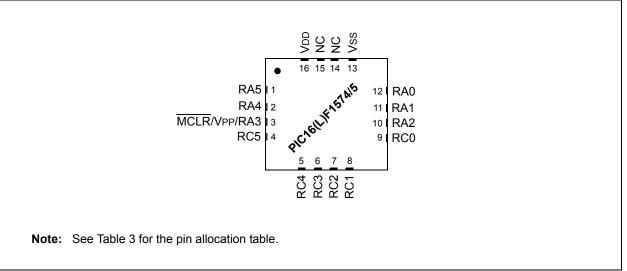

## **PIN DIAGRAMS**

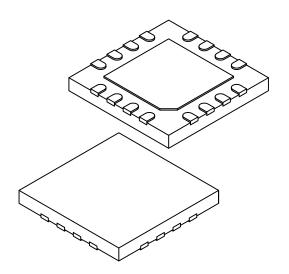

## FIGURE 2: 16-PIN UQFN (4x4)

| REGISTER        | 4-2: CON                                                                                                                                                                                                      | FIGURATION                                                                                                                                               | WORD 2                                        |                                     |                     |                                              |            |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------|---------------------|----------------------------------------------|------------|

|                 |                                                                                                                                                                                                               | R/P-1                                                                                                                                                    | R/P-1                                         | R/P-1                               | R/P-1               | R/P-1                                        | R/P-1      |

|                 |                                                                                                                                                                                                               | LVP <sup>(1)</sup>                                                                                                                                       | DEBUG <sup>(2)</sup>                          | LPBOREN                             | BORV <sup>(3)</sup> | STVREN                                       | PLLEN      |

|                 |                                                                                                                                                                                                               | bit 13                                                                                                                                                   |                                               |                                     |                     |                                              | bit 8      |

| U-1             | U-1                                                                                                                                                                                                           | U-1                                                                                                                                                      | U-1                                           | U-1                                 | R/P-1               | R/P-1                                        | R/P-1      |

| _               |                                                                                                                                                                                                               |                                                                                                                                                          |                                               |                                     | PPS1WAY             | WRT                                          | <1:0>      |

| bit 7           |                                                                                                                                                                                                               |                                                                                                                                                          |                                               |                                     |                     | •                                            | bit 0      |

|                 |                                                                                                                                                                                                               |                                                                                                                                                          |                                               |                                     |                     |                                              |            |

| Legend:         |                                                                                                                                                                                                               |                                                                                                                                                          |                                               |                                     |                     |                                              |            |

| R = Readab      |                                                                                                                                                                                                               | P = Programr                                                                                                                                             |                                               |                                     | nented bit, read    |                                              |            |

| '0' = Bit is cl | eared                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                         |                                               | n = Value whe                       | en blank or afte    | r Bulk Erase                                 |            |

| bit 13          | 1 = ON -<br>0 = OFF -                                                                                                                                                                                         | ltage Program<br>Low-voltage<br>Configuration<br>High Voltage                                                                                            | programming<br>bit is ignored.<br>on MCLR/VPP | enabled. MC                         | •                   |                                              | CLR. MCLRE |

| bit 12          | 1 = OFF -<br>0 = ON -                                                                                                                                                                                         | bugger Mode bi<br>In-Circuit Debu<br>In-Circuit Debu                                                                                                     | igger disabled;<br>igger enabled;             | ICSPCLK and                         |                     |                                              |            |

| bit 11          | 1 = OFF -                                                                                                                                                                                                     | <b>LPBOREN:</b> Low-Power Brown-out Reset Enable bit<br>1 = OFF – Low-power Brown-out Reset is disabled<br>0 = ON – Low-power Brown-out Reset is enabled |                                               |                                     |                     |                                              |            |

| bit 10          | <b>BORV:</b> Brown-out Reset Voltage Selection bit <sup>(3)</sup><br>1 = LOW – Brown-out Reset voltage (VBOR), low trip point selected<br>0 = HIGH – Brown-out Reset voltage (VBOR), high trip point selected |                                                                                                                                                          |                                               |                                     |                     |                                              |            |

| bit 9           | 1 = ON -                                                                                                                                                                                                      | ack Overflow/U<br>Stack Overflow<br>Stack Overflow                                                                                                       | or Underflow                                  | will cause a Re                     |                     |                                              |            |

| bit 8           |                                                                                                                                                                                                               | Enable bit<br>4xPLL enabled<br>4xPLL disabled                                                                                                            |                                               |                                     |                     |                                              |            |

| bit 7-3         | Unimplemer                                                                                                                                                                                                    | nted: Read as '                                                                                                                                          | 1'                                            |                                     |                     |                                              |            |

| bit 2           | <b>PPS1WAY</b> : F<br>1 = ON<br>0 = OFF                                                                                                                                                                       | PPSLOCK is se                                                                                                                                            | bit can only be<br>et, all future cha         | set once after a<br>inges to PPS re | gisters are prev    | quence is execu<br>ented<br>d an unlocking s |            |

| <b>2</b> : ⊤    | his bit cannot b<br>he DEBUG bit i                                                                                                                                                                            | e programmed<br>n Configuration                                                                                                                          | Words is man                                  | aged automatic                      | ally by device      | development to                               | •          |

## REGISTER 4-2: CONFIGURATION WORD 2

- debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

- **3:** See VBOR parameter for specific trip point voltages.

## 4.7 Register Definitions: Device ID

#### R R R R R R DEV<13:8> bit 13 bit 8 R R R R R R R R DEV<7:0> bit 7 bit 0

## REGISTER 4-3: DEVICEID: DEVICE ID REGISTER<sup>(1)</sup>

#### Legend:

| - |                  |  |

|---|------------------|--|

|   | R = Readable bit |  |

|   |                  |  |

| '0' = Bit is cleared | '1' = Bit is set | x = Bit is unknown |

|----------------------|------------------|--------------------|

|                      |                  |                    |

## bit 13-0 **DEV<13:0>:** Device ID bits

Refer to Table 4-1 to determine what these bits will read on which device. A value of 3FFFh is invalid.

Note 1: This location cannot be written.

## REGISTER 4-4: REVISIONID: REVISION ID REGISTER<sup>(1)</sup>

| R      | R | R    | R        | R | R     |

|--------|---|------|----------|---|-------|

|        |   | REV< | 13:8>    |   |       |

| bit 13 |   |      |          |   | bit 8 |

|        |   |      |          |   |       |

| -      | - |      | <b>D</b> |   |       |

| R     | R | R | R    | R     | R | R | R     |

|-------|---|---|------|-------|---|---|-------|

|       |   |   | REV< | :7:0> |   |   |       |

| bit 7 |   |   |      |       |   |   | bit 0 |

| Legend:              |                  |                    |  |

|----------------------|------------------|--------------------|--|

| R = Readable bit     |                  |                    |  |

| '0' = Bit is cleared | '1' = Bit is set | x = Bit is unknown |  |

bit 13-0 **REV<13:0>:** Revision ID bits These bits are used to identify the device revision.

**Note 1:** This location cannot be written.

#### TABLE 4-1: DEVICE ID VALUES

| DEVICE      | Device ID | Revision ID |

|-------------|-----------|-------------|

| PIC16F1574  | 3000h     | 2xxxh       |

| PIC16F1575  | 3001h     | 2xxxh       |

| PIC16F1578  | 3002h     | 2xxxh       |

| PIC16F1579  | 3003h     | 2xxxh       |

| PIC16LF1574 | 3004h     | 2xxxh       |

| PIC16LF1575 | 3005h     | 2xxxh       |

| PIC16LF1578 | 3006h     | 2xxxh       |

| PIC16LF1579 | 3007h     | 2xxxh       |

### 5.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 5-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), and peripherals, are *not* affected by the change in frequency.

## 5.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.8** "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT) and Watchdog Timer (WDT).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

## 5.2.2.5 FRC

The FRC clock is an uncalibrated, nominal 600 kHz peripheral clock source.

The FRC is automatically turned on by the peripherals requesting the FRC clock.

The FRC clock will continue to run during Sleep.

#### 5.2.2.6 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits, IRCF<3:0> of the OSCCON register.

The postscaler outputs of the 16 MHz HFINTOSC, **500 kHz MFINTOSC**, and **31 kHz** LFINTOSC output connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

Note: Following any Reset, the IRCF<3:0> bits of the OSCCON register are set to '0111' and the frequency selection is set to 500 kHz. The user can modify the IRCF bits to select a different frequency.

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

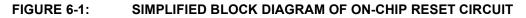

## 6.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- · Stack Underflow

- Programming mode exit

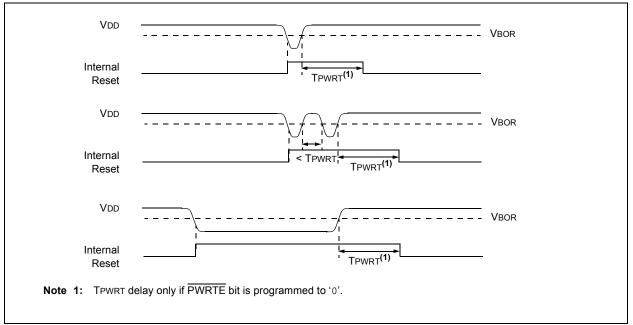

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-chip Reset Circuit is shown in Figure 6-1.

## 6.3 Register Definitions: BOR Control

## REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-Out Reset Enable bit                                          |

|---------|--------------------------------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words = 01:                                          |

|         | 1 = BOR Enabled                                                                      |

|         | 0 = BOR Disabled                                                                     |

|         | If BOREN <1:0> in Configuration Words <u>≠ 01</u> :                                  |

|         | SBOREN is read/write, but has no effect on the BOR                                   |

| bit 6   | BORFS: Brown-Out Reset Fast Start bit <sup>(1)</sup>                                 |

|         | If BOREN <1:0> = 10 (Disabled in Sleep) or BOREN<1:0> = 01 (Under software control): |

|         | 1 = Band gap is forced on always (covers sleep/wake-up/operating cases)              |

|         | 0 = Band gap operates normally, and may turn off                                     |

|         | <u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u>    |

|         | BORFS is Read/Write, but has no effect.                                              |

| bit 5-1 | Unimplemented: Read as '0'                                                           |

| bit 0   | BORRDY: Brown-Out Reset Circuit Ready Status bit                                     |

|         | 1 = The Brown-out Reset circuit is active                                            |

|         | 0 = The Brown-out Reset circuit is inactive                                          |

| Note di | DODEN 41/02 hits are leasted in Canfiguration Wards                                  |

#### **Note 1:** BOREN<1:0> bits are located in Configuration Words.

| TABLE 6-5: | SUMMARY OF REGISTERS ASSOCIATED WITH RESETS |

|------------|---------------------------------------------|

|            |                                             |

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|------------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  |       |            | —     |       |       | BORRDY | 75                  |

| PCON   | STKOVF | STKUNF | _     | RWDT       | RMCLR | RI    | POR   | BOR    | 79                  |

| STATUS | —      | _      | _     | TO         | PD    | Z     | DC    | С      | 23                  |

| WDTCON |        |        |       | WDTPS<4:0> |       |       |       |        | 99                  |

**Legend:** — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4              | Bit 11/3 | Bit 10/2    | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------------------|----------|-------------|---------|---------|---------------------|

|         | 13:8 |         | —       | _        | - CLKOUTEN BOREN<1:0> |          | —           | 56      |         |                     |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WD                    | TE<1:0>  | — FOSC<1:0> |         | <1:0>   | 50                  |

|         | 13:8 | _       | _       | LVP      | DEBUG                 | LPBOREN  | BORV        | STVREN  | PLLEN   | 67                  |

| CONFIG2 | 7:0  | —       | —       |          |                       | _        | PPS1WAY     | WRT     | <1:0>   | 57                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

## 8.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- 8. I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- CWG module using HFINTOSC

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information on this module.

## 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.12 "Determining the Cause of a Reset**".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

## 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

© 2016 Microchip Technology Inc.

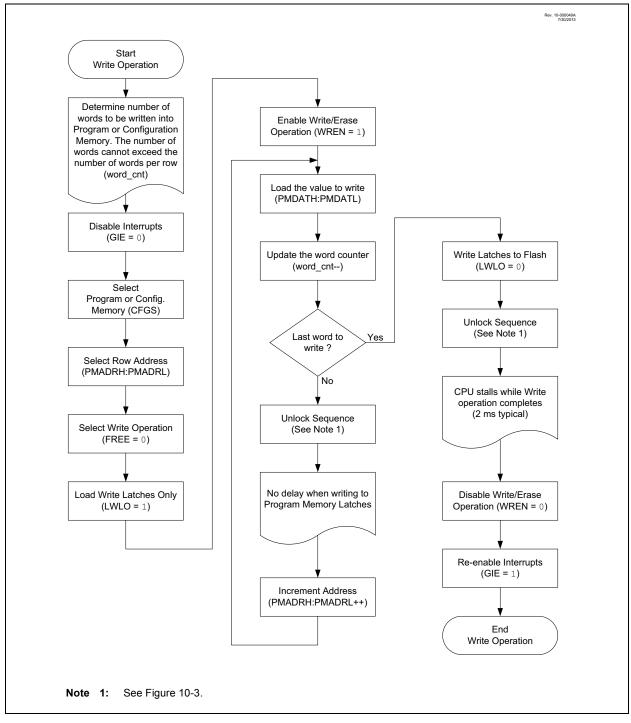

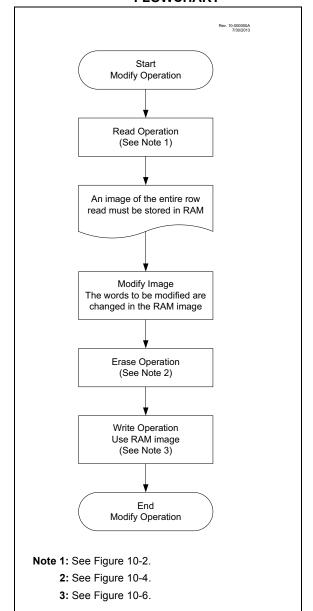

## 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

## FIGURE 10-7:

#### FLASH PROGRAM MEMORY MODIFY FLOWCHART

| W-0/0                                                                                            | W-0/0 | W-0/0             | W-0/0 | W-0/0        | W-0/0            | W-0/0    | W-0/0       |  |  |

|--------------------------------------------------------------------------------------------------|-------|-------------------|-------|--------------|------------------|----------|-------------|--|--|

| Program Memory Control Register 2                                                                |       |                   |       |              |                  |          |             |  |  |

| bit 7                                                                                            |       |                   |       |              |                  |          | bit 0       |  |  |

|                                                                                                  |       |                   |       |              |                  |          |             |  |  |

| Legend:                                                                                          |       |                   |       |              |                  |          |             |  |  |

| R = Readable b                                                                                   | bit   | W = Writable      | bit   | U = Unimpler | nented bit, read | l as '0' |             |  |  |

| S = Bit can only be set x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |       |                   |       |              |                  |          | ther Resets |  |  |

| '1' = Bit is set                                                                                 |       | '0' = Bit is clea | ared  |              |                  |          |             |  |  |

## REGISTER 10-6: PMCON2: PROGRAM MEMORY CONTROL 2 REGISTER

#### bit 7-0 Flash Memory Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

| Name   | Bit 7                             | Bit 6           | Bit 5  | Bit 4 | Bit 3     | Bit 2  | Bit 1 | Bit 0 | Register on<br>Page |

|--------|-----------------------------------|-----------------|--------|-------|-----------|--------|-------|-------|---------------------|

| INTCON | GIE                               | PEIE            | TMR0IE | INTE  | IOCIE     | TMR0IF | INTF  | IOCIF | 86                  |

| PMCON1 | (1)                               | CFGS            | LWLO   | FREE  | WRERR     | WREN   | WR    | RD    | 115                 |

| PMCON2 | Program Memory Control Register 2 |                 |        |       |           |        |       |       |                     |

| PMADRL | PMADRL<7:0>                       |                 |        |       |           |        |       |       |                     |

| PMADRH | (1)                               |                 |        | F     | MADRH<6:0 | >      |       |       | 114                 |

| PMDATL | PMDATL<7:0>                       |                 |        |       |           |        |       |       | 114                 |

| PMDATH | _                                 | — — PMDATH<5:0> |        |       |           |        |       |       | 114                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

**Note 1:** Unimplemented, read as '1'.

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH FLASH PROGRAM MEMORY

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |  |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|--|

| 0015104 | 13:8 | _       | _       |          | _        | CLKOUTEN | BOREI    | N<1:0>  | —       | 50                  |  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   | —        | FOSC    | <1:0>   | 56                  |  |

| 0015100 | 13:8 | _       | -       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 57                  |  |

| CONFIG2 | 7:0  | _       | —       | —        | _        | _        | PPS1WAY  | WRT     | <1:0>   | 57                  |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

'1' = Bit is set

## REGISTER 11-14: ODCONB: PORTB OPEN DRAIN CONTROL REGISTER

| R/W-0/0                                 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0                                                   | U-0 | U-0 | U-0 |  |  |  |

|-----------------------------------------|---------|---------|---------|-------------------------------------------------------|-----|-----|-----|--|--|--|

| ODB7                                    | ODB6    | ODB5    | ODB4    |                                                       | —   | —   | —   |  |  |  |

| bit 7 bit 0                             |         |         |         |                                                       |     |     |     |  |  |  |

|                                         |         |         |         |                                                       |     |     |     |  |  |  |

| Legend:                                 |         |         |         |                                                       |     |     |     |  |  |  |

| R = Readable bit W = Writable bit       |         |         | bit     | U = Unimplemented bit, read as '0'                    |     |     |     |  |  |  |

| u = Bit is unchanged x = Bit is unknown |         |         | nown    | -n/n = Value at POR and BOR/Value at all other Resets |     |     |     |  |  |  |

| bit 7-4 | <b>ODB&lt;7:4&gt;:</b> PORTB Open-Drain Enable bits<br>For RB<7:4> pins, respectively                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Port pin operates as open-drain drive (sink current only)</li> <li>0 = Port pin operates as standard push-pull drive (source and sink current)</li> </ul> |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                             |

## REGISTER 11-15: SLRCONB: PORTB SLEW RATE CONTROL REGISTER

'0' = Bit is cleared

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | SLRB<7:4>: PORTB Slew Rate Enable bits |

|---------|----------------------------------------|

|         | For RB<7:4> pins, respectively         |

|         | 1 = Port pin slew rate is limited      |

|         | 0 = Port pin slews at maximum rate     |

| bit 3-0 | Unimplemented: Read as '0'             |

## REGISTER 11-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | INLVLB<7:4>: PORTB Input Level Select bits                |

|---------|-----------------------------------------------------------|

|         | For RB<7:4> pins, respectively                            |

|         | 1 = ST input used for port reads and interrupt-on-change  |

|         | 0 = TTL input used for port reads and interrupt-on-change |

|         |                                                           |

bit 3-0 Unimplemented: Read as '0'

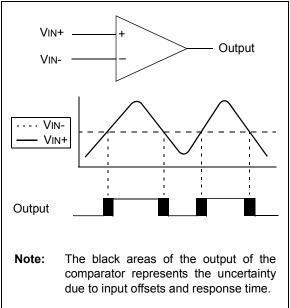

#### FIGURE 18-2: SINGLE COMPARATOR

## 18.2 Comparator Control

The comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- · Output selection

- Output polarity

- Speed/Power selection

- · Hysteresis enable

- Output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR POSITIVE INPUT SELECTION

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC1\_output

- FVR\_buffer2

- Vss

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

## 18.2.3 COMPARATOR NEGATIVE INPUT SELECTION

The CxNCH<2:0> bits of the CMxCON0 register direct one of the input sources to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog<br>input, the appropriate bits must be set in<br>the ANSEL register and the correspond- |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

|       | ing TRIS bits must also be set to disable                                                                                      |

|       | the output drivers.                                                                                                            |

### 18.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

The synchronous comparator output signal (CxOUT\_sync) is available to the following peripheral(s):

- Analog-to-Digital Converter (ADC)

- Timer1

The asynchronous comparator output signal (CxOUT\_async) is available to the following peripheral(s):

Complementary Waveform Generator (CWG)

Note: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

## FIGURE 22-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

|               | - 1819 skot by s |                 |       |       |       | <pre></pre>                                   |   |            |           | · · · · · · · · · · · · · · · · · · · |           |  |

|---------------|------------------|-----------------|-------|-------|-------|-----------------------------------------------|---|------------|-----------|---------------------------------------|-----------|--|

| - 80 (SON)    |                  | • ~~~<br>γ····· | (,    |       | ····· | <<br><<br><                                   | , |            | ,<br>,    | :                                     | ~<br><br> |  |

| 61037 bilee . |                  | ;               | ,     |       |       | 4<br>2000-00-00-00-00-00-00-00-00-00-00-00-00 |   |            | 711177777 | UIIII (C. <sup>A</sup>                | 6         |  |

| :<br>2009     |                  | :<br>           | \<br> | )<br> | ,<br> |                                               |   | )<br>      | ····;     | ·····                                 | ,<br>     |  |

|               |                  | ;<br>;          |       |       | 2     |                                               | 0 | දිනයක් අතර | to Quer   | 8eed et                               | şoze2     |  |

## FIGURE 22-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

| •             | o şoqoqo.   | 0030030808                                                                                                       | to sozioisos | ξ C    | 34         | \$06903K | Monfozios | epelo epelo:                              | gas da sja      | 203 04[0-40 | jeosost.       |

|---------------|-------------|------------------------------------------------------------------------------------------------------------------|--------------|--------|------------|----------|-----------|-------------------------------------------|-----------------|-------------|----------------|

|               |             |                                                                                                                  | pununun      |        |            | mununun  | upunun.   | inghunun                                  |                 |             |                |

|               |             | Veer                                                                                                             | s            | ,      |            |          |           |                                           | i<br>taana di   | Auto, Otes  | 886 - <u>E</u> |

| 983 HEESS     |             | i de la companya de la | Ϋ́           | 4<br>4 |            |          |           |                                           | s - 21          |             | ·····\$        |

| RIXCONT CREAT |             | ÷                                                                                                                | ;<br>;<br>;  | к<br>К | ······     |          |           | :<br>://///////////////////////////////// | ja fagaran      |             | ·····          |

|               |             |                                                                                                                  |              | 4<br>2 |            |          |           |                                           | e surges e<br>T |             | \$<br>6        |

| Esclosi,      |             |                                                                                                                  |              | 4      | ·····      | λ        |           | s to Essar Rais                           | 1               |             |                |

|               | <u>(</u> 20 | èep Comean                                                                                                       | d Executed - |        | Steep Bods |          |           |                                           |                 |             |                |

|               |             |                                                                                                                  |              |        |            |          |           |                                           |                 |             |                |

Wate 3: If the wake-up event requires long confluence warm-up fore, the reconstitute bearing of the VrUit bit can constructe the organic signal is additionally of the requirement of the presence of Q checks.

$\Omega^{*}_{\rm c}$  . The 2004-ABTE measure is idea where the Velot hit is and

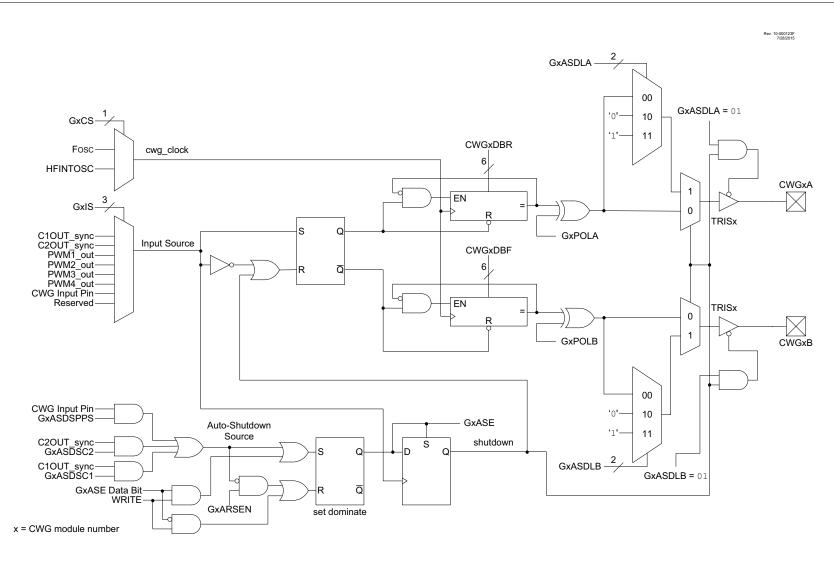

#### FIGURE 24-1: SIMPLIFIED CWG BLOCK DIAGRAM

PIC16(L)F1574/5/8/9

## 24.8 Dead-Band Uncertainty

When the rising and falling edges of the input source triggers the dead-band counters, the input may be asynchronous. This will create some uncertainty in the dead-band time delay. The maximum uncertainty is equal to one CWG clock period. Refer to Equation 24-1 for more detail.

#### EQUATION 24-1: DEAD-BAND UNCERTAINTY

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

Example:

$$Fcwg\_clock = 16 MHz$$

Therefore:

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

$$= \frac{1}{16 MHz}$$

$$= 62.5 ns$$

## 24.9 Auto-Shutdown Control

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software.

## 24.9.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External Input

#### 24.9.1.1 Software Generated Shutdown

Setting the GxASE bit of the CWGxCON2 register will force the CWG into the shutdown state.

When auto-restart is disabled, the shutdown state will persist as long as the GxASE bit is set.

When auto-restart is enabled, the GxASE bit will clear automatically and resume operation on the next rising edge event. See Figure 24-6.

## 24.9.1.2 External Input Source

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Any combination of two input sources can be selected to cause a shutdown condition. The sources are:

- Comparator C1 C1OUT\_sync

- Comparator C2 C2OUT\_sync

- CWG1FLT

Shutdown inputs are selected in the CWGxCON2 register. (Register 24-3).

```

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

```

# PIC16(L)F1574/5/8/9

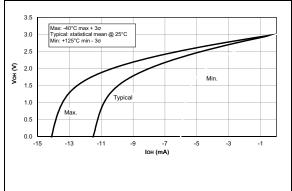

**FIGURE 28-37:** Voh vs. Ioh Over Temperature, VDD = 3.0V.

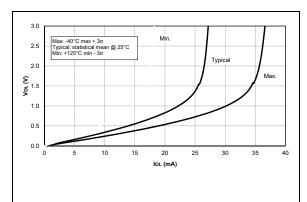

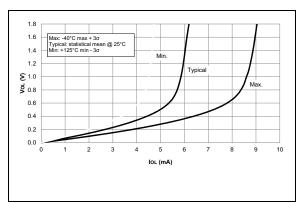

FIGURE 28-38: VOL vs. IOL Over Temperature, VDD = 3.0V.

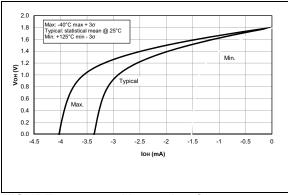

FIGURE 28-39: Voн vs. Ioн Over Temperature, Vod = 1.8V, PIC16LF1574/5/8/9 Only.

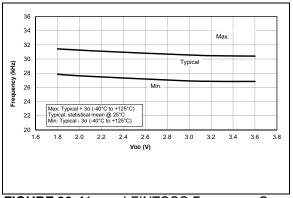

FIGURE 28-41: LFINTOSC Frequency Over VDD and Temperature, PIC16LF1574/5/8/9 Only.

**FIGURE 28-40:** VoL vs. IoL Over Temperature, VDD = 1.8V, PIC16LF1574/5/8/9 Only.

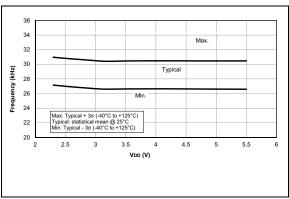

FIGURE 28-42: LFINTOSC Frequency Over VDD and Temperature, PIC16F1574/5/8/9 Only.

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |          |      |  |  |

|-------------------------|-------------|-----------|----------|------|--|--|

| Dimension               | Limits      | MIN       | NOM      | MAX  |  |  |

| Number of Pins          | N           |           | 16       |      |  |  |

| Pitch                   | e 0.65 BSC  |           |          |      |  |  |

| Overall Height          | Α           | 0.45      | 0.50     | 0.55 |  |  |

| Standoff                | A1          | 0.00      | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.127 REF |          |      |  |  |

| Overall Width           | E           | 4.00 BSC  |          |      |  |  |

| Exposed Pad Width       | E2          | 2.50      | 2.60     | 2.70 |  |  |

| Overall Length D 4.00 E |             |           | 4.00 BSC | _    |  |  |

| Exposed Pad Length      | D2          | 2.50      | 2.60     | 2.70 |  |  |

| Terminal Width          | b           | 0.25      | 0.30     | 0.35 |  |  |

| Terminal Length         | L           | 0.30      | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | К           | 0.20      | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-257A Sheet 2 of 2

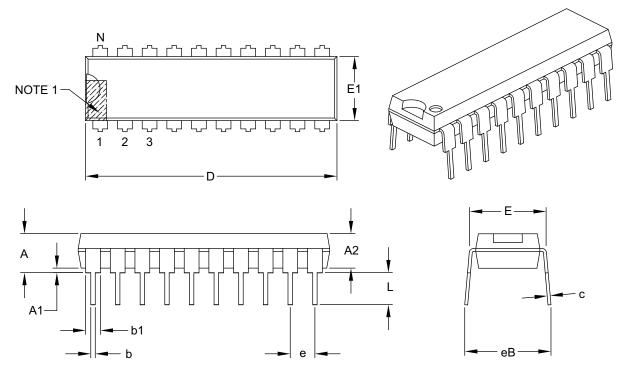

## 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          |       |       |  |

|----------------------------|------------------|----------|-------|-------|--|

| Dimensio                   | n Limits         | MIN      | NOM   | MAX   |  |

| Number of Pins             | Number of Pins N |          |       |       |  |

| Pitch                      | е                | .100 BSC |       |       |  |

| Top to Seating Plane       | Α                | —        | -     | .210  |  |

| Molded Package Thickness   | A2               | .115     | .130  | .195  |  |

| Base to Seating Plane      | A1               | .015     | _     | -     |  |

| Shoulder to Shoulder Width | E                | .300     | .310  | .325  |  |

| Molded Package Width       | E1               | .240     | .250  | .280  |  |

| Overall Length             | D                | .980     | 1.030 | 1.060 |  |

| Tip to Seating Plane       | L                | .115     | .130  | .150  |  |

| Lead Thickness             | С                | .008     | .010  | .015  |  |

| Upper Lead Width           | b1               | .045     | .060  | .070  |  |

| Lower Lead Width           | b                | .014     | .018  | .022  |  |

| Overall Row Spacing §      | eB               | -        | -     | .430  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

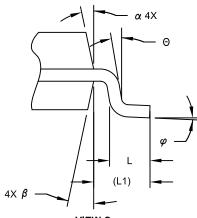

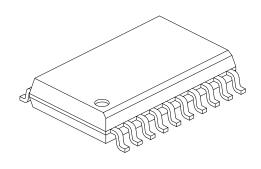

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| VI | EW | С |  |

|----|----|---|--|

|    |    |   |  |

| l                        | N         | <b>IILLIMETER</b> | S   |      |  |  |

|--------------------------|-----------|-------------------|-----|------|--|--|

| Dimension Lim            | its       | MIN               | NOM | MAX  |  |  |

| Number of Pins           | N         |                   | 20  |      |  |  |

| Pitch                    | е         | 1.27 BSC          |     |      |  |  |

| Overall Height           | Α         | -                 | -   | 2.65 |  |  |

| Molded Package Thickness | A2        | 2.05              | -   | -    |  |  |

| Standoff §               | A1        | 0.10              | -   | 0.30 |  |  |

| Overall Width            | E         | 10.30 BSC         |     |      |  |  |

| Molded Package Width     | E1        | 7.50 BSC          |     |      |  |  |

| Overall Length           | D         | 12.80 BSC         |     |      |  |  |

| Chamfer (Optional)       | h         | 0.25              | -   | 0.75 |  |  |

| Foot Length              | L         | 0.40              | -   | 1.27 |  |  |

| Footprint                | L1        | 1.40 REF          |     |      |  |  |

| Lead Angle               | Θ         | 0°                | -   | -    |  |  |

| Foot Angle               | $\varphi$ | 0°                | -   | 8°   |  |  |

| Lead Thickness           | С         | 0.20              | -   | 0.33 |  |  |

| Lead Width               | b         | 0.31              | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α         | 5°                | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β         | 5°                | -   | 15°  |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2