Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1579t-i-gz |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2: PACKAGES

| Packages      | PDIP | SOIC | TSSOP | SSOP | UQFN |

|---------------|------|------|-------|------|------|

| PIC16(L)F1574 | •    | •    | •     |      | •    |

| PIC16(L)F1575 | •    | •    | •     |      | •    |

| PIC16(L)F1578 | •    | •    |       | •    | •    |

| PIC16(L)F1579 | •    | •    |       | •    | •    |

Note: Pin details are subject to change.

# TABLE 3-8:PIC16(L)F1575/9 MEMORY MAP, BANKS 8-15

| 400h<br>40Bh<br>40Ch | Core Registers<br>(Table 3-2) | 480h |                       | 1 r  |                       |      |                       |      |                                |      |                       |      |                       |      |                       |

|----------------------|-------------------------------|------|-----------------------|------|-----------------------|------|-----------------------|------|--------------------------------|------|-----------------------|------|-----------------------|------|-----------------------|

| -                    |                               |      | Core Registers        | 500h | Core Registers        | 580h | Core Registers        | 600h | Core Registers                 | 680h | Core Registers        | 700h | Core Registers        | 780h | Core Registers        |

| 40Ch                 | (14016-5-2)                   | 48Bh | (Table 3-2)           | 50Bh | (Table 3-2)           | 58Bh | (Table 3-2)           | 60Bh | (Table 3-2)                    | 68Bh | (Table 3-2)           | 70Bh | (Table 3-2)           | 78Bh | (Table 3-2)           |

| 10011                | —                             | 48Ch | —                     | 50Ch | —                     | 58Ch | —                     | 60Ch | _                              | 68Ch | _                     | 70Ch | _                     | 78Ch | —                     |

| 40Dh                 | _                             | 48Dh | —                     | 50Dh | —                     | 58Dh | —                     | 60Dh | —                              | 68Dh | _                     | 70Dh | —                     | 78Dh | _                     |

| 40Eh                 | _                             | 48Eh | —                     | 50Eh | —                     | 58Eh | —                     | 60Eh | _                              | 68Eh | _                     | 70Eh | _                     | 78Eh | _                     |

| 40Fh                 | _                             | 48Fh | _                     | 50Fh | _                     | 58Fh | —                     | 60Fh | —                              | 68Fh | _                     | 70Fh | —                     | 78Fh | _                     |

| 410h                 | _                             | 490h | —                     | 510h | —                     | 590h | —                     | 610h | —                              | 690h | _                     | 710h | —                     | 790h | _                     |

| 411h                 | —                             | 491h | —                     | 511h | —                     | 591h | —                     | 611h | —                              | 691h | CWG1DBR               | 711h | —                     | 791h | —                     |

| 412h                 | —                             | 492h | —                     | 512h | —                     | 592h | —                     | 612h | —                              | 692h | CWG1DBF               | 712h | —                     | 792h | —                     |

| 413h                 | —                             | 493h | —                     | 513h | —                     | 593h | —                     | 613h | —                              | 693h | CWG1CON0              | 713h | —                     | 793h | —                     |

| 414h                 | —                             | 494h | —                     | 514h | —                     | 594h | —                     | 614h | _                              | 694h | CWG1CON1              | 714h | _                     | 794h | —                     |

| 415h                 | —                             | 495h | —                     | 515h | —                     | 595h | —                     | 615h | _                              | 695h | CWG1CON2              | 715h | _                     | 795h | —                     |

| 416h                 | —                             | 496h | —                     | 516h | —                     | 596h | —                     | 616h | _                              | 696h | _                     | 716h | _                     | 796h |                       |

| 417h                 | —                             | 497h | —                     | 517h | —                     | 597h | —                     | 617h | _                              | 697h | —                     | 717h | _                     | 797h | —                     |

| 418h                 | —                             | 498h | —                     | 518h | —                     | 598h | —                     | 618h | _                              | 698h | _                     | 718h | _                     | 798h |                       |

| 419h                 | —                             | 499h | —                     | 519h | —                     | 599h | —                     | 619h | _                              | 699h | _                     | 719h | _                     | 799h |                       |

| 41Ah                 | —                             | 49Ah | —                     | 51Ah | —                     | 59Ah | —                     | 61Ah | —                              | 69Ah | —                     | 71Ah | —                     | 79Ah | —                     |

| 41Bh                 | —                             | 49Bh | —                     | 51Bh | —                     | 59Bh | —                     | 61Bh | _                              | 69Bh | —                     | 71Bh | _                     | 79Bh | —                     |

| 41Ch                 | —                             | 49Ch | —                     | 51Ch | —                     | 59Ch | —                     | 61Ch | _                              | 69Ch | —                     | 71Ch | _                     | 79Ch | —                     |

| 41Dh                 | —                             | 49Dh | —                     | 51Dh | —                     | 59Dh | —                     | 61Dh | _                              | 69Dh | _                     | 71Dh | _                     | 79Dh |                       |

| 41Eh                 | —                             | 49Eh | —                     | 51Eh | —                     | 59Eh | —                     | 61Eh | _                              | 69Eh | —                     | 71Eh | _                     | 79Eh | —                     |

| 41Fh                 | —                             | 49Fh | —                     | 51Fh | —                     | 59Fh | —                     | 61Fh | —                              | 69Fh | —                     | 71Fh | —                     | 79Fh | —                     |

| 420h                 |                               | 4A0h |                       | 520h |                       | 5A0h |                       | 620h | General<br>Purpose<br>Register | 6A0h |                       | 720h |                       | 7A0h |                       |

|                      | General                       |      | General               |      | General               |      | General               | 63Fh | 32 Bytes                       |      | Unimplemented         |      | Unimplemented         |      | Unimplemented         |

|                      | Purpose<br>Register           |      | Purpose<br>Register   |      | Purpose<br>Register   |      | Purpose<br>Register   | 640h |                                |      | Read as '0'           |      | Read as '0'           |      | Read as '0'           |

|                      | 80 Bytes                      |      | 80 Bytes              |      | 80 Bytes              |      | 80 Bytes              |      | Unimplemented<br>Read as '0'   |      | iteau as o            |      | iteau as o            |      | Nedu as 0             |

| 46Fh                 |                               | 4EFh |                       | 56Fh |                       | 5EFh |                       | 66Fh |                                | 6EFh |                       | 76Fh |                       | 7EFh |                       |

| 470h                 |                               | 4F0h |                       | 570h |                       | 5F0h |                       | 670h |                                | 6F0h |                       | 770h |                       | 7F0h |                       |

|                      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh          |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |

| 47Fh                 |                               | 4FFh |                       | 57Fh |                       | 5FFh |                       | 67Fh |                                | 6FFh |                       | 77Fh |                       | 7FFh |                       |

Legend: = Unimplemented data memory locations, read as '0'

# TABLE 3-10: PIC16(L)F1574/5/8/9 MEMORY MAP, BANKS 24-31

|      | BANK 24                       |      | BANK 25                       |      | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                       |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| C00h | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2) | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2) |

| C0Bh | (10010 0 2)                   | C8Bh | (10010 0 2)                   | D0Bh | (10510 0 2)                   | D8Bh | (10010 0 2)                   | E0Bh | (10010 0 2)                   | E8Bh | (10010 0 2)                   | F0Bh | (10010 0 2)                   | F8Bh | (10010 0 2)                   |

| C0Ch | _                             | C8Ch | _                             | D0Ch | —                             | D8Ch |                               | E0Ch |                               | E8Ch |                               | F0Ch | _                             | F8Ch |                               |

| C0Dh |                               | C8Dh | _                             | D0Dh | —                             |      |                               |      |                               |      |                               | F0Dh | _                             |      |                               |

| C0Eh |                               | C8Eh |                               | D0Eh | —                             |      |                               |      |                               |      |                               | F0Eh | —                             |      |                               |

| C0Fh | —                             | C8Fh | _                             | D0Fh | —                             |      |                               |      |                               |      |                               | F0Fh | _                             |      |                               |

| C10h | —                             | C90h | _                             | D10h | —                             |      |                               |      |                               |      |                               | F10h | _                             |      |                               |

| C11h | —                             | C91h | _                             | D11h | _                             |      |                               |      |                               |      |                               | F11h | _                             |      |                               |

| C12h | —                             | C92h | _                             | D12h | _                             |      |                               |      |                               |      |                               | F12h | _                             |      |                               |

| C13h |                               | C93h |                               | D13h | —                             |      |                               |      |                               |      |                               | F13h | —                             |      |                               |

| C14h | —                             | C94h |                               | D14h | —                             |      |                               |      |                               |      |                               | F14h | —                             |      |                               |

| C15h | —                             | C95h |                               | D15h | —                             |      |                               |      |                               |      |                               | F15h | —                             |      |                               |

| C16h | —                             | C96h | _                             | D16h | _                             |      |                               |      |                               |      |                               | F16h | _                             |      |                               |

| C17h | —                             | C97h | _                             | D17h | _                             |      |                               |      |                               |      |                               | F17h | _                             |      |                               |

| C18h | _                             | C98h | —                             | D18h | —                             |      | See Table 3-11                |      | See Table 3-12                |      | See Table 3-12                | F18h |                               |      | See Table 3-13                |

| C19h |                               | C99h | _                             | D19h | _                             |      |                               |      |                               |      |                               | F19h | _                             |      |                               |

| C1Ah |                               | C9Ah | _                             | D1Ah | _                             |      |                               |      |                               |      |                               | F1Ah | _                             |      |                               |

| C1Bh |                               | C9Bh | _                             | D1Bh | _                             |      |                               |      |                               |      |                               | F1Bh | _                             |      |                               |

| C1Ch |                               | C9Ch | _                             | D1Ch | —                             |      |                               |      |                               |      |                               | F1Ch | —                             |      |                               |

| C1Dh |                               | C9Dh | —                             | D1Dh | —                             |      |                               |      |                               |      |                               | F1Dh | —                             |      |                               |

| C1Eh |                               | C9Eh | —                             | D1Eh | —                             |      |                               |      |                               |      |                               | F1Eh | _                             |      |                               |

| C1Fh | _                             | C9Fh | _                             | D1Fh | _                             |      |                               |      |                               |      |                               | F1Fh |                               |      |                               |

| C20h |                               | CA0h |                               | D20h |                               |      |                               |      |                               |      |                               | F20h |                               |      |                               |

|      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      |                               |      |                               |      |                               |      | Unimplemented<br>Read as '0'  |      |                               |

| C6Fh |                               | CEFh |                               | D6Fh |                               | DEFh |                               | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                               |

| C70h |                               | CF0h |                               | D70h |                               | DF0h |                               | E70h |                               | EF0h |                               | F70h |                               | FF0h |                               |

|      | Accesses<br>70h – 7Fh         |

|      | -                             | CFFh | 7011-7111                     | D7Fh | /011 - /111                   | DFFh | 7011-7111                     | E7Fh | 701-711                       | EFFh | -                             | F7Fh | 7011-7111                     | FFFh | /011-/111                     |

| CFFh |                               | OFFN |                               | DIFN |                               | DEEU |                               |      |                               |      |                               |      |                               | LLLU |                               |

Legend: = Unimplemented data memory locations, read as '0'

# PIC16(L)F1574/5/8/9

## 6.4 Low-Power Brown-Out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) operates like the BOR to detect low voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR voltage threshold (VLPBOR) has a wider tolerance than the BOR (VBOR), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN = 00) or disabled in Sleep mode (BOREN = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

#### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

# 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

# TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| х     | 1   | Enabled  |

# 6.5.1 MCLR ENABLED

When  $\overline{\text{MCLR}}$  is enabled and the pin is held low, the device is held in Reset. The  $\overline{\text{MCLR}}$  pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

## **Note:** A Reset does not drive the MCLR pin low.

## 6.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.1 "PORTA Registers"** for more information.

# 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register are changed to indicate the WDT Reset. See **Section 9.0 "Watchdog Timer (WDT)"** for more information.

## 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

## 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 3.5.2 "Overflow/Underflow Reset"** for more information.

# 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

## 6.10 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overline{\text{PWRTE}}$  bit of Configuration Words.

# 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

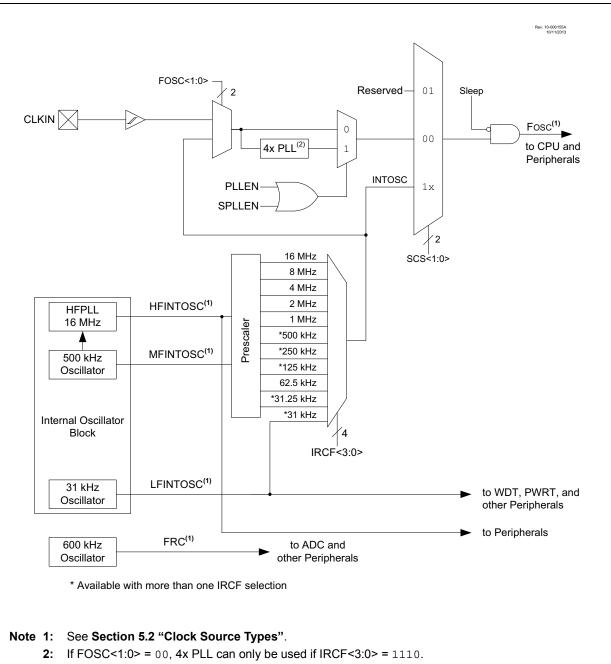

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 5.0 "Oscillator Module"** for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 FOSC cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

## 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | х  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is set on POR                                         |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

## TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

## TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

| R/W-0/0                               | R/W-0/0        | R/W-0/0         | R/W-0/0   | U-0            | U-0              | U-0              | U-0          |

|---------------------------------------|----------------|-----------------|-----------|----------------|------------------|------------------|--------------|

| PWM4IE                                | PWM3IE         | PWM2IE          | PWM1IE    |                | —                | —                | —            |

| bit 7                                 |                |                 |           |                |                  |                  | bit 0        |

|                                       |                |                 |           |                |                  |                  |              |

| Legend:                               |                |                 |           |                |                  |                  |              |

| R = Readable                          | bit            | W = Writable    | bit       | U = Unimpler   | mented bit, read | as '0'           |              |

| u = Bit is unch                       | anged          | x = Bit is unkr | nown      | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set '0' = Bit is cleared |                |                 |           |                |                  |                  |              |

|                                       |                |                 |           |                |                  |                  |              |

| bit 7                                 |                | /M4 Interrupt E |           |                |                  |                  |              |

|                                       |                | the PWM4 inte   |           |                |                  |                  |              |

|                                       |                | the PWM4 inte   | •         |                |                  |                  |              |

| bit 6                                 |                | /M3 Interrupt E |           |                |                  |                  |              |

|                                       |                | the PWM3 inte   | •         |                |                  |                  |              |

|                                       | 0 = Disables   | the PWM3 inte   | errupt    |                |                  |                  |              |

| bit 5                                 | PWM2IE: PW     | /M2 Interrupt E | nable bit |                |                  |                  |              |

|                                       |                | the PWM2 inte   |           |                |                  |                  |              |

|                                       | 0 = Disables   | the PWM2 inte   | errupt    |                |                  |                  |              |

| bit 4                                 | PWM1IE: PW     | /M1 Interrupt E | nable bit |                |                  |                  |              |

|                                       |                | the PWM1 inte   |           |                |                  |                  |              |

|                                       | 0 = Disables   | the PWM1 inte   | errupt    |                |                  |                  |              |

| bit 3-0                               | Unimplemen     | ted: Read as '  | 0'        |                |                  |                  |              |

|                                       |                |                 |           |                |                  |                  |              |

| Note: Bit                             | PEIE of the IN | TCON register   | must be   |                |                  |                  |              |

|                                       | to enable any  |                 |           |                |                  |                  |              |

|                                       |                |                 |           |                |                  |                  |              |

| U-0              | U-0   | R/W-1/1              | R/W-1/1 | R/W-1/1                            | R/W-1/1                                               | R/W-1/1 | R/W-1/1 |  |  |  |

|------------------|-------|----------------------|---------|------------------------------------|-------------------------------------------------------|---------|---------|--|--|--|

| _                | _     | WPUA5                | WPUA4   | WPUA3                              | WPUA2                                                 | WPUA1   | WPUA0   |  |  |  |

| bit 7            |       |                      |         |                                    |                                                       |         | bit 0   |  |  |  |

|                  |       |                      |         |                                    |                                                       |         |         |  |  |  |

| Legend:          |       |                      |         |                                    |                                                       |         |         |  |  |  |

| R = Readable     | bit   | W = Writable         | bit     | U = Unimplemented bit, read as '0' |                                                       |         |         |  |  |  |

| u = Bit is uncha | anged | d x = Bit is unknown |         |                                    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |  |  |  |

| '1' = Bit is set |       | '0' = Bit is clea    | ared    |                                    |                                                       |         |         |  |  |  |

| '1' = Bit is set |       | ʻ0' = Bit is clea    | ared    |                                    |                                                       |         |         |  |  |  |

## REGISTER 11-5: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits<sup>(3)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

- **3:** For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

## REGISTER 11-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | ODA5    | ODA4    | —   | ODA2    | ODA1    | ODA0    |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>ODA&lt;5:4&gt;:</b> PORTA Open-Drain Enable bits<br>For RA<5:4> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0 | <b>ODA&lt;2:0&gt;:</b> PORTA Open-Drain Enable bits<br>For RA<2:0> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

# 12.0 PERIPHERAL PIN SELECT (PPS) MODULE

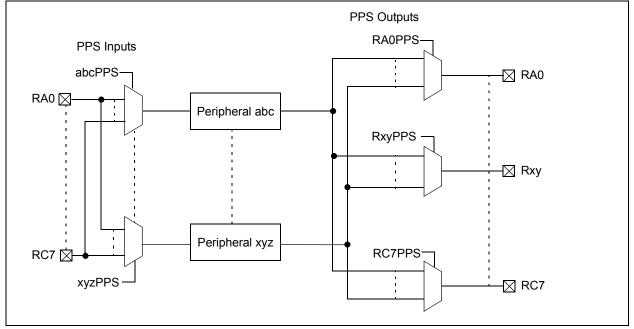

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 12-1.

# 12.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Multiple peripherals can operate from the same source simultaneously. Port reads always return the pin level regardless of peripheral PPS selection. If a pin also has associated analog functions, the ANSEL bit for that pin must be cleared to enable the digital input buffer.

Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 12-1.

| Note: | The notation "xxx" in the register name is    |

|-------|-----------------------------------------------|

|       | a place holder for the peripheral identifier. |

|       | For example, CLC1PPS.                         |

# 12.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- · CWG (auto-shutdown)

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 12-2.

**Note:** The notation "Rxy" is a place holder for the pin identifier. For example, RA0PPS.

## FIGURE 12-1: SIMPLIFIED PPS BLOCK DIAGRAM

## REGISTER 12-3: PPSLOCK: PPS LOCK REGISTER

| U-0                        | U-0               | U-0                                            | U-0                                                 | U-0                                                                             | U-0                                                                                                                                                    | R/W-0/0                                                                                                                                                                           |  |  |  |

|----------------------------|-------------------|------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| _                          | —                 | _                                              | —                                                   | _                                                                               | _                                                                                                                                                      | PPSLOCKED                                                                                                                                                                         |  |  |  |

| bit 7 bit                  |                   |                                                |                                                     |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |  |  |  |

|                            |                   |                                                |                                                     |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |  |  |  |

|                            |                   |                                                |                                                     |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |  |  |  |

| e bit                      | W = Writable I    | oit                                            | U = Unimplemented bit, read as '0'                  |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |  |  |  |

| u = Bit is unchanged x = B |                   | k = Bit is unknown                             |                                                     | -n/n = Value at POR and BOR/Value at all oth                                    |                                                                                                                                                        |                                                                                                                                                                                   |  |  |  |

|                            | '0' = Bit is clea | ared                                           |                                                     |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |  |  |  |

|                            | e bit             | e bit W = Writable H<br>nanged x = Bit is unkn | e bit W = Writable bit<br>nanged x = Bit is unknown | e bit W = Writable bit U = Unimplen<br>nanged x = Bit is unknown -n/n = Value a | -     -     -     -       e bit     W = Writable bit     U = Unimplemented bit, rea       nanged     x = Bit is unknown     -n/n = Value at POR and BO | -     -     -     -     -       e bit     W = Writable bit     U = Unimplemented bit, read as '0'       nanged     x = Bit is unknown     -n/n = Value at POR and BOR/Value at al |  |  |  |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

1 = PPS is locked. PPS selections can not be changed.

0 = PPS is not locked. PPS selections can be changed.

## 13.6 Register Definitions: Interrupt-on-Change Control

#### **REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER**

| U-0                                     | U-0 | R/W-0/0            | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------------|-----|--------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| _                                       | _   | IOCAP5             | IOCAP4                                                | IOCAP3                             | IOCAP2  | IOCAP1  | IOCAP0  |  |

| bit 7                                   |     |                    |                                                       | -                                  |         |         | bit 0   |  |

|                                         |     |                    |                                                       |                                    |         |         |         |  |

| Legend:                                 |     |                    |                                                       |                                    |         |         |         |  |

| R = Readable bit                        |     | W = Writable bi    | t                                                     | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                    | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set                        |     | '0' = Bit is clear | ed                                                    |                                    |         |         |         |  |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

# 14.3 Register Definitions: FVR Control

| R/W-0/0                                                                                                                                                                                                                                                                                                                                       | R-q/q                                                                                                                                       | R/W-0/0                                                   | R/W-0/0                                                  | R/W-0/0                     | R/W-0/0                                                                      | R/W-0/0          | R/W-0/0              |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------|------------------|----------------------|--|--|

| FVREN <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                          | FVRRDY <sup>(2)</sup>                                                                                                                       | TSEN <sup>(3)</sup>                                       | TSRNG <sup>(3)</sup>                                     | CDAFV                       | ′R<1:0> <sup>(1)</sup>                                                       | ADFVR            | <1:0> <sup>(1)</sup> |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |                                                           |                                                          |                             |                                                                              |                  | bit                  |  |  |

|                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                             |                                                           |                                                          |                             |                                                                              |                  |                      |  |  |

| Legend:                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                             |                                                           |                                                          |                             |                                                                              |                  |                      |  |  |

| R = Readable                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                             | W = Writable                                              |                                                          |                             | mented bit, read                                                             |                  |                      |  |  |

| u = Bit is unc                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                           | x = Bit is unk                                            |                                                          |                             | at POR and BO                                                                |                  | other Resets         |  |  |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                                              | :                                                                                                                                           | '0' = Bit is cle                                          | ared                                                     | q = Value de                | pends on condit                                                              | ion              |                      |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                         | 1 = Fixed Vo                                                                                                                                | d Voltage Refe<br>Itage Referenc<br>Itage Referenc        | e is enabled                                             | bit <sup>(1)</sup>          |                                                                              |                  |                      |  |  |

| bit 6                                                                                                                                                                                                                                                                                                                                         | 1 = Fixed Vo                                                                                                                                | ed Voltage Re<br>Itage Referenc<br>Itage Referenc         | e output is rea                                          |                             | enabled                                                                      |                  |                      |  |  |

| bit 5                                                                                                                                                                                                                                                                                                                                         | 1 = Tempera                                                                                                                                 | erature Indicator<br>ture Indicator i<br>ture Indicator i | s enabled                                                | )                           |                                                                              |                  |                      |  |  |

| bit 4                                                                                                                                                                                                                                                                                                                                         | 1 = VOUT = V                                                                                                                                | perature Indica<br>′DD - 4V⊤ (Higł<br>′DD - 2V⊤ (Low      | Range)                                                   | election bit <sup>(3)</sup> |                                                                              |                  |                      |  |  |

| bit 3-2                                                                                                                                                                                                                                                                                                                                       | 11 = Compara<br>10 = Compara<br>01 = Compara                                                                                                | ator FVR Buffe<br>ator FVR Buffe                          | er Gain is 4x, v<br>er Gain is 2x, v<br>er Gain is 1x, v | vith output Vcc             | bits <sup>(1)</sup><br>DAFVR = 4x VFVF<br>DAFVR = 2x VFVF<br>DAFVR = 1x VFVF | <sub>2</sub> (4) |                      |  |  |

| bit 1-0 <b>ADFVR&lt;1:0&gt;:</b> ADC FVR Buffer Gain Selection bit <sup>(1)</sup><br>11 = ADC FVR Buffer Gain is 4x, with output VADFVR = 4x VFVR <sup>(4)</sup><br>10 = ADC FVR Buffer Gain is 2x, with output VADFVR = 2x VFVR <sup>(4)</sup><br>01 = ADC FVR Buffer Gain is 1x, with output VADFVR = 1x VFVR<br>00 = ADC FVR Buffer is off |                                                                                                                                             |                                                           |                                                          |                             |                                                                              |                  |                      |  |  |

| inę                                                                                                                                                                                                                                                                                                                                           | To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clear ing the Buffer Gain Selection bits. |                                                           |                                                          |                             |                                                                              |                  |                      |  |  |

## **REGISTER 14-1:** FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

- 2: FVRRDY is always '1' for the PIC16F1574/5/8/9 devices.

- 3: See Section 15.0 "Temperature Indicator Module" for additional information.

- 4: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR>1:0> |       | ADFV  | R<1:0> | 149                 |

**Legend:** Shaded cells are unused by the Fixed Voltage Reference module.

| R/W-x/u                                                                                  | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u | R/W-x/u      | R/W-x/u | R/W-x/u |

|------------------------------------------------------------------------------------------|---------|--------------------|---------|---------|--------------|---------|---------|

|                                                                                          |         |                    | ADRE    | S<9:2>  |              |         |         |

| bit 7                                                                                    |         |                    |         |         |              |         | bit 0   |

|                                                                                          |         |                    |         |         |              |         |         |

| Legend:                                                                                  |         |                    |         |         |              |         |         |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0'                 |         |                    |         |         |              |         |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other R |         |                    |         |         | other Resets |         |         |

| '1' = Bit is set                                                                         |         | '0' = Bit is clear | red     |         |              |         |         |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

#### **REGISTER 16-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRES<1:0> |         | —       | —       | —       | —       | —       | —       |

| bit 7      |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits Lower two bits of 10-bit conversion result bit 5-0 Reserved: Do not use.

## 20.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 20-1 displays the Timer1 enable selections.

| TABLE 20-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 20.2 Clock Source Selection

The TMR1CS<1:0> bits of the T1CON register are used to select the clock source for Timer1. Table 20-2 displays the clock source selections.

#### 20.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

#### 20.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI. The external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- · Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

#### TABLE 20-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | T1OSCEN <sup>(1)</sup> | Clock Source                   |

|-------------|------------------------|--------------------------------|

| 11          | x                      | LFINTOSC                       |

| 10          | x                      | External Clocking on T1CKI Pin |

| 01          | x                      | System Clock (Fosc)            |

| 0 0         | x                      | Instruction Clock (Fosc/4)     |

Note 1: T1OSC is not available on all devices.

## 20.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

## 20.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

# 20.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 20-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

#### 20.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 20-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 20-6 for timing details.

## 20.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 20.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

| Name    | Bit 7     | Bit 6                                   | Bit 5  | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------|-----------------------------------------|--------|------------|------------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF    | RCIDL                                   |        | SCKP       | BRG16      |        | WUE    | ABDEN  | 204                 |

| INTCON  | GIE       | PEIE                                    | TMR0IE | INTE       | IOCIE      | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1    | TMR1GIE   | ADIE                                    | RCIE   | TXIE       | —          | _      | TMR2IE | TMR1IE | 87                  |

| PIR1    | TMR1GIF   | ADIF                                    | RCIF   | TXIF       | —          | _      | TMR2IF | TMR1IF | 90                  |

| RCREG   |           |                                         | EUS    | ART Receiv | e Data Reg | gister |        |        | 197*                |

| RCSTA   | SPEN      | SPEN RX9 SREN CREN ADDEN FERR OERR RX9D |        |            |            |        |        | 203*   |                     |

| SPBRGL  | BRG<7:0>  |                                         |        |            |            | 205*   |        |        |                     |

| SPBRGH  | BRG<15:8> |                                         |        |            |            | 205*   |        |        |                     |

| TXSTA   | CSRC      | TX9                                     | TXEN   | SYNC       | SENDB      | BRGH   | TRMT   | TX9D   | 202                 |

#### TABLE 22-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

# 23.7 Register Definitions: PWM Control

Long bit name prefixes for the 16-bit PWM peripherals are shown in Table 23-1. Refer to **Section 1.1 "Register and Bit Naming Conventions**" for more information

#### TABLE 23-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| PWM1       | PWM1            |

| PWM2       | PWM2            |

| PWM3       | PWM3            |

| PWM4       | PWM4            |

## REGISTER 23-1: PWMxCON: PWM CONTROL REGISTER

| R/W-0/0 | U-0 | R/HS/HC-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0   |

|---------|-----|-------------|---------|---------|---------|-----|-------|

| EN      | —   | OUT         | POL     | MODE    | E<1:0>  | —   | _     |

| bit 7   |     |             |         |         |         |     | bit 0 |

| Legend:                                  |                  |                               |                                                       |

|------------------------------------------|------------------|-------------------------------|-------------------------------------------------------|

| HC = Bit i                               | s cleared by ha  | rdware                        | HS = Bit is set by hardware                           |

| R = Read                                 | able bit         | W = Writable bit              | U = Unimplemented bit, read as '0'                    |

| u = Bit is                               | unchanged        | x = Bit is unknown            | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is                             | set              | '0' = Bit is cleared          |                                                       |

|                                          |                  |                               |                                                       |

| bit 7                                    | EN: PWM          | Module Enable bit             |                                                       |

|                                          |                  | le is enabled                 |                                                       |

|                                          | 0 = Modu         | le is disabled                |                                                       |

| bit 6                                    | Unimplen         | nented: Read as '0'           |                                                       |

| bit 5                                    | OUT: Outp        | out State of the PWM module   |                                                       |

| bit 4                                    | POL: PWI         | M Output Polarity Control bit |                                                       |

|                                          | 1 = PWM          | output active state is low    |                                                       |

|                                          | 0 = PWM          | output active state is high   |                                                       |