Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-UQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1574-e-ig |

TABLE 3-13: PIC16(L)F1574/5/8/9 MEMORY MAP, BANK 31

|         |      | , 27                 |                   |

|---------|------|----------------------|-------------------|

|         |      | Bank 31              |                   |

|         | F8Ch |                      |                   |

|         |      | Unimplemented        |                   |

|         |      | Read as '0'          |                   |

|         |      |                      |                   |

|         | FE3h |                      |                   |

|         | FE4h | STATUS_SHAD          |                   |

|         | FE5h | WREG_SHAD            |                   |

|         | FE6h | BSR_SHAD             |                   |

|         | FE7h | PCLATH_SHAD          |                   |

|         | FE8h | FSR0L_SHAD           |                   |

|         | FE9h | FSR0H_SHAD           |                   |

|         | FEAh | FSR1L_SHAD           |                   |

|         | FEBh | FSR1H_SHAD           |                   |

|         | FECh | _                    |                   |

|         | FEDh | STKPTR               |                   |

|         | FEEh | TOSL                 |                   |

|         | FEFh | TOSH                 |                   |

|         |      | •                    |                   |

|         |      |                      |                   |

| Legend: |      | Unimplemented data n | nemory locations, |

|         | read | l as '0'.            |                   |

|         |      |                      |                   |

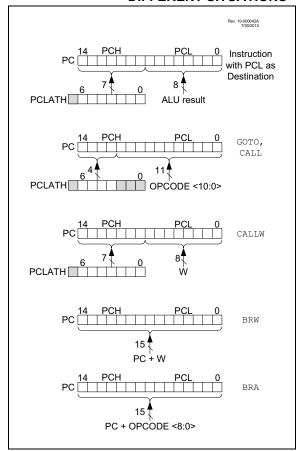

### 3.4 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-4 shows the five situations for the loading of the PC.

FIGURE 3-4: LOADING OF PC IN DIFFERENT SITUATIONS

### 3.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

#### 3.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, "Implementing a Table Read" (DS00556).

#### 3.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

# 4.2 Register Definitions: Configuration Words

### **REGISTER 4-1: CONFIGURATION WORD 1**

| U-1    | U-1 | R/P-1    | R/P-1         | R/P-1 | U-1   |

|--------|-----|----------|---------------|-------|-------|

| _      | _   | CLKOUTEN | BOREN<1:0>(1) |       | _     |

| bit 13 |     |          |               |       | bit 8 |

| R/P-1         | R/P-1 | R/P-1                | R/P-1     | R/P-1 | U-1 | R/P-1 | R/P-1 |  |

|---------------|-------|----------------------|-----------|-------|-----|-------|-------|--|

| <u>CP</u> (2) | MCLRE | PWRTE <sup>(1)</sup> | WDTE<1:0> |       | _   | FOSC  | <1:0> |  |

| bit 7         |       |                      |           |       |     |       | bit 0 |  |

| Legend:              |                      |                                          |

|----------------------|----------------------|------------------------------------------|

| R = Readable bit     | P = Programmable bit | U = Unimplemented bit, read as '1'       |

| '0' = Bit is cleared | '1' = Bit is set     | n = Value when blank or after Bulk Erase |

| bit 13-12 | Unimplemented: Read as '1' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 11 CLKOUTEN: Clock Out Enable bit

1 = OFF - CLKOUT function is disabled. I/O or oscillator function on CLKOUT pin

0 = ON - CLKOUT function is enabled on CLKOUT pin

bit 10-9 **BOREN<1:0>:** Brown-out Reset Enable bits<sup>(1)</sup>

11 = ON - Brown-out Reset enabled. The SBOREN bit is ignored.

10 = SLEEP - Brown-out Reset enabled while running and disabled in Sleep. The SBOREN bit is ignored.

01 = SBODEN- Brown-out Reset controlled by the SBOREN bit in the BORCON register

00 = OFF — Brown-out Reset disabled. The SBOREN bit is ignored.

bit 8 Unimplemented: Read as '1'

1 = OFF – Code protection off. Program Memory can be read and written.

0 = ON - Code protection on. Program Memory cannot be read or written externally.

bit 6 MCLRE: MCLR/VPP Pin Function Select bit

If LVP bit = 1 (ON):

This bit is ignored. MCLR/VPP pin function is MCLR; Weak pull-up enabled.

If LVP bit = 0 (OFF):

1 = ON  $-\overline{MCLR}/VPP$  pin function is  $\overline{MCLR}$ ; Weak pull-up enabled.

0 = OFF – MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of pin's WPU control bit.

bit 5 **PWRTE**: Power-up Timer Enable bit<sup>(1)</sup>

1 = OFF-PWRT disabled

0 = ON - PWRT enabled

bit 4-3 WDTE<1:0>: Watchdog Timer Enable bit

11 = ON - WDT enabled. SWDTEN is ignored.

10 = SLEEP - WDT enabled while running and disabled in Sleep. SWDTEN is ignored.

01 = SWDTEN- WDT controlled by the SWDTEN bit in the WDTCON register

00 = OFF - WDT disabled. SWDTEN is ignored.

bit 2 Unimplemented: Read as '1'

bit 1-0 FOSC<1:0>: Oscillator Selection bits

11 = ECH - External Clock, High-Power mode: CLKI on CLKI

10 = ECM - External Clock, Medium Power mode: CLKI on CLKI

01 = ECL - External Clock, Low-Power mode: CLKI on CLKI

00 = INTOSC-I/O function on CLKI

Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

2: Once enabled, code-protect can only be disabled by bulk erasing the device.

## 5.0 OSCILLATOR MODULE

### 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external logic level clocks. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

Selectable system clock source between external or internal sources via software. The oscillator module can be configured in one of the following clock modes.

- ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- ECM External Clock Medium Power mode (0.5 MHz to 4 MHz)

- ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. INTOSC Internal oscillator (31 kHz to 32 MHz).

Clock Source modes are selected by the FOSC<1:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source.

The INTOSC internal oscillator block produces low, medium, and high-frequency clock sources, designated LFINTOSC, MFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these three clock sources.

# 5.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 5-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), and peripherals, are *not* affected by the change in frequency.

#### 5.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.8** "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT) and Watchdog Timer (WDT).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

#### 5.2.2.5 FRC

The FRC clock is an uncalibrated, nominal 600 kHz peripheral clock source.

The FRC is automatically turned on by the peripherals requesting the FRC clock.

The FRC clock will continue to run during Sleep.

# 5.2.2.6 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits, IRCF<3:0> of the OSCCON register.

The postscaler outputs of the 16 MHz HFINTOSC, **500 kHz MFINTOSC**, and **31 kHz** LFINTOSC output connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

Note: Following any Reset, the IRCF<3:0> bits of the OSCCON register are set to '0111' and the frequency selection is set to 500 kHz. The user can modify the IRCF bits to select a different frequency.

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

## 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Internal Oscillator Block (INTOSC)

# 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<1:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

Note: Any automatic clock switch does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

### 5.4 Clock Switching Before Sleep

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock Status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

TABLE 5-1: OSCILLATOR SWITCHING DELAYS

| Switch From      | Switch To                                                               | Frequency                                       | Oscillator Delay                    |

|------------------|-------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------|

| Sleep/POR        | LFINTOSC <sup>(1)</sup> MFINTOSC <sup>(1)</sup> HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (TWARM)(2) |

| Sleep/POR        | EC <sup>(1)</sup>                                                       | DC – 32 MHz                                     | 2 cycles                            |

| LFINTOSC         | EC <sup>(1)</sup>                                                       | DC – 32 MHz                                     | 1 cycle of each                     |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                      | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                      |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                 | 31 kHz                                          | 1 cycle of each                     |

| PLL inactive     | PLL active                                                              | 16-32 MHz                                       | 2 ms (approx.)                      |

Note 1: PLL inactive.

2: See Section 27.0 "Electrical Specifications".

### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| U-0   | R-0/q | R-q/q | R-0/q  | R-0/q  | R-q/q  | R-0/q  | R-0/q  |

|-------|-------|-------|--------|--------|--------|--------|--------|

| _     | PLLR  | OSTS  | HFIOFR | HFIOFL | MFIOFR | LFIOFR | HFIOFS |

| bit 7 |       |       |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared g = Conditional

bit 7 **Unimplemented:** Read as '0'

bit 6 PLLR 4x PLL Ready bit

1 = 4x PLL is ready 0 = 4x PLL is not ready

bit 5 OSTS: Oscillator Start-up Timer Status bit

1 = Running from the clock defined by the FOSC<1:0> bits of the Configuration Words

0 = Running from an internal oscillator (FOSC<1:0> = 00)

bit 4 HFIOFR: High-Frequency Internal Oscillator Ready bit

1 = HFINTOSC is ready

0 = HFINTOSC is not ready

bit 3 HFIOFL: High-Frequency Internal Oscillator Locked bit

1 = HFINTOSC is at least 2% accurate 0 = HFINTOSC is not 2% accurate

bit 2 MFIOFR: Medium-Frequency Internal Oscillator Ready bit

1 = MFINTOSC is ready

0 = MFINTOSC is not ready

bit 1 LFIOFR: Low-Frequency Internal Oscillator Ready bit

1 = LFINTOSC is ready0 = LFINTOSC is not ready

bit 0 **HFIOFS:** High-Frequency Internal Oscillator Stable bit

1 = HFINTOSC is at least 0.5% accurate 0 = HFINTOSC is not 0.5% accurate

TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name       | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|------------|------------------------|------------------------|---------|---------|---------|---------|---------|---------|------------------|

| ANSELC     | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | _       | _       | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 132              |

| INLVLC     | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 133              |

| LATC       | LATC7 <sup>(1)</sup>   | LATC6 <sup>(1)</sup>   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 131              |

| ODCONC     | ODC7 <sup>(1)</sup>    | ODC6 <sup>(1)</sup>    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    | 133              |

| OPTION_REG | WPUEN                  | INTEDG                 | TMR0CS  | TMR0SE  | PSA     | PS<2:0> |         |         | 178              |

| PORTC      | RC7 <sup>(1)</sup>     | RC6 <sup>(1)</sup>     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 131              |

| SLRCONC    | SLRC7 <sup>(1)</sup>   | SLRC6 <sup>(1)</sup>   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 133              |

| TRISC      | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 131              |

| WPUC       | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 132              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: PIC16(L)F1578/9 only.

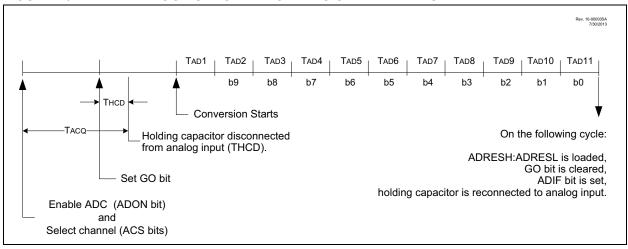

TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock Period (TAD) Device Frequency |            |            |            |              | osc)       |            |

|-----------------------------------------|------------|------------|------------|--------------|------------|------------|

| ADC<br>Clock<br>Source                  | ADCS<2:0 > | 20 MHz     | 16 MHz     | 16 MHz 8 MHz |            | 1 MHz      |

| Fosc/2                                  | 000        | 100 ns     | 125 ns     | 250 ns       | 500 ns     | 2.0 μs     |

| Fosc/4                                  | 100        | 200 ns     | 250 ns     | 500 ns       | 1.0 μs     | 4.0 μs     |

| Fosc/8                                  | 001        | 400 ns     | 500 ns     | 1.0 μs       | 2.0 μs     | 8.0 μs     |

| Fosc/16                                 | 101        | 800 ns     | 1.0 µs     | 2.0 μs       | 4.0 μs     | 16.0 μs    |

| Fosc/32                                 | 010        | 1.6 μs     | 2.0 μs     | 4.0 μs       | 8.0 µs     | 32.0 μs    |

| Fosc/64                                 | 110        | 3.2 μs     | 4.0 μs     | 8.0 µs       | 16.0 μs    | 64.0 μs    |

| FRC                                     | x11        | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs   | 1.0-6.0 μs | 1.0-6.0 μs |

Legend: Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range, (see TAD parameter). The TAD period when using the Fosc-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

FIGURE 16-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

### 16.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register)

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- Read ADC Result.

- Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 16.4 "ADC Acquisition Requirements".

### **EXAMPLE 16-1: ADC CONVERSION**

```

; This code block configures the ADC

; for polling, Vdd and Vss references, FRC

; oscillator and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL

ADCON1

B'11110000' ; Right justify, FRC

MOVLW

;oscillator

MOVWF

ADCON1

;Vdd and Vss Vref+

BANKSEL

TRISA

TRISA,0

;Set RAO to input

BSF

BANKSEL

ANSEL

BSF

ANSEL,0

;Set RAO to analog

BANKSEL

WPUA

BCF

WPUA,0

;Disable weak

;pull-up on RA0

BANKSEL

ADCON0

B'00000001' ;Select channel AN0

MOVLW

MOVWF

ADCONO ; Turn ADC On

CALL

SampleTime ;Acquisiton delay

BSF

ADCON0, ADGO ; Start conversion

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

$-1

;No, test again

BANKSEL

ADRESH

ADRESH,W

MOVF

;Read upper 2 bits

MOVWF

RESULTHI

;store in GPR space

BANKSEL

ADRESL

MOVF

ADRESL,W

;Read lower 8 bits

MOVWF

RESULTLO

;Store in GPR space

```

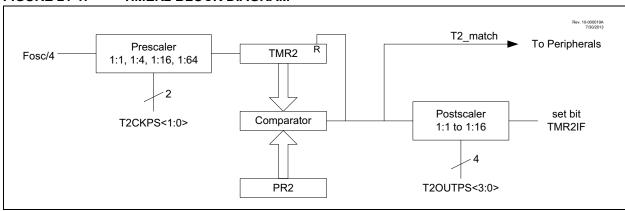

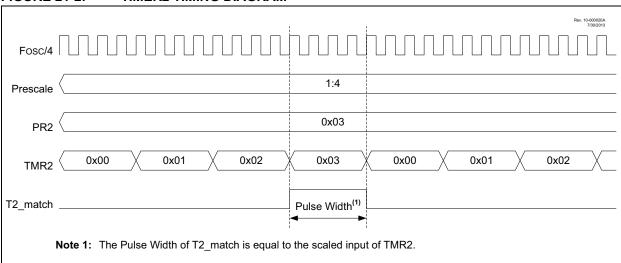

## 21.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- · Interrupt on TMR2 match with PR2

See Figure 21-1 for a block diagram of Timer2.

FIGURE 21-1: TIMER2 BLOCK DIAGRAM

### FIGURE 21-2: TIMER2 TIMING DIAGRAM

# REGISTER 22-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R-0/0 |

|---------|---------|---------|---------|---------|-------|-------|-------|

| SPEN    | RX9     | SREN    | CREN    | ADDEN   | FERR  | OERR  | RX9D  |

| bit 7   |         |         |         |         |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)

0 = Serial port disabled (held in Reset)

bit 6 **RX9:** 9-bit Receive Enable bit

1 = Selects 9-bit reception0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Don't care

<u>Synchronous mode – Master:</u>

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - Slave

Don't care

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables receiver

0 = Disables receiver

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

Asynchronous mode 8-bit (RX9 = 0):

Don't care

bit 2 FERR: Framing Error bit

1 = Framing error (can be updated by reading RCREG register and receive next valid byte)

0 = No framing error

bit 1 **OERR:** Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 **RX9D:** Ninth bit of Received Data

This can be address/data bit or a parity bit and must be calculated by user firmware.

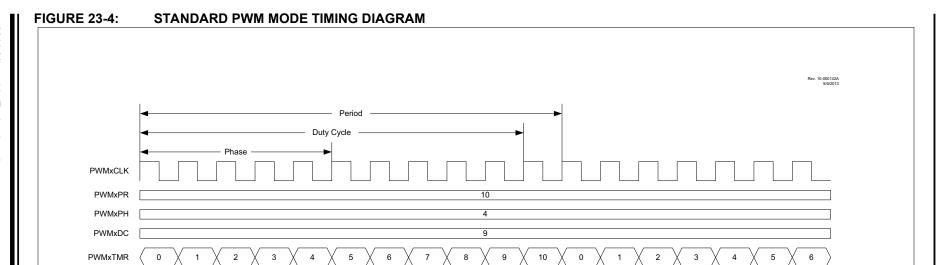

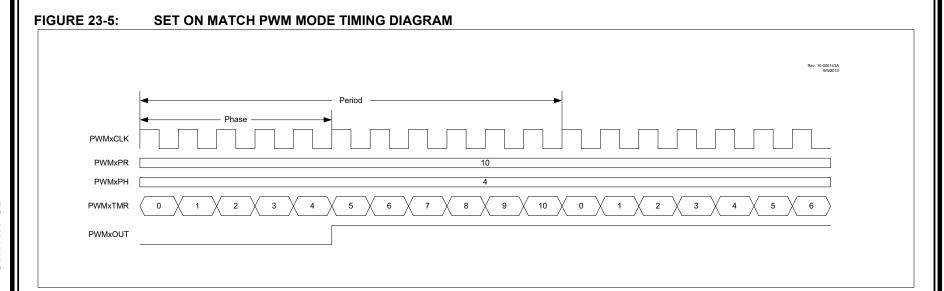

**PWMxOUT**

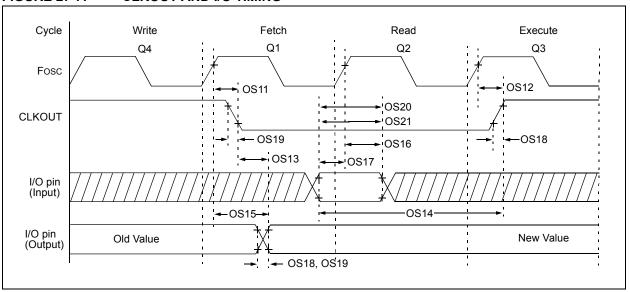

FIGURE 27-7: CLKOUT AND I/O TIMING

**TABLE 27-10: CLKOUT AND I/O TIMING PARAMETERS**

| Standard      | Standard Operating Conditions (unless otherwise stated) |                                                            |               |          |          |       |                                               |  |  |  |  |

|---------------|---------------------------------------------------------|------------------------------------------------------------|---------------|----------|----------|-------|-----------------------------------------------|--|--|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                                             | Min.          | Тур†     | Max.     | Units | Conditions                                    |  |  |  |  |

| OS11          | TosH2ckL                                                | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                            | _             | _        | 70       | ns    | $3.3 V \leq V_{DD} \leq 5.0 V$                |  |  |  |  |

| OS12          | TosH2ckH                                                | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                            | _             | _        | 72       | ns    | $3.3V \leq V_{DD} \leq 5.0V$                  |  |  |  |  |

| OS13          | TckL2ioV                                                | CLKOUT↓ to Port out valid <sup>(1)</sup>                   | _             | _        | 20       | ns    |                                               |  |  |  |  |

| OS14          | TioV2ckH                                                | Port input valid before CLKOUT↑ <sup>(1)</sup>             | Tosc + 200 ns | _        | _        | ns    |                                               |  |  |  |  |

| OS15          | TosH2ioV                                                | Fosc↑ (Q1 cycle) to Port out valid                         | _             | 50       | 70*      | ns    | $3.3V \leq V_{DD} \leq 5.0V$                  |  |  |  |  |

| OS16          | TosH2ioI                                                | Fosc↑ (Q2 cycle) to Port input invalid (I/O in setup time) | 50            | _        | _        | ns    | $3.3 V \leq V \text{DD} \leq 5.0 V$           |  |  |  |  |

| OS17          | TioV2osH                                                | Port input valid to Fosc↑ (Q2 cycle) (I/O in setup time)   | 20            | _        | _        | ns    |                                               |  |  |  |  |

| OS18*         | TioR                                                    | Port output rise time                                      | _             | 40       | 72       | ns    | VDD = 1.8V                                    |  |  |  |  |

|               |                                                         |                                                            | _             | 15       | 32       |       | $3.3V \leq V \text{DD} \leq 5.0V$             |  |  |  |  |

| OS19*         | TioF                                                    | Port output fall time                                      |               | 28<br>15 | 55<br>30 | ns    | $V_{DD} = 1.8V$<br>$3.3V \le V_{DD} \le 5.0V$ |  |  |  |  |

| OS20*         | Tinp                                                    | INT pin input high or low time                             | 25            | _        | _        | ns    |                                               |  |  |  |  |

| OS21*         | Tioc                                                    | Interrupt-on-change new input level time                   | 25            | _        | _        | ns    |                                               |  |  |  |  |

These parameters are characterized but not tested.

Note 1: Measurements are taken in EXTRC mode where CLKOUT output is 4 x Tosc.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

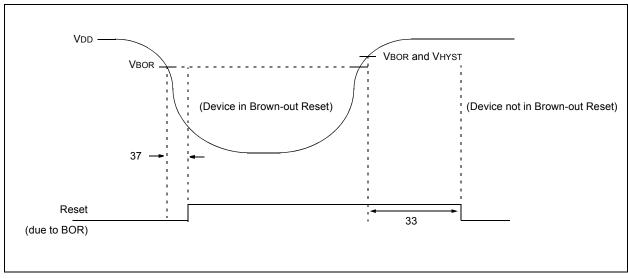

TABLE 27-11: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET PARAMETERS

| Standard Operating Conditions (unless otherwise stated) |        |                                                          |      |      |      |       |                                                       |  |  |  |

|---------------------------------------------------------|--------|----------------------------------------------------------|------|------|------|-------|-------------------------------------------------------|--|--|--|

| Param.<br>No.                                           | Sym.   | Characteristic                                           | Min. | Тур† | Max. | Units | Conditions                                            |  |  |  |

| 30                                                      | ТмсL   | MCLR Pulse Width (low)                                   | 2    | _    | _    | μS    |                                                       |  |  |  |

| 31                                                      | TWDTLP | Low-Power Watchdog Timer<br>Time-out Period              | 10   | 16   | 27   | ms    | VDD = 3.3V-5V,<br>1:512 Prescaler used                |  |  |  |

| 32                                                      | Tost   | Oscillator Start-up Timer Period <sup>(1)</sup>          | _    | 1024 | _    | Tosc  |                                                       |  |  |  |

| 33*                                                     | TPWRT  | Power-up Timer Period                                    | 40   | 65   | 140  | ms    | PWRTE = 0                                             |  |  |  |

| 34*                                                     | Tioz   | I/O high-impedance from MCLR Low or Watchdog Timer Reset | _    |      | 2.0  | μS    |                                                       |  |  |  |

| 35                                                      | VBOR   | Brown-out Reset Voltage <sup>(2)</sup>                   | 2.55 | 2.70 | 2.85 | V     | BORV = 0                                              |  |  |  |

|                                                         |        |                                                          | 2.35 | 2.45 | 2.58 | V     | BORV = 1                                              |  |  |  |

|                                                         |        |                                                          | 1.80 | 1.90 | 2.05 | V     | (PIC16F1574/5/8/9)<br>BORV = 1<br>(PIC16LF1574/5/8/9) |  |  |  |

| 36*                                                     | VHYST  | Brown-out Reset Hysteresis                               | 0    | 25   | 60   | mV    | $-40^{\circ}C \le TA \le +85^{\circ}C$                |  |  |  |

| 37*                                                     | TBORDC | Brown-out Reset DC Response Time                         | 1    | 16   | 35   | μS    | VDD ≤ VBOR                                            |  |  |  |

| 38                                                      | VLPBOR | Low-Power Brown-Out Reset Voltage                        | 1.8  | 2.1  | 2.5  | V     | LPBOR = 1                                             |  |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

- 2: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

FIGURE 27-9: BROWN-OUT RESET TIMING AND CHARACTERISTICS

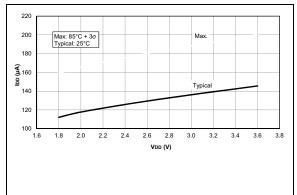

FIGURE 28-13: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16LF1574/5/8/9 Only.

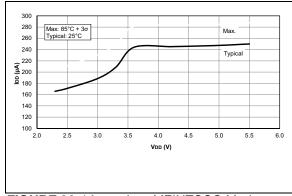

FIGURE 28-14: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16F1574/5/8/9 Only.

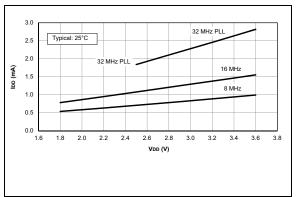

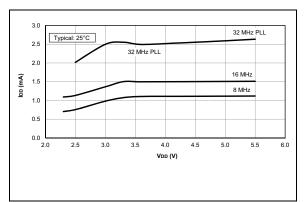

FIGURE 28-15: IDD Typical, HFINTOSC Mode, PIC16LF1574/5/8/9 Only.

FIGURE 28-16: IDD Maximum, HFINTOSC Mode, PIC16LF1574/5/8/9 Only.

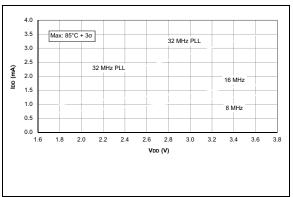

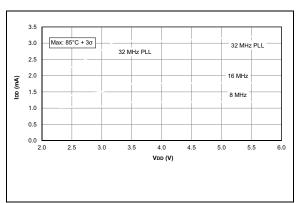

FIGURE 28-17: IDD Typical, HFINTOSC Mode, PIC16F1574/5/8/9 Only.

FIGURE 28-18: IDD Maximum, HFINTOSC Mode, PIC16F1574/5/8/9 Only.

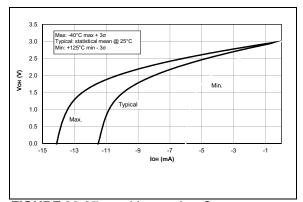

FIGURE 28-37: VOH vs. IOH Over Temperature, VDD = 3.0V.

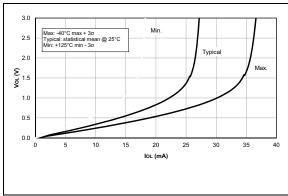

FIGURE 28-38: Vol. vs. Iol Over Temperature, VDD = 3.0V.

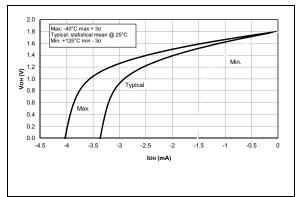

FIGURE 28-39: VOH VS. IOH OVER

Temperature, VDD = 1.8V, PIC16LF1574/5/8/9

Only.

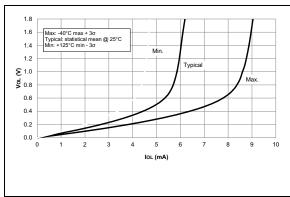

**FIGURE 28-40:** Vol vs. Iol Over Temperature, VDD = 1.8V, PIC16LF1574/5/8/9 Only.

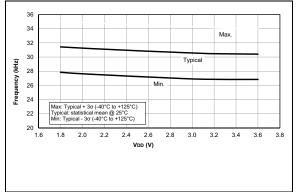

FIGURE 28-41: LFINTOSC Frequency Over VDD and Temperature, PIC16LF1574/5/8/9 Only.

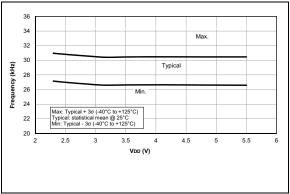

FIGURE 28-42: LFINTOSC Frequency Over VDD and Temperature, PIC16F1574/5/8/9 Only.

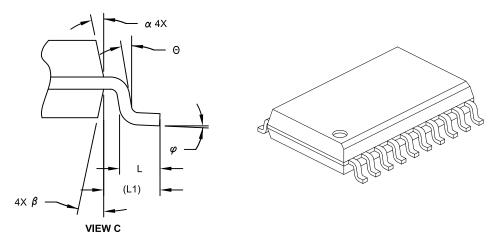

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |

|--------------------------|-------------|-----------|-----|------|--|

| Dimension Lim            | nits        | MIN       | NOM | MAX  |  |

| Number of Pins           | N           | 20        |     |      |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |

| Overall Height           | Α           | -         | -   | 2.65 |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |

| Standoff §               | A1          | 0.10      | _   | 0.30 |  |

| Overall Width            | Е           | 10.30 BSC |     |      |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |

| Overall Length           | D           | 12.80 BSC |     |      |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |

| Lead Thickness           | С           | 0.20      | -   | 0.33 |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |

# Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2

Note:

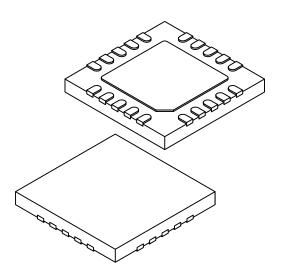

# 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |      |      |  |

|-------------------------|-------------|-----------|------|------|--|

| Dimension               | MIN         | NOM       | MAX  |      |  |

| Number of Terminals     | N           | 20        |      |      |  |

| Pitch                   | е           | 0.50 BSC  |      |      |  |

| Overall Height          | Α           | 0.45 0.50 |      | 0.55 |  |

| Standoff                | A1          | 0.00      | 0.02 | 0.05 |  |

| Terminal Thickness      | A3          | 0.127 REF |      |      |  |

| Overall Width           | Е           | 4.00 BSC  |      |      |  |

| Exposed Pad Width       | E2          | 2.60      | 2.70 | 2.80 |  |

| Overall Length          | D           | 4.00 BSC  |      |      |  |

| Exposed Pad Length      | D2          | 2.60      | 2.70 | 2.80 |  |

| Terminal Width          | b           | 0.20      | 0.25 | 0.30 |  |

| Terminal Length         | L           | 0.30      | 0.40 | 0.50 |  |

| Terminal-to-Exposed-Pad | K           | 0.20      | -    | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-255A Sheet 2 of 2