### Microchip Technology - PIC16LF1574-E/P Datasheet

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1574-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-2:PIC16(L)F1574/5 PINOUT DESCRIPTION (CONTINUED)

| Name                                         | Function          | Input<br>Type | Output<br>Type | Description                                          |

|----------------------------------------------|-------------------|---------------|----------------|------------------------------------------------------|

| RC4/ADCACT <sup>(1)</sup> /CK <sup>(1)</sup> | RC4               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

|                                              | ADCACT            | TTL/ST        | —              | ADC Auto-conversion Trigger input.                   |

|                                              | СК                | ST            | CMOS           | USART synchronous clock.                             |

| RC5/RX <sup>(1,3)</sup>                      | RC5               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

|                                              | RX                | ST            | _              | USART asynchronous input.                            |

| OUT <sup>(2)</sup>                           | C10UT             | _             | CMOS           | Comparator output.                                   |

|                                              | C2OUT             | _             | CMOS           | Comparator output.                                   |

|                                              | PWM10UT           | -             | CMOS           | PWM1 output.                                         |

|                                              | PWM2OUT           | -             | CMOS           | PWM2 output.                                         |

|                                              | PWM3OUT           | _             | CMOS           | PWM3 output.                                         |

|                                              | PWM4OUT           | -             | CMOS           | PWM4 output.                                         |

|                                              | CWG1A             | _             | CMOS           | Complementary Output Generator Output A.             |

|                                              | CWG1B             | _             | CMOS           | Complementary Output Generator Output B.             |

|                                              | TX/CK             | -             | CMOS           | USART asynchronous TX data/synchronous clock output. |

|                                              | DT <sup>(3)</sup> | _             | CMOS           | USART synchronous data output.                       |

| VDD                                          | Vdd               | Power         | —              | Positive supply.                                     |

| Vss                                          | Vss               | Power         | —              | Ground reference.                                    |

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal

Levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-1.

3: These USART functions are bidirectional. The output pin selections must be the same as the input pin selections.

|    |      | BANK5          |      | BANK6          |      | BANK7          |

|----|------|----------------|------|----------------|------|----------------|

|    | 280h |                | 300h |                | 380h |                |

| rs |      | Core Registers |      | Core Registers |      | Core Registers |

|    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |

|    | 28Bh |                | 30Bh |                | 38Bh |                |

|    | 28Ch | ODCONA         | 30Ch | SLRCONA        | 38Ch | INLVLA         |

|    | 28Dh | _              | 30Dh | _              | 38Dh | _              |

|    | 28Eh | ODCONC         | 30Eh | SLRCONC        | 38Eh | INLVLC         |

|    | 28Fh | _              | 30Fh | _              | 38Fh | _              |

|    | 290h | _              | 310h | _              | 390h | _              |

|    | 291h | _              | 311h | _              | 391h | IOCAP          |

|    | 292h | _              | 312h | _              | 392h | IOCAN          |

|    | 293h | _              | 313h | _              | 393h | IOCAF          |

|    | 294h | _              | 314h | _              | 394h | _              |

|    | 295h | _              | 315h | _              | 395h | _              |

|    | 296h | _              | 316h | _              | 396h | _              |

|    | 297h | _              | 317h | _              | 397h | IOCCP          |

|    | 298h |                | 318h | _              | 398h | IOCCN          |

|    | 299h | _              | 319h | _              | 399h | IOCCF          |

|    | 29Ah | _              | 31Ah | _              | 39Ah | _              |

|    | 29Bh | _              | 31Bh | _              | 39Bh | _              |

|    | 29Ch |                | 31Ch |                | 39Ch | _              |

|    | 29Dh | _              | 31Dh | _              | 39Dh | _              |

|    | 20Fh |                | 2456 |                | 2056 |                |

\_

General Purpose Register 80 Bytes

Accesses 70h – 7Fh

#### TABLE 3-4: PIC16(L)F1575 MEMORY MAP, BANKS 0-7 BANK0 BANK1

BANK2

| 000h |                                            | 080h |                                            | 100h |                                            | 180h |                                            | 200h |                                            | 280h |                                            | 300h |                                            | 380h |   |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|---|

|      | Core Registers                             |      | C |

|      | (Table 3-2)                                |      |   |

| 00Bh |                                            | 08Bh |                                            | 10Bh |                                            | 18Bh |                                            | 20Bh |                                            | 28Bh |                                            | 30Bh |                                            | 38Bh |   |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                                     | 20Ch | WPUA                                       | 28Ch | ODCONA                                     | 30Ch | SLRCONA                                    | 38Ch |   |

| 00Dh | —                                          | 08Dh | —                                          | 10Dh | —                                          | 18Dh | _                                          | 20Dh | _                                          | 28Dh | _                                          | 30Dh | —                                          | 38Dh |   |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | ANSELC                                     | 20Eh | WPUC                                       | 28Eh | ODCONC                                     | 30Eh | SLRCONC                                    | 38Eh |   |

| 00Fh | —                                          | 08Fh | —                                          | 10Fh | —                                          | 18Fh |                                            | 20Fh | _                                          | 28Fh | —                                          | 30Fh | —                                          | 38Fh |   |

| 010h | —                                          | 090h | —                                          | 110h | —                                          | 190h | —                                          | 210h | —                                          | 290h | _                                          | 310h | —                                          | 390h |   |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | CM1CON0                                    | 191h | PMADRL                                     | 211h | —                                          | 291h | _                                          | 311h | —                                          | 391h |   |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | CM1CON1                                    | 192h | PMADRH                                     | 212h | —                                          | 292h | _                                          | 312h | —                                          | 392h |   |

| 013h | PIR3                                       | 093h | PIE3                                       | 113h | CM2CON0                                    | 193h | PMDATL                                     | 213h | _                                          | 293h | —                                          | 313h | —                                          | 393h |   |

| 014h | —                                          | 094h | —                                          | 114h | CM2CON1                                    | 194h | PMDATH                                     | 214h | _                                          | 294h | —                                          | 314h | —                                          | 394h |   |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h | CMOUT                                      | 195h | PMCON1                                     | 215h | _                                          | 295h | —                                          | 315h | —                                          | 395h |   |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | BORCON                                     | 196h | PMCON2                                     | 216h | _                                          | 296h | —                                          | 316h | —                                          | 396h |   |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | VREGCON <sup>(1)</sup>                     | 217h | —                                          | 297h | —                                          | 317h | —                                          | 397h |   |

| 018h | T1CON                                      | 098h | OSCTUNE                                    | 118h | DACCON0                                    | 198h | —                                          | 218h | —                                          | 298h | —                                          | 318h | _                                          | 398h |   |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | DACCON1                                    | 199h | RCREG                                      | 219h | —                                          | 299h | _                                          | 319h | _                                          | 399h |   |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah | —                                          | 19Ah | TXREG                                      | 21Ah | —                                          | 29Ah | —                                          | 31Ah | —                                          | 39Ah |   |

| 01Bh | PR2                                        | 09Bh | ADRESL                                     | 11Bh | —                                          | 19Bh | SPBRGL                                     | 21Bh | —                                          | 29Bh | —                                          | 31Bh | —                                          | 39Bh |   |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch | —                                          | 19Ch | SPBRGH                                     | 21Ch | _                                          | 29Ch | —                                          | 31Ch | _                                          | 39Ch |   |

| 01Dh | —                                          | 09Dh | ADCON0                                     | 11Dh | —                                          | 19Dh | RCSTA                                      | 21Dh | _                                          | 29Dh | _                                          | 31Dh | —                                          | 39Dh |   |

| 01Eh | —                                          | 09Eh | ADCON1                                     | 11Eh | —                                          | 19Eh | TXSTA                                      | 21Eh | _                                          | 29Eh | —                                          | 31Eh | —                                          | 39Eh |   |

| 01Fh | —                                          | 09Fh | ADCON2                                     | 11Fh | —                                          | 19Fh | BAUDCON                                    | 21Fh | —                                          | 29Fh | —                                          | 31Fh | —                                          | 39Fh |   |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h |                                            | 3A0h |   |

|      | General<br>Purpose<br>Register<br>80 Bytes |      |   |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                            | 3EFh |   |

| 070h |                                            | 0F0h |                                            | 170h |                                            | 1F0h |                                            | 270h |                                            | 2F0h |                                            | 370h |                                            | 3F0h |   |

|      | Common RAM                                 |      | Accesses<br>70h – 7Fh                      |      |   |

| 07Fh |                                            | 0FFh |                                            | 17Fh |                                            | 1FFh |                                            | 27Fh |                                            | 2FFh |                                            | 37Fh |                                            | 3FFh |   |

|      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |                                            |      |   |

BANK3

BANK4

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1575.

DS40001782C-page 26

### 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

### 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4 "Write Protection"** for more information.

### 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

### 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16(L)F157x Memory Programming Specification*" (DS40001766).

### 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

### 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Internal Oscillator Block (INTOSC)

### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<1:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

| Note: | Any automatic clock switch does not      |

|-------|------------------------------------------|

|       | update the SCS bits of the OSCCON        |

|       | register. The user can monitor the OSTS  |

|       | bit of the OSCSTAT register to determine |

|       | the current system clock source.         |

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

### 5.4 Clock Switching Before Sleep

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock Status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

| TABLE 5-1: | <b>OSCILLATOR SWITCHING DELAYS</b> |

|------------|------------------------------------|

|            | OUCLEATOR OWN ON TO DEER TO        |

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay                                |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| Sleep/POR        | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (Twarm) <sup>(2)</sup> |

| Sleep/POR        | EC <sup>(1)</sup>                                                             | DC – 32 MHz                                     | 2 cycles                                        |

| LFINTOSC         | EC <sup>(1)</sup>                                                             | DC – 32 MHz                                     | 1 cycle of each                                 |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                                  |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                                 |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)                                  |

Note 1: PLL inactive.

2: See Section 27.0 "Electrical Specifications".

| U-0              | U-0   | R/W-1/1           | R/W-1/1 | R/W-1/1                            | R/W-1/1       | R/W-1/1          | R/W-1/1      |  |  |  |

|------------------|-------|-------------------|---------|------------------------------------|---------------|------------------|--------------|--|--|--|

| _                | _     | WPUA5             | WPUA4   | WPUA3                              | WPUA2         | WPUA1            | WPUA0        |  |  |  |

| bit 7            |       |                   |         |                                    |               |                  | bit 0        |  |  |  |

|                  |       |                   |         |                                    |               |                  |              |  |  |  |

| Legend:          |       |                   |         |                                    |               |                  |              |  |  |  |

| R = Readable     | bit   | W = Writable      | bit     | U = Unimplemented bit, read as '0' |               |                  |              |  |  |  |

| u = Bit is uncha | anged | x = Bit is unkr   | nown    | -n/n = Value a                     | at POR and BO | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared    |                                    |               |                  |              |  |  |  |

| '1' = Bit is set |       | ʻ0' = Bit is clea | ared    |                                    |               |                  |              |  |  |  |

### REGISTER 11-5: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits<sup>(3)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

- **3:** For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

### REGISTER 11-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     |     |         | ODA4    | —   | ODA2    | ODA1    | ODA0    |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>ODA&lt;5:4&gt;:</b> PORTA Open-Drain Enable bits<br>For RA<5:4> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0 | <b>ODA&lt;2:0&gt;:</b> PORTA Open-Drain Enable bits<br>For RA<2:0> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

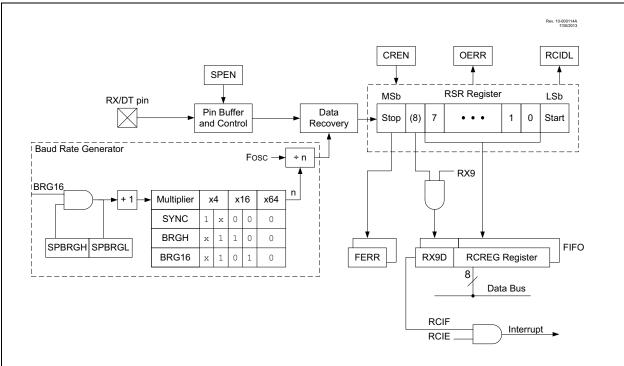

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

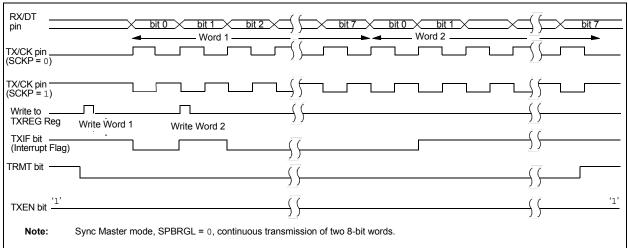

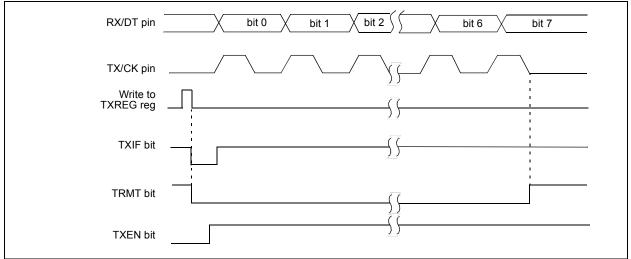

### FIGURE 22-10: SYNCHRONOUS TRANSMISSION

## TABLE 22-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|---------|-------------------------------|-------|--------|-------|-------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL | —      | SCKP  | BRG16 | —      | WUE    | ABDEN  | 204                 |

| INTCON  | GIE                           | PEIE  | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1    | TMR1GIE                       | ADIE  | RCIE   | TXIE  | —     | —      | TMR2IE | TMR1IE | 87                  |

| PIR1    | TMR1GIF                       | ADIF  | RCIF   | TXIF  | —     | —      | TMR2IF | TMR1IF | 90                  |

| RCSTA   | SPEN                          | RX9   | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 203                 |

| SPBRGL  |                               |       |        | BRG   | <7:0> |        |        |        | 205*                |

| SPBRGH  | BRG<15:8>                     |       |        |       |       |        |        |        |                     |

| TXREG   | EUSART Transmit Data Register |       |        |       |       |        |        |        |                     |

| TXSTA   | CSRC                          | TX9   | TXEN   | SYNC  | SENDB | BRGH   | TRMT   | TX9D   | 202                 |

|         | •                             |       | •      | -     |       | •      | -      |        | •                   |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission.

\* Page provides register information.

PIC16(L)F1574/5/8/9

|                    | R/W-0/0                                                                                                                            | R/W-0/0                                                                                                                                                       | R/W-0/0                                                     | U-0                                           | U-0                                   | R/W-0/0         | R/W-0/0       |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|---------------------------------------|-----------------|---------------|--|--|--|

| _                  | OF                                                                                                                                 | VI<1:0>                                                                                                                                                       | OFO <sup>(1)</sup>                                          | _                                             | _                                     | OFS             | <1:0>         |  |  |  |

| bit 7              |                                                                                                                                    |                                                                                                                                                               |                                                             |                                               |                                       |                 | bit C         |  |  |  |

|                    |                                                                                                                                    |                                                                                                                                                               |                                                             |                                               |                                       |                 |               |  |  |  |

| Legend:            |                                                                                                                                    |                                                                                                                                                               |                                                             |                                               |                                       |                 |               |  |  |  |

| R = Readab         | le bit                                                                                                                             | W = Writable b                                                                                                                                                | bit                                                         | U = Unimplem                                  | nented bit, rea                       | d as '0'        |               |  |  |  |

| u = Bit is un      | changed                                                                                                                            | x = Bit is unkn                                                                                                                                               | own                                                         | -n/n = Value a                                | t POR and BC                          | R/Value at all  | other Resets  |  |  |  |

| 1' = Bit is s      | et                                                                                                                                 | '0' = Bit is clea                                                                                                                                             | red                                                         |                                               |                                       |                 |               |  |  |  |

|                    |                                                                                                                                    |                                                                                                                                                               |                                                             |                                               |                                       |                 |               |  |  |  |

| bit 7              | Unimpleme                                                                                                                          | nted: Read as '0                                                                                                                                              | )'                                                          |                                               |                                       |                 |               |  |  |  |

| bit 6-5            | OFM<1:0>:                                                                                                                          | Offset Mode Sel                                                                                                                                               | ect bits                                                    |                                               |                                       |                 |               |  |  |  |

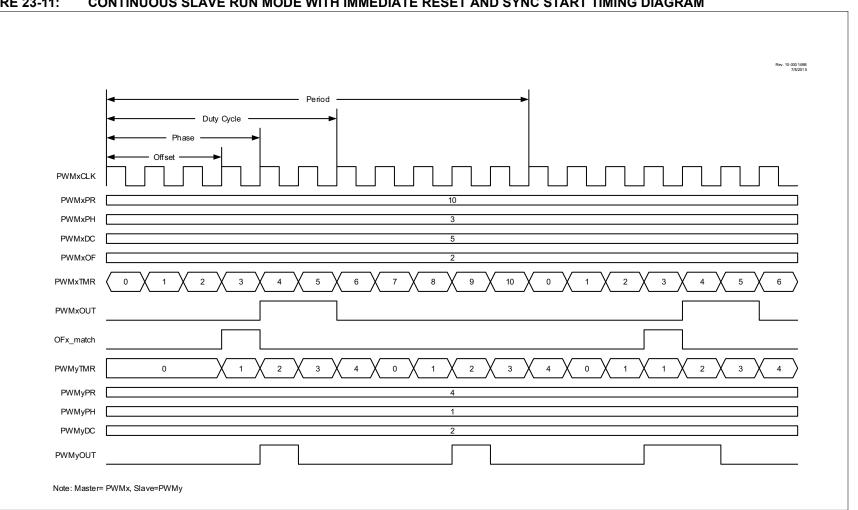

|                    | 11 = Continu                                                                                                                       | uous Slave Run                                                                                                                                                | mode with Imn                                               | nediate Reset a                               | and synchroniz                        | zed start, wher | n the selecte |  |  |  |

|                    |                                                                                                                                    | Offset Trigger occurs.                                                                                                                                        |                                                             |                                               |                                       |                 |               |  |  |  |

|                    |                                                                                                                                    | ot Slave Run mo                                                                                                                                               |                                                             |                                               |                                       |                 |               |  |  |  |

|                    |                                                                                                                                    | ndent Slave Run                                                                                                                                               | •                                                           | chronized start                               | , when the sele                       | ected Offset Tr | igger occurs  |  |  |  |

|                    | •                                                                                                                                  | ndent Run mode                                                                                                                                                |                                                             |                                               |                                       |                 |               |  |  |  |

| bit 4              |                                                                                                                                    |                                                                                                                                                               | ontrol bit                                                  | 4 <b>OFO:</b> Offset Match Output Control bit |                                       |                 |               |  |  |  |

|                    | If MODE<1:0> = 11 (PWM Center-Aligned mode):                                                                                       |                                                                                                                                                               |                                                             |                                               |                                       |                 |               |  |  |  |

|                    |                                                                                                                                    |                                                                                                                                                               |                                                             |                                               | · · · · · · · · · · · · · · · · · · · |                 |               |  |  |  |

|                    | 1 = OFx_ma                                                                                                                         | atch occurs on co                                                                                                                                             | ounter match w                                              | hen counter de                                |                                       |                 |               |  |  |  |

|                    | $1 = OFx_ma$<br>$0 = OFx_ma$                                                                                                       | atch occurs on co<br>atch occurs on co                                                                                                                        | ounter match w                                              | hen counter de<br>hen counter inc             |                                       |                 |               |  |  |  |

|                    | 1 = OFx_ma<br>0 = OFx_ma<br>If MODE<1:0                                                                                            | atch occurs on co<br>atch occurs on co<br>0 > = 00, 01  or                                                                                                    | ounter match w                                              | hen counter de<br>hen counter inc             |                                       |                 |               |  |  |  |

| bit 3-2            | 1 = OFx_ma<br>0 = OFx_ma<br><u>If MODE&lt;1:(</u><br>bit is ignored                                                                | atch occurs on co<br>atch occurs on co<br>D = 00, 01 or                                                                                                       | ounter match w<br>ounter match w<br>10 (all other mo        | hen counter de<br>hen counter inc             |                                       |                 |               |  |  |  |

|                    | 1 = OFx_ma<br>0 = OFx_ma<br><u>If MODE&lt;1:(</u><br>bit is ignored<br><b>Unimpleme</b>                                            | atch occurs on co<br>atch occurs on co<br><u>D = 00, 01 or</u><br>1<br>nted: Read as '0                                                                       | punter match w<br>punter match w<br>10 <u>(all other mo</u> | rhen counter de<br>rhen counter inc<br>odes): |                                       |                 |               |  |  |  |

| bit 3-2<br>bit 1-0 | 1 = OFx_ma<br>0 = OFx_ma<br><u>If MODE&lt;1:(</u><br>bit is ignored<br><b>Unimplemen</b><br><b>OFS&lt;1:0&gt;:</b> (               | atch occurs on co<br>atch occurs on co<br><u>D = 00, 01 or</u><br>I<br><b>nted:</b> Read as '0<br>Offset Trigger Sc                                           | punter match w<br>punter match w<br>10 <u>(all other mo</u> | rhen counter de<br>rhen counter inc<br>odes): |                                       |                 |               |  |  |  |

|                    | 1 = OFx_ma<br>0 = OFx_ma<br><u>If MODE&lt;1:(</u><br>bit is ignored<br><b>Unimplemen</b><br><b>OFS&lt;1:0&gt;:</b> (<br>11 = OF4_r | atch occurs on co<br>atch occurs on co<br>D = 00, 01  or<br>d<br><b>nted:</b> Read as '0<br>Offset Trigger Sc<br>natch <sup>(1)</sup>                         | punter match w<br>punter match w<br>10 <u>(all other mo</u> | rhen counter de<br>rhen counter inc<br>odes): |                                       |                 |               |  |  |  |

|                    | 1 = OFx_ma<br>0 = OFx_ma<br><u>If MODE&lt;1:(</u><br>bit is ignored<br><b>Unimpleme</b><br><b>OFS&lt;1:0&gt;:</b> (                | atch occurs on co<br>atch occurs on co<br>D = 00, 01  or<br>f<br><b>nted:</b> Read as '0<br>Offset Trigger Sc<br>natch <sup>(1)</sup><br>natch <sup>(1)</sup> | punter match w<br>punter match w<br>10 <u>(all other mo</u> | rhen counter de<br>rhen counter inc<br>odes): |                                       |                 |               |  |  |  |

### REGISTER 23-6: PWMxOFCON: PWM OFFSET TRIGGER SOURCE SELECT REGISTER

Note 1: The OF\_match corresponding to the PWM used becomes reserved.

### 24.12 Register Definitions: CWG Control

|                                                                                                                                                                                                                                                   |            |                   |         |                | -                |                  |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|---------|----------------|------------------|------------------|-------------|

| R/W-0/0                                                                                                                                                                                                                                           | U-0        | U-0               | R/W-0/0 | R/W-0/0        | U-0              | U-0              | R/W-0/0     |

| GxEN                                                                                                                                                                                                                                              |            |                   | GxPOLB  | GxPOLA         | —                |                  | GxCS0       |

| bit 7                                                                                                                                                                                                                                             |            |                   |         |                |                  |                  | bit 0       |

|                                                                                                                                                                                                                                                   |            |                   |         |                |                  |                  |             |

| Legend:                                                                                                                                                                                                                                           |            |                   |         |                |                  |                  |             |

| R = Readable                                                                                                                                                                                                                                      | bit        | W = Writable      | bit     | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is unch                                                                                                                                                                                                                                   | anged      | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BOF   | R/Value at all o | ther Resets |

| '1' = Bit is set                                                                                                                                                                                                                                  |            | '0' = Bit is clea | ared    | q = Value der  | pends on conditi | on               |             |

| bit 7 <b>GxEN:</b> CWGx Enable bit<br>1 = Module is enabled<br>0 = Module is disabledbit 6-5 <b>Unimplemented</b> : Read as '0'bit 4 <b>GxPOLB:</b> CWGxB Output Polarity bit<br>1 = Output is inverted polarity<br>0 = Output is normal polarity |            |                   |         |                |                  |                  |             |

| bit 3 <b>GxPOLA:</b> CWGxA Output Polarity bit<br>1 = Output is inverted polarity<br>0 = Output is normal polarity                                                                                                                                |            |                   |         |                |                  |                  |             |

| bit 2-1                                                                                                                                                                                                                                           | Unimplemen | ted: Read as 'o   | )'      |                |                  |                  |             |

| bit 2-1 Unimplemented: Read as '0'<br>bit 0 GxCS0: CWGx Clock Source Select bit<br>1 = HFINTOSC<br>0 = Fosc                                                                                                                                       |            |                   |         |                |                  |                  |             |

### REGISTER 24-1: CWGxCON0: CWG CONTROL REGISTER 0

| Name     | Bit 7 | Bit 6   | Bit 5  | Bit 4   | Bit 3    | Bit 2       | Bit 1     | Bit 0  | Register<br>on Page |

|----------|-------|---------|--------|---------|----------|-------------|-----------|--------|---------------------|

| ANSELA   | _     | _       | _      | ANSA4   | —        | ANSA2       | ANSA1     | ANSA0  | 121                 |

| CWG1CON0 | G1EN  | —       | —      | G1POLB  | G1POLA   | _           | —         | G1CS0  | 253                 |

| CWG1CON1 | G1ASD | LB<1:0> | G1ASD  | LA<1:0> | —        | G1IS<2:0>   |           |        | 254                 |

| CWG1CON2 | G1ASE | G1ARSEN | _      | _       | G1ASDSC2 | G1ASDSC1    | G1ASDSPPS | —      | 255                 |

| CWG1DBF  | _     | _       |        |         | CW       | 256         |           |        |                     |

| CWG1DBR  | _     | _       |        |         | CW       | WG1DBR<5:0> |           |        | 256                 |

| TRISA    |       | —       | TRISA5 | TRISA4  | _(1)     | TRISA2      | TRISA1    | TRISA0 | 120                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by CWG. **Note 1:** Unimplemented, read as '1'.

| Mnemonic,<br>Operands |      |                                               | Ì                  | 14-Bit Opcode |        |      |      | Status   |       |

|-----------------------|------|-----------------------------------------------|--------------------|---------------|--------|------|------|----------|-------|

|                       |      | Description                                   | Description Cycles |               | Sb LSb |      |      | Affected | Notes |

|                       |      | CONTROL OPERA                                 | TIONS              |               |        |      |      |          |       |

| BRA                   | k    | Relative Branch                               | 2                  | 11            | 001k   | kkkk | kkkk |          |       |

| BRW                   | _    | Relative Branch with W                        | 2                  | 00            | 0000   | 0000 | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2                  | 10            | 0kkk   | kkkk | kkkk |          |       |

| CALLW                 | -    | Call Subroutine with W                        | 2                  | 00            | 0000   | 0000 | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2                  | 10            | 1kkk   | kkkk | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2                  | 00            | 0000   | 0000 | 1001 |          |       |

| RETLW                 | k    | Return with literal in W                      | 2                  | 11            | 0100   | kkkk | kkkk |          |       |

| RETURN                | _    | Return from Subroutine                        | 2                  | 00            | 0000   | 0000 | 1000 |          |       |

|                       |      | INHERENT OPERA                                | TIONS              | •             |        |      |      |          |       |

| CLRWDT                | _    | Clear Watchdog Timer                          | 1                  | 00            | 0000   | 0110 | 0100 | TO, PD   |       |

| NOP                   | -    | No Operation                                  | 1                  | 00            | 0000   | 0000 | 0000 |          |       |

| OPTION                | -    | Load OPTION_REG register with W               | 1                  | 00            | 0000   | 0110 | 0010 |          |       |

| RESET                 | -    | Software device Reset                         | 1                  | 00            | 0000   | 0000 | 0001 |          |       |

| SLEEP                 | -    | Go into Standby mode                          | 1                  | 00            | 0000   | 0110 | 0011 | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1                  | 00            | 0000   | 0110 | Offf |          |       |

|                       |      | C-COMPILER OPT                                | IMIZED             |               |        |      |      | •        | •     |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1                  | 11            | 0001   | 0nkk | kkkk |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1                  | 00            | 0000   | 0001 | 0nmm | Z        | 2, 3  |

|                       |      | modifier, mm                                  |                    |               |        |      | kkkk |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1                  | 11            | 1111   | 0nkk | lnmm | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1                  | 00            | 0000   | 0001 | kkkk |          | 2, 3  |

|                       |      | modifier, mm                                  |                    |               |        |      |      |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1                  | 11            | 1111   | 1nkk |      |          | 2     |

### TABLE 26-3: ENHANCED MID-RANGE INSTRUCTION SET (CONTINUED)

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

**3:** See Table in the MOVIW and MOVWI instruction descriptions.

## PIC16(L)F1574/5/8/9

| ΜΟνωι            | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                                                    |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                                                                                |

| Operation:       | $\label{eq:W} \begin{split} W &\to INDFn \\ \text{Effective address is determined by} \\ \bullet \ FSR + 1 \ (\text{preincrement}) \\ \bullet \ FSR - 1 \ (\text{predecrement}) \\ \bullet \ FSR + k \ (\text{relative offset}) \\ \text{After the Move, the FSR value will be} \\ \text{either:} \\ \bullet \ FSR + 1 \ (\text{all increments}) \\ \bullet \ FSR - 1 \ (\text{all decrements}) \\ \text{Unchanged} \end{split}$ |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

### Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                      |  |  |  |  |

|------------------|------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] OPTION                                       |  |  |  |  |

| Operands:        | None                                                 |  |  |  |  |

| Operation:       | $(W) \to OPTION\_REG$                                |  |  |  |  |

| Status Affected: | None                                                 |  |  |  |  |

| Description:     | Move data from W register to<br>OPTION_REG register. |  |  |  |  |

| RESET            | Software Reset                                                                 |

|------------------|--------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                  |

| Operands:        | None                                                                           |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.           |

| Status Affected: | None                                                                           |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software. |

### 27.3 DC Characteristics

### TABLE 27-1:SUPPLY VOLTAGE

| PIC16LF       | 1574/5/8/9 | 1                                           | Standard Operating Conditions (unless otherwise stated) |       |                      |        |                                                                                                                                                                             |  |

|---------------|------------|---------------------------------------------|---------------------------------------------------------|-------|----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIC16F1       | 574/5/8/9  |                                             |                                                         |       |                      |        |                                                                                                                                                                             |  |

| Param.<br>No. | Sym.       | Characteristic                              | Min.                                                    | Тур†  | Max.                 | Units  | Conditions                                                                                                                                                                  |  |

| D001          | Vdd        | Supply Voltage                              |                                                         |       |                      |        |                                                                                                                                                                             |  |

|               |            |                                             | VDDMIN<br>1.8<br>2.5                                    | _     | VDDMAX<br>3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≤ 32 MHz <b>(Note 3)</b>                                                                                                                              |  |

| D001          |            |                                             | 2.3<br>2.5                                              | _     | 5.5<br>5.5           | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≤ 32 MHz <b>(Note 3)</b>                                                                                                                              |  |

| D002*         | Vdr        | RAM Data Retention Voltage <sup>(1)</sup>   |                                                         |       |                      |        | ·                                                                                                                                                                           |  |

|               |            |                                             | 1.5                                                     | _     | _                    | V      | Device in Sleep mode                                                                                                                                                        |  |

| D002*         |            |                                             | 1.7                                                     | _     | _                    | V      | Device in Sleep mode                                                                                                                                                        |  |

| D002A*        | VPOR       | Power-on Reset Release Voltage              | 2)                                                      |       |                      |        |                                                                                                                                                                             |  |

|               |            |                                             | —                                                       | 1.6   | —                    | V      |                                                                                                                                                                             |  |

| D002A*        |            |                                             | —                                                       | 1.6   | —                    | V      |                                                                                                                                                                             |  |

| D002B*        | VPORR*     | Power-on Reset Rearm Voltage <sup>(2)</sup> |                                                         |       |                      |        |                                                                                                                                                                             |  |

|               |            |                                             | —                                                       | 0.8   | —                    | V      |                                                                                                                                                                             |  |

| D002B*        |            |                                             | —                                                       | 1.5   | —                    | V      |                                                                                                                                                                             |  |

| D003          | VFVR       | Fixed Voltage Reference Voltage             | —                                                       | 1.024 | _                    | V      | $-40^{\circ}C \leq TA \leq +85^{\circ}C$                                                                                                                                    |  |

| D003A         | VADFVR     | FVR Gain Voltage Accuracy for<br>ADC        | -4<br>-4<br>-5                                          | _     | 4<br>4<br>5          | %      | $ \begin{array}{l} 1x \; VFvR, \; ADFVR = 01, \; VDD \geq 2.5V \\ 2x \; VFvR, \; ADFVR = 10, \; VDD \geq 2.5V \\ 4x \; VFvR, \; ADFVR = 11, \; VDD \geq 4.75V \end{array} $ |  |

| D003B         | VCDAFVR    | FVR Gain Voltage Accuracy for<br>Comparator | -4<br>-4<br>-5                                          | —     | 4<br>4<br>5          | %      | 1x VFVR, CDAFVR = 01, VDD $\geq$ 2.5V<br>2x VFVR, CDAFVR = 10, VDD $\geq$ 2.5V<br>4x VFVR, CDAFVR = 11, VDD $\geq$ 4.75V                                                    |  |

| D004*         | SVDD       | VDD Rise Rate <sup>(2)</sup>                | 0.05                                                    | —     | —                    | V/ms   | Ensures that the Power-on Reset signal is released properly.                                                                                                                |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: See Figure 27-3, POR and POR REARM with Slow Rising VDD.

3: PLL required for 32 MHz operation.

## TABLE 27-4: I/O PORTS

| Param.<br>No. | Sym.                         | Characteristic                       | Min.              | Тур†     | Max.     | Units | Conditions                                                                 |  |  |

|---------------|------------------------------|--------------------------------------|-------------------|----------|----------|-------|----------------------------------------------------------------------------|--|--|

|               | VIL                          | Input Low Voltage                    |                   |          |          |       |                                                                            |  |  |

|               |                              | I/O PORT:                            |                   |          |          |       |                                                                            |  |  |

| D030          |                              | with TTL buffer                      | _                 |          | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |

| D030A         |                              |                                      | _                 |          | 0.15 VDD | V     | $1.8V \le V \text{DD} \le 4.5V$                                            |  |  |

| D031          |                              | with Schmitt Trigger buffer          | _                 |          | 0.2 VDD  | V     | $2.0V \le V\text{DD} \le 5.5V$                                             |  |  |

|               |                              | with I <sup>2</sup> C levels         | _                 | _        | 0.3 Vdd  | V     |                                                                            |  |  |

|               |                              | with SMbus levels                    | _                 | _        | 0.8      | V     | $2.7V \le V\text{DD} \le 5.5V$                                             |  |  |

| D032          |                              | MCLR                                 | _                 |          | 0.2 VDD  | V     |                                                                            |  |  |

|               | VIH                          | Input High Voltage                   |                   |          |          | •     | •                                                                          |  |  |

|               |                              | I/O PORT:                            |                   |          |          |       |                                                                            |  |  |

| D040          |                              | with TTL buffer                      | 2.0               | _        | —        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |

| D040A         |                              |                                      | 0.25 VDD +<br>0.8 | _        | -        | V     | $1.8V \le V\text{DD} \le 4.5V$                                             |  |  |

| D041          |                              | with Schmitt Trigger buffer          | 0.8 Vdd           | _        | —        | V     | $2.0V \le V \text{DD} \le 5.5 V$                                           |  |  |

|               | with I <sup>2</sup> C levels | 0.7 Vdd                              | _                 | —        | V        |       |                                                                            |  |  |

|               |                              | with SMbus levels                    | 2.1               | _        | —        | V     | $2.7V \le V\text{DD} \le 5.5V$                                             |  |  |

| D042          |                              | MCLR                                 | 0.8 Vdd           | _        | —        | V     |                                                                            |  |  |

|               | lı∟                          | Input Leakage Current <sup>(1)</sup> |                   |          |          |       | ·                                                                          |  |  |

| D060          |                              | I/O Ports                            | —                 | ± 5      | ± 125    | nA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 85°C                    |  |  |

|               |                              |                                      | —                 | ± 5      | ± 1000   | nA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance, 125°C                    |  |  |

| D061          |                              | MCLR <sup>(2)</sup>                  | —                 | ± 50     | ± 200    | nA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance, 85°C                     |  |  |

|               | IPUR                         | Weak Pull-up Current                 |                   |          |          |       | ·                                                                          |  |  |

| D070*         |                              |                                      | 25                | 100      | 200      | μA    | VDD = 3.3V, VPIN = VSS                                                     |  |  |

|               |                              |                                      | 25                | 140      | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                     |  |  |

|               | Vol                          | Output Low Voltage                   |                   |          |          |       |                                                                            |  |  |

| D080          |                              | I/O Ports                            | _                 | _        | 0.6      | v     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |

|               | Voн                          | Output High Voltage                  |                   |          |          | 1     | 1                                                                          |  |  |

| D090          |                              | I/O Ports                            | Vdd - 0.7         | _        | _        | v     | Іон = 3.5 mA, VDD = 5V<br>Іон = 3 mA, VDD = 3.3V<br>Іон = 1 mA, VDD = 1.8V |  |  |