Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1574-e-st |

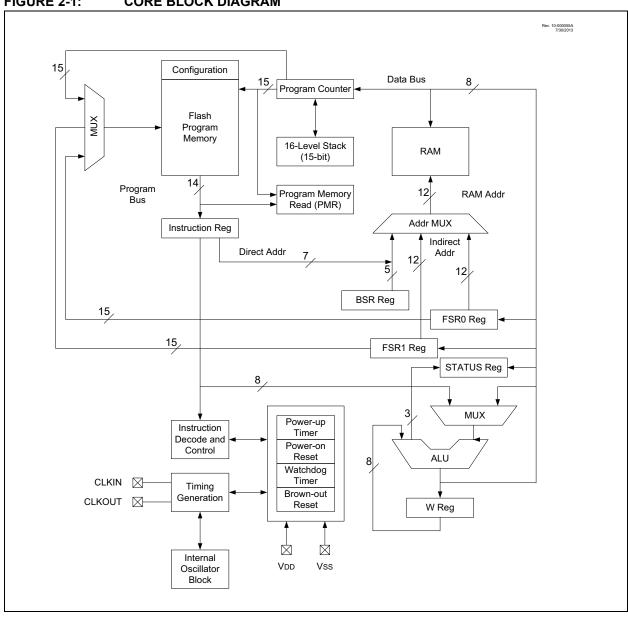

#### 2.0 **ENHANCED MID-RANGE CPU**

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- · File Select Registers

- · Instruction Set

FIGURE 2-1: **CORE BLOCK DIAGRAM**

#### 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See Section 27.0 "Electrical Specifications" for the LFINTOSC tolerances.

#### 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

TABLE 9-1: WDT OPERATING MODES

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       |        | Awake          | Active      |

| 10        |        |                | Disabled    |

| 0.1       | 1      | Х              | Active      |

| 01        |        |                | Disabled    |

| 00        | Х      | Х              | Disabled    |

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 9.4 Clearing the WDT

**Time-Out Period**

The WDT is cleared when any of the following conditions occur:

Any Reset

9.3

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- · Oscillator Start-up Timer (OST) is running

See Table 9-2 for more information.

#### 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See **Section 5.0 "Oscillator Module"** for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register are changed to indicate the event. The  $\overline{\text{RWDT}}$  bit in the PCON register can also be used. See **Section 3.0 "Memory Organization"** for more information.

TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                        | WDT        |

|---------------------------------------------------|------------|

| WDTE<1:0> = 00                                    |            |

| WDTE<1:0> = 01 and SWDTEN = 0                     |            |

| WDTE<1:0> = 10 and enter Sleep                    | Classed    |

| CLRWDT Command                                    | Cleared    |

| Oscillator Fail Detected                          |            |

| Exit Sleep + System Clock = EXTRC, INTOSC, EXTCLK |            |

| Change INTOSC divider (IRCF bits)                 | Unaffected |

#### **EXAMPLE 10-3: WRITING TO FLASH PROGRAM MEMORY**

```

; This write routine assumes the following:

; 1. 64 bytes of data are loaded, starting at the address in DATA_ADDR

; 2. Each word of data to be written is made up of two adjacent bytes in DATA_ADDR,

; stored in little endian format

; 3. A valid starting address (the Least Significant bits = 00000) is loaded in ADDRH: ADDRL

; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

INTCON, GIE

; Disable ints so required sequences will execute properly

BANKSEL

PMADRH

; Bank 3

; Load initial address

MOVF

ADDRH, W

MOVWF

PMADRH

MOVF

ADDRL,W

MOVWF

PMADRL

MOVLW

LOW DATA_ADDR ; Load initial data address

MOVWF

FSR0L

HIGH DATA_ADDR ; Load initial data address

MOVLW

MOVWF

FSR0H

BCF

PMCON1,CFGS

; Not configuration space

BSF

PMCON1, WREN

; Enable writes

; Only Load Write Latches

BSF

PMCON1,LWLO

LOOP

MOVIW

FSR0++

; Load first data byte into lower

MOVWF

PMDATL

MOVIW

FSR0++

; Load second data byte into upper

MOVWF

HTAGMG

MOVF

PMADRL,W

; Check if lower bits of address are '00000'

XORLW

0x1F

; Check if we're on the last of 32 addresses

ANDI-W

0x1F

BTFSC

STATUS.Z

; Exit if last of 32 words,

GOTO

START_WRITE

MOVLW

55h

; Start of required write sequence:

MOVWF

PMCON2

; Write 55h

Required

Sequence

MOVLW

0AAh

MOVWF

PMCON2

; Write AAh

BSF

PMCON1,WR

; Set WR bit to begin write

; NOP instructions are forced as processor

NOP

; loads program memory write latches

NOP

INCF

PMADRL,F

; Still loading latches Increment address

GOTO

LOOP

; Write next latches

START_WRITE

PMCON1,LWLO

; No more loading latches - Actually start Flash program

; memory write

MOVLW

55h

; Start of required write sequence:

MOVWF

PMCON2

; Write 55h

MOVLW

0AAh

MOVWF

PMCON2

; Write AAh

BSF

PMCON1,WR

; Set WR bit to begin write

NOP

; NOP instructions are forced as processor writes

; all the program memory write latches simultaneously

NOP

; to program memory.

; After NOPs, the processor

; stalls until the self-write process in complete

; after write processor continues with 3rd instruction

BCF

PMCON1, WREN

; Disable writes

BSF

INTCON, GIE

; Enable interrupts

```

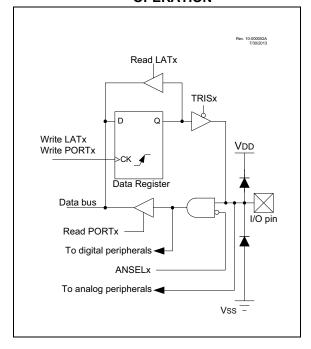

#### 11.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- · TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- · LATx registers (output latch)

- · INLVLx (input level control)

- ODCONx registers (open-drain)

- · SLRCONx registers (slew rate

Some ports may have one or more of the following additional registers. These registers are:

- · ANSELx (analog select)

- · WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

TABLE 11-1: PORT AVAILABILITY PER DEVICE

| Device        | PORTA | PORTB | PORTC |

|---------------|-------|-------|-------|

| PIC16(L)F1574 | •     |       | •     |

| PIC16(L)F1575 | •     |       | •     |

| PIC16(L)F1578 | •     | •     | •     |

| PIC16(L)F1579 | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

FIGURE 11-1: GENERIC I/O PORT OPERATION

#### REGISTER 11-5: WPUA: WEAK PULL-UP PORTA REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **WPUA<5:0>**: Weak Pull-up Register bits<sup>(3)</sup>

1 = Pull-up enabled0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

3: For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

#### REGISTER 11-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| _     | _   | ODA5    | ODA4    | _   | ODA2    | ODA1    | ODA0    |

| bit 7 |     |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 ODA<5:4>: PORTA Open-Drain Enable bits

For RA<5:4> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

bit 3 **Unimplemented:** Read as '0'

bit 2-0 ODA<2:0>: PORTA Open-Drain Enable bits

For RA<2:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 11-20: ANSELC: PORTC ANALOG SELECT REGISTER

| R/W-1/1              | R/W-1/1              | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|-----|-----|---------|---------|---------|---------|

| ANSC7 <sup>(2)</sup> | ANSC6 <sup>(2)</sup> | _   | _   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| bit 7                |                      |     |     |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-6 ANSC<7:6>: Analog Select between Analog or Digital Function on pins RC<7:6>, respectively<sup>(1, 2)</sup>

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

bit 5-4 **Unimplemented:** Read as '0'

bit 3-0 ANSC<3:0>: Analog Select between Analog or Digital Function on pins RC<3:0>, respectively<sup>(1)</sup>

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input (1). Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

2: ANSC<7:6> are available on PIC16(L)F1578/9 only.

#### REGISTER 11-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| WPUC7 <sup>(3)</sup> | WPUC6 <sup>(3)</sup> | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(3)</sup>

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

3: WPUC<7:6> are available on PIC16(L)F1578/9 only.

#### 18.8 Register Definitions: Comparator Control

#### REGISTER 18-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0 | R-0/0 | U-0 | R/W-0/0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|---------|-------|-----|---------|-----|---------|---------|---------|

| CxON    | CxOUT | _   | CxPOL   | _   | CxSP    | CxHYS   | CxSYNC  |

| bit 7   |       |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 CxON: Comparator Enable bit

1 = Comparator is enabled

0 = Comparator is disabled and consumes no active power

bit 6 **CxOUT:** Comparator Output bit

If CxPOL = 1 (inverted polarity):

1 = CxVP < CxVN 0 = CxVP > CxVN

If CxPOL = 0 (non-inverted polarity):

1 = CxVP > CxVN 0 = CxVP < CxVN

bit 5 **Unimplemented:** Read as '0'

bit 4 CxPOL: Comparator Output Polarity Select bit

1 = Comparator output is inverted0 = Comparator output is not inverted

bit 3 **Unimplemented:** Read as '0'

bit 2 CxSP: Comparator Speed/Power Select bit

1 = Comparator mode in normal power, higher speed0 = Comparator mode in low-power, low-speed

bit 1 CxHYS: Comparator Hysteresis Enable bit

1 = Comparator hysteresis enabled0 = Comparator hysteresis disabled

bit 0 CxSYNC: Comparator Output Synchronous Mode bit

1 = Comparator output to Timer1 and I/O pin is synchronous to changes on Timer1 clock source. Output updated on the falling edge of Timer1 clock source.

0 = Comparator output to Timer1 and I/O pin is asynchronous

#### REGISTER 18-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | U-0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|---------|---------|------------|---------|-----|------------|---------|---------|

| CxINTP  | CxINTN  | CxPCH<1:0> |         | _   | CxNCH<2:0> |         |         |

| bit 7   |         |            |         |     |            |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 CXINTP: Comparator Interrupt on Positive Going Edge Enable bits

1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit

0 = No interrupt flag will be set on a positive going edge of the CxOUT bit

bit 6 **CxINTN:** Comparator Interrupt on Negative Going Edge Enable bits

1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit

0 = No interrupt flag will be set on a negative going edge of the CxOUT bit

bit 5-4 **CxPCH<1:0>:** Comparator Positive Input Channel Select bits

11 = CxVP connects to Vss

10 = CxVP connects to FVR Voltage Reference

01 = CxVP connects to DAC Voltage Reference

00 = CxVP connects to CxIN+ pin

bit 3 **Unimplemented:** Read as '0'

bit 2-0 CxNCH<1:0>: Comparator Negative Input Channel Select bits

111 = CxVN connects to GND

110 = CxVN connects to FVR Voltage Reference

101 = Reserved

100 = Reserved

011 = CxVN connects to CxIN3- pin

010 = CxVN connects to CxIN2- pin

001 = CxVN connects to CxIN1- pin

000 = CxVN connects to CxIN0- pin

#### **REGISTER 18-3: CMOUT: COMPARATOR OUTPUT REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| _     | _   | _   | _   | -   | _   | MC2OUT | MC1OUT |

| bit 7 |     |     | •   |     |     |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-2 **Unimplemented:** Read as '0'

bit 1 MC2OUT: Mirror Copy of C2OUT bit bit 0 MC1OUT: Mirror Copy of C1OUT bit

#### 20.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

### 20.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 20.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

# 20.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

#### 20.5 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 20.5.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 20-3 for timing details.

TABLE 20-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK    | T1GPOL | T1G | Timer1 Operation |

|----------|--------|-----|------------------|

| <b>↑</b> | 0      | 0   | Counts           |

| 1        | 0      | 1   | Holds Count      |

| <b>↑</b> | 1      | 0   | Holds Count      |

| <b>↑</b> | 1      | 1   | Counts           |

# 20.5.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 20-4. Source selection is controlled by the T1GSS<1:0> bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

**TABLE 20-4: TIMER1 GATE SOURCES**

| T1GSS | Timer1 Gate Source                                                 |

|-------|--------------------------------------------------------------------|

| 00    | Timer1 Gate pin (T1G)                                              |

| 01    | Overflow of Timer0 (T0_overflow) (TMR0 increments from FFh to 00h) |

| 10    | Comparator 1 Output (C1OUT_sync) <sup>(1)</sup>                    |

| 11    | Comparator 2 Output (C2OUT_sync) <sup>(1)</sup>                    |

Note 1: Optionally synchronized comparator output.

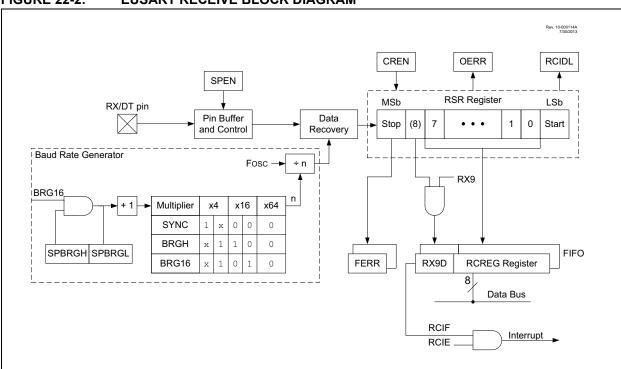

#### FIGURE 22-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- · Transmit Status and Control (TXSTA)

- · Receive Status and Control (RCSTA)

- · Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

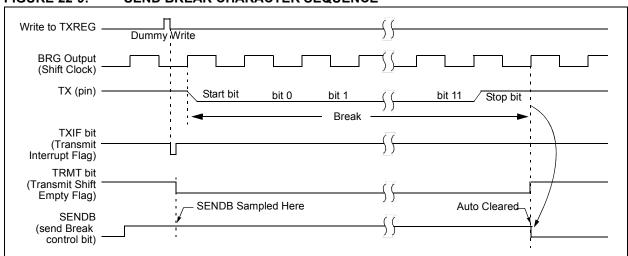

#### 22.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 22-9 for the timing of the Break character sequence.

#### 22.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- Set the TXEN and SENDB bits to enable the Break sequence.

- Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 22.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- · RCIF bit is set

- · FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 22.4.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

#### REGISTER 23-5: PWMxLDCON: PWM RELOAD TRIGGER SOURCE SELECT REGISTER

| R/W-0/0            | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|--------------------|---------|-----|-----|-----|-----|---------|---------|

| LDA <sup>(1)</sup> | LDT     | _   | _   | _   | _   | LDS<    | <1:0>   |

| bit 7              |         |     |     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 LDA: Load Buffer Armed bit<sup>(1)</sup>

<u>If LDT = 1</u>:

1 = Load the OFx, PHx, DCx and PRx buffers at the end of the period when the selected trigger occurs.

0 = Do not load buffers/load has completed

If LDT = 0:

1 = Load OF, PH, DC and PR buffers at the end of the current period

0 = Do not load buffers or load has completed

bit 6 LDT: Load Buffer on Trigger bit

1 = Load buffers on trigger enabled

0 = Load on trigger disabled

Load the OFx, PHx, DCx and PRx buffers at the end of every period after the selected trigger occurs.

Reload internal double buffers at the end of current period. PWMxLDS bits are ignored.

bit 5-2 **Unimplemented:** Read as '0'

bit 1-0 LDS<1:0>: Load Trigger Source Select bits

11 = LD4\_trigger<sup>(2)</sup>

10 = LD3 trigger<sup>(2)</sup>

01 = LD2\_trigger<sup>(2)</sup>

$00 = LD1 \text{ trigger}^{(2)}$

**Note 1:** This bit is cleared by the module after a reload operation. It can be cleared in software to clear an existing arming event.

2: The LD trigger corresponding to the PWM used becomes reserved.

### 26.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDFSR FSRn, k                                                                                    |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                                     |

| Operation:       | $FSR(n) + k \to FSR(n)$                                                                                   |

| Status Affected: | None                                                                                                      |

| Description:     | The signed 6-bit literal 'k' is added to the contents of the FSRnH:FSRnL register pair.                   |

|                  | FSRn is limited to the range 0000h - FFFFh. Moving beyond these bounds will cause the FSR to wrap-around. |

| AND literal with W                                                                                        |

|-----------------------------------------------------------------------------------------------------------|

| [ label ] ANDLW k                                                                                         |

| $0 \leq k \leq 255$                                                                                       |

| (W) .AND. $(k) \rightarrow (W)$                                                                           |

| Z                                                                                                         |

| The contents of W register are AND'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| result is placed in the W register.                                                                       |

|                                                                                                           |

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                     |

| Status Affected: | C, DC, Z                                                                                                      |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                     |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                              |

| Status Affected: | Z                                                                                                                                                      |

| Description:     | AND the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                     |

| Operation:       | $(W) + (f) \rightarrow (destination)$                                                                                                                                  |

| Status Affected: | C, DC, Z                                                                                                                                                               |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                               |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ASRF f {,d}                                                                                                                                                                                                |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                   |

| Operation:       | $(f<7>)\rightarrow dest<7>$<br>$(f<7:1>)\rightarrow dest<6:0>,$<br>$(f<0>)\rightarrow C,$                                                                                                                            |

| Status Affected: | C, Z                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are shifted one bit to the right through the Carry flag. The MSb remains unchanged. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |

|                  | ▶ register f                                                                                                                                                                                                         |

| ADDWFC           | ADD W and CARRY bit to f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                        |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                             |

| Status Affected: | C, DC, Z                                                                                                                                                       |

| Description:     | Add W, the Carry flag and data memory location 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed in data memory location 'f'. |

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVWI ++FSRn<br>[ label ] MOVWIFSRn<br>[ label ] MOVWI FSRn++<br>[ label ] MOVWI FSRn<br>[ label ] MOVWI k[FSRn]                                                                                                                                                                                                 |

| Operands:        | $n \in [0,1]$<br>$mm \in [00,01, 10, 11]$<br>$-32 \le k \le 31$                                                                                                                                                                                                                                                            |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR - 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR - 1 (all decrements)</li> <li>Unchanged</li> </ul> |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h - FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation                                                             |

|------------------|--------------------------------------------------------------------------|

| Syntax:          | [ label ] NOP                                                            |

| Operands:        | None                                                                     |

| Operation:       | No operation                                                             |

| Status Affected: | None                                                                     |

| Description:     | No operation.                                                            |

| Words:           | 1                                                                        |

| Cycles:          | 1                                                                        |

| Example:         | NOP                                                                      |

|                  |                                                                          |

| OPTION           | Load OPTION_REG Register with W                                          |

| Syntax:          | [label] OPTION                                                           |

| Operands:        | None                                                                     |

| Operation:       | $(W) \rightarrow OPTION\_REG$                                            |

| Status Affected: | None                                                                     |

| Description:     | Move data from W register to OPTION_REG register.                        |

|                  |                                                                          |

| RESET            | Software Reset                                                           |

| Syntax:          | [label] RESET                                                            |

| Operands:        | None                                                                     |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.     |

| Status Affected: | None                                                                     |

| Description:     | This instruction provides a way to execute a hardware Reset by software. |

TABLE 27-5: MEMORY PROGRAMMING SPECIFICATIONS

**Standard Operating Conditions (unless otherwise stated)**

| Param.<br>No. | Sym.   | Characteristic                            | Min.   | Typ† | Max.   | Units | Conditions                                                           |

|---------------|--------|-------------------------------------------|--------|------|--------|-------|----------------------------------------------------------------------|

|               |        | Program Memory Programming Specifications |        |      |        |       |                                                                      |

| D110          | VIHH   | Voltage on MCLR/VPP pin                   | 8.0    | _    | 9.0    | V     | (Note 2)                                                             |

| D111          | IDDP   | Supply Current during<br>Programming      | _      | _    | 10     | mA    |                                                                      |

| D112          | VBE    | VDD for Bulk Erase                        | 2.7    |      | VDDMAX | V     |                                                                      |

| D113          | VPEW   | VDD for Write or Row Erase                | VDDMIN |      | VDDMAX | V     |                                                                      |

| D114          | IPPPGM | Current on MCLR/VPP during Erase/Write    | _      | 1.0  | _      | mA    |                                                                      |

| D115          | IDDPGM | Current on VDD during Erase/Write         | _      | 5.0  | _      | mA    |                                                                      |

|               |        | Program Flash Memory                      |        |      |        |       |                                                                      |

| D121          | ЕР     | Cell Endurance                            | 10K    | _    | _      | E/W   | -40°C ≤ TA ≤ +85°C (Note 1)                                          |

| D122          | VPRW   | VDD for Read/Write                        | VDDMIN | _    | VDDMAX | V     |                                                                      |

| D123          | Tıw    | Self-timed Write Cycle Time               | _      | 2    | 2.5    | ms    |                                                                      |

| D124          | TRETD  | Characteristic Retention                  | -      | 40   | _      | Year  | Provided no other specifications are violated                        |

| D125          | EHEFC  | High-Endurance Flash Cell                 | 100K   | _    | _      | E/W   | $0^{\circ}C \le TA \le +60^{\circ}C$ , lower byte last 128 addresses |

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Self-write and Block Erase.

**<sup>2:</sup>** Required only if single-supply programming is disabled.

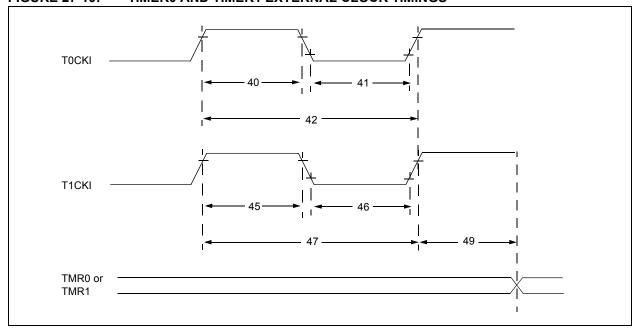

FIGURE 27-10: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 27-12: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |           |                                                      |                              |                |                                           |      |        |       |                     |

|---------------------------------------------------------|-----------|------------------------------------------------------|------------------------------|----------------|-------------------------------------------|------|--------|-------|---------------------|

| Param.<br>No.                                           | Sym.      |                                                      | Characteristic               |                | Min.                                      | Тур† | Max.   | Units | Conditions          |

| 40*                                                     | Тт0Н      | T0CKI High Pulse Width  No Prescaler  With Prescaler |                              | No Prescaler   | 0.5 Tcy + 20                              | _    | _      | ns    |                     |

|                                                         |           |                                                      |                              | 10             | _                                         | _    | ns     |       |                     |

| 41*                                                     | TT0L      | T0CKI Low Pulse Width  No Prescaler  With Prescaler  |                              | No Prescaler   | 0.5 Tcy + 20                              | _    | _      | ns    |                     |

|                                                         |           |                                                      |                              | 10             | _                                         | _    | ns     |       |                     |

| 42*                                                     | Тт0Р      | T0CKI Period                                         | d                            |                | Greater of:<br>20 or <u>TCY + 40</u><br>N | _    | _      | ns    | N = prescale value  |

| 45*                                                     | Тт1Н      | T1CKI High<br>Time                                   | Synchronous, N               | No Prescaler   | 0.5 Tcy + 20                              | _    | _      | ns    |                     |

|                                                         |           |                                                      | Synchronous, v               | vith Prescaler | 15                                        | _    | _      | ns    |                     |

|                                                         |           |                                                      | Asynchronous                 |                | 30                                        | _    | _      | ns    |                     |

| 46*                                                     | TT1L      | T1CKI Low<br>Time                                    | Synchronous, N               | No Prescaler   | 0.5 Tcy + 20                              | _    | _      | ns    |                     |

|                                                         |           |                                                      | Synchronous, v               | vith Prescaler | 15                                        | _    | _      | ns    |                     |

|                                                         |           |                                                      | Asynchronous                 |                | 30                                        | _    | _      | ns    |                     |

| 47*                                                     | Тт1Р      | T1CKI Input<br>Period                                | Synchronous                  |                | Greater of:<br>30 or TCY + 40<br>N        | _    | _      | ns    | N = prescale value  |

|                                                         |           |                                                      | Asynchronous                 |                | 60                                        | _    | _      | ns    |                     |

| 49*                                                     | TCKEZTMR1 | Delay from E<br>Increment                            | external Clock Edge to Timer |                | 2 Tosc                                    | _    | 7 Tosc | _     | Timers in Sync mode |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

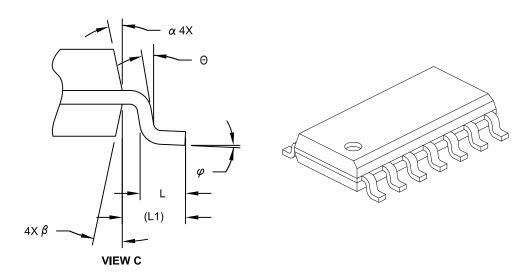

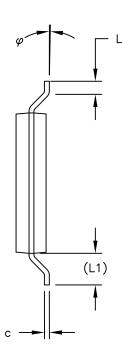

#### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |     |      |  |  |

|--------------------------|-------------|----------|-----|------|--|--|

| Dimension Lir            | MIN         | NOM      | MAX |      |  |  |

| Number of Pins           | N           | 14       |     |      |  |  |

| Pitch                    | е           | 1.27 BSC |     |      |  |  |

| Overall Height           | Α           | 1.79     |     |      |  |  |

| Molded Package Thickness | A2          | 1.25     | -   | -    |  |  |

| Standoff §               | A1          | 0.10     | -   | 0.25 |  |  |

| Overall Width            | Е           | 6.00 BSC |     |      |  |  |

| Molded Package Width     | E1          | 3.90 BSC |     |      |  |  |

| Overall Length           | D           | 8.65 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25     | -   | 0.50 |  |  |

| Foot Length              | L           | 0.40     | -   | 1.27 |  |  |

| Footprint                | L1          | 1.04 REF |     |      |  |  |

| Lead Angle               | Θ           | 0°       | -   | -    |  |  |

| Foot Angle               | $\varphi$   | 0°       | -   | 8°   |  |  |

| Lead Thickness           | С           | 0.10     | -   | 0.25 |  |  |

| Lead Width               | b           | 0.31     | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5° - 15° |     |      |  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -   | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

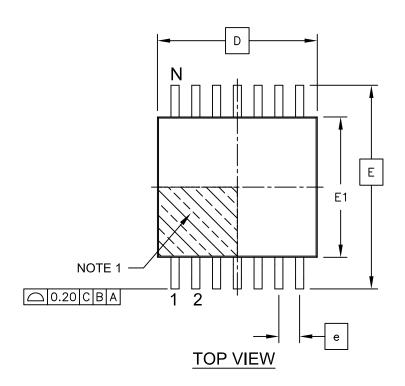

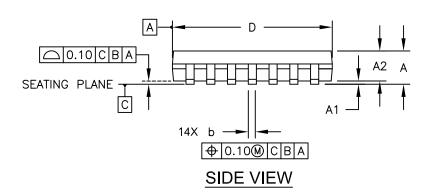

### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2

### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614

Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071

Fax: 630-285-0075

Cleveland Independence, OH

Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423

Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323

Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY

Tel: 631-435-6000

San Jose, CA

Tel: 408-735-9110

Canada - Toronto

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongging

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan

Tel: 86-769-8702-9880

China - Hangzhou

Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533

Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829

Fax: 86-24-2334-2393

1 UX. 00 Z+ 200+ 200

China - Shenzhen

Tel: 86-755-8864-2200

Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

V---- D-----

**Korea - Daegu** Tel: 82-53-744-4301

Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200

Fax: 82-2-558-5932 or

82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857

Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870

Fax: 60-4-227-4068

1 ax. 00-4-221-4000

Philippines - Manila

Tel: 63-2-634-9065

Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870

Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366

Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Taiwan - Taipei

Tel: 886-2-2508-8600

Fax: 886-2-2508-8600

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf

Tel: 49-2129-3766400

Germany - Karlsruhe

Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611

Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399

Fax: 31-416-690340

Poland - Warsaw

Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90

Fax: 34-91-708-08-91 Sweden - Stockholm

Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15