## Microchip Technology - PIC16LF1574-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

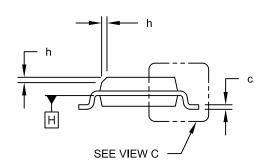

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1574-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name       | Bit 7     | Bit 6    | Bit 5   | Bit 4 | Bit 3     | Bit 2     | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------|-----------|----------|---------|-------|-----------|-----------|-----------|-----------|----------------------|---------------------------------|

| Bank 27 | •          | •         |          | •       | •     |           |           |           |           |                      |                                 |

| D8Ch    | _          | Unimpleme | nted     |         |       |           |           |           |           | _                    | —                               |

| D8Dh    | _          | Unimpleme | nted     |         |       |           |           |           |           | _                    | —                               |

| D8Eh    | PWMEN      | _         | —        | _       | _     | PWM4EN_A  | PWM3EN_A  | PWM2EN_A  | PWM1EN_A  | 0000                 | 0000                            |

| D8Fh    | PWMLD      | _         | _        | _       | _     | PWM4LDA_A | PWM3LDA_A | PWM2LDA_A | PWM1LDA_A | 0000                 | 000                             |

| D90h    | PWMOUT     | _         | _        | _       | _     | PWM4OUT_A | PWM3OUT_A | PWM2OUT_A | PWM10UT_A | 0000                 | 0000                            |

| D91h    | PWM1PHL    |           |          |         |       | PH<7:0>   |           |           |           | xxxx xxxx            | นนนน นนนเ                       |

| D92h    | PWM1PHH    |           | PH<15:8> |         |       |           |           |           |           |                      | นนนน นนนเ                       |

| D93h    | PWM1DCL    |           |          |         |       | DC<7:0>   |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| D94h    | PWM1DCH    |           |          |         |       | DC<15:8>  |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| D95h    | PWM1PRL    |           |          |         |       | PR<7:0>   |           |           |           | xxxx xxxx            | นนนน นนนเ                       |

| D96h    | PWM1PRH    |           |          |         |       | PR<15:8>  |           |           |           | xxxx xxxx            | นนนน นนนเ                       |

| D97h    | PWM10FL    |           |          |         |       | OF<7:0>   |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| D98h    | PWM10FH    |           |          |         |       | OF<15:8>  |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| D99h    | PWM1TMRL   |           |          |         |       | TMR<7:0>  |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| D9Ah    | PWM1TMRH   |           |          |         |       | TMR<15:8> |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| D9Bh    | PWM1CON    | EN        | —        | OUT     | POL   | MODI      | E<1:0>    |           | _         | 0-00 00              | 0-00 00                         |

| D9Ch    | PWM1INTE   | —         | —        | —       | —     | OFIE      | PHIE      | DCIE      | PRIE      | 000                  | 000                             |

| D9Dh    | PWM1INTF   | —         | —        | —       | —     | OFIF      | PHIF      | DCIF      | PRIF      | 000                  | 000                             |

| D9Eh    | PWM1CLKCON | —         |          | PS<2:0> |       | —         | —         | CS<       | <1:0>     | -000 -000            | -00000                          |

| D9Fh    | PWM1LDCON  | LDA       | LDT      | —       | —     | —         | —         | LDS       | <1:0>     | 00000                | 0000                            |

| DA0h    | PWM10FCON  | —         | OFM      | <1:0>   | OFO   | —         | —         | OFS       | <1:0>     | -000 -000            | -00000                          |

| DA1h    | PWM2PHL    |           |          |         |       | PH<7:0>   |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA2h    | PWM2PHH    |           |          |         |       | PH<15:8>  |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA3h    | PWM2DCL    |           |          |         |       | DC<7:0>   |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA4h    | PWM2DCH    |           |          |         |       | DC<15:8>  |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA5h    | PWM2PRL    |           |          |         |       | PR<7:0>   |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| DA6h    | PWM2PRH    |           |          |         |       | PR<15:8>  |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA7h    | PWM2OFL    |           |          |         |       | OF<7:0>   |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| DA8h    | PWM2OFH    |           |          |         |       | OF<15:8>  |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| DA9h    | PWM2TMRL   |           |          |         |       | TMR<7:0>  |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| DAAh    | PWM2TMRH   |           |          |         |       | TMR<15:8> |           |           |           | xxxx xxxx            | uuuu uuuu                       |

#### TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3:

Unimplemented, read as '1'.

## TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address  | Name            | Bit 7                                      | Bit 6                           | Bit 5        | Bit 4           | Bit 3   | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------|-----------------|--------------------------------------------|---------------------------------|--------------|-----------------|---------|--------|-----------|-----------|----------------------|---------------------------------|

| Bank 31  |                 |                                            |                                 |              |                 |         |        |           |           |                      |                                 |

| F8Ch     | —               | Unimpleme                                  | nted                            |              |                 |         |        |           |           | -                    | —                               |

| <br>FE3h |                 |                                            |                                 |              |                 |         |        |           |           |                      |                                 |

| FE4h     | STATUS_<br>SHAD | —                                          | —                               | —            | _               | _       | Z_SHAD | DC_SHAD   | C_SHAD    | xxx                  | uuu                             |

| FE5h     | WREG_<br>SHAD   | Working Re                                 | Working Register Shadow         |              |                 |         |        |           |           |                      | uuuu uuuu                       |

| FE6h     | BSR_<br>SHAD    | —                                          | — — Bank Select Register Shadow |              |                 |         |        |           | x xxxx    | u uuuu               |                                 |

| FE7h     | PCLATH_<br>SHAD | Program Counter Latch High Register Shadow |                                 |              |                 |         |        | -xxx xxxx | uuuu uuuu |                      |                                 |

| FE8h     | FSR0L_<br>SHAD  | Indirect Data                              | a Memory Ad                     | dress 0 Low  | Pointer Shadov  | N       |        |           |           | XXXX XXXX            | uuuu uuuu                       |

| FE9h     | FSR0H_<br>SHAD  | Indirect Date                              | a Memory Ad                     | dress 0 High | n Pointer Shado | W       |        |           |           | XXXX XXXX            | uuuu uuuu                       |

| FEAh     | FSR1L_<br>SHAD  | Indirect Data                              | a Memory Ad                     | dress 1 Low  | Pointer Shadov  | N       |        |           |           | XXXX XXXX            | uuuu uuuu                       |

| FEBh     | FSR1H_<br>SHAD  | Indirect Data                              | a Memory Ad                     | dress 1 High | n Pointer Shado | W       |        |           |           | XXXX XXXX            | uuuu uuuu                       |

| FECh     | —               | Unimpleme                                  | nted                            |              |                 |         |        |           |           | -                    | —                               |

| FEDh     | STKPTR          | —                                          | —                               | —            | Current Stack   | Pointer |        |           |           | 1 1111               | 1 1111                          |

| FEEh     | TOSL            | Top-of-Stack                               | k Low byte                      |              |                 |         |        |           |           | xxxx xxxx            | uuuu uuuu                       |

| FEFh     | TOSH            | _                                          | Top-of-Stack                    | High byte    |                 |         |        |           |           | -xxx xxxx            | -uuu uuuu                       |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.Note 1: PIC16(L)F1578/9 only.

2: PIC16F1574/5/8/9 only.

**3:** Unimplemented, read as '1'.

## 5.5 Register Definitions: Oscillator Control

| R/W-0/0          | R/W-0/0                                                                                                       | R/W-1/1                                                                                                                                                                                                         | R/W-1/1                            | R/W-1/1                                               | U-0                | R/W-0/0      | R/W-0/0 |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------|--------------------|--------------|---------|--|--|

| SPLLEN           |                                                                                                               | IRCF                                                                                                                                                                                                            | <3:0>                              |                                                       | _                  | SCS          | <1:0>   |  |  |

| bit 7            |                                                                                                               |                                                                                                                                                                                                                 |                                    |                                                       |                    |              | bit 0   |  |  |

|                  |                                                                                                               |                                                                                                                                                                                                                 |                                    |                                                       |                    |              |         |  |  |

| Legend:          |                                                                                                               |                                                                                                                                                                                                                 | .,                                 |                                                       |                    |              |         |  |  |

| R = Readable     |                                                                                                               | W = Writable I                                                                                                                                                                                                  |                                    | •                                                     | nented bit, rea    |              |         |  |  |

| u = Bit is uncha | anged                                                                                                         | x = Bit is unkn                                                                                                                                                                                                 |                                    | -n/n = Value at POR and BOR/Value at all other Resets |                    |              |         |  |  |

| '1' = Bit is set |                                                                                                               | '0' = Bit is clea                                                                                                                                                                                               | ared                               |                                                       |                    |              |         |  |  |

| bit 7            | If PLLEN in C<br>SPLLEN bit i                                                                                 |                                                                                                                                                                                                                 | ords = <u>1:</u><br>_L is always e | nabled (subject                                       | t to oscillator re | equirements) |         |  |  |

| bit 6-3          | 1111 = 16 M<br>1110 = 8 M<br>1101 = 4 M<br>1100 = 2 M<br>1011 = 1 M<br>1010 = 500<br>1001 = 250<br>1000 = 125 | Hz or 32 MHz H<br>Hz HF<br>Hz HF<br>kHz HF <sup>(1)</sup><br>kHz HF <sup>(1)</sup><br>kHz HF <sup>(1)</sup><br>kHz MF (defau<br>kHz MF<br>kHz MF<br>kHz MF<br>5 kHz MF<br>25 kHz HF <sup>(1)</sup><br>25 kHz MF | IF (see <b>Secti</b> e             | on 5.2.2.1 "HFI                                       | NTOSC")            |              |         |  |  |

| bit 2            | Unimplemer                                                                                                    | nted: Read as '                                                                                                                                                                                                 | )'                                 |                                                       |                    |              |         |  |  |

| bit 1-0          | 1x = Internal<br>01 = Reserve                                                                                 | System Clock Se<br>oscillator block<br>ed<br>etermined by Fe                                                                                                                                                    |                                    | Configuration W                                       | Vords.             |              |         |  |  |

| Note 1: Dup      | licate frequen                                                                                                | cv derived from                                                                                                                                                                                                 | HFINTOSC.                          |                                                       |                    |              |         |  |  |

### REGISTER 5-1: OSCCON: OSCILLATOR CONTROL REGISTER

## PIC16(L)F1574/5/8/9

| TABLE 9-3: | SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER |

|------------|-----------------------------------------------------|

| Name   | Bit 7  | Bit 6  | Bit 5        | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | Register<br>on Page |

|--------|--------|--------|--------------|-------|-------|-------|----------|-------|---------------------|

| OSCCON | SPLLEN |        | IRCF<3:0>    |       |       |       | SCS<1:0> |       | 69                  |

| PCON   | STKOVF | STKUNF | —            | RWDT  | RMCLR | RI    | POR      | BOR   | 79                  |

| STATUS | —      | _      | _            | TO    | PD    | Z     | DC       | С     | 23                  |

| WDTCON | _      | _      | — WDTPS<4:0> |       |       |       |          |       | 99                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|

|         | 13:8 | _       | —       |          | —        | CLKOUTEN | BOREN<1:0> |         | —       | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   |            | FOSC    | <1:0>   | 56                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

## 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection  $(\overline{CP} = 0)^{(1)}$ , disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash program memory array is enabled by clearing the CP bit of Configuration Words.

## **10.1 PMADRL and PMADRH Registers**

The PMADRH:PMADRL register pair can address up to a maximum of 16K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

## 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

| Note: | If the user wants to modify only a portion<br>of a previously programmed row, then the<br>contents of the entire row must be read<br>and saved in RAM prior to the erase.<br>Then, new data and retained data can be       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | written into the write latches to reprogram<br>the row of Flash program memory. How-<br>ever, any unprogrammed locations can be<br>written without first erasing the row. In this<br>case, it is not necessary to save and |

|       | rewrite the other previously programmed locations.                                                                                                                                                                         |

#### 11.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information. Analog input functions, such as ADC inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when it is in Analog mode.

| R/W-0/0                                 | R/W-0/                               | 0 R/W-0/0                                                  | R/W-0/0                                             | U-0                          | U-0              | U-0              | U-0          |

|-----------------------------------------|--------------------------------------|------------------------------------------------------------|-----------------------------------------------------|------------------------------|------------------|------------------|--------------|

|                                         | TRIG                                 | SEL<3:0> <sup>(1)</sup>                                    |                                                     |                              | _                |                  |              |

| bit 7                                   |                                      |                                                            |                                                     |                              |                  |                  | bit 0        |

|                                         |                                      |                                                            |                                                     |                              |                  |                  |              |

| Legend:                                 |                                      |                                                            |                                                     |                              |                  |                  |              |

| R = Readable                            | e bit                                | W = Writable                                               | bit                                                 | U = Unimpler                 | nented bit, read | l as '0'         |              |

| u = Bit is unchanged x = Bit is unknown |                                      |                                                            |                                                     | -n/n = Value a               | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set '0' = Bit is cleared   |                                      |                                                            |                                                     |                              |                  |                  |              |

|                                         |                                      |                                                            |                                                     |                              |                  |                  |              |

| bit 7-4                                 | TRIGSEL                              | .<3:0>: Auto-Conve                                         | ersion Trigger                                      | Selection bits <sup>(1</sup> | )                |                  |              |

|                                         | 0000 =                               | No auto-conversio                                          | n trigger seled                                     | ted                          |                  |                  |              |

|                                         | 0001 =                               | PWM1 – PWM1_ir                                             | nterrupt                                            |                              |                  |                  |              |

|                                         |                                      | PWM2 – PWM2_ir                                             |                                                     |                              |                  |                  |              |

|                                         |                                      |                                                            |                                                     |                              |                  |                  |              |

|                                         | 0011 =                               | Timer0 – T0_overf                                          | low <sup>(2)</sup>                                  |                              |                  |                  |              |

|                                         |                                      | Timer0 – T0_overf<br>Timer1 – T1_overf                     |                                                     |                              |                  |                  |              |

|                                         | 0100 =                               |                                                            | low <sup>(2)</sup>                                  |                              |                  |                  |              |

|                                         | 0100 =<br>0101 =                     | Timer1 – T1_overf                                          | low <sup>(2)</sup><br>h                             |                              |                  |                  |              |

|                                         | 0100 =<br>0101 =<br>0110 =           | Timer1 – T1_overf<br>Timer2 – T2_matc                      | low <sup>(2)</sup><br>h<br>C1OUT_sync               |                              |                  |                  |              |

|                                         | 0100 =<br>0101 =<br>0110 =<br>0111 = | Timer1 – T1_overf<br>Timer2 – T2_matc<br>Comparator C1 – ( | low <sup>(2)</sup><br>h<br>C1OUT_sync<br>C2OUT_sync |                              |                  |                  |              |

#### REGISTER 16-3: ADCON2: ADC CONTROL REGISTER 2

1010 = PWM3 – PWM3\_OF\_match 1011 = PWM3 – PWM3\_interrupt 1100 = PWM4 – PWM4\_OF\_match 1101 = PWM4 – PWM4\_interrupt

1111 = CWG input pin

Unimplemented: Read as '0' Note 1: This is a rising edge sensitive input for all sources. 2: Signal also sets its corresponding interrupt flag.

1110 = ADC Auto-Conversion Trigger input pin

bit 3-0

| DS40001782C-page | 160 |

|------------------|-----|

|------------------|-----|

| R/W-0/0          | R/W-0/0                                                                                        | R/W-0/0                                                                                                                                                                                                                                      | R/W-0/0                                                               | U-0             | R/W-0/0          | R/W-0/0    | R/W-0/0      |  |  |

|------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------|------------------|------------|--------------|--|--|

| CxINTP           | CxINTN                                                                                         | CxPCI                                                                                                                                                                                                                                        | H<1:0>                                                                |                 |                  | CxNCH<2:0> |              |  |  |

| bit 7            |                                                                                                |                                                                                                                                                                                                                                              |                                                                       |                 |                  |            | bit 0        |  |  |

| Legend:          |                                                                                                |                                                                                                                                                                                                                                              |                                                                       |                 |                  |            |              |  |  |

| R = Readable     | e bit                                                                                          | W = Writable                                                                                                                                                                                                                                 | bit                                                                   | U = Unimple     | mented bit, read | d as '0'   |              |  |  |

| u = Bit is unc   | hanged                                                                                         | x = Bit is unkr                                                                                                                                                                                                                              | nown                                                                  |                 | at POR and BC    |            | other Resets |  |  |

| '1' = Bit is set |                                                                                                | '0' = Bit is clea                                                                                                                                                                                                                            | ared                                                                  |                 |                  |            |              |  |  |

|                  |                                                                                                |                                                                                                                                                                                                                                              |                                                                       |                 |                  |            |              |  |  |

| bit 7            | 1 = The CxI                                                                                    | mparator Interru<br>F interrupt flag v<br>rupt flag will be                                                                                                                                                                                  | will be set upo                                                       | n a positive go | ing edge of the  |            |              |  |  |

| bit 6            | 1 = The CxI                                                                                    | <b>CxINTN:</b> Comparator Interrupt on Negative Going Edge Enable bits<br>1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit<br>0 = No interrupt flag will be set on a negative going edge of the CxOUT bit |                                                                       |                 |                  |            |              |  |  |

| bit 5-4          | 11 = CxVP o<br>10 = CxVP o<br>01 = CxVP o                                                      | Comparator I<br>connects to Vss<br>connects to FVF<br>connects to DAC<br>connects to CXII                                                                                                                                                    | R Voltage Refe<br>C Voltage Refe                                      | rence           | t bits           |            |              |  |  |

| bit 3            | Unimpleme                                                                                      | nted: Read as '                                                                                                                                                                                                                              | 0'                                                                    |                 |                  |            |              |  |  |

| bit 2-0          | 111 = CxVN<br>110 = CxVN<br>101 = Rese<br>100 = Rese<br>011 = CxVN<br>010 = CxVN<br>001 = CxVN |                                                                                                                                                                                                                                              | ND<br>/R Voltage Re<br><td></td> <td>ct bits</td> <td></td> <td></td> |                 | ct bits          |            |              |  |  |

## REGISTER 18-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

## REGISTER 18-3: CMOUT: COMPARATOR OUTPUT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| _     | —   | _   | —   | _   | _   | MC2OUT | MC1OUT |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 7-2 Unimplemented: Read as '0'

- bit 1 MC2OUT: Mirror Copy of C2OUT bit

- bit 0 MC10UT: Mirror Copy of C10UT bit

## 19.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 3-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

TMR0CS

TMR0 can be used to gate Timer1

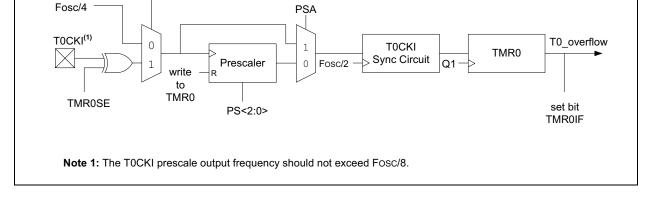

Figure 19-1 is a block diagram of the Timer0 module.

## 19.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 19.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### FIGURE 19-1: TIMER0 BLOCK DIAGRAM

#### 19.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

Rev. 10-000017A 8/5/2013

### 20.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 20.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

## 20.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 20-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

#### 20.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 20-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 20-6 for timing details.

## 20.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 20.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

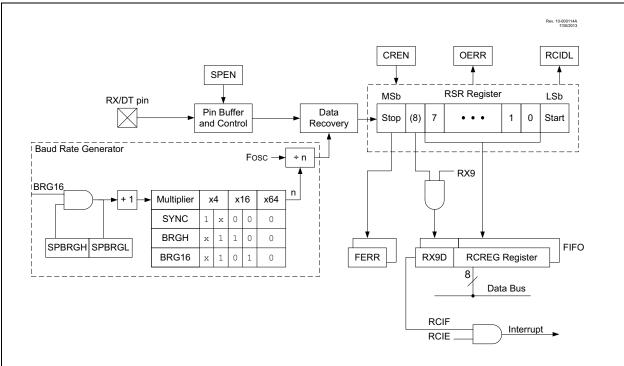

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

### 22.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSEL bit must be        |

|       | cleared for the receiver to function.      |

#### 22.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

Note: If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

#### 22.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters

will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 22.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

## 22.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

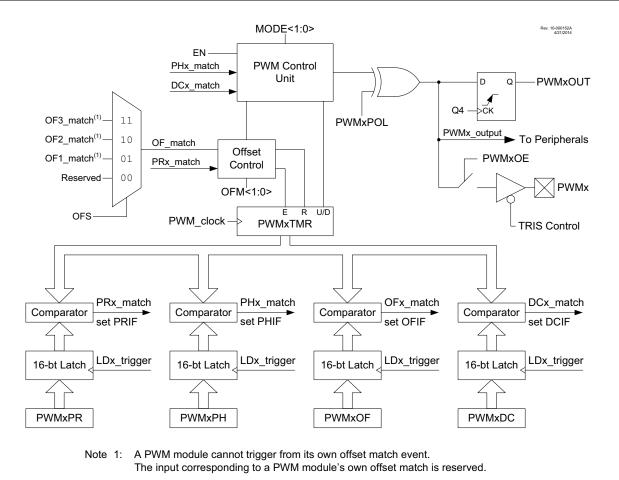

## 23.0 16-BIT PULSE-WIDTH MODULATION (PWM) MODULE

The Pulse-Width Modulation (PWM) module generates a pulse width modulated signal determined by the phase, duty cycle, period, and offset event counts that are contained in the following registers:

- PWMxPH register

- PWMxDC register

- PWMxPR register

- PWMxOF register

Figure 23-1 shows a simplified block diagram of the PWM operation.

Each PWM module has four modes of operation:

- Standard

- · Set On Match

- Toggle On Match

- · Center-Aligned

For a more detailed description of each PWM mode, refer to **Section 23.2** "**PWM Modes**".

Each PWM module has four offset modes:

- Independent Run

- · Slave Run with Synchronous Start

- · One-Shot Slave with Synchronous Start

- Continuous Run Slave with Synchronous Start and Timer Reset

Using the offset modes, each PWM module can offset its waveform relative to any other PWM module in the same device. For a more detailed description of the offset modes refer to **Section 23.3 "Offset Modes"**.

Every PWM module has a configurable reload operation to ensure all event count buffers change at the end of a period thereby avoiding signal glitches. Figure 23-2 shows a simplified block diagram of the reload operation. For a more detailed description of the reload operation, refer to Section **Section 23.4 "Reload Operation"**.

## FIGURE 23-1: 16-BIT PWM BLOCK DIAGRAM

#### REGISTER 23-11: PWMxPRH: PWMx PERIOD COUNT HIGH REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | PR<     | :15:8>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **PR<15:8>**: PWM Period High bits Upper eight bits of PWM period count

## REGISTER 23-12: PWMxPRL: PWMx PERIOD COUNT LOW REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PR<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PR<7:0>**: PWM Period Low bits Lower eight bits of PWM period count

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared       q = Value depends on condition         bit 7-6       GxASDLB<1:0>: CWGx Shutdown State for CWGxB         When an auto shutdown event is present (GxASE = 1):       11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.         10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.       01 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still w control the polarity of the output.         bit 5-4       GxASDLA<1:0>: CWGx Shutdown State for CWGxA         When an auto shutdown event is present (GxASE = 1):       11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.       10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.       10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.         12 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.       10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w control t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x/u          | R/W-x/u      | R/W-x/u                                                                                                 | R/W-x/u       | U-0          | R/W-0/0         | R/W-0/0          | R/W-0/0     |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|---------------------------------------------------------------------------------------------------------|---------------|--------------|-----------------|------------------|-------------|--|--|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared       q = Value depends on condition         bit 7-6       GxASDLB<10>: CWGx Shutdown State for CWGxB         When an auto shutdown event is present (GxASE = 1):       11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.         10 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.       01 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.         01 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLA bit.       01 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         bit 5-4       GxASDLA<1:0>: CWGx Shutdown State for CWGxA         When an auto shutdown event is present (GxASE = 1):       11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.       01 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         11 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w control the polarity of the output.       01 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w control the polarity of the output.         bit 3       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GxASE            | DLB<1:0>     | GxASD                                                                                                   | LA<1:0>       | _            |                 | GxIS<2:0>        |             |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared       q = Value depends on condition         bit 7-6       GxASDLB<1:0>: CWGx Shutdown State for CWGxB         When an auto shutdown event is present (GxASE = 1):       11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.         10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.       01 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.         00 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still w control the polarity of the output.         bit 5-4       GxASDLA<1:0>: CWGx Shutdown State for CWGxA         When an auto shutdown event is present (GxASE = 1):         11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w control the polarity of the output.         bit 3       Unimplemented: Read as '0'         bit 2-0       GxIS<2:0>: CWGx Input So                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7            |              |                                                                                                         |               |              | •               |                  | bit C       |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared       q = Value depends on condition         bit 7-6       GxASDLB<1:0>: CWGx Shutdown State for CWGxB         When an auto shutdown event is present (GxASE = 1):       11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.         10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.       01 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.         00 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still w control the polarity of the output.         bit 5-4       GxASDLA<1:0>: CWGx Shutdown State for CWGxA         When an auto shutdown event is present (GxASE = 1):         11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.         10 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w control the polarity of the output.         bit 3       Unimplemented: Read as '0'         bit 2-0       GxIS<2:0>: CWGx Input So                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |              |                                                                                                         |               |              |                 |                  |             |  |  |

| <ul> <li>bit and the first intervent in the first intervent is the first intervent is the first is unchanged if it is unchanged</li></ul> | Legend:          |              |                                                                                                         |               |              |                 |                  |             |  |  |

| <ul> <li>'1' = Bit is set '0' = Bit is cleared q = Value depends on condition</li> <li>bit 7-6 GxASDLB&lt;1:0&gt;: CWGx Shutdown State for CWGxB<br/>When an auto shutdown event is present (GxASE = 1):<br/>11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.<br/>10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.<br/>11 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.<br/>10 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still w<br/>control the polarity of the output.</li> <li>bit 5-4 GxASDLA&lt;1:0&gt;: CWGx Shutdown State for CWGxA<br/>When an auto shutdown event is present (GxASE = 1):<br/>11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w<br/>control the polarity of the output.</li> <li>bit 3 Unimplemented: Read as '0'<br/>bit 2-0 GxIS&lt;2:0&gt;: CWGx Input Source Select bits<br/>111 = Reserved<br/>110 = CWG input pin<br/>101 = PWM4 – PVM4_out<br/>100 = PWM3 – PVM4_out<br/>100 = PWM3 – PVM4_out<br/>100 = PWM1 – PVM4_out</li> <li>011 = PWM4 – PVM4_out</li> </ul>                                 | R = Readable     | e bit        | W = Writable                                                                                            | bit           | U = Unimpler | mented bit, rea | d as '0'         |             |  |  |

| <ul> <li>bit 7-6 GxASDLB&lt;1:0&gt;: CWGx Shutdown State for CWGxB<br/>When an auto shutdown event is present (GxASE = 1):<br/>11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.<br/>10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.<br/>01 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still w<br/>control the polarity of the output.</li> <li>bit 5-4 GxASDLA&lt;1:0&gt;: CWGx Shutdown State for CWGxA<br/>When an auto shutdown event is present (GxASE = 1):<br/>11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.<br/>11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.<br/>11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.<br/>11 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w<br/>control the polarity of the output.</li> <li>bit 3 Unimplemented: Read as '0'</li> <li>bit 2-0 GxIS&lt;2:0&gt;: CWGx Input Source Select bits<br/>111 = Reserved<br/>110 = CWGi nput pin<br/>101 = PWM4 – PWM4_out<br/>100 = PWM3 – PWM4_out<br/>100 = PWM3 – PWM4_out<br/>100 = PWM1 – PWM4_out</li> <li>101 = PWM2 – PWM4_out</li> <li>101 = PWM2 – PWM4_out</li> <li>101 = PWM2 – PWM4_out</li> <li>101 = PWM1 – PWM4_out</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            | u = Bit is unc   | hanged       | x = Bit is unki                                                                                         | nown          | -n/n = Value | at POR and BC   | R/Value at all o | ther Resets |  |  |

| <ul> <li>When an auto shutdown event is present (GxASE = 1):</li> <li>11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.</li> <li>10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.</li> <li>01 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still w control the polarity of the output.</li> <li>bit 5-4</li> <li><b>GxASDLA&lt;1:0&gt;:</b> CWGx Shutdown State for CWGxA</li> <li>When an auto shutdown event is present (GxASE = 1):</li> <li>11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.</li> <li>10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.</li> <li>10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.</li> <li>01 = CWGxA pin is tri-stated</li> <li>00 = CWGxA pin is tri-stated</li> <li>00 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.</li> <li>01 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w control the polarity of the output.</li> <li>bit 3</li> <li>Unimplemented: Read as '0'</li> <li>bit 2-0</li> <li>GxIS&lt;2:0&gt;: CWGx Input Source Select bits</li> <li>111 = Reserved</li> <li>110 = CWG input pin</li> <li>101 = PWM4 - PWM4_out</li> <li>100 = PWM3 - PWM3_out</li> <li>101 = PWM2 - PWM2_out</li> <li>100 = PWM1 - PWM1_out</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | '1' = Bit is set | I            | '0' = Bit is cle                                                                                        | ared          | q = Value de | pends on condi  | tion             |             |  |  |

| <ul> <li>When an auto shutdown event is present (GxASE = 1):</li> <li>11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.</li> <li>10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.</li> <li>01 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still w control the polarity of the output.</li> <li>bit 5-4</li> <li><b>GxASDLA&lt;1:0&gt;:</b> CWGx Shutdown State for CWGxA</li> <li>When an auto shutdown event is present (GxASE = 1):</li> <li>11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.</li> <li>10 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.</li> <li>10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.</li> <li>01 = CWGxA pin is tri-stated</li> <li>00 = CWGxA pin is tri-stated</li> <li>00 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.</li> <li>01 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w control the polarity of the output.</li> <li>bit 3</li> <li>Unimplemented: Read as '0'</li> <li>bit 2-0</li> <li>GxIS&lt;2:0&gt;: CWGx Input Source Select bits</li> <li>111 = Reserved</li> <li>110 = CWG input pin</li> <li>101 = PWM4 - PWM4_out</li> <li>100 = PWM3 - PWM3_out</li> <li>101 = PWM2 - PWM2_out</li> <li>100 = PWM1 - PWM1_out</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |              |                                                                                                         |               |              |                 |                  |             |  |  |

| <ul> <li>11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.</li> <li>10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.</li> <li>01 = CWGxB pin is tri-stated</li> <li>00 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still w control the polarity of the output.</li> <li>bit 5-4</li> <li><b>GxASDLA&lt;1:0&gt;:</b> CWGx Shutdown State for CWGxA</li> <li>When an auto shutdown event is present (GxASE = 1):</li> <li>11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.</li> <li>10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.</li> <li>10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.</li> <li>01 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.</li> <li>01 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still w control the polarity of the output.</li> <li>bit 3</li> <li>Unimplemented: Read as '0'</li> <li>bit 2-0</li> <li>GxIS</li> <li>GxIS</li> <li>CWGx Input Source Select bits</li> <li>111 = Reserved</li> <li>110 = CWG input pin</li> <li>101 = PWM4 – PWM4_out</li> <li>100 = PWM3 – PWM3_out</li> <li>101 = PWM2 – PWM2_out</li> <li>100 = PWM1 – PWM1_out</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7-6          | GxASDLB<1    | I:0>: CWGx Sh                                                                                           | utdown State  | for CWGxB    |                 |                  |             |  |  |