Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·><Fl

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | LINbus, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1574t-i-sl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

## REGISTER 3-1: STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to **Section 26.0 "Instruction Set Summary"**).

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and <u>Digit</u> Borrow out bits, respectively, in subtraction.

| U-0                                     | U-0 | U-0               | R-1/q                                                 | R-1/q                              | R/W-0/u | R/W-0/u           | R/W-0/u          |  |  |  |

|-----------------------------------------|-----|-------------------|-------------------------------------------------------|------------------------------------|---------|-------------------|------------------|--|--|--|

|                                         | _   | —                 | TO                                                    | PD                                 | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |  |

| bit 7                                   |     |                   |                                                       |                                    |         |                   | bit 0            |  |  |  |

|                                         |     |                   |                                                       |                                    |         |                   |                  |  |  |  |

| Legend:                                 |     |                   |                                                       |                                    |         |                   |                  |  |  |  |

| R = Readable b                          | oit | W = Writable I    | bit                                                   | U = Unimplemented bit, read as '0' |         |                   |                  |  |  |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |                   |                  |  |  |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared                                                  | q = Value depends on condition     |         |                   |                  |  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                               |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                             |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1: | For $\overline{\text{Borrow}}$ the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

# TABLE 3-5: PIC16(L)F1578 MEMORY MAP, BANKS 0-7

|       | BANK0                         |        | ,<br>BANK1                    |      | BANK2                         |      | BANK3                         |       | BANK4                         |        | BANK5                         |                      | BANK6                                      |        | BANK7                         |

|-------|-------------------------------|--------|-------------------------------|------|-------------------------------|------|-------------------------------|-------|-------------------------------|--------|-------------------------------|----------------------|--------------------------------------------|--------|-------------------------------|

| 000h  | Core Registers<br>(Table 3-2) | 080h   | Core Registers<br>(Table 3-2) | 100h | Core Registers<br>(Table 3-2) | 180h | Core Registers<br>(Table 3-2) | 200h  | Core Registers<br>(Table 3-2) | 280h   | Core Registers<br>(Table 3-2) | 300h                 | Core Registers<br>(Table 3-2)              | 380h   | Core Registers<br>(Table 3-2) |

| 00Bh  |                               | 08Bh   |                               | 10Bh |                               | 18Bh |                               | 20Bh  |                               | 28Bh   |                               | 30Bh                 |                                            | 38Bh   |                               |

| 00Ch  | PORTA                         | 08Ch   | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch  | WPUA                          | 28Ch   | ODCONA                        | 30Ch                 | SLRCONA                                    | 38Ch   | INLVLA                        |

| 00Dh  | PORTB                         | 08Dh   | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh  | WPUB                          | 28Dh   | ODCONB                        | 30Dh                 | SLRCONB                                    | 38Dh   | INLVLB                        |

| 00Eh  | PORTC                         | 08Eh   | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh  | WPUC                          | 28Eh   | ODCONC                        | 30Eh                 | SLRCONC                                    | 38Eh   | INLVLC                        |

| 00Fh  | _                             | 08Fh   | -                             | 10Fh | _                             | 18Fh | _                             | 20Fh  | _                             | 28Fh   | _                             | 30Fh                 | _                                          | 38Fh   | —                             |

| 010h  | _                             | 090h   | _                             | 110h | _                             | 190h | _                             | 210h  | _                             | 290h   | _                             | 310h                 | _                                          | 390h   | —                             |

| 011h  | PIR1                          | 091h   | PIE1                          | 111h | CM1CON0                       | 191h | PMADRL                        | 211h  | —                             | 291h   | —                             | 311h                 | —                                          | 391h   | IOCAP                         |

| 012h  | PIR2                          | 092h   | PIE2                          | 112h | CM1CON1                       | 192h | PMADRH                        | 212h  | —                             | 292h   | —                             | 312h                 | —                                          | 392h   | IOCAN                         |

| 013h  | PIR3                          | 093h   | PIE3                          | 113h | CM2CON0                       | 193h | PMDATL                        | 213h  | _                             | 293h   | _                             | 313h                 | —                                          | 393h   | IOCAF                         |

| 014h  | —                             | 094h   | —                             | 114h | CM2CON1                       | 194h | PMDATH                        | 214h  | _                             | 294h   | _                             | 314h                 | —                                          | 394h   | IOCBP                         |

| 015h  | TMR0                          | 095h   | OPTION_REG                    | 115h | CMOUT                         | 195h | PMCON1                        | 215h  | _                             | 295h   | _                             | 315h                 | —                                          | 395h   | IOCBN                         |

| 016h  | TMR1L                         | 096h   | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h  | _                             | 296h   | _                             | 316h                 |                                            | 396h   | IOCBF                         |

| 017h  | TMR1H                         | 097h   | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(1)</sup>        | 217h  | _                             | 297h   | _                             | 317h                 | _                                          | 397h   | IOCCP                         |

| 018h  | T1CON                         | 098h   | OSCTUNE                       | 118h | DACCON0                       | 198h | —                             | 218h  | —                             | 298h   | —                             | 318h                 | —                                          | 398h   | IOCCN                         |

| 019h  | T1GCON                        | 099h   | OSCCON                        | 119h | DACCON1                       | 199h | RCREG                         | 219h  | _                             | 299h   | _                             | 319h                 | —                                          | 399h   | IOCCF                         |

| 01Ah  | TMR2                          | 09Ah   | OSCSTAT                       | 11Ah | —                             | 19Ah | TXREG                         | 21Ah  | —                             | 29Ah   | —                             | 31Ah                 |                                            | 39Ah   | —                             |

| 01Bh  | PR2                           | 09Bh   | ADRESL                        | 11Bh | —                             | 19Bh | SPBRGL                        | 21Bh  | —                             | 29Bh   | —                             | 31Bh                 |                                            | 39Bh   | —                             |

| 01Ch  | T2CON                         | 09Ch   | ADRESH                        | 11Ch | —                             | 19Ch | SPBRGH                        | 21Ch  | —                             | 29Ch   | —                             | 31Ch                 | _                                          | 39Ch   | —                             |

| 01Dh  | —                             | 09Dh   | ADCON0                        | 11Dh | —                             | 19Dh | RCSTA                         | 21Dh  | —                             | 29Dh   | —                             | 31Dh                 | —                                          | 39Dh   | —                             |

| 01Eh  |                               | 09Eh   | ADCON1                        | 11Eh | —                             | 19Eh | TXSTA                         | 21Eh  | _                             | 29Eh   | _                             | 31Eh                 |                                            | 39Eh   | —                             |

| 01Fh  | _                             | 09Fh   | ADCON2                        | 11Fh | —                             | 19Fh | BAUDCON                       | 21Fh  | _                             | 29Fh   | _                             | 31Fh                 | _                                          | 39Fh   | _                             |

| 020h  | General<br>Purpose            | 0A0h   | General<br>Purpose            | 120h | General<br>Purpose            | 1A0h | General<br>Purpose            | 220h  | General<br>Purpose            | 2A0h   | General<br>Purpose            | 320h<br>32Fh<br>330h | General<br>Purpose<br>Register<br>16 Bytes | 3A0h   | Unimplemented<br>Read as '0'  |

| 06Fh  | Register<br>80 Bytes          | 0EFh   | Register<br>80 Bytes          | 16Fh | Register<br>80 Bytes          | 1EFh | Register<br>80 Bytes          | 26Fh  | Register<br>80 Bytes          | 2EFh   | Register<br>80 Bytes          | 36Fh                 | Unimplemented<br>Read as '0'               | 3EFh   | Read as 0                     |

| 070h  |                               | 0F0h   |                               | 170h |                               | 1F0h |                               | 270h  |                               | 2F0h   |                               | 370h                 |                                            | 3F0h   |                               |

| 0.011 | Common RAM                    | 5. 611 | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         | 2.011 | Accesses<br>70h – 7Fh         | 2. 011 | Accesses<br>70h – 7Fh         | 0.011                | Accesses<br>70h – 7Fh                      | 5. 0.1 | Accesses<br>70h – 7Fh         |

| 07Fh  |                               | 0FFh   |                               | 17Fh |                               | 1FFh |                               | 27Fh  |                               | 2FFh   |                               | 37Fh                 |                                            | 3FFh   |                               |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1578.

#### TABLE 3-11: PIC16(L)F1574/5/8/9 MEMORY MAP, BANK 27

|                 | MAP, BANK 27            |                        |

|-----------------|-------------------------|------------------------|

|                 | Bank 27                 |                        |

| D8Ch            | _                       |                        |

| D8Dh            | <br>PWMEN               |                        |

| D8Eh<br>D8Fh    | PWMLD                   |                        |

| D90h            | PWMOUT                  |                        |

| D91h            | PWM1PHL                 |                        |

| D92h            | PWM1PHH                 |                        |

| D93h            | PWM1DCL                 |                        |

| D94h            | PWM1DCH<br>PWM1PRL      |                        |

| D95h<br>D96h    | PWMIPRL<br>PWM1PRH      |                        |

| D9011<br>D97h   | PWM10FL                 |                        |

| D98h            | PWM10FH                 |                        |

| D99h            | PWM1TMRL                |                        |

| D9Ah            | PWM1TMRH                |                        |

| D9Bh            | PWM1CON                 |                        |

| D9Ch<br>D9Dh    | PWM1INTE<br>PWM1INTF    |                        |

| D9Dh<br>D9Eh    | PWM1CLKCON              |                        |

| D9Eh<br>D9Fh    | PWM1LDCON               |                        |

| DA0h            | PWM10FC0N               |                        |

| DA1h            | PWM2PHL                 |                        |

| DA2h            | PWM2PHH                 |                        |

| DA3h            | PWM2DCL<br>PWM2DCH      |                        |

| DA4h<br>DA5h    | PWM2DCH<br>PWM2PRL      |                        |

| DA6h            | PWM2PRH                 |                        |

| DA7h            | PWM2OFL                 |                        |

| DA8h            | PWM2OFH                 |                        |

| DA9h            | PWM2TMRL                |                        |

| DAAh            | PWM2TMRH                |                        |

| DABh            | PWM2CON<br>PWM2INTE     |                        |

| DACh<br>DADh    | PWM2INTE<br>PWM2INTF    |                        |

| DADh            | PWM2CLKCON              |                        |

| DAFh            | PWM2LDCON               |                        |

| DB0h            | PWM2OFCON               |                        |

| DB1h            | PWM3PHL                 |                        |

| DB2h            | PWM3PHH<br>PWM3DCL      |                        |

| DB3h<br>DB4h    | PWM3DCL<br>PWM3DCH      |                        |

| DB4II<br>DB5h   | PWM3PRL                 |                        |

| DB6h            | PWM3PRH                 |                        |

| DB7h            | PWM3OFL                 |                        |

| DB8h            | PWM30FH                 |                        |

| DB9h            | PWM3TMRL                |                        |

| DBAh            | PWM3TMRH<br>PWM3CON     |                        |

| DBBh<br>DBCh    | PWM3INTE                |                        |

| DBDh            | PWM3INTF                |                        |

| DBEh            | PWM3CLKCON              |                        |

| DBFh            | PWM3LDCON               |                        |

| DC0h            | PWM3OFCON               |                        |

| DC1h            | PWM4PHL<br>PWM4PHH      |                        |

| DC2h<br>DC3h    | PWM4PHH<br>PWM4DCL      |                        |

| DC4h            | PWM4DCH                 |                        |

| DC5h            | PWM4PRL                 |                        |

| DC6h            | PWM4PRH                 |                        |

| DC7h            | PWM40FL                 |                        |

| DC8h            | PWM40FH                 |                        |

| DC9h            | PWM4TMRL                |                        |

| DCAh            | PWM4TMRH<br>PWM4CON     |                        |

| DCBh<br>DCCh    | PWM4CON<br>PWM4INTE     |                        |

| DCCh            | PWM4INTE<br>PWM4INTF    |                        |

| DCEh            | PWM4CLKCON              |                        |

| DCFh            | PWM4LDCON               |                        |

| DD0h            | PWM40FC0N               |                        |

| DD1h            |                         |                        |

|                 |                         |                        |

| DEFh            | —                       |                        |

| Legend: = Unimp | plemented data memory l | ocations, read as '0'. |

# TABLE 3-12: PIC16(L)F1574/5/8/9 MEMORY MAP, BANK 28-29 MAP

|         |                  |          | .0-23                 |

|---------|------------------|----------|-----------------------|

|         | Bank 28          | _        | Bank 29               |

| E0Ch    | _                | E8Ch     | —                     |

| E0Dh    | —                | E8Dh     | —                     |

| E0Eh    | —                | E8Eh     | —                     |

| E0Fh    | PPSLOCK          | E8Fh     | —                     |

| E10h    | INTPPS           | E90h     | RA0PPS                |

| E11h    | TOCKIPPS         | E91h     | RA1PPS                |

| E12h    | T1CKIPPS         | E92h     | RA2PPS                |

|         |                  |          | 104211-0              |

| E13h    | T1GPPS           | E93h     | -                     |

| E14h    | CWG1PPS          | E94h     | RA4PPS                |

| E15h    | RXPPS            | E95h     | RA5PPS                |

| E16h    | CKPPS            | E96h     | _                     |

| E17h    | ADCACTPPS        | E97h     | _                     |

| E18h    | _                | E98h     |                       |

| E19h    | _                | E99h     | _                     |

| E1Ah    |                  | E9Ah     |                       |

|         |                  |          |                       |

| E1Bh    |                  | E9Bh     | —                     |

| E1Ch    | _                | E9Ch     | RB4PPS <sup>(1)</sup> |

| E1Dh    | -                | E9Dh     | RB5PPS <sup>(1)</sup> |

|         | -                |          | RB6PPS <sup>(1)</sup> |

| E1Eh    |                  | E9Eh     |                       |

| E1Fh    |                  | E9Fh     | RB7PPS <sup>(1)</sup> |

| E20h    | _                | EA0h     | RC0PPS                |

| E21h    | _                | EA1h     | RC1PPS                |

| E22h    |                  | EA2h     | RC2PPS                |

| E23h    |                  | EA3h     | RC3PPS                |

|         |                  | -        |                       |

| E24h    | _                | EA4h     | RC4PPS                |

| E25h    |                  | EA5h     | RC5PPS                |

| E26h    | _                | EA6h     | RC6PPS <sup>(1)</sup> |

| E27h    |                  | EA7h     | RC7PPS <sup>(1)</sup> |

|         |                  |          | KUTFF3.               |

| E28h    |                  | EA8h     |                       |

| E29h    | _                | EA9h     | —                     |

| E2Ah    |                  | EAAh     |                       |

| E2Bh    |                  | EABh     | —                     |

| E2Ch    |                  | EACh     | _                     |

| E2Dh    |                  | EADh     |                       |

| E2Eh    |                  | EAEh     |                       |

|         |                  |          |                       |

| E2Fh    |                  | EAFh     | —                     |

| E30h    | _                | EB0h     | —                     |

| E31h    | _                | EB1h     | _                     |

| E32h    | _                | EB2h     | —                     |

| E33h    |                  | EB3h     |                       |

| E34h    |                  | EB4h     | _                     |

| E35h    |                  | EB5h     |                       |

| E36h    |                  | EB5h     |                       |

|         |                  |          | _                     |

| E37h    |                  | EB7h     | —                     |

| E38h    |                  | EB8h     | —                     |

| E39h    | _                | EB9h     | ]                     |

| E3Ah    |                  | EBAh     |                       |

| E3Bh    |                  | EBBh     | _                     |

| E3Ch    |                  | EBCh     |                       |

|         |                  |          |                       |

| E3Dh    |                  | EBDh     | —                     |

| E3Eh    |                  | EBEh     | —                     |

| E3Fh    |                  | EBFh     | —                     |

| E40h    |                  | EC0h     |                       |

|         | _                |          | _                     |

| E6Fh    |                  | EEFh     |                       |

| Legend: | = Unimpleme      | 1        | memory locations,     |

|         | read as '0'      |          |                       |

| lote 1: | Unimplemented on | PIC16(L) | )F1574/5.             |

|         |                  |          |                       |

# 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

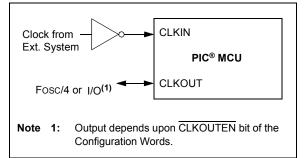

#### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the CLKIN input. CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through the Fosc bits in the Configuration Words:

- ECH High power, 4-20 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

The Oscillator Start-up Timer (OST), when available, is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-On Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

© 2016 Microchip Technology Inc.

# 11.1 PORTA Registers

## 11.1.1 DATA REGISTER

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 11-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input-only and its TRIS bit will always read as '1'. Example 11-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 11-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

### 11.1.2 DIRECTION CONTROL

The TRISA register (Register 11-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

### 11.1.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.1.4 SLEW RATE CONTROL

The SLRCONA register (Register 11-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

# 11.1.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 11-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 27-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

# 11.1.6 ANALOG CONTROL

The ANSELA register (Register 11-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

# EXAMPLE 11-1: INITIALIZING PORTA

```

; This code example illustrates

; initializig the PORTA register. The

; other ports are initialized in the same

; manner.

BANKSEL PORTA

;

CLRF

PORTA

;Init PORTA

BANKSEL LATA

;Data Latch

CLRF

T.ATA

;

BANKSEL ANSELA

;

CLRF

ANSELA

;digital I/O

BANKSEL TRISA

MOVLW

B'00111000' ;Set RA<5:3> as inputs

MOVWF

TRISA

;and set RA<2:0> as

;outputs

```

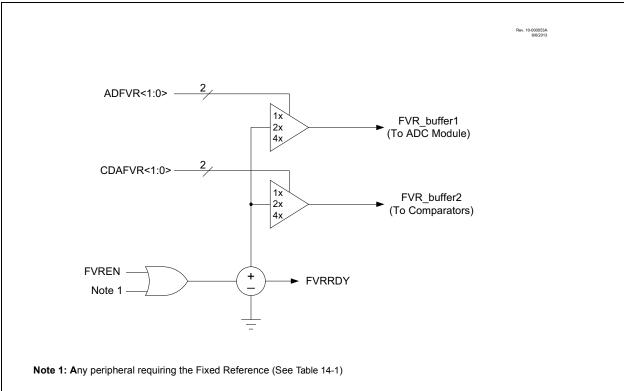

# 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR) is a stable voltage reference, independent of VDD, with a nominal output level (VFVR) of 1.024V. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- Comparator positive input

- · Comparator negative input

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

# 14.1 Independent Gain Amplifier

The output of the FVR supplied to the peripherals, (listed above), is routed through a programmable gain amplifier. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 16.0 "Analog-to-Digital Converter** (**ADC**) **Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the comparator modules. Reference **Section 18.0 "Comparator Module"** for additional information.

To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.

# 14.2 FVR Stabilization Period

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set.

FIGURE 14-1: VOLTAGE REFERENCE BLOCK DIAGRAM

| Peripheral | Conditions                                                        | Description                                                        |

|------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 010 and<br>IRCF<3:0> = 000x                           | INTOSC is active and device is not in Sleep.                       |

|            | BOREN<1:0> = 11                                                   | BOR always enabled.                                                |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                     | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                                     | BOR under software control, BOR Fast Start enabled.                |

| LDO        | All PIC16F1574/5/8/9 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the Low-Power Regulator when in Sleep mode. |

# TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

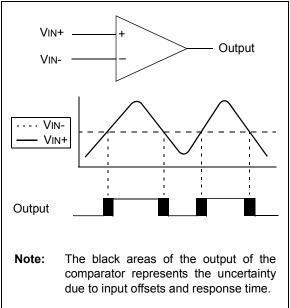

#### FIGURE 18-2: SINGLE COMPARATOR

# 18.2 Comparator Control

The comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- Output selection

- Output polarity

- Speed/Power selection

- Hysteresis enable

- · Output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR POSITIVE INPUT SELECTION

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC1\_output

- FVR\_buffer2

- Vss

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

# 18.2.3 COMPARATOR NEGATIVE INPUT SELECTION

The CxNCH<2:0> bits of the CMxCON0 register direct one of the input sources to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog<br>input, the appropriate bits must be set in<br>the ANSEL register and the correspond- |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

|       | ing TRIS bits must also be set to disable                                                                                      |

|       | the output drivers.                                                                                                            |

### 18.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

The synchronous comparator output signal (CxOUT\_sync) is available to the following peripheral(s):

- Analog-to-Digital Converter (ADC)

- Timer1

The asynchronous comparator output signal (CxOUT\_async) is available to the following peripheral(s):

Complementary Waveform Generator (CWG)

Note: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

# 20.6 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

**Note:** The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 20.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- · TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the  $\overline{\text{T1SYNC}}$  bit setting.

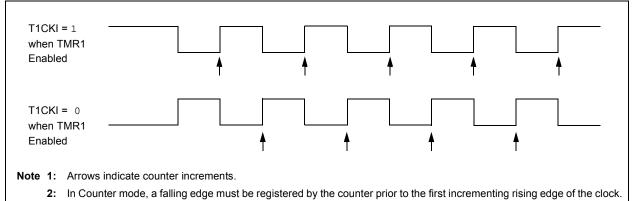

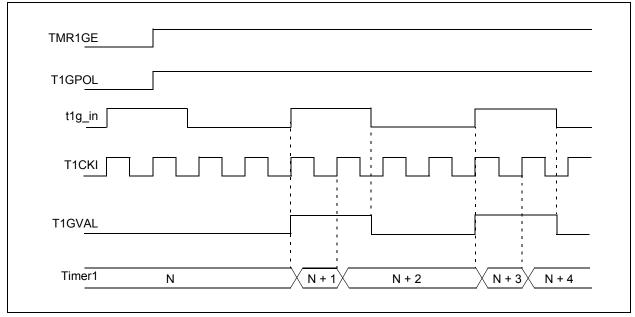

# FIGURE 20-3: TIMER1 GATE ENABLE MODE

| FIGURE 22-12:                                   | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                   |

|-------------------------------------------------|-----------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)         |                                                                             |

| TX/CK pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                             |

| SREN bit                                        | ·0'                                                                         |

| RCIF bit<br>(Interrupt)                         |                                                                             |

| Read<br>RCREG                                   | ŕ                                                                           |

| Note: Timing dia                                | gram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

#### **~**

#### TABLE 22-8: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4      | Bit 3       | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

|---------|----------|-----------|--------|------------|-------------|--------|--------|--------|---------------------|--|

| BAUDCON | ABDOVF   | RCIDL     |        | SCKP       | BRG16       | _      | WUE    | ABDEN  | 204                 |  |

| INTCON  | GIE      | PEIE      | TMR0IE | INTE       | IOCIE       | TMR0IF | INTF   | IOCIF  | 86                  |  |

| PIE1    | TMR1GIE  | ADIE      | RCIE   | TXIE       | —           | _      | TMR2IE | TMR1IE | 87                  |  |

| PIR1    | TMR1GIF  | ADIF      | RCIF   | TXIF       | —           | _      | TMR2IF | TMR1IF | 90                  |  |

| RCREG   |          |           | EUS    | ART Receiv | ve Data Reg | gister |        |        | 197*                |  |

| RCSTA   | SPEN     | RX9       | SREN   | CREN       | ADDEN       | FERR   | OERR   | RX9D   | 203                 |  |

| SPBRGL  | BRG<7:0> |           |        |            |             |        |        |        |                     |  |

| SPBRGH  |          | BRG<15:8> |        |            |             |        |        |        |                     |  |

| TXSTA   | CSRC     | TX9       | TXEN   | SYNC       | SENDB       | BRGH   | TRMT   | TX9D   | 202                 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

Page provides register information. \*

# TABLE 23-2: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

| Name                    | Bit 7    | Bit 6  | Bit 5    | Bit 4  | Bit 3       | Bit 2     | Bit 1     | Bit 0     | Register<br>on Page |  |

|-------------------------|----------|--------|----------|--------|-------------|-----------|-----------|-----------|---------------------|--|

| OSCCON                  | SPLLEN   |        | IRC      | F<3:0> | •           | _         | SCS       | <1:0>     | 69                  |  |

| PIE3                    | PWM4IE   | PWM3IE | PWM2IE   | PWM1IE | _           |           |           |           | 89                  |  |

| PIR3                    | PWM4IF   | PWM3IF | PWM2IF   | PWM1IF | _           | _         | _         | _         | 92                  |  |

| PWMEN                   | -        | —      | —        | _      | PWM4EN_A    | PWM3EN_A  | PWM2EN_A  | PWM1EN_A  | 243                 |  |

| PWMLD                   | _        | _      | _        | _      | PWM4LDA_A   | PWM3LDA_A | PWM2LDA_A | PWM1LDA_A | 243                 |  |

| PWMOUT                  | _        | _      | _        | _      | PWM4OUT_A   | PWM3OUT_A | PWM2OUT_A | PWM1OUT_A | 243                 |  |

| PWM1PHL                 |          |        |          | F      | PH<7:0>     | . –       | . –       |           | 238                 |  |

| PWM1PHH                 | PH<15:8> |        |          |        |             |           |           |           |                     |  |

| PWM1DCL                 | DC<7:0>  |        |          |        |             |           |           |           |                     |  |

| PWM1DCH                 | DC<15:8> |        |          |        |             |           |           |           |                     |  |

| PWM1PRL                 |          |        |          | F      | PR<7:0>     |           |           |           | 240                 |  |

| PWM1PRH                 |          |        |          | Р      | R<15:8>     |           |           |           | 240                 |  |

| PWM10FL                 |          |        |          |        | )F<7:0>     |           |           |           | 241                 |  |

| PWM10FH                 |          |        |          |        | F<15:8>     |           |           |           | 241                 |  |

| PWM1TMRL                |          |        |          |        | MR<7:0>     |           |           |           | 242                 |  |

| PWM1TMRH                |          |        |          |        | IR<15:8>    |           |           |           | 242                 |  |

| PWM1CON                 | EN       | _      | OUT      | POL    | T           | E<1:0>    | _         | _         | 233                 |  |

| PWM1INTE                | _        | _      | _        | _      | OFIE        | PHIE      | DCIE      | PRIE      | 233                 |  |

| PWM1INTF                |          |        |          |        | OFIE        | PHIF      | DCIF      | PRIF      | 234                 |  |

| PWM1CLKCON              |          |        | PS<2:0>  |        | -           |           | -         | :1:0>     | 235                 |  |

| PWM1CLRCON<br>PWM1LDCON | LDA      | LDT    | F 3 2.02 |        |             |           |           | <1:0>     | 235                 |  |

| PWM10FCON               | LDA      | OFM    | <1:0>    | OFO    |             |           | -         | <1:0>     | 230                 |  |

|                         |          | OTIV   | <1.02    |        | <br>PH<7:0> | —         | 013       | <1.02     | 237                 |  |

| PWM2PHL                 |          |        |          |        | H<15:8>     |           |           |           |                     |  |

| PWM2PHH                 |          |        |          |        |             |           |           |           | 238                 |  |

| PWM2DCL                 |          |        |          |        | )C<7:0>     |           |           |           | 239                 |  |

| PWM2DCH                 |          |        |          |        | C<15:8>     |           |           |           | 239                 |  |

| PWM2PRL                 |          |        |          |        | PR<7:0>     |           |           |           | 240                 |  |

| PWM2PRH                 |          |        |          |        | R<15:8>     |           |           |           | 240                 |  |

| PWM2OFL                 |          |        |          |        | )F<7:0>     |           |           |           | 241                 |  |

| PWM2OFH                 |          |        |          |        | F<15:8>     |           |           |           | 241                 |  |

| PWM2TMRL                |          |        |          |        | VIR<7:0>    |           |           |           | 242                 |  |

| PWM2TMRH                |          |        |          | -      | 1R<15:8>    |           |           |           | 242                 |  |

| PWM2CON                 | EN       | —      | OUT      | POL    |             | E<1:0>    | -         | -         | 233                 |  |

| PWM2INTE                |          | _      | —        |        | OFIE        | PHIE      | DCIE      | PRIE      | 234                 |  |

| PWM2INTF                |          |        |          | —      | OFIF        | PHIF      | DCIF      | PRIF      | 234                 |  |

| PWM2CLKCON              | —        |        | PS<2:0>  |        | _           | —         | -         | <1:0>     | 235                 |  |

| PWM2LDCON               | LDA      | LDT    | —        | -      | _           | _         | -         | <1:0>     | 236                 |  |

| PWM2OFCON               | —        | OFM    | <1:0>    | OFO    | -           | —         | OFS       | <1:0>     | 237                 |  |

| PWM3PHL                 |          |        |          |        | PH<7:0>     |           |           |           | 238                 |  |

| PWM3PHH                 |          |        |          |        | H<15:8>     |           |           |           | 238                 |  |

| PWM3DCL                 |          |        |          |        | )C<7:0>     |           |           |           | 239                 |  |

| PWM3DCH                 |          |        |          |        | C<15:8>     |           |           |           | 239                 |  |

| PWM3PRL                 |          |        |          |        | PR<7:0>     |           |           |           | 240                 |  |

| PWM3PRH                 |          |        |          |        | R<15:8>     |           |           |           | 240                 |  |

| PWM3OFL                 |          |        |          |        | )F<7:0>     |           |           |           | 241                 |  |

| PWM3OFH                 |          |        |          | 0      | F<15:8>     |           |           |           | 241                 |  |

| PWM3TMRL                |          |        |          | T      | VIR<7:0>    |           |           |           | 242                 |  |

| PWM3TMRH                |          |        | 1        | TN     | 1R<15:8>    |           |           |           | 242                 |  |

| PWM3CON                 | EN       | —      | OUT      | POL    | MODE        | =<1:0>    | —         | —         | 233                 |  |

| PWM3INTE                | _        | —      | —        | —      | OFIE        | PHIE      | DCIE      | PRIE      | 234                 |  |

| PWM3INTF                | _        | _      | —        |        | OFIF        | PHIF      | DCIF      | PRIF      | 234                 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PWM.

|                  | <b>D</b> 444 676                                                  |                                                                                                                                                                                                                                |              |                                                   | 5 4 4 6 40       |                     |           |  |  |  |  |

|------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------|------------------|---------------------|-----------|--|--|--|--|

| R/W-0/0          | R/W-0/0                                                           | U-0                                                                                                                                                                                                                            | U-0          | R/W-0/0                                           | R/W-0/0          | R/W-0/0             | U-0       |  |  |  |  |

| GxASE            | GxARSEN                                                           |                                                                                                                                                                                                                                | —            | GxASDSC2                                          | GxASDSC1         | GxASDSPPS           |           |  |  |  |  |

| bit 7            |                                                                   |                                                                                                                                                                                                                                |              |                                                   |                  |                     | bit (     |  |  |  |  |

| Legend:          |                                                                   |                                                                                                                                                                                                                                |              |                                                   |                  |                     |           |  |  |  |  |

| R = Readable     | e bit                                                             | W = Writable                                                                                                                                                                                                                   | e bit        | U = Unimpler                                      | nented bit, read | as '0'              |           |  |  |  |  |

| u = Bit is unc   | hanged                                                            | x = Bit is unl                                                                                                                                                                                                                 | known        | -n/n = Value a                                    | at POR and BO    | R/Value at all othe | er Resets |  |  |  |  |

| '1' = Bit is set | t                                                                 | '0' = Bit is cl                                                                                                                                                                                                                | eared        | q = Value dep                                     | pends on condit  | ion                 |           |  |  |  |  |

| bit 7<br>bit 6   | 1 = An auto-<br>0 = No auto-<br><b>GxARSEN:</b> A<br>1 = Auto-res | GxASE: Auto-Shutdown Event Status bit<br>1 = An auto-shutdown event has occurred<br>0 = No auto-shutdown event has occurred<br>GxARSEN: Auto-Restart Enable bit<br>1 = Auto-restart is enabled<br>0 = Auto-restart is disabled |              |                                                   |                  |                     |           |  |  |  |  |

| bit 5-4          | Unimplemer                                                        | nted: Read as                                                                                                                                                                                                                  | '0'          |                                                   |                  |                     |           |  |  |  |  |

| bit 3            | 1 = Shutdow                                                       | n when Comp                                                                                                                                                                                                                    | arator C2 ou | comparator C2 I<br>tput (C2OUT_s<br>t on shutdown |                  |                     |           |  |  |  |  |

| bit 2            | 1 = Shutdow                                                       | n when Comp                                                                                                                                                                                                                    | arator C1 ou | comparator C1 I<br>tput (C1OUT_s<br>t on shutdown |                  |                     |           |  |  |  |  |

| bit 1            | 1 = Shutdow                                                       | <b>GxASDSPPS:</b> CWG Input Pin Enable bit<br>1 = Shutdown when CWG input pin (CWGxIN) is high<br>0 = CWG input pin (CWGxIN) signal has no effect on shutdown                                                                  |              |                                                   |                  |                     |           |  |  |  |  |

| bit 0            | Unimplemer                                                        | nted: Read as                                                                                                                                                                                                                  | '0'          |                                                   |                  |                     |           |  |  |  |  |

|                  | F                                                                 |                                                                                                                                                                                                                                |              |                                                   |                  |                     |           |  |  |  |  |

# REGISTER 24-3: CWGxCON2: CWG CONTROL REGISTER 2

# 25.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>™</sup> refer to the "*PIC16(L)F157x Memory Programming Specification*" (DS40001766).

# 25.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

# 25.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5** "**MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

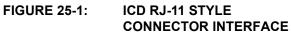

# 25.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 25-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 25-2.

# PIC16(L)F1574/5/8/9

| LSLF             | Logical Left Shift                                                                                                                                                                                                                       | MOVF             | Move f                                                                                                                                                                                              |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] LSLF                                                                                                                                                                                                                    | Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                           |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                                       | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                  |  |  |  |

| Operation:       | $(f<7>) \rightarrow C$<br>$(f<6:0>) \rightarrow dest<7:1>$<br>$0 \rightarrow dest<0>$                                                                                                                                                    | Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                            |  |  |  |

|                  |                                                                                                                                                                                                                                          | Status Affected: | Z                                                                                                                                                                                                   |  |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                                     | Description:     | The contents of register f is moved to<br>a destination dependent upon the                                                                                                                          |  |  |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the left through the Carry flag.<br>A '0' is shifted into the LSb. If 'd' is '0',<br>the result is placed in W. If 'd' is '1', the<br>result is stored back in register 'f'.<br>C |                  | status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ , the<br>destination is file register f itself. $d = 1$<br>is useful to test a file register since<br>status flag Z is affected. |  |  |  |

|                  |                                                                                                                                                                                                                                          | Words:           | 1                                                                                                                                                                                                   |  |  |  |

|                  |                                                                                                                                                                                                                                          | Cycles:          | 1                                                                                                                                                                                                   |  |  |  |

|                  |                                                                                                                                                                                                                                          | Example:         | MOVF FSR, 0                                                                                                                                                                                         |  |  |  |

| LSRF             | Logical Right Shift                                                                                                                                                                                                                      |                  | After Instruction<br>W = value in FSR register                                                                                                                                                      |  |  |  |

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                                                                               |                  | Z = 1                                                                                                                                                                                               |  |  |  |

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                                                                           |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                    |  |  |

| Operation:       | $\begin{array}{l} 0 \rightarrow dest < 7 > \\ (f < 7:1 >) \rightarrow dest < 6:0 >, \\ (f < 0 >) \rightarrow C, \end{array}$                                                                                                         |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                                 |  |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. A '0' is shifted into the MSb. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is stored back in register 'f'. |  |  |

|                  | 0 → register f C                                                                                                                                                                                                                     |  |  |

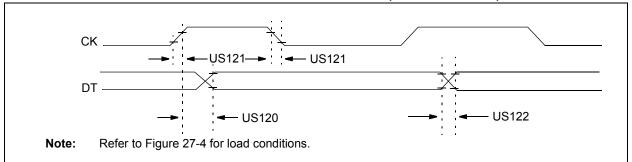

# FIGURE 27-13: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

# TABLE 27-17: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                                                              |                                        |      |      |                                  |                                |

|---------------------------------------------------------|--------------------------------------------------------------|----------------------------------------|------|------|----------------------------------|--------------------------------|

| Param.<br>No.                                           | Symbol                                                       | Characteristic                         | Min. | Max. | Units                            | Conditions                     |

| US120 TCKH2DTV                                          | SYNC XMIT (Master and Slave)<br>Clock high to data-out valid | _                                      | 80   | ns   | $3.0V \le V\text{DD} \le 5.5V$   |                                |

|                                                         |                                                              | —                                      | 100  | ns   | $1.8V \leq V\text{DD} \leq 5.5V$ |                                |

| US121 TCKRF                                             | Clock out rise time and fall time (Master mode)              | _                                      | 45   | ns   | $3.0V \le V\text{DD} \le 5.5V$   |                                |

|                                                         |                                                              | _                                      | 50   | ns   | $1.8V \le V\text{DD} \le 5.5V$   |                                |

| US122                                                   | TDTRF                                                        | TDTRF Data-out rise time and fall time | —    | 45   | ns                               | $3.0V \le V\text{DD} \le 5.5V$ |

|                                                         |                                                              |                                        | _    | 50   | ns                               | $1.8V \le V\text{DD} \le 5.5V$ |

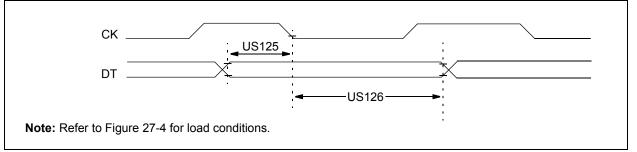

# FIGURE 27-14: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

# TABLE 27-18: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                                                                |      |      |       |            |

|---------------------------------------------------------|----------|--------------------------------------------------------------------------------|------|------|-------|------------|

| Param.<br>No.                                           | Symbol   | Characteristic                                                                 | Min. | Max. | Units | Conditions |

| US125                                                   | TDTV2CKL | SYNC RCV (Master and Slave)<br>Data-hold before CK $\downarrow$ (DT hold time) | 10   | _    | ns    |            |

| US126                                                   | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                                 | 15   |      | ns    |            |

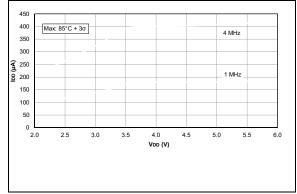

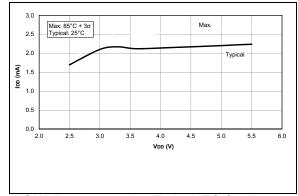

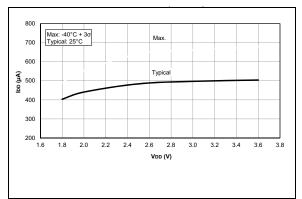

FIGURE 28-7: IDD Typical, EC Oscillator, Medium Power Mode, PIC16F1574/5/8/9 Only.

FIGURE 28-8: IDD Maximum, EC Oscillator, Medium Power Mode, PIC16F1574/5/8/9 Only.

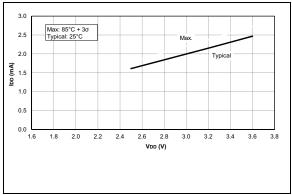

**FIGURE 28-9:** IDD Typical, EC Oscillator, High-Power Mode, Fosc = 32 kHz, PIC16LF1574/5/8/9 Only.

**FIGURE 28-10:** IDD Typical, EC Oscillator, High-Power Mode, Fosc = 32 kHz, PIC16F1574/5/8/9 Only.

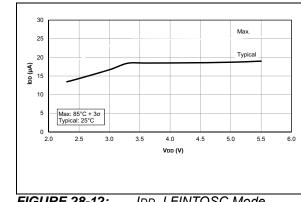

FIGURE 28-12: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16F1574/5/8/9 Only.

12 (**V**rl) 10 8 Typical 4 2 0 3.4 3.6 1.8 2.0 2.2 2.4 2.6 2.8 3.0 3.2 3.8 1.6 VDD (V) FIGURE 28-11: IDD, LFINTOSC Mode,

Max.

Fosc = 31 kHz, PIC16LF1574/5/8/9 Only.

18

16

14

Max: 85°C + 3o Typical: 25°C

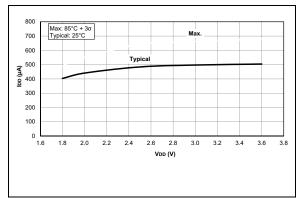

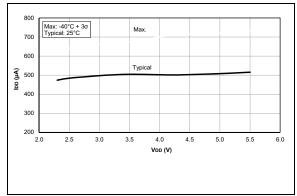

FIGURE 28-31: Ipd, Comparator, Low-Power Mode (CxSP = 0), PIC16LF1574/5/8/9 Only.

**FIGURE 28-32:** Ipd, Comparator, Low-Power Mode (CxSP = 0), PIC16F1574/5/8/9 Only.

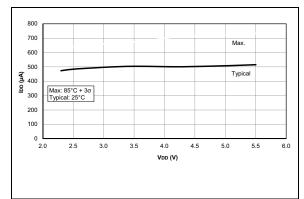

**FIGURE 28-33:** Ipd, Comparator, Normal Power Mode (CxSP = 1), PIC16LF1574/5/8/9 Only.

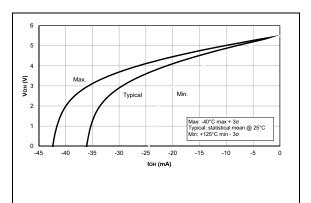

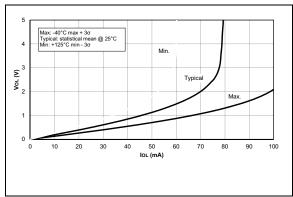

**FIGURE 28-35:** VOH vs. IOH Over Temperature, VDD = 5.5V, PIC16F1574/5/8/9 Only.

**FIGURE 28-34:** Ipd, Comparator, Normal Power Mode (CxSP = 1), PIC16F1574/5/8/9 Only.

**FIGURE 28-36:** VoL vs. IoL Over Temperature, VDD = 5.5V, PIC16F1574/5/8/9 Only.

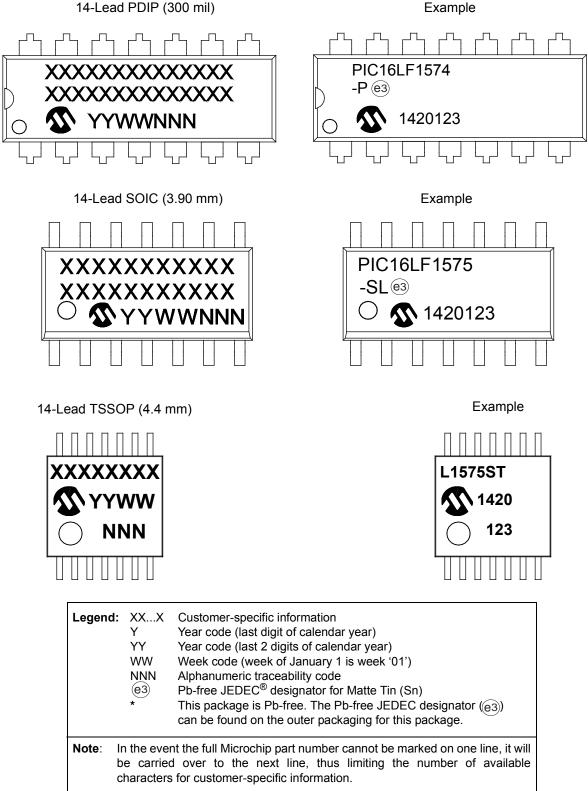

#### 30.0 PACKAGING INFORMATION

#### 30.1 **Package Marking Information**

14-Lead PDIP (300 mil)

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | IS MILLIMETERS |      |      |  |

|--------------------------|-------|----------------|------|------|--|

| Dimension                | MIN   | NOM            | MAX  |      |  |

| Number of Pins           | N     | 14             |      |      |  |

| Pitch                    | е     | 0.65 BSC       |      |      |  |

| Overall Height           | А     | I              | 1.20 |      |  |

| Molded Package Thickness | A2    | 0.80           | 1.00 | 1.05 |  |

| Standoff                 | A1    | 0.05           | -    | 0.15 |  |

| Overall Width            | E     | E 6.40 BSC     |      |      |  |

| Molded Package Width     | E1    | 4.30           | 4.40 | 4.50 |  |

| Molded Package Length    | D     | 4.90           | 5.00 | 5.10 |  |

| Foot Length              | L     | 0.45           | 0.60 | 0.75 |  |

| Footprint                | (L1)  | 1.00 REF       |      |      |  |

| Foot Angle               | φ     | 0°             | -    | 8°   |  |

| Lead Thickness           | С     | 0.09           | -    | 0.20 |  |

| Lead Width               | b     | 0.19           | -    | 0.30 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2