# Microchip Technology - PIC16LF1575-E/P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

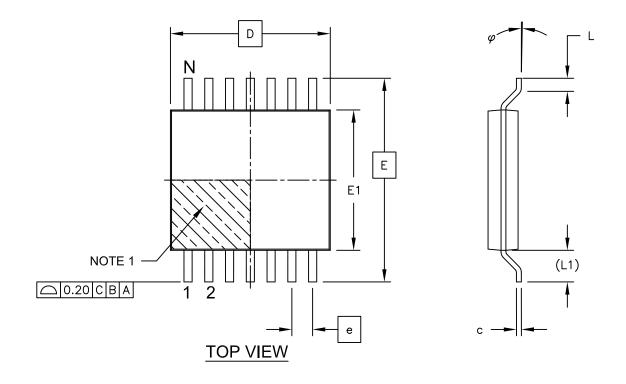

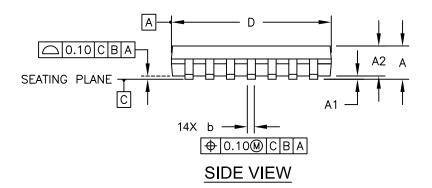

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1575-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Analog Peripherals**

- 10-Bit Analog-to-Digital Converter (ADC):

- Up to 12 external channels

- Conversion available during Sleep

- Two Comparators:

- Low-Power/High-Speed modes

- Fixed Voltage Reference at (non)inverting input(s)

- Comparator outputs externally accessible

- Synchronization with Timer1 clock source

- Software hysteresis enable

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- Voltage Reference:

TABLE 1:

- Fixed Voltage Reference with 1.024V, 2.048V and 4.096V output levels

# **Clocking Structure**

- Precision Internal Oscillator:

- Factory calibrated ±1%, typical

- Software-selectable clock speeds from 31 kHz to 32 MHz

- · External Oscillator Block with:

- Two external clock modes up to 32 MHz

- Digital Oscillator Input Available

Program Flash Memory Memory 8-Bit/16-Bit Timers SRAM (bytes) Data Sheet Index I0-Bit ADC (ch) Comparators **I6-Bit PWM** Bit DAC Debug<sup>(1)</sup> (Kwords) Pins (Kbytes) EUSART Program Flash CWG PPS Device <u>0</u> Data PIC12(L)F1571 1.75 2/4(2) 128 6 1 3 4 1 1 0 Ν Ι (A) 1 2/4(2) PIC12(L)F1572 (A) 2 3.5 256 6 1 3 4 1 1 1 Ν L 2/5(3)PIC16(L)F1574 12 2 (B) 4 7 512 4 8 1 1 1 Y Т 2/5(3) PIC16(L)F1575 8 14 1024 12 2 4 8 1 1 1 Y I (B) 2/5<sup>(3)</sup> PIC16(L)F1578 (B) 4 7 512 18 2 4 12 1 1 1 Y L 2/5(3) PIC16(L)F1579 8 14 18 2 12 1 Y (B) 1024 4 1 1 Т

**Note 1:** I – Debugging integrated on chip.

2: Three additional 16-bit timers available when not using the 16-bit PWM outputs.

PIC12(L)F1571/2 AND PIC16(L)F1574/5/8/9 FAMILY TYPES

3: Four additional 16-bit timers available when not using the 16-bit PWM outputs.

#### **Data Sheet Index:**

- A) DS-40001723 PIC12(L)F1571/2 Data Sheet, 8-Pin Flash, 8-bit MCU with High-Precision 16-bit PWM

- B) Future Release PIC16(L)F1574/5/8/9 Data Sheet, 8-Pin Flash, 8-bit MCU with High-Precision 16-bit PWM

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

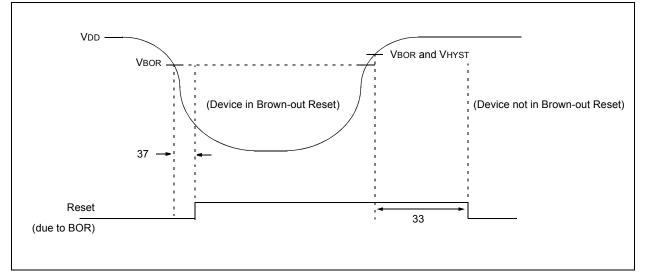

## 6.4 Low-Power Brown-Out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) operates like the BOR to detect low voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit ( $\overline{\text{BOR}}$ ) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR voltage threshold (VLPBOR) has a wider tolerance than the BOR (VBOR), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN = 00) or disabled in Sleep mode (BOREN = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

#### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

# 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

# TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

# 6.5.1 MCLR ENABLED

When  $\overline{\text{MCLR}}$  is enabled and the pin is held low, the device is held in Reset. The  $\overline{\text{MCLR}}$  pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

# **Note:** A Reset does not drive the MCLR pin low.

# 6.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.1 "PORTA Registers"** for more information.

# 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register are changed to indicate the WDT Reset. See **Section 9.0 "Watchdog Timer (WDT)"** for more information.

# 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

# 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 3.5.2 "Overflow/Underflow Reset"** for more information.

# 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

# 6.10 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overline{\text{PWRTE}}$  bit of Configuration Words.

# 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 5.0 "Oscillator Module"** for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 FOSC cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

| U-0          | R/W-0/0                                    | R/W-0/0                     | U-0          | U-0            | U-0              | U-0              | U-0         |

|--------------|--------------------------------------------|-----------------------------|--------------|----------------|------------------|------------------|-------------|

| _            | C2IF                                       | C1IF                        | _            | _              | _                | _                | _           |

| bit 7        |                                            |                             |              |                | I                |                  | bit 0       |

|              |                                            |                             |              |                |                  |                  |             |

| Legend:      |                                            |                             |              |                |                  |                  |             |

| R = Read     | able bit                                   | W = Writable I              | bit          | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is u | unchanged                                  | x = Bit is unkn             | own          | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is | set                                        | '0' = Bit is clea           | ared         |                |                  |                  |             |

|              |                                            |                             |              |                |                  |                  |             |

| bit 7        | Unimplemen                                 | ted: Read as '              | )'           |                |                  |                  |             |

| bit 6        | C2IF: Compa                                | rator C2 Interru            | ipt Flag bit |                |                  |                  |             |

|              | 1 = Interrupt i                            |                             |              |                |                  |                  |             |

|              |                                            | s not pending               |              |                |                  |                  |             |

| bit 5        |                                            | rator C1 Interru            | ipt Flag bit |                |                  |                  |             |

|              | 1 = Interrupt i<br>0 = Interrupt i         | s penaing<br>is not pending |              |                |                  |                  |             |

| bit 4-0      | •                                          | ted: Read as '(             | י'           |                |                  |                  |             |

| 2.0 1 0      | C                                          |                             |              |                |                  |                  |             |

| Note:        | Interrupt flog bits a                      | ro oot whon on              | intorrunt    |                |                  |                  |             |

| Note:        | Interrupt flag bits a condition occurs, re |                             |              |                |                  |                  |             |

|              | its corresponding e                        |                             |              |                |                  |                  |             |

|              | Interrupt Enable b                         |                             |              |                |                  |                  |             |

|              | register. User soft                        |                             |              |                |                  |                  |             |

|              | appropriate interrupto enabling an inter   |                             |              |                |                  |                  |             |

|              |                                            |                             |              |                |                  |                  |             |

# REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

# 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 27.0 "Electrical Specifications"** for the LFINTOSC tolerances.

# 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | х      | Х              | Active      |

| 1.0       |        |                | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | х              | Disabled    |

| 00        | х      | Х              | Disabled    |

## TABLE 9-1: WDT OPERATING MODES

# 9.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

# 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- · Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- Device wakes up from Sleep

- Oscillator fail

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 9-2 for more information.

# 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See **Section 5.0 "Oscillator Module"** for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See **Section 3.0 "Memory Organization"** for more information.

# TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                        | WDT        |

|---------------------------------------------------|------------|

| WDTE<1:0> = 00                                    |            |

| WDTE<1:0> = 01 and SWDTEN = 0                     |            |

| WDTE<1:0> = 10 and enter Sleep                    | Cleared    |

| CLRWDT Command                                    | Cleared    |

| Oscillator Fail Detected                          |            |

| Exit Sleep + System Clock = EXTRC, INTOSC, EXTCLK |            |

| Change INTOSC divider (IRCF bits)                 | Unaffected |

# 11.6 Register Definitions: PORTC

#### **REGISTER 11-17: PORTC: PORTC REGISTER**

| R/W-x/u            | R/W-x/u                                                                 | R/W-x/u            | R/W-x/u            | R/W-x/u       | R/W-x/u                                              | R/W-x/u | R/W-x/u |

|--------------------|-------------------------------------------------------------------------|--------------------|--------------------|---------------|------------------------------------------------------|---------|---------|

| RC7 <sup>(2)</sup> | RC6 <sup>(2)</sup>                                                      | RC5                | RC4                | RC3           | RC2                                                  | RC1     | RC0     |

| bit 7              |                                                                         |                    |                    |               |                                                      |         | bit 0   |

|                    |                                                                         |                    |                    |               |                                                      |         |         |

| Legend:            |                                                                         |                    |                    |               |                                                      |         |         |

| R = Readable bit   | t                                                                       | W = Writable bi    | t                  | U = Unimpleme | ented bit, read as                                   | '0'     |         |

| u = Bit is unchan  | unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all o |                    | x = Bit is unknown |               | -n/n = Value at POR and BOR/Value at all other Reset |         |         |

| '1' = Bit is set   |                                                                         | '0' = Bit is clear | ed                 |               |                                                      |         |         |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1, 2)</sup> 1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

2: RC<7:6> are available on PIC16(L)F1578/9 only.

# REGISTER 11-18: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1               | R/W-1/1               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7                 |                       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits<sup>(1)</sup> 1 = PORTC pin configured as an input (tri-stated) 0 = PORTC pin configured as an output

Note 1: TRISC<7:6> are available on PIC16(L)F1578/9 only.

#### REGISTER 11-19: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u              | R/W-x/u              | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| LATC7 <sup>(1)</sup> | LATC6 <sup>(1)</sup> | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

Note 1: LATC<7:6> are available on PIC16(L)F1578/9 only.

2: Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

| R/W-0/0             | R/W-0/0                                                              | R/W-0/0            | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------------------|----------------------------------------------------------------------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|

| ODC7 <sup>(1)</sup> | ODC6 <sup>(1)</sup>                                                  | ODC5               | ODC4    | ODC3                                                  | ODC2    | ODC1    | ODC0    |

| bit 7               |                                                                      |                    |         |                                                       |         |         | bit 0   |

|                     |                                                                      |                    |         |                                                       |         |         |         |

| Legend:             |                                                                      |                    |         |                                                       |         |         |         |

| R = Readable bit    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                    |         |                                                       |         |         |         |

| u = Bit is unchan   | = Bit is unchanged x = Bit is unknown                                |                    | wn      | -n/n = Value at POR and BOR/Value at all other Resets |         |         | Resets  |

| '1' = Bit is set    |                                                                      | '0' = Bit is clear | ed      |                                                       |         |         |         |

## REGISTER 11-22: ODCONC: PORTC OPEN DRAIN CONTROL REGISTER

bit 7-0

ODC<7:0>: PORTC Open-Drain Enable bits<sup>(1)</sup>

For RC<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

**Note 1:** ODC<7:6> are available on PIC16(L)F1578/9 only.

## REGISTER 11-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| SLRC7 <sup>(1)</sup> | SLRC6 <sup>(1)</sup> | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7                | •                    |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits<sup>(1)</sup> For RC<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

Note 1: SLRC<7:6> are available on PIC16(L)F1578/9 only.

#### REGISTER 11-24: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| R/W-1/1                | R/W-1/1                | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|------------------------|------------------------|---------|---------|---------|---------|---------|---------|

| INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7                  |                        |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits<sup>(1)</sup>

For RC<7:0> pins, respectively

1 = ST input used for port reads and interrupt-on-change

0 = TTL input used for port reads and interrupt-on-change

Note 1: INLVLC<7:6> are available on PIC16(L)F1578/9 only.

#### **Register Definitions: ADC Control** 16.3

# REGISTER 16-1: ADCON0: ADC CONTROL REGISTER 0

| U-0          | R/W-0/0                  | R/W-0/0           | R/W-0/0        | R/W-0/0                      | R/W-0/0         | R/W-0/0                            | R/W-0/0      |

|--------------|--------------------------|-------------------|----------------|------------------------------|-----------------|------------------------------------|--------------|

| _            |                          |                   | CHS<4:0>       |                              |                 | GO/DONE                            | ADON         |

| oit 7        |                          |                   |                |                              |                 |                                    | bit C        |

|              |                          |                   |                |                              |                 |                                    |              |

| Legend:      |                          |                   |                |                              |                 |                                    |              |

| R = Read     | lable bit                | W = Writable      | bit            | •                            | nented bit, rea |                                    |              |

|              | unchanged                | x = Bit is unki   |                | -n/n = Value a               | at POR and B    | OR/Value at all o                  | other Resets |

| '1' = Bit is | set                      | '0' = Bit is cle  | ared           |                              |                 |                                    |              |

| bit 7        | Unimpleme                | nted: Read as '   | 0'             |                              |                 |                                    |              |

| bit 6-2      | CHS<4:0>:                | Analog Channe     | I Select bits  |                              |                 |                                    |              |

|              | 00000 = AN               | 10                |                |                              |                 |                                    |              |

|              | 00001 = AN               | J1                |                |                              |                 |                                    |              |

|              | 00010 = AN               |                   |                |                              |                 |                                    |              |

|              | 00011 = AN<br>00100 = AN |                   |                |                              |                 |                                    |              |

|              | 00101 = AN               |                   |                |                              |                 |                                    |              |

|              | 00110 = AN               | 16                |                |                              |                 |                                    |              |

|              | 00111 = AN               |                   |                |                              |                 |                                    |              |

|              | 01000 = AN<br>01001 = AN |                   |                |                              |                 |                                    |              |

|              | 01001 = AN<br>01010 = AN |                   |                |                              |                 |                                    |              |

|              | 01010 = AN               |                   |                |                              |                 |                                    |              |

|              | 01100 = Re               | served. No cha    | nnel connecte  | d.                           |                 |                                    |              |

|              | •                        |                   |                |                              |                 |                                    |              |

|              | •                        |                   |                |                              |                 |                                    |              |

|              | •<br>11100 - Do          | served. No cha    | nnol connocto  | d                            |                 |                                    |              |

|              |                          | nperature Indica  |                | u.                           |                 |                                    |              |

|              | 11110 <b>= DA</b>        | C (Digital-to-An  | alog Converte  | r) <sup>(2)</sup>            |                 |                                    |              |

|              | 11111 <b>= FV</b>        | R (Fixed Voltage  | e Reference) E | Buffer 1 Output <sup>(</sup> | 3)              |                                    |              |

| bit 1        | GO/DONE:                 | ADC Conversio     | n Status bit   |                              |                 |                                    |              |

|              |                          | nversion cycle ir |                |                              |                 | nversion cycle.<br>sion has comple | ated         |

|              |                          | version comple    | -              |                              |                 | sion has comple                    | ieu.         |

| bit 0        | ADON: ADO                | -                 |                | 9.000                        |                 |                                    |              |

|              | 1 = ADC is e             |                   |                |                              |                 |                                    |              |

|              |                          | disabled and co   | nsumes no op   | erating current              |                 |                                    |              |

| Note 1:      | See Section 15.          | 0 "Temperature    | e Indicator Mo | dule" for more               | information.    |                                    |              |

| 2:           | See Section 17.          | 0 "5-Bit Digital  | -to-Analog Co  | onverter (DAC)               | Module" for r   | more information                   | า.           |

| 3:           | See Section 14.          | 0 "Fixed Voltag   | e Reference    | (FVR)" for more              | e information.  |                                    |              |

| 4:           | Available on PIC         | 16(L)F1578/9 de   | evices only.   |                              |                 |                                    |              |

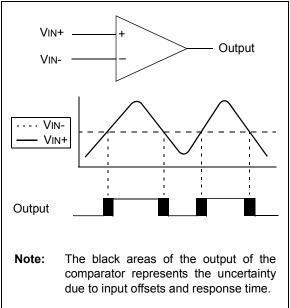

#### FIGURE 18-2: SINGLE COMPARATOR

# 18.2 Comparator Control

The comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- Output selection

- Output polarity

- Speed/Power selection

- Hysteresis enable

- · Output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR POSITIVE INPUT SELECTION

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC1\_output

- FVR\_buffer2

- Vss

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

# 18.2.3 COMPARATOR NEGATIVE INPUT SELECTION

The CxNCH<2:0> bits of the CMxCON0 register direct one of the input sources to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog<br>input, the appropriate bits must be set in<br>the ANSEL register and the correspond- |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

|       | ing TRIS bits must also be set to disable                                                                                      |

|       | the output drivers.                                                                                                            |

## 18.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

The synchronous comparator output signal (CxOUT\_sync) is available to the following peripheral(s):

- Analog-to-Digital Converter (ADC)

- Timer1

The asynchronous comparator output signal (CxOUT\_async) is available to the following peripheral(s):

Complementary Waveform Generator (CWG)

Note: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

| R/W-0/u                 | R/W-0/u                        | R/W-0/u                            | R/W-0/u         | R/W/HC-0/u                         | R-x/x                           | R/W-0/u  | R/W-0/u      |  |  |  |  |

|-------------------------|--------------------------------|------------------------------------|-----------------|------------------------------------|---------------------------------|----------|--------------|--|--|--|--|

| TMR1GE                  | T1GPOL                         | T1GTM                              | T1GSPM          | T1GGO/<br>DONE                     | T1GVAL                          | T1GS     | S<1:0>       |  |  |  |  |

| bit 7                   |                                | •                                  |                 |                                    |                                 |          |              |  |  |  |  |

|                         |                                |                                    |                 |                                    |                                 |          |              |  |  |  |  |

| Legend:<br>R = Readable | - hit                          | W = Writable                       | hit             |                                    | opted bit read                  | 1 00 '0' |              |  |  |  |  |

| u = Bit is unc          |                                | x = Bit is unkl                    |                 | •                                  | ented bit, read<br>t POR and BO |          | other Pecets |  |  |  |  |

| '1' = Bit is set        | 0                              | 0' = Bit is cle                    |                 |                                    | ared by hardw                   |          |              |  |  |  |  |

|                         | •                              |                                    |                 |                                    |                                 |          |              |  |  |  |  |

| bit 7                   | TMR1GE: Ti                     | mer1 Gate Ena                      | ble bit         |                                    |                                 |          |              |  |  |  |  |

|                         | If TMR1ON =                    |                                    |                 |                                    |                                 |          |              |  |  |  |  |

|                         | This bit is ign<br>If TMR1ON = |                                    |                 |                                    |                                 |          |              |  |  |  |  |

|                         |                                |                                    | rolled by the T | imer1 gate func                    | tion                            |          |              |  |  |  |  |

|                         | 0 = Timer1 c                   | counts regardle                    | ss of Timer1 g  | ate function                       |                                 |          |              |  |  |  |  |

| bit 6                   |                                | mer1 Gate Pola                     | •               |                                    |                                 |          |              |  |  |  |  |

|                         |                                |                                    |                 | unts when gate<br>nts when gate is |                                 |          |              |  |  |  |  |

| bit 5                   | -                              | er1 Gate Toggl                     | •               | nts when gate is                   | 5 10 10                         |          |              |  |  |  |  |

|                         |                                | Gate Toggle mo                     |                 |                                    |                                 |          |              |  |  |  |  |

|                         | 0 = Timer1 (                   | Gate Toggle mo                     | de is disabled  | and toggle flip-                   | flop is cleared                 |          |              |  |  |  |  |

| 1.11 A                  | -                              | flip-flop toggles                  | -               |                                    |                                 |          |              |  |  |  |  |

| bit 4                   |                                | mer1 Gate Sing                     | •               | e bit<br>abled and is cor          | trolling Timor1                 | aata     |              |  |  |  |  |

|                         |                                | gate Single-Pul                    |                 |                                    |                                 | yale     |              |  |  |  |  |

| bit 3                   | T1GGO/DOM                      | NE: Timer1 Gat                     | e Single-Pulse  | Acquisition Sta                    | tus bit                         |          |              |  |  |  |  |

|                         |                                |                                    |                 | s ready, waiting                   |                                 |          |              |  |  |  |  |

| <b>h</b> # 0            | -                              | • • •                              | •               | as completed o                     | r has not been                  | started  |              |  |  |  |  |

| bit 2                   |                                | ner1 Gate Valu                     |                 | ate that could be                  | a provided to T                 |          |              |  |  |  |  |

|                         |                                | y Timer1 Gate                      |                 |                                    |                                 |          |              |  |  |  |  |

| bit 1-0                 | T1GSS<1:0>                     | : Timer1 Gate                      | Source Select   | bits                               |                                 |          |              |  |  |  |  |

|                         |                                |                                    |                 | d output (C2OU                     |                                 |          |              |  |  |  |  |

|                         |                                | rator 1 optional<br>overflow outpu |                 | d output (C1OU                     | II_sync)                        |          |              |  |  |  |  |

|                         | 00 = Timer0                    | overnow outpu                      |                 | /                                  |                                 |          |              |  |  |  |  |

# REGISTER 20-2: T1GCON: TIMER1 GATE CONTROL REGISTER

| Name    | Bit 7                         | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |  |

|---------|-------------------------------|-----------|--------|-------|-------|--------|--------|--------|---------------------|--|--|

| BAUDCON | ABDOVF                        | RCIDL     | —      | SCKP  | BRG16 | —      | WUE    | ABDEN  | 204                 |  |  |

| INTCON  | GIE                           | PEIE      | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |  |  |

| PIE1    | TMR1GIE                       | ADIE      | RCIE   | TXIE  | —     | _      | TMR2IE | TMR1IE | 87                  |  |  |

| PIR1    | TMR1GIF                       | ADIF      | RCIF   | TXIF  | —     | —      | TMR2IF | TMR1IF | 90                  |  |  |

| RCSTA   | SPEN                          | RX9       | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 203*                |  |  |

| SPBRGL  |                               |           |        | BRG   | <7:0> |        |        |        | 205*                |  |  |

| SPBRGH  |                               | BRG<15:8> |        |       |       |        |        |        |                     |  |  |

| TXREG   | EUSART Transmit Data Register |           |        |       |       |        |        |        |                     |  |  |

| TXSTA   | CSRC                          | TX9       | TXEN   | SYNC  | SENDB | BRGH   | TRMT   | TX9D   | 202                 |  |  |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous transmission.

\* Page provides register information.

#### 22.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 22-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 22.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

# 22.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 22.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional<br>characters will be received until the overrun |  |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | condition is cleared. See Section                                                              |  |  |  |  |  |  |  |  |  |  |

|       | 22.1.2.5 "Receive Overrun Error" for                                                           |  |  |  |  |  |  |  |  |  |  |

|       | more information on overrun errors.                                                            |  |  |  |  |  |  |  |  |  |  |

# 22.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

|             |                   |            |                             |                   | SYNC       | <b>C =</b> 0, <b>BRG</b>    | I = 0, BRG        | <b>616 =</b> 0 |                             |                |                    |                             |  |

|-------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD        | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 16.000 MHz |                |                             | Fosc           | Fosc = 11.0592 MHz |                             |  |

| <b>RATE</b> | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300         | _                 | _          | _                           | _                 |            | _                           | _                 |                | _                           | _              |                    |                             |  |

| 1200        | 1221              | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1202              | 0.16           | 207                         | 1200           | 0.00               | 143                         |  |

| 2400        | 2404              | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2404              | 0.16           | 103                         | 2400           | 0.00               | 71                          |  |

| 9600        | 9470              | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9615              | 0.16           | 25                          | 9600           | 0.00               | 17                          |  |

| 10417       | 10417             | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10417             | 0.00           | 23                          | 10165          | -2.42              | 16                          |  |

| 19.2k       | 19.53k            | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.23k            | 0.16           | 12                          | 19.20k         | 0.00               | 8                           |  |

| 57.6k       | —                 | —          | _                           | 57.60k            | 0.00       | 7                           | —                 | —              | _                           | 57.60k         | 0.00               | 2                           |  |

| 115.2k      | —                 | _          | _                           | _                 | _          | _                           | _                 | _              | _                           | _              | _                  | —                           |  |

#### TABLE 22-5:BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  |            |                             |                  | SYNC       | <b>C =</b> 0, <b>BRG</b>    | I = 0, BRG     | <b>616 =</b> 0 |                             | _              |            |                             |

|--------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            |                             | Fosc = 4.000 MHz |            |                             | Fosc           | : = 3.686      | 4 MHz                       | Fos            | c = 1.000  | ) MHz                       |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                |            | _                           | 300              | 0.16       | 207                         | 300            | 0.00           | 191                         | 300            | 0.16       | 51                          |

| 1200   | 1202             | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200           | 0.00           | 47                          | 1202           | 0.16       | 12                          |

| 2400   | 2404             | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400           | 0.00           | 23                          | —              | —          | —                           |

| 9600   | 9615             | 0.16       | 12                          | _                | _          | —                           | 9600           | 0.00           | 5                           | —              | _          | —                           |

| 10417  | 10417            | 0.00       | 11                          | 10417            | 0.00       | 5                           | —              | _              | _                           | —              | _          | _                           |

| 19.2k  | —                | _          | _                           | _                | _          | _                           | 19.20k         | 0.00           | 2                           | —              | _          | _                           |

| 57.6k  | —                | —          | —                           | —                | —          | —                           | 57.60k         | 0.00           | 0                           | —              | —          | —                           |

| 115.2k | —                | —          | _                           | _                | —          | _                           | —              | —              | _                           | —              | —          | —                           |

|        |                   |            |                             |                | SYNC       | <b>=</b> 0, BRGH            | l = 1, BRO     | <b>616 =</b> 0 |                             |                |            |                             |

|--------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz |            |                             | Foso           | = 18.43    | 2 MHz                       | Foso           | = 16.00        | 0 MHz                       | Fosc           | = 11.059   | 92 MHz                      |

|        | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                 | _          | _                           |                | _          | _                           |                | _              | _                           |                | _          | _                           |

| 1200   | _                 | _          | _                           | —              | _          | _                           | _              | _              | _                           | _              | _          | _                           |

| 2400   | _                 | _          | _                           | _              | _          | _                           | _              | _              | _                           | _              | _          | _                           |

| 9600   | 9615              | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9615           | 0.16           | 103                         | 9600           | 0.00       | 71                          |

| 10417  | 10417             | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10417          | 0.00           | 95                          | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k            | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.23k         | 0.16           | 51                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 56.82k            | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 58.82k         | 2.12           | 16                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 113.64k           | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 111.1k         | -3.55          | 8                           | 115.2k         | 0.00       | 5                           |

|        |                |            |                             | SYNC = 0       | , BRGH     | = 1, BRG16                  | 6 = 1 or SY    | 'NC = 1,   | BRG16 = 1                   |                |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Foso           | : = 20.00  | 0 MHz                       | Fosc           | = 18.43    | 2 MHz                       | Fosc           | : = 16.00  | 0 MHz                       | Fosc           | = 11.059   | 92 MHz                      |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00       | 16665                       | 300.0          | 0.00       | 15359                       | 300.0          | 0.00       | 13332                       | 300.0          | 0.00       | 9215                        |

| 1200   | 1200           | -0.01      | 4166                        | 1200           | 0.00       | 3839                        | 1200.1         | 0.01       | 3332                        | 1200           | 0.00       | 2303                        |

| 2400   | 2400           | 0.02       | 2082                        | 2400           | 0.00       | 1919                        | 2399.5         | -0.02      | 1666                        | 2400           | 0.00       | 1151                        |

| 9600   | 9597           | -0.03      | 520                         | 9600           | 0.00       | 479                         | 9592           | -0.08      | 416                         | 9600           | 0.00       | 287                         |

| 10417  | 10417          | 0.00       | 479                         | 10425          | 0.08       | 441                         | 10417          | 0.00       | 383                         | 10433          | 0.16       | 264                         |

| 19.2k  | 19.23k         | 0.16       | 259                         | 19.20k         | 0.00       | 239                         | 19.23k         | 0.16       | 207                         | 19.20k         | 0.00       | 143                         |

| 57.6k  | 57.47k         | -0.22      | 86                          | 57.60k         | 0.00       | 79                          | 57.97k         | 0.64       | 68                          | 57.60k         | 0.00       | 47                          |

| 115.2k | 116.3k         | 0.94       | 42                          | 115.2k         | 0.00       | 39                          | 114.29k        | -0.79      | 34                          | 115.2k         | 0.00       | 23                          |

# TABLE 22-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                  |            |                             |                |            |                             |                  |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz                                     |            |                             | Fosc = 4.000 MHz |            |                             | Fosc           | = 3.686    | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 6666                        | 300.0            | 0.01       | 3332                        | 300.0          | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200                                                 | -0.02      | 1666                        | 1200             | 0.04       | 832                         | 1200           | 0.00       | 767                         | 1202             | 0.16       | 207                         |

| 2400   | 2401                                                 | 0.04       | 832                         | 2398             | 0.08       | 416                         | 2400           | 0.00       | 383                         | 2404             | 0.16       | 103                         |

| 9600   | 9615                                                 | 0.16       | 207                         | 9615             | 0.16       | 103                         | 9600           | 0.00       | 95                          | 9615             | 0.16       | 25                          |

| 10417  | 10417                                                | 0          | 191                         | 10417            | 0.00       | 95                          | 10473          | 0.53       | 87                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k                                               | 0.16       | 103                         | 19.23k           | 0.16       | 51                          | 19.20k         | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 57.14k                                               | -0.79      | 34                          | 58.82k           | 2.12       | 16                          | 57.60k         | 0.00       | 15                          | —                | _          | _                           |

| 115.2k | 117.6k                                               | 2.12       | 16                          | 111.1k           | -3.55      | 8                           | 115.2k         | 0.00       | 7                           | —                | _          | —                           |

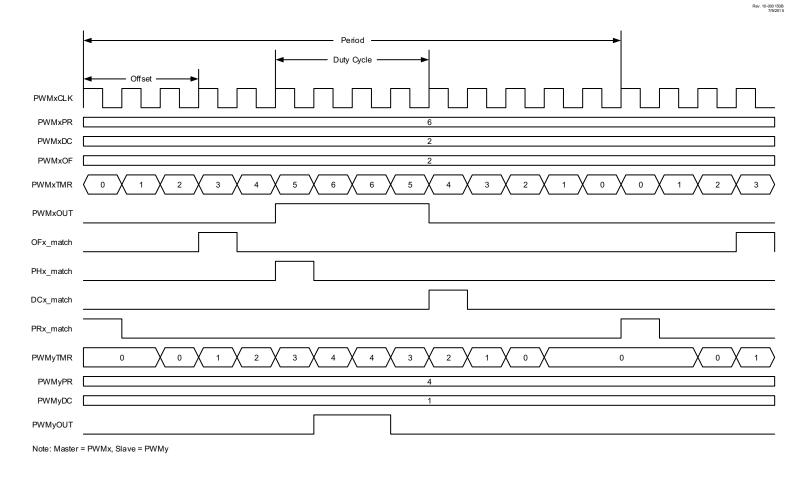

# FIGURE 23-12: OFFSET MATCH ON INCREMENTING TIMER TIMING DIAGRAM

PIC16(L)F1574/5/8/9

|                    | R/W-0/0                                                                                                                            | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0/0                                              | U-0                                         | U-0              | R/W-0/0        | R/W-0/0      |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------|------------------|----------------|--------------|--|--|--|

| — OFM<1:0>         |                                                                                                                                    | OFO <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OFO <sup>(1)</sup> —                                 |                                             | OFS              | OFS<1:0>       |              |  |  |  |

| bit 7              |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                             |                  |                | bit C        |  |  |  |