Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1575-e-st |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-3**: PIC16(L)F1578/9 PINOUT DESCRIPTION (CONTINUED)

| Name                      | Function          | Input<br>Type | Output<br>Type | Description                                          |

|---------------------------|-------------------|---------------|----------------|------------------------------------------------------|

| RC1/AN5/C1IN1-/C2IN1-     | RC1               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

|                           | AN5               | AN            | _              | ADC Channel input.                                   |

|                           | C1IN1-            | AN            | _              | Comparator negative input.                           |

|                           | C2IN1-            | AN            | _              | Comparator negative input.                           |

| RC2/AN6/C1IN2-/C2IN2-     | RC2               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

|                           | AN6               | AN            | _              | ADC Channel input.                                   |

|                           | C1IN2-            | AN            | _              | Comparator negative input.                           |

|                           | C2IN2-            | AN            | _              | Comparator negative input.                           |

| RC3/AN7/C1IN3-/C2IN3-     | RC3               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

|                           | AN7               | AN            | _              | ADC Channel input.                                   |

|                           | C1IN3-            | AN            | _              | Comparator negative input.                           |

|                           | C2IN3-            | AN            | _              | Comparator negative input.                           |

| RC4/ADCACT <sup>(1)</sup> | RC4               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

|                           | ADCACT            | TTL/ST        | _              | ADC Auto-conversion Trigger input.                   |

| RC5                       | RC5               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

| OUT <sup>(2)</sup>        | C1OUT             | —             | CMOS           | Comparator output.                                   |

|                           | C2OUT             | —             | CMOS           | Comparator output.                                   |

|                           | PWM10UT           | _             | CMOS           | PWM1 output.                                         |

|                           | PWM2OUT           | —             | CMOS           | PWM2 output.                                         |

|                           | PWM3OUT           | _             | CMOS           | PWM3 output.                                         |

|                           | PWM4OUT           | _             | CMOS           | PWM4 output.                                         |

|                           | CWG1A             | _             | CMOS           | Complementary Output Generator Output A.             |

|                           | CWG1B             | _             | CMOS           | Complementary Output Generator Output B.             |

|                           | TX/CK             | —             | CMOS           | USART asynchronous TX data/synchronous clock output. |

|                           | DT <sup>(3)</sup> | —             | CMOS           | USART synchronous data output.                       |

| Vdd                       | Vdd               | Power         | —              | Positive supply.                                     |

| Vss                       | Vss               | Power         | —              | Ground reference.                                    |

Open-Drain Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C Schmitt Trigger input with I<sup>2</sup>C = HV = High Voltage

XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-1.

3: These USART functions are bidirectional. The output pin selections must be the same as the input pin selections.

## 4.2 Register Definitions: Configuration Words

#### R/P-1 U-1 U-1 R/P-1 R/P-1 U-1 BOREN<1:0>(1) CLKOUTEN bit 13 bit 8 R/P-1 R/P-1 R/P-1 **R/P-1 R/P-1 R/P-1** U-1 R/P-1 CP(2) PWRTE<sup>(1)</sup> MCLRE WDTE<1:0> FOSC<1:0> bit 7 bit 0 Legend: R = Readable bit P = Programmable bit U = Unimplemented bit, read as '1' '0' = Bit is cleared '1' = Bit is set n = Value when blank or after Bulk Erase bit 13-12 Unimplemented: Read as '1' bit 11 **CLKOUTEN:** Clock Out Enable bit 1 = OFF - CLKOUT function is disabled. I/O or oscillator function on CLKOUT pin 0 = ON - CLKOUT function is enabled on CLKOUT pin bit 10-9 BOREN<1:0>: Brown-out Reset Enable bits<sup>(1)</sup> - Brown-out Reset enabled. The SBOREN bit is ignored. 11 = ON 10 = SLEEP - Brown-out Reset enabled while running and disabled in Sleep. The SBOREN bit is ignored. 01 = SBODEN- Brown-out Reset controlled by the SBOREN bit in the BORCON register 00 = OFF- Brown-out Reset disabled. The SBOREN bit is ignored. bit 8 Unimplemented: Read as '1' CP: Flash Program Memory Code Protection bit<sup>(2)</sup> bit 7 1 = OFF – Code protection off. Program Memory can be read and written. 0 = ON - Code protection on. Program Memory cannot be read or written externally. bit 6 MCLRE: MCLR/VPP Pin Function Select bit If LVP bit = 1 (ON): This bit is ignored. MCLR/VPP pin function is MCLR; Weak pull-up enabled. If LVP bit = 0 (OFF): $1 = ON - \overline{MCLR}/VPP$ pin function is $\overline{MCLR}$ ; Weak pull-up enabled. 0 = OFF – MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of pin's WPU control bit. **PWRTE:** Power-up Timer Enable bit<sup>(1)</sup> bit 5 1 = OFF-PWRT disabled 0 = ON - PWRT enabled WDTE<1:0>: Watchdog Timer Enable bit bit 4-3 - WDT enabled. SWDTEN is ignored. 11 = ON 10 = SLEEP - WDT enabled while running and disabled in Sleep. SWDTEN is ignored. 01 = SWDTEN-WDT controlled by the SWDTEN bit in the WDTCON register 00 = OFF - WDT disabled. SWDTEN is ignored. bit 2 Unimplemented: Read as '1' bit 1-0 FOSC<1:0>: Oscillator Selection bits 11 = ECH - External Clock, High-Power mode: CLKI on CLKI - External Clock, Medium Power mode: CLKI on CLKI 10 = ECM01 = ECL- External Clock, Low-Power mode: CLKI on CLKI 00 = INTOSC-I/O function on CLKI Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer. Once enabled, code-protect can only be disabled by bulk erasing the device. 2:

## **REGISTER 4-1: CONFIGURATION WORD 1**

| U-0              | R-0/q                                                                                                                                        | R-q/q                                                                                                                                                        | R-0/q             | R-0/q           | R-q/q            | R-0/q            | R-0/q        |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|------------------|------------------|--------------|--|--|--|--|

| —                | PLLR                                                                                                                                         | OSTS                                                                                                                                                         | HFIOFR            | HFIOFL          | MFIOFR           | LFIOFR           | HFIOFS       |  |  |  |  |

| bit 7            |                                                                                                                                              |                                                                                                                                                              |                   |                 |                  |                  | bit C        |  |  |  |  |

|                  |                                                                                                                                              |                                                                                                                                                              |                   |                 |                  |                  |              |  |  |  |  |

| Legend:          |                                                                                                                                              |                                                                                                                                                              |                   |                 |                  |                  |              |  |  |  |  |

| R = Readable     | e bit                                                                                                                                        | W = Writable                                                                                                                                                 | bit               | U = Unimpler    | nented bit, reac | l as '0'         |              |  |  |  |  |

| u = Bit is unc   | hanged                                                                                                                                       | x = Bit is unkr                                                                                                                                              | nown              | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is set | t                                                                                                                                            | '0' = Bit is cle                                                                                                                                             | ared              | q = Condition   | al               |                  |              |  |  |  |  |

|                  |                                                                                                                                              |                                                                                                                                                              |                   |                 |                  |                  |              |  |  |  |  |

| bit 7            | •                                                                                                                                            | ted: Read as '                                                                                                                                               | 0'                |                 |                  |                  |              |  |  |  |  |

| bit 6            | PLLR 4x PLL                                                                                                                                  | •                                                                                                                                                            |                   |                 |                  |                  |              |  |  |  |  |

|                  | 1 = 4x PLL i<br>0 = 4x PLL i                                                                                                                 |                                                                                                                                                              |                   |                 |                  |                  |              |  |  |  |  |

| bit 5            |                                                                                                                                              | •                                                                                                                                                            | mer Status hit    |                 |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                              | <ul> <li>STS: Oscillator Start-up Timer Status bit</li> <li>Running from the clock defined by the FOSC&lt;1:0&gt; bits of the Configuration Words</li> </ul> |                   |                 |                  |                  |              |  |  |  |  |

|                  | 0 = Running from an internal oscillator (FOSC<1:0> bits of the Comparation Words<br>0 = Running from an internal oscillator (FOSC<1:0> = 00) |                                                                                                                                                              |                   |                 |                  |                  |              |  |  |  |  |

| bit 4            | HFIOFR: Hig                                                                                                                                  | h-Frequency Ir                                                                                                                                               | iternal Oscillate | or Ready bit    |                  |                  |              |  |  |  |  |

|                  | 1 = HFINTO                                                                                                                                   |                                                                                                                                                              |                   |                 |                  |                  |              |  |  |  |  |

|                  | 0 = HFINTO                                                                                                                                   | SC is not ready                                                                                                                                              | 1                 |                 |                  |                  |              |  |  |  |  |

| bit 3            | •                                                                                                                                            | h-Frequency In                                                                                                                                               |                   | or Locked bit   |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                              | 1 = HFINTOSC is at least 2% accurate<br>0 = HFINTOSC is not 2% accurate                                                                                      |                   |                 |                  |                  |              |  |  |  |  |

| bit 2            |                                                                                                                                              |                                                                                                                                                              |                   | illator Poady b | i+               |                  |              |  |  |  |  |

|                  | 1 = MFINTO                                                                                                                                   | dium-Frequend                                                                                                                                                | y memai Osc       | illator Ready D | it.              |                  |              |  |  |  |  |

|                  |                                                                                                                                              | SC is not read                                                                                                                                               | /                 |                 |                  |                  |              |  |  |  |  |

| bit 1            | LFIOFR: Low                                                                                                                                  | : Low-Frequency Internal Oscillator Ready bit                                                                                                                |                   |                 |                  |                  |              |  |  |  |  |

|                  | 1 = LFINTOS                                                                                                                                  | SC is ready                                                                                                                                                  |                   | -               |                  |                  |              |  |  |  |  |

|                  | 0 = LFINTOS                                                                                                                                  | SC is not ready                                                                                                                                              |                   |                 |                  |                  |              |  |  |  |  |

| bit 0            | HFIOFS: Hig                                                                                                                                  | h-Frequency Ir                                                                                                                                               | ternal Oscillato  | or Stable bit   |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                              | SC is at least 0                                                                                                                                             |                   |                 |                  |                  |              |  |  |  |  |

|                  | 0 = HFINTO                                                                                                                                   | SC is not 0.5%                                                                                                                                               | accurate          |                 |                  |                  |              |  |  |  |  |

## REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

## 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

## 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- · BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 1.0        | 37     | Awake       | Active   | Waits for BOR ready (BORRDY = 1)                                    |

| 10         | Х      | Sleep       | Disabled |                                                                     |

| 0.1        | 1      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 01         | 0      | х           | Disabled | Begins immediately (BORRDY = x)                                     |

| 00         | Х      | Х           | Disabled |                                                                     |

#### TABLE 6-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

## 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

## 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

## 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

## 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | х  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is set on POR                                         |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

## TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

## TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

# 9.6 Register Definitions: Watchdog Control

| U-0             | U-0                                  | R/W-0/0                                                                                                  | R/W-1/1        | R/W-0/0           | R/W-1/1        | R/W-1/1  | R/W-0/0      |  |  |  |  |

|-----------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|----------------|-------------------|----------------|----------|--------------|--|--|--|--|

| _               | —                                    |                                                                                                          |                | WDTPS<4:0>        |                |          | SWDTEN       |  |  |  |  |

| oit 7           |                                      |                                                                                                          |                |                   |                |          | bit (        |  |  |  |  |

| .egend:         |                                      |                                                                                                          |                |                   |                |          |              |  |  |  |  |

| R = Readable    | e bit                                | W = Writable                                                                                             | bit            | U = Unimpleme     | ented bit, rea | d as '0' |              |  |  |  |  |

| ı = Bit is unc  |                                      | x = Bit is unkr                                                                                          | nown           | -n/n = Value at   |                |          | other Resets |  |  |  |  |

| 1' = Bit is set | •                                    | '0' = Bit is clea                                                                                        | ared           |                   |                |          |              |  |  |  |  |

|                 |                                      |                                                                                                          |                |                   |                |          |              |  |  |  |  |

| it 7-6          | -                                    | <b>nted:</b> Read as '<br><b>)&gt;:</b> Watchdog Ti                                                      |                | alaat hita(1)     |                |          |              |  |  |  |  |

| oit 5-1         |                                      | -                                                                                                        | Ther Period S  | elect bits, ,     |                |          |              |  |  |  |  |

|                 |                                      | Prescale Rate                                                                                            |                | interval (1:22)   |                |          |              |  |  |  |  |

|                 | 11111 = R                            | eserved. Results                                                                                         |                | intervar (1.52)   |                |          |              |  |  |  |  |

|                 | •                                    |                                                                                                          |                |                   |                |          |              |  |  |  |  |

|                 | •                                    |                                                                                                          |                |                   |                |          |              |  |  |  |  |

|                 | 10011 = R                            | eserved. Results                                                                                         | s in minimum   | interval (1:32)   |                |          |              |  |  |  |  |

|                 | 10010 = <b>1</b> :                   | 010 = 1:8388608 (2 <sup>23</sup> ) (Interval 256s nominal)                                               |                |                   |                |          |              |  |  |  |  |

|                 | 10001 = <b>1</b> :                   | 1194304 (2 <sup>22</sup> ) (Interval 128s nominal)                                                       |                |                   |                |          |              |  |  |  |  |

|                 | 10000 = <b>1</b> :                   | :2097152 (2 <sup>21</sup> ) (Interval 64s nominal)<br>:1048576 (2 <sup>20</sup> ) (Interval 32s nominal) |                |                   |                |          |              |  |  |  |  |

|                 | 01111 <b>= 1</b> :                   | 1048576 (2 <sup>20</sup> ) (Interval 32s nominal)<br>524288 (2 <sup>19</sup> ) (Interval 16s nominal)    |                |                   |                |          |              |  |  |  |  |

|                 | 01110 = 1:                           | 524288 (2 <sup>19</sup> ) (In                                                                            | iterval 16s no | ominal)           |                |          |              |  |  |  |  |

|                 |                                      | 262144 (2 <sup>18</sup> ) (In<br>131072 (2 <sup>17</sup> ) (In                                           |                |                   |                |          |              |  |  |  |  |

|                 |                                      | 65536 (Interval                                                                                          |                | ,                 |                |          |              |  |  |  |  |

|                 |                                      |                                                                                                          |                |                   |                |          |              |  |  |  |  |

|                 |                                      | 010 = 1:32768 (Interval 1s nominal)<br>001 = 1:16384 (Interval 512 ms nominal)                           |                |                   |                |          |              |  |  |  |  |

|                 |                                      | $p_0 = 1:8192$ (Interval 256 ms nominal)                                                                 |                |                   |                |          |              |  |  |  |  |

|                 |                                      | 4096 (Interval 1                                                                                         |                |                   |                |          |              |  |  |  |  |

|                 |                                      | 2048 (Interval 6                                                                                         |                |                   |                |          |              |  |  |  |  |

|                 |                                      | 1024 (Interval 3                                                                                         |                | ·                 |                |          |              |  |  |  |  |

|                 |                                      | 512 (Interval 16<br>256 (Interval 8 r                                                                    |                |                   |                |          |              |  |  |  |  |

|                 |                                      | 128 (Interval 4 r                                                                                        |                |                   |                |          |              |  |  |  |  |

|                 |                                      | 64 (Interval 2 m                                                                                         | ,              |                   |                |          |              |  |  |  |  |

|                 |                                      | 32 (Interval 1 m                                                                                         | ,              |                   |                |          |              |  |  |  |  |

| oit O           | SWDTEN: S                            | Software Enable/                                                                                         | Disable for V  | Vatchdog Timer bi | it             |          |              |  |  |  |  |

|                 | <u>If WDTE&lt;1:</u> (               | )> = 1x:                                                                                                 |                | ·                 |                |          |              |  |  |  |  |

|                 | This bit is ig                       | nored.                                                                                                   |                |                   |                |          |              |  |  |  |  |

|                 | If WDTE<1:                           |                                                                                                          |                |                   |                |          |              |  |  |  |  |

|                 | 1 = WDT is                           |                                                                                                          |                |                   |                |          |              |  |  |  |  |

|                 | 0 = WDT is<br><u>If WDTE&lt;1:</u> ( |                                                                                                          |                |                   |                |          |              |  |  |  |  |

|                 |                                      |                                                                                                          |                |                   |                |          |              |  |  |  |  |

## REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

© 2016 Microchip Technology Inc.

#### 11.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information. Analog input functions, such as ADC inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when it is in Analog mode.

| Peripheral | Conditions                                                        | Description                                                        |

|------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 010 and<br>IRCF<3:0> = 000x                           | INTOSC is active and device is not in Sleep.                       |

|            | BOREN<1:0> = 11                                                   | BOR always enabled.                                                |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                     | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                                     | BOR under software control, BOR Fast Start enabled.                |

| LDO        | All PIC16F1574/5/8/9 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the Low-Power Regulator when in Sleep mode. |

# TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

#### **Register Definitions: ADC Control** 16.3

## REGISTER 16-1: ADCON0: ADC CONTROL REGISTER 0

| U-0          | R/W-0/0                  | R/W-0/0           | R/W-0/0        | R/W-0/0                      | R/W-0/0         | R/W-0/0                            | R/W-0/0      |  |  |  |  |

|--------------|--------------------------|-------------------|----------------|------------------------------|-----------------|------------------------------------|--------------|--|--|--|--|

| _            |                          |                   | CHS<4:0>       |                              |                 | GO/DONE                            | ADON         |  |  |  |  |

| oit 7        |                          |                   |                |                              |                 |                                    | bit C        |  |  |  |  |

|              |                          |                   |                |                              |                 |                                    |              |  |  |  |  |

| Legend:      |                          |                   |                |                              |                 |                                    |              |  |  |  |  |

| R = Read     | lable bit                | W = Writable      | bit            | •                            | nented bit, rea |                                    |              |  |  |  |  |

|              | unchanged                | x = Bit is unki   |                | -n/n = Value a               | at POR and B    | OR/Value at all o                  | other Resets |  |  |  |  |

| '1' = Bit is | set                      | '0' = Bit is cle  | ared           |                              |                 |                                    |              |  |  |  |  |

| bit 7        | Unimpleme                | nted: Read as '   | 0'             |                              |                 |                                    |              |  |  |  |  |

| bit 6-2      | CHS<4:0>:                | Analog Channe     | I Select bits  |                              |                 |                                    |              |  |  |  |  |

|              | 00000 = AN               | 10                |                |                              |                 |                                    |              |  |  |  |  |

|              | 00001 = AN               | J1                |                |                              |                 |                                    |              |  |  |  |  |

|              | 00010 = AN               |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | 00011 = AN<br>00100 = AN |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | 00101 = AN               |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | 00110 = AN               | 00110 = AN6       |                |                              |                 |                                    |              |  |  |  |  |

|              | 00111 = AN               |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | 01000 = AN<br>01001 = AN |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | 01001 = AN<br>01010 = AN |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | 01010 = AN               |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | 01100 = Re               | served. No cha    | nnel connecte  | d.                           |                 |                                    |              |  |  |  |  |

|              | •                        |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | •                        |                   |                |                              |                 |                                    |              |  |  |  |  |

|              | •<br>11100 - Do          | served. No cha    | nnol connocto  | d                            |                 |                                    |              |  |  |  |  |

|              |                          | nperature Indica  |                | u.                           |                 |                                    |              |  |  |  |  |

|              | 11110 <b>= DA</b>        | C (Digital-to-An  | alog Converte  | r) <sup>(2)</sup>            |                 |                                    |              |  |  |  |  |

|              | 11111 <b>= FV</b>        | R (Fixed Voltage  | e Reference) E | Buffer 1 Output <sup>(</sup> | 3)              |                                    |              |  |  |  |  |

| bit 1        | GO/DONE:                 | ADC Conversio     | n Status bit   |                              |                 |                                    |              |  |  |  |  |

|              |                          | nversion cycle ir |                |                              |                 | nversion cycle.<br>sion has comple | ated         |  |  |  |  |

|              |                          | version comple    | -              |                              |                 | sion has comple                    | ieu.         |  |  |  |  |

| bit 0        | ADON: ADO                | -                 |                | 9.000                        |                 |                                    |              |  |  |  |  |

|              | 1 = ADC is e             |                   |                |                              |                 |                                    |              |  |  |  |  |

|              |                          | disabled and co   | nsumes no op   | erating current              |                 |                                    |              |  |  |  |  |

| Note 1:      | See Section 15.          | 0 "Temperature    | e Indicator Mo | dule" for more               | information.    |                                    |              |  |  |  |  |

| 2:           | See Section 17.          | 0 "5-Bit Digital  | -to-Analog Co  | onverter (DAC)               | Module" for r   | more information                   | า.           |  |  |  |  |

| 3:           | See Section 14.          | 0 "Fixed Voltag   | e Reference    | (FVR)" for more              | e information.  |                                    |              |  |  |  |  |

| 4:           | Available on PIC         | 16(L)F1578/9 de   | evices only.   |                              |                 |                                    |              |  |  |  |  |

| R/W-x/u          | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u                                  | R/W-x/u | R/W-x/u | R/W-x/u      |  |

|------------------|---------|--------------------|---------|------------------------------------------|---------|---------|--------------|--|

| —                | —       | —                  | _       | —                                        |         | ADRE    | S<9:8>       |  |

| bit 7            |         |                    |         |                                          |         |         | bit 0        |  |

|                  |         |                    |         |                                          |         |         |              |  |

| Legend:          |         |                    |         |                                          |         |         |              |  |

| R = Readable     | bit     | W = Writable       | bit     | U = Unimplemented bit, read as '0'       |         |         |              |  |

| u = Bit is uncha | anged   | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all |         |         | other Resets |  |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                                          |         |         |              |  |

|                  |         |                    |         |                                          |         |         |              |  |

## REGISTER 16-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

bit 7-2 **Reserved**: Do not use.

| bit 1-0 | ADRES<9:8>: ADC Result Register bits       |

|---------|--------------------------------------------|

|         | Upper two bits of 10-bit conversion result |

# REGISTER 16-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|--|--|--|

| ADRES<7:0> |         |         |         |         |         |         |         |  |  |  |  |

| bit 7      |         |         |         |         |         |         | bit 0   |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits Lower eight bits of 10-bit conversion result

## 20.5.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

## 20.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

## 20.5.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 20-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

## 20.5.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/ DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/ DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 20-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 20-6 for timing details.

## 20.5.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 20.5.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

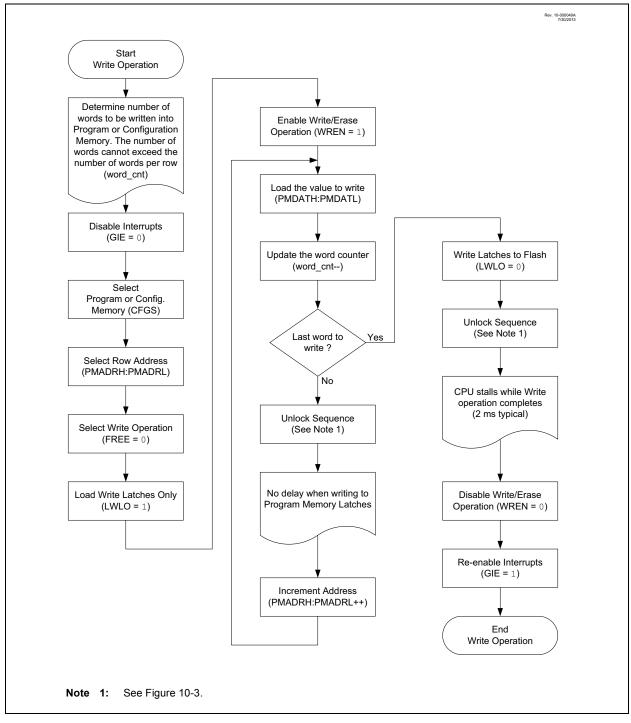

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

| FIGURE 22-12:                                   | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                   |

|-------------------------------------------------|-----------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)         |                                                                             |

| TX/CK pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                             |

| SREN bit                                        | ·0'                                                                         |

| RCIF bit<br>(Interrupt)                         |                                                                             |

| Read<br>RCREG                                   | ŕ                                                                           |

| Note: Timing dia                                | gram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

#### **~**

#### TABLE 22-8: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name    | Bit 7     | Bit 6 | Bit 5  | Bit 4      | Bit 3       | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------|-------|--------|------------|-------------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF    | RCIDL |        | SCKP       | BRG16       | _      | WUE    | ABDEN  | 204                 |

| INTCON  | GIE       | PEIE  | TMR0IE | INTE       | IOCIE       | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1    | TMR1GIE   | ADIE  | RCIE   | TXIE       | —           | _      | TMR2IE | TMR1IE | 87                  |

| PIR1    | TMR1GIF   | ADIF  | RCIF   | TXIF       | —           | _      | TMR2IF | TMR1IF | 90                  |

| RCREG   |           |       | EUS    | ART Receiv | ve Data Reg | gister |        |        | 197*                |

| RCSTA   | SPEN      | RX9   | SREN   | CREN       | ADDEN       | FERR   | OERR   | RX9D   | 203                 |

| SPBRGL  | BRG<7:0>  |       |        |            |             |        |        | 205*   |                     |

| SPBRGH  | BRG<15:8> |       |        |            |             |        |        | 205*   |                     |

| TXSTA   | CSRC      | TX9   | TXEN   | SYNC       | SENDB       | BRGH   | TRMT   | TX9D   | 202                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

Page provides register information. \*

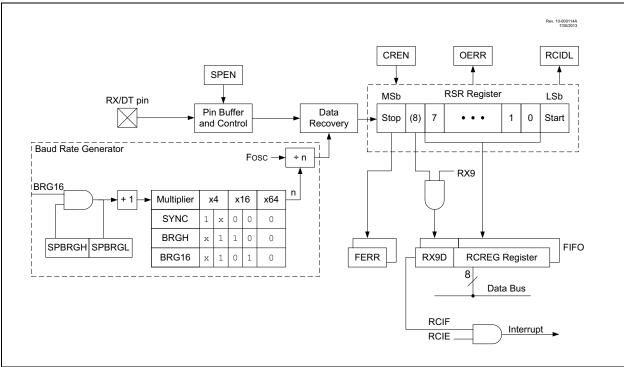

# 23.1 Fundamental Operation

The PWM module produces a 16-bit resolution pulse width modulated output.

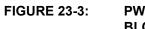

Each PWM module has an independent timer driven by a selection of clock sources determined by the PWMxCLKCON register (Register 23-4). The timer value is compared to event count registers to generate the various events of a the PWM waveform, such as the period and duty cycle. For a block diagram describing the clock sources refer to Figure 23-3.

Each PWM module can be enabled individually using the EN bit of the PWMxCON register, or several PWM modules can be enabled simultaneously using the mirror bits of the PWMEN register.

The current state of the PWM output can be read using the OUT bit of the PWMxCON register. In some modes this bit can be set and cleared by software giving additional software control over the PWM waveform. This bit is synchronized to Fosc/4 and therefore does not change in real time with respect to the PWM\_clock.

| Note: | If PWM_clock > Fosc/4, the OUT bit may       |

|-------|----------------------------------------------|

|       | not accurately represent the output state of |

|       | the PWM.                                     |

PWM CLOCK SOURCE BLOCK DIAGRAM

## 23.1.1 PWMx PIN CONFIGURATION

All PWM outputs are multiplexed with the PORT data latch, so the pins must also be configured as outputs by clearing the associated PORT TRIS bits.

The slew rate feature may be configured to optimize the rate to be used in conjunction with the PWM outputs. High-speed output switching is attained by clearing the associated PORT SLRCON bits.

The PWM outputs can be configured to be open-drain outputs by setting the associated PORT ODCON bits.

23.1.2 PWMx Output Polarity

The output polarity is inverted by setting the POL bit of the PWMxCON register. The polarity control affects the PWM output even when the module is not enabled.

| Note: There          | Note: There are no long and short bit name variants for the following three mirror registers |              |               |                |                   |                   |              |  |

|----------------------|----------------------------------------------------------------------------------------------|--------------|---------------|----------------|-------------------|-------------------|--------------|--|

| REGISTER 23-1        | 7. DWM                                                                                       |              |               |                | ER                |                   |              |  |

|                      |                                                                                              |              |               |                |                   |                   |              |  |

| U-0                  | U-0                                                                                          | U-0          | U-(           | 0 R/W-0/0      | 0 R/W-0/0         | R/W-0/0           | R/W-0/0      |  |

| —                    | _                                                                                            | —            |               | PWM4EN         | A PWM3EN_         | A PWM2EN_A        | PWM1EN_A     |  |

| bit 7                |                                                                                              |              |               |                |                   |                   | bit 0        |  |

|                      |                                                                                              |              |               |                |                   |                   |              |  |

| Legend:              |                                                                                              |              |               |                |                   |                   |              |  |

| R = Readable bit     |                                                                                              | W = Writa    | ble bit       | U = Unimp      | plemented bit, re | ad as '0'         |              |  |

| u = Bit is unchang   | ged                                                                                          | x = Bit is   | unknown       | -n/n = Valu    | ue at POR and B   | OR/Value at all o | other Resets |  |

| '1' = Bit is set     |                                                                                              | '0' = Bit is | cleared       |                |                   |                   |              |  |

|                      |                                                                                              |              |               |                |                   |                   |              |  |

| bit 7-4 Ur           | nimplemen                                                                                    | ted: Read    | <b>as</b> '0' |                |                   |                   |              |  |

| bit 3-0 PV           | VMxEN: PV                                                                                    | VM4/PWM      | 3/PWM2/PW     | M1 Enable bits |                   |                   |              |  |

| Mi                   | rror copy of                                                                                 | EN bits in   | PWMxCON<      | <7>            |                   |                   |              |  |

|                      |                                                                                              |              |               |                |                   |                   |              |  |

| <b>REGISTER 23-1</b> | 8: PWM                                                                                       | LD: LD B     | IT ACCESS     | REGISTER       |                   |                   |              |  |

| U-0                  | U-0                                                                                          | U-0          | U-0           | R/W-0/0        | R/W-0/0           | R/W-0/0           | R/W-0/0      |  |

| _                    | _                                                                                            | —            | _             | PWM4LDA_A      | PWM3LDA_A         | PWM2LDA_A         | PWM1LDA_A    |  |

| bit 7                |                                                                                              |              |               |                |                   |                   | bit 0        |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 **PWMxLDA:** PWM4/PWM3/PWM2/PWM1 LD bits Mirror copy of LD bits in PWMxLDCON<7>

## REGISTER 23-19: PWMOUT: PWMOUT BIT ACCESS REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0   | R/W-0/0   | R/W-0/0   | R/W-0/0   |

|-------|-----|-----|-----|-----------|-----------|-----------|-----------|

| _     | —   | _   | _   | PWM4OUT_A | PWM3OUT_A | PWM2OUT_A | PWM1OUT_A |

| bit 7 |     |     |     |           |           |           | bit 0     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 **PWMxOUT:** PWM4/PWM3/PWM2/PWM1 Output bits Mirror copy of OUT bits in PWMxCON<5>

| RETFIE           | Return from Interrupt                                                                                                                                                                                          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                 |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                           |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                        |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                           |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                              |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                              |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                         |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                         |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                        |

| Operands:        | None                                                                                                                                                  |

| Operation:       | $TOS\toPC$                                                                                                                                            |

| Status Affected: | None                                                                                                                                                  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |

| RETLW            | Return with literal in W                                                                                                           | RLF              | Deteta Left fithrough Correc                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                           |                  | Rotate Left f through Carry                                                                                                                                                       |

| Operands:        | $0 \le k \le 255$                                                                                                                  | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                          |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                       | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                |

| Status Affected: | None                                                                                                                               | Operation:       | See description below                                                                                                                                                             |

| Description:     | The W register is loaded with the 8-bit                                                                                            | Status Affected: | С                                                                                                                                                                                 |

| Description.     | literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is |

| Words:           | 1                                                                                                                                  |                  | stored back in register 'f'.                                                                                                                                                      |

| Cycles:          | 2                                                                                                                                  |                  | - C - Register f                                                                                                                                                                  |

| Example:         | CALL TABLE;W contains table                                                                                                        | Words:           | 1                                                                                                                                                                                 |

|                  | ;offset value<br>• ;W now has table value                                                                                          | Cycles:          | 1                                                                                                                                                                                 |

| TABLE            | •                                                                                                                                  | Example:         | RLF REG1,0                                                                                                                                                                        |

|                  | •                                                                                                                                  |                  | Before Instruction                                                                                                                                                                |

|                  | ADDWF PC ;W = offset<br>RETLW kl ;Begin table                                                                                      |                  | REG1 = 1110 0110                                                                                                                                                                  |

|                  | RETLW k2 ;                                                                                                                         |                  | C = 0                                                                                                                                                                             |