Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·><Fl

| 2 0 000                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | LINbus, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1575t-i-sl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

## 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See section **Section 3.5 "Stack"** for more details.

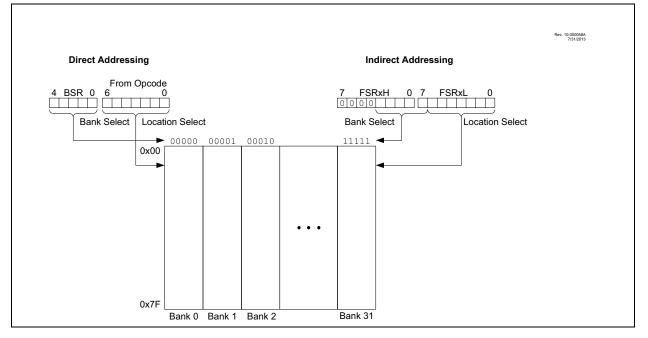

## 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

## 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 26.0** "Instruction Set Summary" for more details.

### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

## FIGURE 3-10: TRADITIONAL DATA MEMORY MAP

## REGISTER 4-2: CONFIGURATION WORD 2 (CONTINUED)

#### bit 1-0 WRT<1:0>: Flash Memory Self-Write Protection bits

- 4 kW Flash memory: (PIC16(L)F1574/8):

- 11 = OFF Write protection off

- 10 = BOOT 0000h to 1FFh write protected, 0200h to 0FFFh may be modified by PMCON control

- 01 = HALF 0000h to 07FFh write protected, 0800h to 0FFFh may be modified by PMCON control

- 00 = ALL 0000h to 0FFFh write protected, no addresses may be modified by PMCON control

- 8 kW Flash memory: (PIC16(L)F1575/9)

- 11 = OFF Write protection off

- 10 = BOOT 0000h to 1FFh write protected, 0200h to 1FFFh may be modified by PMCON control

- 01 = HALF 0000h to 0FFFh write protected, 1000h to 1FFFh may be modified by PMCON control

- 00 = ALL 0000h to 1FFFh write protected, no addresses may be modified by PMCON control

- Note 1: This bit cannot be programmed to '0' when programming mode is entered via LVP.

- **2:** The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

- **3:** See VBOR parameter for specific trip point voltages.

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

## TABLE 10-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|---------------|----------------------|-----------------------------|

| PIC16(L)F1574 |                      |                             |

| PIC16(L)F1575 | 32                   | 32                          |

| PIC16(L)F1578 | 52                   | 52                          |

| PIC16(L)F1579 |                      |                             |

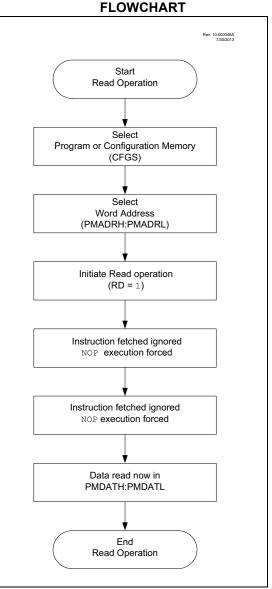

# 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH: PMDATL register pair will hold this value until another read or until it is written to by the user.

Note: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a 2-cycle instruction on the next instruction after the RD bit is set.

# FIGURE 10-1: FLASH PROGRAM MEMORY READ

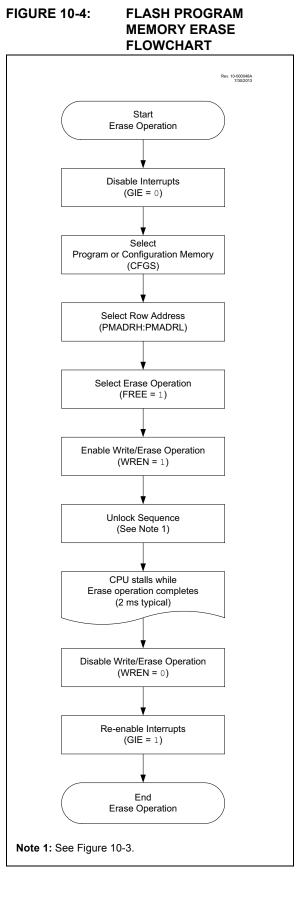

# 10.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

See Example 10-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

## EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

| ; 1. A               | valid addr                                                    | ess within the                                                                                              | s the following:<br>erase row is loaded in ADDRH:ADDRL<br>d in shared data memory 0x70 - 0x7F (common RAM)                                                                                                                                                                                                                                                     |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVWF<br>BCF<br>BSF<br>BSF | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W<br>PMADRH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN | <pre>; Disable ints so required sequences will execute properly<br/>; Load lower 8 bits of erase address boundary<br/>; Load upper 6 bits of erase address boundary<br/>; Not configuration space<br/>; Specify an erase operation<br/>; Enable writes</pre>                                                                                                   |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP                  | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR                                                                | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                                    | PMCON1,WREN<br>INTCON,GIE                                                                                   | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                        |

## REGISTER 12-3: PPSLOCK: PPS LOCK REGISTER

| U-0                                   | U-0               | U-0                                            | U-0                                                 | U-0                                                                             | U-0                                                                                                                                                    | R/W-0/0                                                                                                                                                                           |

|---------------------------------------|-------------------|------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _                                     | —                 | _                                              | —                                                   | _                                                                               | _                                                                                                                                                      | PPSLOCKED                                                                                                                                                                         |

|                                       |                   |                                                |                                                     |                                                                                 |                                                                                                                                                        | bit 0                                                                                                                                                                             |

|                                       |                   |                                                |                                                     |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |

|                                       |                   |                                                |                                                     |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |

| R = Readable bit W = Writable bit     |                   |                                                | U = Unimplemented bit, read as '0'                  |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |

| u = Bit is unchanged x = Bit is unkno |                   | own                                            | -n/n = Value a                                      | at POR and BC                                                                   | OR/Value at al                                                                                                                                         | I other Resets                                                                                                                                                                    |

|                                       | '0' = Bit is clea | ared                                           |                                                     |                                                                                 |                                                                                                                                                        |                                                                                                                                                                                   |

|                                       | e bit             | e bit W = Writable H<br>nanged x = Bit is unkn | e bit W = Writable bit<br>nanged x = Bit is unknown | e bit W = Writable bit U = Unimplen<br>nanged x = Bit is unknown -n/n = Value a | -     -     -     -       e bit     W = Writable bit     U = Unimplemented bit, rea       nanged     x = Bit is unknown     -n/n = Value at POR and BO | -     -     -     -     -       e bit     W = Writable bit     U = Unimplemented bit, read as '0'       nanged     x = Bit is unknown     -n/n = Value at POR and BOR/Value at al |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

1 = PPS is locked. PPS selections can not be changed.

0 = PPS is not locked. PPS selections can be changed.

| REGISTER 13-4: | IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER <sup>(1)</sup> |

|----------------|------------------------------------------------------------------------|

|----------------|------------------------------------------------------------------------|

| R/W-0/0                           | R/W-0/0 | R/W-0/0             | R/W-0/0       | U-0                  | U-0            | U-0                 | U-0   |

|-----------------------------------|---------|---------------------|---------------|----------------------|----------------|---------------------|-------|

| IOCBP7                            | IOCBP6  | IOCBP5              | IOCBP4        | _                    | —              | —                   | —     |

| bit 7                             |         |                     |               |                      |                |                     | bit 0 |

|                                   |         |                     |               |                      |                |                     |       |

| Legend:                           |         |                     |               |                      |                |                     |       |

| R = Readable bit W = Writable bit |         | :                   | U = Unimpleme | ented bit, read as ' | כי             |                     |       |

| u = Bit is unchar                 | nged    | x = Bit is unknow   | wn            | -n/n = Value at      | POR and BOR/Va | lue at all other Re | esets |

| '1' = Bit is set                  |         | '0' = Bit is cleare | ed            |                      |                |                     |       |

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

### REGISTER 13-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER<sup>(1)</sup>

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | —   | -   | _   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 **IOCBN<7:4>**: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

- bit 3-0 Unimplemented: Read as '0'

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

## REGISTER 13-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER<sup>(1)</sup>

| R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0   |

|------------|------------|------------|------------|-----|-----|-----|-------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | —   | _   | —   | —     |

| bit 7      | -          | •          |            |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | IOCBF<7:4>: Interrupt-on-Change PORTB Flag bits                                                      |

|---------|------------------------------------------------------------------------------------------------------|

|         | 1 = An enabled change was detected on the associated pin.                                            |

|         | Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was |

|         | detected on RBx.                                                                                     |

|         | 0 = No change was detected, or the user cleared the detected change.                                 |

|         |                                                                                                      |

bit 3-0 Unimplemented: Read as '0'

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

| ADC Clock Period (TAD) |               | Device Frequency (Fosc) |            |            |            |            |  |

|------------------------|---------------|-------------------------|------------|------------|------------|------------|--|

| ADC<br>Clock<br>Source | ADCS<2:0<br>> | 20 MHz                  | 16 MHz     | 8 MHz      | 4 MHz      | 1 MHz      |  |

| Fosc/2                 | 000           | 100 ns                  | 125 ns     | 250 ns     | 500 ns     | 2.0 μs     |  |

| Fosc/4                 | 100           | 200 ns                  | 250 ns     | 500 ns     | 1.0 μs     | 4.0 μs     |  |

| Fosc/8                 | 001           | 400 ns                  | 500 ns     | 1.0 μs     | 2.0 μs     | 8.0 μs     |  |

| Fosc/16                | 101           | 800 ns                  | 1.0 μs     | 2.0 μs     | 4.0 μs     | 16.0 μs    |  |

| Fosc/32                | 010           | 1.6 μs                  | 2.0 μs     | 4.0 μs     | 8.0 μs     | 32.0 μs    |  |

| Fosc/64                | 110           | 3.2 μs                  | 4.0 μs     | 8.0 μs     | 16.0 μs    | 64.0 μs    |  |

| FRC                    | x11           | 1.0-6.0 μs              | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs |  |

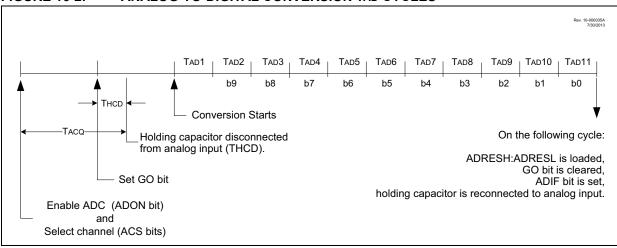

## TABLE 16-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range, (see TAD parameter). The TAD period when using the FOSC-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

## FIGURE 16-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

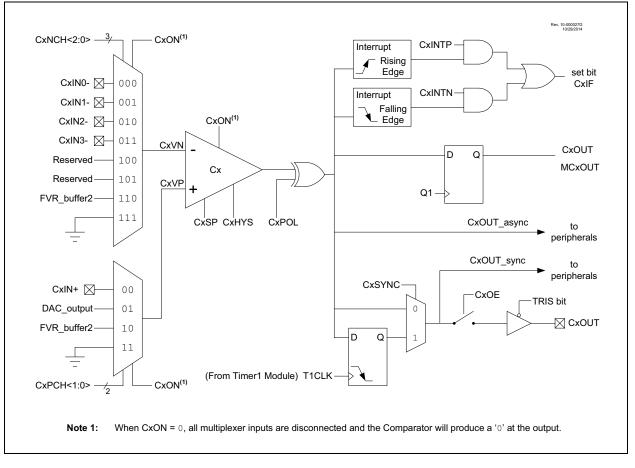

## 18.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- Programmable Speed/Power optimization

- PWM shutdown

- · Programmable and Fixed Voltage Reference

## 18.1 Comparator Overview

A single comparator is shown in Figure 18-2 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are listed in Table 18-1.

### TABLE 18-1: AVAILABLE COMPARATORS

| Device        | C1 | C2 |

|---------------|----|----|

| PIC16(L)F1574 | •  | •  |

| PIC16(L)F1575 | •  | •  |

| PIC16(L)F1578 | •  | •  |

| PIC16(L)F1579 | •  | •  |

### FIGURE 18-1: COMPARATOR MODULE SIMPLIFIED BLOCK DIAGRAM

## 23.1 Fundamental Operation

The PWM module produces a 16-bit resolution pulse width modulated output.

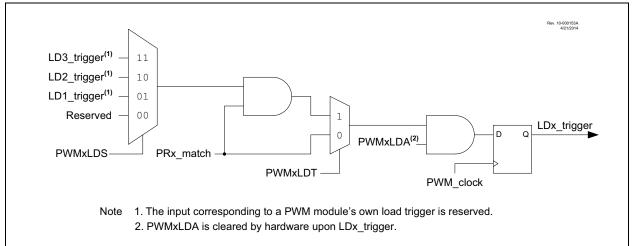

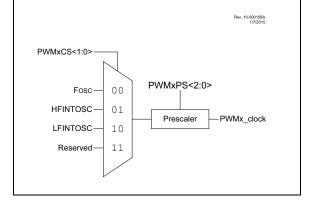

Each PWM module has an independent timer driven by a selection of clock sources determined by the PWMxCLKCON register (Register 23-4). The timer value is compared to event count registers to generate the various events of a the PWM waveform, such as the period and duty cycle. For a block diagram describing the clock sources refer to Figure 23-3.

Each PWM module can be enabled individually using the EN bit of the PWMxCON register, or several PWM modules can be enabled simultaneously using the mirror bits of the PWMEN register.

The current state of the PWM output can be read using the OUT bit of the PWMxCON register. In some modes this bit can be set and cleared by software giving additional software control over the PWM waveform. This bit is synchronized to Fosc/4 and therefore does not change in real time with respect to the PWM\_clock.

| Note: | If PWM_clock > Fosc/4, the OUT bit may       |

|-------|----------------------------------------------|

|       | not accurately represent the output state of |

|       | the PWM.                                     |

PWM CLOCK SOURCE BLOCK DIAGRAM

## 23.1.1 PWMx PIN CONFIGURATION

All PWM outputs are multiplexed with the PORT data latch, so the pins must also be configured as outputs by clearing the associated PORT TRIS bits.

The slew rate feature may be configured to optimize the rate to be used in conjunction with the PWM outputs. High-speed output switching is attained by clearing the associated PORT SLRCON bits.

The PWM outputs can be configured to be open-drain outputs by setting the associated PORT ODCON bits.

23.1.2 PWMx Output Polarity

The output polarity is inverted by setting the POL bit of the PWMxCON register. The polarity control affects the PWM output even when the module is not enabled.

## 23.7 Register Definitions: PWM Control

Long bit name prefixes for the 16-bit PWM peripherals are shown in Table 23-1. Refer to **Section 1.1 "Register and Bit Naming Conventions**" for more information

#### TABLE 23-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| PWM1       | PWM1            |

| PWM2       | PWM2            |

| PWM3       | PWM3            |

| PWM4       | PWM4            |

## REGISTER 23-1: PWMxCON: PWM CONTROL REGISTER

| R/W-0/0 | U-0 | R/HS/HC-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0   |

|---------|-----|-------------|---------|---------|---------|-----|-------|

| EN      | —   | OUT         | POL     | MODE    | E<1:0>  | —   | _     |

| bit 7   |     |             |         |         |         |     | bit 0 |

| Legend:                         |                  |                               |                                                       |  |  |

|---------------------------------|------------------|-------------------------------|-------------------------------------------------------|--|--|

| HC = Bit i                      | s cleared by ha  | rdware                        | HS = Bit is set by hardware                           |  |  |

| R = Readable bit                |                  | W = Writable bit              | U = Unimplemented bit, read as '0'                    |  |  |

| u = Bit is unchanged            |                  | x = Bit is unknown            | -n/n = Value at POR and BOR/Value at all other Resets |  |  |

| '1' = Bit is set                |                  | '0' = Bit is cleared          |                                                       |  |  |

|                                 |                  |                               |                                                       |  |  |

| bit 7 EN: PWM Module Enable bit |                  | Module Enable bit             |                                                       |  |  |

| 1 = Module is enabled           |                  |                               |                                                       |  |  |

| 0 = Module is disabled          |                  |                               |                                                       |  |  |

| bit 6                           | Unimplen         | nented: Read as '0'           |                                                       |  |  |

| bit 5                           | OUT: Outp        | out State of the PWM module   |                                                       |  |  |

| bit 4                           | POL: PWI         | M Output Polarity Control bit |                                                       |  |  |

|                                 | 1 = PWM          | output active state is low    |                                                       |  |  |

|                                 | 0 = PWM          | output active state is high   |                                                       |  |  |

| bit 3-2                         | MODE<1:          | 0>: PWM Mode Control bits     |                                                       |  |  |

|                                 | 11 = Cent        | er-Aligned mode               |                                                       |  |  |

|                                 | 10 <b>= Togg</b> | le On Match mode              |                                                       |  |  |

|                                 | 01 = Set (       | On Match mode                 |                                                       |  |  |

|                                 | 00 = Stan        | dard PWM mode                 |                                                       |  |  |

bit 1-0 Unimplemented: Read as '0'

| Name       | Bit 7    | Bit 6     | Bit 5                   | Bit 4 | Bit 3   | Bit 2  | Bit 1 | Bit 0 | Register<br>on Page |

|------------|----------|-----------|-------------------------|-------|---------|--------|-------|-------|---------------------|

| PWM3CLKCON | _        |           | PS<2:0>                 |       | _       | _      | CS<   | :1:0> | 235                 |

| PWM3LDCON  | LDA      | LDT       | —                       | —     | _       | _      | LDS   | <1:0> | 236                 |

| PWM30FC0N  | _        | OFM       | OFM<1:0> OFO - OFS<1:0> |       |         |        | <1:0> | 237   |                     |

| PWM4PHL    |          | PH<7:0>   |                         |       |         |        |       | 238   |                     |

| PWM4PHH    |          |           |                         | PI    | H<15:8> |        |       |       | 238                 |

| PWM4DCL    |          |           |                         | D     | C<7:0>  |        |       |       | 239                 |

| PWM4DCH    |          | DC<15:8>  |                         |       |         |        |       | 239   |                     |

| PWM4PRL    |          | PR<7:0>   |                         |       |         |        |       | 240   |                     |

| PWM4PRH    | PR<15:8> |           |                         |       |         |        | 240   |       |                     |

| PWM40FL    |          | OF<7:0>   |                         |       |         |        |       | 241   |                     |

| PWM40FH    | OF<15:8> |           |                         |       |         |        | 241   |       |                     |

| PWM4TMRL   |          | TMR<7:0>  |                         |       |         |        |       | 242   |                     |

| PWM4TMRH   |          | TMR<15:8> |                         |       |         |        | 242   |       |                     |

| PWM4CON    | EN       | _         | OUT                     | POL   | MODE    | E<1:0> |       | —     | 233                 |

| PWM4INTE   | _        | _         | _                       | _     | OFIE    | PHIE   | DCIE  | PRIE  | 234                 |

| PWM4INTF   |          | —         | _                       | _     | OFIF    | PHIF   | DCIF  | PRIF  | 234                 |

| PWM4CLKCON | _        |           | PS<2:0>                 | •     | _       | _      | CS<   | :1:0> | 235                 |

| PWM4LDCON  | LDA      | LDT       | —                       | —     | _       | _      | LDS   | <1:0> | 236                 |

| PWM40FCON  | _        | OFM       | <1:0>                   | OFO   | _       | _      | OFS   | <1:0> | 237                 |

## TABLE 23-2: SUMMARY OF REGISTERS ASSOCIATED WITH PWM (CONTINUED)

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PWM.

## TABLE 23-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 | -       | —       | -        | —        | CLKOUTEN | BORE     | N<1:0>  | —       | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | _        | FOSC    | C<1:0>  | 56                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

# FIGURE 26-1: GENERAL FORMAT FOR INSTRUCTIONS

| 13                                                                                                                                                     | 8 7                                                                                | 6              |                         | 0            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------|-------------------------|--------------|

| OPCODE                                                                                                                                                 | d                                                                                  |                | f (FILE #)              |              |

| d = 0 for des<br>d = 1 for des<br>f = 7-bit file                                                                                                       | stination f                                                                        |                | s                       |              |

| Bit-oriented file 1<br>13                                                                                                                              | r <b>egister o</b><br>10 9                                                         | perat<br>7     | t <b>ions</b><br>6      | 0            |

| OPCODE                                                                                                                                                 |                                                                                    | ,<br>BIT #)    | -                       |              |

| b = 3-bit bit f<br>f = 7-bit file                                                                                                                      |                                                                                    | ddres          | s                       |              |

| Literal and contr                                                                                                                                      | ol operat                                                                          | ions           |                         |              |

| General                                                                                                                                                |                                                                                    |                |                         |              |

| 13                                                                                                                                                     | 8                                                                                  | 7              |                         | 0            |

| OPCODE                                                                                                                                                 |                                                                                    |                | k (literal)             |              |

| k = 8-bit imn                                                                                                                                          | nediate va                                                                         | alue           |                         |              |

| CALL and GOTO ir                                                                                                                                       | structions                                                                         | s only         |                         |              |

| <u>13 11</u>                                                                                                                                           | 10                                                                                 | ,              |                         | 0            |

| OPCODE                                                                                                                                                 |                                                                                    | k              | (literal)               |              |

| k = 11-bit im                                                                                                                                          | mediate v                                                                          | alue           |                         |              |

|                                                                                                                                                        | only                                                                               |                |                         |              |

| MOVLP instruction<br>13                                                                                                                                | Ully                                                                               | 7              | 3                       | 0            |

| OPCODE                                                                                                                                                 |                                                                                    |                | k (literal)             |              |

| k = 7-bit imn                                                                                                                                          | nediate va                                                                         | lue            |                         |              |

|                                                                                                                                                        |                                                                                    |                |                         |              |

| MOVLB instruction                                                                                                                                      | only                                                                               |                | 54                      | 0            |

| 13<br>OPCODE                                                                                                                                           |                                                                                    |                | 5 4<br>k (litera        | 0            |

| k = 5-bit imn                                                                                                                                          | nediate va                                                                         | مىال           | (                       | ,            |

|                                                                                                                                                        |                                                                                    | liue           |                         |              |

|                                                                                                                                                        |                                                                                    |                |                         |              |

| BRA instruction or                                                                                                                                     |                                                                                    | 0              |                         | 0            |

| BRA instruction or<br>13<br>OPCODE                                                                                                                     | 9                                                                                  | 8              | k (literal)             | 0            |

| 13<br>OPCODE                                                                                                                                           | 9                                                                                  | -              | k (literal)             | 0            |

| 13                                                                                                                                                     | 9                                                                                  | -              | k (literal)             | 0            |

| 13<br>OPCODE<br>k = 9-bit imr<br>FSR Offset instru                                                                                                     | 9<br>mediate va                                                                    | -              | k (literal)             | 0            |

| 13<br>OPCODE<br>k = 9-bit imr<br>FSR Offset instru<br>13                                                                                               | 9<br>mediate va                                                                    | alue<br>6      | 5                       | 0            |

| 13<br>OPCODE<br>k = 9-bit imr<br>FSR Offset instru<br>13<br>OPCODE                                                                                     | 9<br>mediate va<br>ctions<br>7                                                     | alue           |                         | 0            |

| 13<br>OPCODE<br>k = 9-bit imr<br>FSR Offset instru<br>13                                                                                               | 9<br>mediate va<br>ctions<br>7<br>iate FSR                                         | alue<br>6<br>n | 5                       | 0            |

| 13<br>OPCODE<br>k = 9-bit imr<br>FSR Offset instru<br>13<br>OPCODE<br>n = appropr                                                                      | 9<br>mediate va<br>ctions<br>7<br>iate FSR<br>mediate va                           | alue<br>6<br>n | 5                       | 0            |

| 13<br>OPCODE<br>k = 9-bit imr<br>FSR Offset instru<br>13<br>OPCODE<br>n = appropr<br>k = 6-bit imr<br>FSR Increment ins                                | 9<br>mediate va<br>ctions<br>7<br>iate FSR<br>mediate va                           | alue<br>6<br>n | 5<br>k (litera<br>3 2 1 | 0            |

| 13<br>OPCODE<br>k = 9-bit imr<br>FSR Offset instru<br>13<br>OPCODE<br>n = appropr<br>k = 6-bit imr<br>FSR Increment ins<br>13                          | 9<br>nediate va<br>ctions<br>7<br>iate FSR<br>mediate va<br>structions<br>iate FSR | alue<br>6<br>n | 5<br>k (litera<br>3 2 1 | 0<br>I)<br>0 |

| 13<br>OPCODE<br>k = 9-bit imr<br>FSR Offset instru<br>13<br>OPCODE<br>n = appropr<br>k = 6-bit imr<br>FSR Increment ins<br>13<br>OPCODE<br>n = appropr | 9<br>nediate va<br>ctions<br>7<br>iate FSR<br>mediate va<br>structions<br>iate FSR | alue<br>6<br>n | 5<br>k (litera<br>3 2 1 | 0<br>I)<br>0 |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                    |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                               |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |

| IORLW            | Inclusive OR literal with W                                                                                        |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |  |  |

## TABLE 27-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup>

| PIC16LF       | 1574/5/8/9      | Standard Operating Conditions (unless otherwise stated) |      |      |       |            |                                            |  |  |

|---------------|-----------------|---------------------------------------------------------|------|------|-------|------------|--------------------------------------------|--|--|

| PIC16F1       | 574/5/8/9       |                                                         |      |      |       |            |                                            |  |  |

| Param. Device |                 | Min.                                                    | Тур† | Max. | Units | Conditions |                                            |  |  |

| No.           | Characteristics |                                                         | 1961 |      |       | Vdd        | Note                                       |  |  |

| D013          |                 | _                                                       | 41   | 51   | μA    | 1.8        | Fosc = 1 MHz,                              |  |  |

|               |                 | —                                                       | 69   | 80   | μA    | 3.0        | External Clock (ECM),<br>Medium Power mode |  |  |

| D013          |                 | —                                                       | 79   | 107  | μA    | 2.3        | Fosc = 1 MHz,                              |  |  |

|               |                 |                                                         | 105  | 138  | μA    | 3.0        | External Clock (ECM),                      |  |  |

|               |                 |                                                         | 151  | 184  | μA    | 5.0        | Medium Power mode                          |  |  |

| D014          |                 |                                                         | 134  | 152  | μA    | 1.8        | Fosc = 4 MHz,                              |  |  |

|               |                 | -                                                       | 234  | 268  | μA    | 3.0        | External Clock (ECM),<br>Medium Power mode |  |  |

| D014          |                 |                                                         | 201  | 255  | μA    | 2.3        | Fosc = 4 MHz,                              |  |  |

|               |                 | —                                                       | 270  | 329  | μA    | 3.0        | External Clock (ECM),<br>Medium Power mode |  |  |

|               |                 | —                                                       | 344  | 431  | μA    | 5.0        |                                            |  |  |

| D015          |                 | —                                                       | 7    | 19   | μA    | 1.8        | Fosc = 31 kHz,                             |  |  |

|               |                 | —                                                       | 9    | 20   | μA    | 3.0        | LFINTOSC,<br>-40°C ≤ Ta ≤ +85°C            |  |  |

| D015          |                 |                                                         | 15   | 25   | μA    | 2.3        | Fosc = 31 kHz,                             |  |  |

|               |                 | _                                                       | 18   | 28   | μA    | 3.0        | └ LFINTOSC,<br>40°C ≤ TA ≤ +85°C           |  |  |

|               |                 | _                                                       | 20   | 29   | μA    | 5.0        | $=-40$ C $\leq$ 1A $\leq$ +65 C            |  |  |

| D016          |                 | —                                                       | 128  | 174  | μA    | 1.8        | Fosc = 500 kHz,                            |  |  |

|               |                 | _                                                       | 153  | 203  | μA    | 3.0        | MFINTOSC                                   |  |  |

| D016          |                 | —                                                       | 166  | 241  | μA    | 2.3        | Fosc = 500 kHz,                            |  |  |

|               |                 |                                                         | 187  | 273  | μA    | 3.0        | MFINTOSC                                   |  |  |

|               |                 | _                                                       | 249  | 332  | μA    | 5.0        |                                            |  |  |

| D017*         |                 | _                                                       | 0.6  | 0.7  | mA    | 1.8        | Fosc = 8 MHz,                              |  |  |

|               |                 | _                                                       | 0.9  | 1.1  | mA    | 3.0        | HFINTOSC                                   |  |  |

| D017*         |                 | —                                                       | 0.7  | 1.0  | mA    | 2.3        | Fosc = 8 MHz,                              |  |  |

|               |                 | _                                                       | 1.0  | 1.1  | mA    | 3.0        | HFINTOSC                                   |  |  |

|               |                 | _                                                       | 1.1  | 1.2  | mA    | 5.0        |                                            |  |  |

| D018          |                 | _                                                       | 0.9  | 1.0  | mA    | 1.8        | Fosc = 16 MHz,                             |  |  |

|               |                 | _                                                       | 1.3  | 1.4  | mA    | 3.0        | HFINTOSC                                   |  |  |

| D018          |                 | _                                                       | 1.1  | 1.3  | mA    | 2.3        | Fosc = 16 MHz,                             |  |  |

|               |                 | _                                                       | 1.3  | 1.5  | mA    | 3.0        | HFINTOSC                                   |  |  |

|               |                 | _                                                       | 1.5  | 1.8  | mA    | 5.0        | -                                          |  |  |

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: CLKIN = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: PLL required for 32 MHz operation.

| Standard Operating Conditions (unless otherwise stated) |           |                                        |            |                           |                                                          |  |  |

|---------------------------------------------------------|-----------|----------------------------------------|------------|---------------------------|----------------------------------------------------------|--|--|

| Param.<br>No.                                           | Sym.      | Characteristic                         | Typ. Units |                           | Conditions                                               |  |  |

| ТН01 θја                                                |           | Thermal Resistance Junction to Ambient | 70         | °C/W                      | 14-pin PDIP package                                      |  |  |

|                                                         | 95.3      |                                        | °C/W       | 14-pin SOIC package       |                                                          |  |  |

|                                                         |           |                                        | 100        | °C/W                      | 14-pin TSSOP package                                     |  |  |

|                                                         |           |                                        | 31.8       | °C/W                      | 16-pin UQFN 4x4mm package                                |  |  |

|                                                         |           |                                        | 62.2       | °C/W                      | 20-pin PDIP package                                      |  |  |

|                                                         |           |                                        | 77.7       | °C/W                      | 20-pin SOIC package                                      |  |  |

|                                                         |           |                                        | 87.3       | °C/W                      | 20-pin SSOP package                                      |  |  |

|                                                         |           |                                        | 32.8       | °C/W                      | 20-pin UQFN 4x4mm package                                |  |  |

| TH02                                                    | θJC       | Thermal Resistance Junction to Case    | 32.75      | °C/W                      | 14-pin PDIP package                                      |  |  |

|                                                         |           |                                        | 31         | °C/W                      | 14-pin SOIC package                                      |  |  |

|                                                         |           | 24.4                                   | °C/W       | 14-pin TSSOP package      |                                                          |  |  |

|                                                         |           | 24.4                                   | °C/W       | 16-pin UQFN 4x4mm package |                                                          |  |  |

|                                                         |           | 27.5                                   | °C/W       | 20-pin PDIP package       |                                                          |  |  |

|                                                         |           | 23.1                                   | °C/W       | 20-pin SOIC package       |                                                          |  |  |

|                                                         |           | 31.1                                   | °C/W       | 20-pin SSOP package       |                                                          |  |  |

|                                                         |           | 27.4                                   | °C/W       | 20-pin UQFN 4x4mm package |                                                          |  |  |

| TH03                                                    | TJMAX     | Maximum Junction Temperature           | 150        | °C                        |                                                          |  |  |

| TH04                                                    | PD        | Power Dissipation                      | —          | W                         | PD = PINTERNAL + PI/O                                    |  |  |

| TH05                                                    | PINTERNAL | Internal Power Dissipation             | _          | W                         | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06                                                    | Pi/o      | I/O Power Dissipation                  | _          | W                         | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07                                                    | Pder      | Derated Power                          | _          | W                         | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |  |

## TABLE 27-6: THERMAL CHARACTERISTICS

**Note 1:** IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature; TJ = Junction Temperature

## 30.2 Package Details

The following sections give the technical details of the packages.

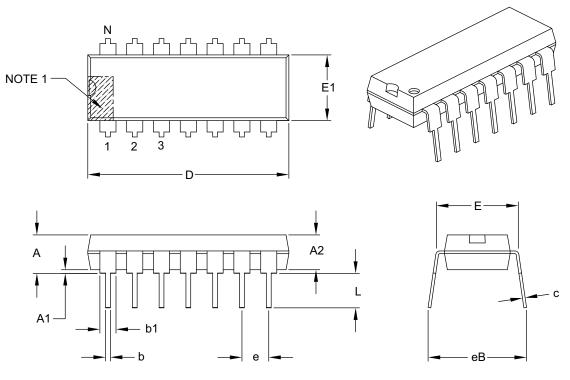

## 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      |          |      |      |  |

|----------------------------|------------|----------|------|------|--|

| Dimens                     | ion Limits | MIN      | NOM  | MAX  |  |

| Number of Pins             | Ν          | 14       |      |      |  |

| Pitch                      | е          | .100 BSC |      |      |  |

| Top to Seating Plane       | Α          | -        | -    | .210 |  |

| Molded Package Thickness   | A2         | .115     | .130 | .195 |  |

| Base to Seating Plane      | A1         | .015     | -    | -    |  |

| Shoulder to Shoulder Width | E          | .290     | .310 | .325 |  |

| Molded Package Width       | E1         | .240     | .250 | .280 |  |

| Overall Length             | D          | .735     | .750 | .775 |  |

| Tip to Seating Plane       | L          | .115     | .130 | .150 |  |

| Lead Thickness             | С          | .008     | .010 | .015 |  |

| Upper Lead Width           | b1         | .045     | .060 | .070 |  |

| Lower Lead Width           | b          | .014     | .018 | .022 |  |

| Overall Row Spacing §      | eB         | -        | -    | .430 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

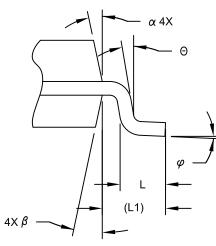

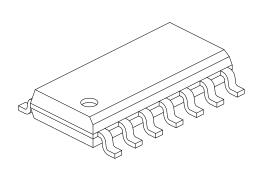

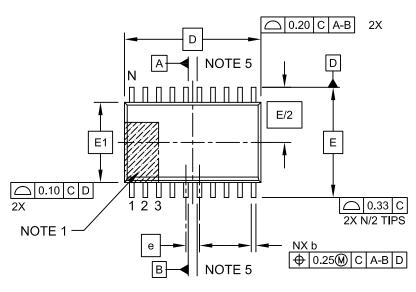

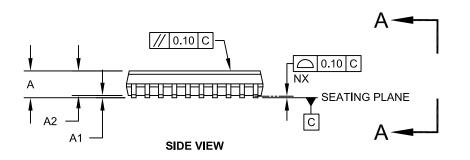

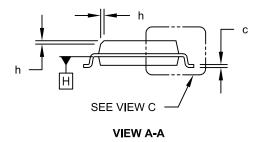

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | MILLIMETERS |             |          |      |  |

|--------------------------|-------------|-------------|----------|------|--|

| Dimension Lir            | MIN         | NOM         | MAX      |      |  |

| Number of Pins           | N           | 14          |          |      |  |

| Pitch                    | е           |             | 1.27 BSC |      |  |

| Overall Height           | A           | -           | -        | 1.75 |  |

| Molded Package Thickness | A2          | 1.25        | -        | -    |  |

| Standoff §               | A1          | 0.10        | -        | 0.25 |  |

| Overall Width            | E           | 6.00 BSC    |          |      |  |

| Molded Package Width     | E1          | 3.90 BSC    |          |      |  |

| Overall Length           | D           | 8.65 BSC    |          |      |  |

| Chamfer (Optional)       | h           | 0.25 - 0.50 |          |      |  |

| Foot Length              | L           | 0.40        | -        | 1.27 |  |

| Footprint                | L1          | 1.04 REF    |          |      |  |

| Lead Angle               | Θ           | 0°          | -        | -    |  |

| Foot Angle               | φ           | 0°          | -        | 8°   |  |

| Lead Thickness           | c           | 0.10        | -        | 0.25 |  |

| Lead Width               | b           | 0.31        | -        | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°          | -        | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°          | -        | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2