Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | LINbus, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                             |

| Supplier Device Package    | 14-TSSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1575t-i-st |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.6 "Indirect Addressing"** for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-14.

| TABLE 3-2: | CORE REGISTERS |

|------------|----------------|

| IADLL J-Z. |                |

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| k0Bh or x8Bh | INTCON |

# TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY

| Address | Name                 | Bit 7                             | Bit 6              | Bit 5          | Bit 4           | Bit 3                   | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------|-----------------------------------|--------------------|----------------|-----------------|-------------------------|--------|--------|-----------|----------------------|---------------------------------|

| Bank 0  |                      |                                   |                    |                |                 |                         |        |        |           |                      |                                 |

| 00Ch    | PORTA                | _                                 | _                  | RA5            | RA4             | RA3                     | RA2    | RA1    | RA0       | xx xxxx              | xx xxxx                         |

| 00Dh    | PORTB <sup>(1)</sup> | RB7                               | RB6                | RB5            | RB4             | —                       | —      |        | —         | xxxx                 | xxxx                            |

| 00Eh    | PORTC                | RC7 <sup>(1)</sup>                | RC6 <sup>(1)</sup> | RC5            | RC4             | RC3                     | RC2    | RC1    | RC0       | xxxx xxxx            | xxxx xxxx                       |

| 00Fh    | —                    | Unimplemen                        | nted               |                |                 |                         |        |        |           | _                    | _                               |

| 010h    | —                    | Unimplemen                        | nted               |                |                 |                         |        |        |           | _                    | _                               |

| 011h    | PIR1                 | TMR1GIF                           | ADIF               | RCIF           | TXIF            | —                       | —      | TMR2IF | TMR1IF    | 000000               | 000000                          |

| 012h    | PIR2                 | _                                 | C2IF               | C1IF           | _               | —                       | —      | _      | —         | -00                  | -00                             |

| 013h    | PIR3                 | PWM4IF                            | PWM3IF             | PWM2IF         | PWM1IF          | —                       | —      | _      | —         | 0000                 | 0000                            |

| 014h    | —                    |                                   |                    |                |                 |                         |        |        |           | —                    | —                               |

| 015h    | TMR0                 | Holding Reg                       | ister for the 8    | 3-bit Timer0 ( | Count           |                         |        |        |           | xxxx xxxx            | uuuu uuuu                       |

| 016h    | TMR1L                | Holding Reg                       | ister for the l    | _east Signific | ant Byte of the | 16-bit TMR1 Co          | ount   |        |           | xxxx xxxx            | uuuu uuuu                       |

| 017h    | TMR1H                | Holding Reg                       | ister for the I    | Most Significa | ant Byte of the | 16-bit TMR1 Co          | unt    |        |           | xxxx xxxx            | uuuu uuuu                       |

| 018h    | T1CON                | TMR1C                             | S<1:0>             | T1CK           | PS<1:0>         | —                       | T1SYNC | _      | TMR10N    | 0000 -0-0            | uuuu -u-u                       |

| 019h    | T1GCON               | TMR1GE                            | T1GPOL             | T1GTM          | T1GSPM          | T <u>1GGO</u> /<br>DONE | T1GVAL | T1GS   | S<1:0>    | 0000 0x00            | uuuu uxuu                       |

| 01Ah    | TMR2                 | Timer2 Mod                        | ule Register       |                |                 |                         |        |        |           | 0000 0000            | 0000 0000                       |

| 01Bh    | PR2                  | Timer2 Period Register            |                    |                |                 |                         |        |        |           | 1111 1111            | 1111 1111                       |

| 01Ch    | T2CON                | - T20UTPS<3:0> TMR20N T2CKPS<1:0> |                    |                |                 |                         |        |        | -000 0000 | -000 0000            |                                 |

| 01Dh    | _                    | Unimplemented                     |                    |                |                 |                         |        |        |           | _                    | _                               |

| 01Eh    | —                    | Unimplemented                     |                    |                |                 |                         |        |        |           | _                    |                                 |

| 01Fh    | —                    | Unimplemer                        | nted               |                |                 |                         |        |        |           | _                    | _                               |

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

| Address | Name       | Bit 7     | Bit 6    | Bit 5   | Bit 4 | Bit 3     | Bit 2     | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------|-----------|----------|---------|-------|-----------|-----------|-----------|-----------|----------------------|---------------------------------|

| Bank 27 | •          | •         |          | •       | •     |           |           |           |           |                      |                                 |

| D8Ch    | _          | Unimpleme | nted     |         |       |           |           |           |           | —                    | —                               |

| D8Dh    | _          | Unimpleme | nted     |         |       |           |           |           |           | _                    | —                               |

| D8Eh    | PWMEN      | _         | —        | _       | _     | PWM4EN_A  | PWM3EN_A  | PWM2EN_A  | PWM1EN_A  | 0000                 | 0000                            |

| D8Fh    | PWMLD      | _         | _        | _       | _     | PWM4LDA_A | PWM3LDA_A | PWM2LDA_A | PWM1LDA_A | 0000                 | 000                             |

| D90h    | PWMOUT     | _         | _        | _       | _     | PWM4OUT_A | PWM3OUT_A | PWM2OUT_A | PWM10UT_A | 0000                 | 0000                            |

| D91h    | PWM1PHL    |           |          |         |       | PH<7:0>   |           |           |           | xxxx xxxx            | นนนน นนนเ                       |

| D92h    | PWM1PHH    |           |          |         |       | PH<15:8>  |           |           |           | xxxx xxxx            | นนนน นนนเ                       |

| D93h    | PWM1DCL    |           |          |         |       | DC<7:0>   |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| D94h    | PWM1DCH    |           |          |         |       | DC<15:8>  |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| D95h    | PWM1PRL    |           |          |         |       | PR<7:0>   |           |           |           | xxxx xxxx            | นนนน นนนเ                       |

| D96h    | PWM1PRH    |           |          |         |       | PR<15:8>  |           |           |           | xxxx xxxx            | นนนน นนนเ                       |

| D97h    | PWM10FL    |           |          |         |       | OF<7:0>   |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| D98h    | PWM10FH    |           |          |         |       | OF<15:8>  |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| D99h    | PWM1TMRL   |           |          |         |       | TMR<7:0>  |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| D9Ah    | PWM1TMRH   |           |          |         |       | TMR<15:8> |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| D9Bh    | PWM1CON    | EN        | —        | OUT     | POL   | MODI      | E<1:0>    |           | _         | 0-00 00              | 0-00 00                         |

| D9Ch    | PWM1INTE   | —         | —        | —       | —     | OFIE      | PHIE      | DCIE      | PRIE      | 000                  | 000                             |

| D9Dh    | PWM1INTF   | —         | —        | —       | —     | OFIF      | PHIF      | DCIF      | PRIF      | 000                  | 000                             |

| D9Eh    | PWM1CLKCON | —         |          | PS<2:0> |       | —         | —         | CS<       | <1:0>     | -000 -000            | -00000                          |

| D9Fh    | PWM1LDCON  | LDA       | LDT      | —       | —     | —         | —         | LDS       | <1:0>     | 00000                | 0000                            |

| DA0h    | PWM10FCON  | —         | OFM      | <1:0>   | OFO   | —         | —         | OFS       | <1:0>     | -000 -000            | -00000                          |

| DA1h    | PWM2PHL    |           |          |         |       | PH<7:0>   |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA2h    | PWM2PHH    |           | PH<15:8> |         |       |           |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA3h    | PWM2DCL    |           | DC<7:0>  |         |       |           |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA4h    | PWM2DCH    |           | DC<15:8> |         |       |           |           |           |           | xxxx xxxx            | uuuu uuuu                       |

| DA5h    | PWM2PRL    | PR<7:0>   |          |         |       |           |           |           | xxxx xxxx | սսսս սսսս            |                                 |

| DA6h    | PWM2PRH    | PR<15:8>  |          |         |       |           |           |           | xxxx xxxx | uuuu uuuu            |                                 |

| DA7h    | PWM2OFL    | OF<7:0>   |          |         |       |           |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| DA8h    | PWM2OFH    |           |          |         |       | OF<15:8>  |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| DA9h    | PWM2TMRL   |           |          |         |       | TMR<7:0>  |           |           |           | xxxx xxxx            | սսսս սսսս                       |

| DAAh    | PWM2TMRH   |           |          |         |       | TMR<15:8> |           |           |           | xxxx xxxx            | uuuu uuuu                       |

#### TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3:

Unimplemented, read as '1'.

| Address            | Name                | Bit 7            | Bit 6            | Bit 5   | Bit 4 | Bit 3    | Bit 2         | Bit 1    | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------------------|---------------------|------------------|------------------|---------|-------|----------|---------------|----------|-----------|----------------------|---------------------------------|

| Bank 27            | Bank 27 (Continued) |                  |                  |         |       |          |               |          |           |                      |                                 |

| DC9h               | PWM4TMRL            |                  |                  |         | -     | TMR<7:0> |               |          |           | xxxx xxxx            | uuuu uuuu                       |

| DCAh               | PWM4TMRH            |                  |                  |         | Т     | MR<15:8> |               |          |           | xxxx xxxx            | uuuu uuuu                       |

| DCBh               | PWM4CON             | EN               | —                | OUT     | POL   | MODE     | E<1:0>        | _        | —         | 0000 00              | 0000 00                         |

| DCCh               | PWM4INTE            | —                | —                | —       | —     | OFIE     | PHIE          | DCIE     | PRIE      | 000                  | 000                             |

| DCDh               | PWM4INTF            | —                | —                | —       | —     | OFIF     | PHIF          | DCIF     | PRIF      | 000                  | 000                             |

| DCEh               | PWM4CLKCON          | —                |                  | PS<2:0> |       | _        | —             | CS∢      | <1:0>     | -000 -000            | -00000                          |

| DCFh               | PWM4LDCON           | LDA              | LDT              | —       | —     | —        | —             | LDS      | <1:0>     | 00000                | 0000                            |

| DD0h               | PWM40FCON           | —                | OFM              | <1:0>   | OFO   | _        | —             | OFS      | <1:0>     | -000 -000            | -00000                          |

| DD1h<br>to<br>DEFh | _                   | Unimplemer       | Inimplemented    |         |       |          |               |          |           | _                    |                                 |

| Bank 28            |                     |                  |                  |         |       |          |               |          |           |                      |                                 |

| E0Ch               |                     |                  |                  |         |       |          |               |          |           |                      |                                 |

| E0Eh               | -                   | Unimplemen       | ited             |         |       |          |               |          |           | —                    | _                               |

| E0Fh               | PPSLOCK             | —                | —                | _       | —     | _        | _             | —        | PPSLOCKED | 0                    | 0                               |

| E10h               | INTPPS              | _                | _                | _       |       | •        | INTPPS<4:0>   |          |           | 0 0010               | u uuuu                          |

| E11h               | TOCKIPPS            | _                | _                | _       |       |          | T0CKIPPS<4:0> | >        |           | 0 0010               | u uuuu                          |

| E12h               | T1CKIPPS            | _                | _                | _       |       |          | T1CKIPPS<4:0> | <b>`</b> |           | 0 0101               | u uuuu                          |

| E13h               | T1GPPS              | _                | _                | _       |       |          | T1GPPS<4:0>   |          |           | 0 0100               | u uuuu                          |

| E14h               | CWG1INPPS           | _                |                  |         |       |          |               |          | 0 0010    | u uuuu               |                                 |

| E15h               | RXPPS               | — — — RXPPS<4:0> |                  |         |       |          |               | 1 0101   | u uuuu    |                      |                                 |

| E16h               | CKPPS               | _                | — — — CKPPS<4:0> |         |       |          |               |          | 1 0101    | u uuuu               |                                 |

| E17h               | ADCACTPPS           | ADCACTPPS<4:0>   |                  |         |       |          |               | 1 0101   | u uuuu    |                      |                                 |

| E18h<br>to<br>E6Fh | _                   | Unimplemer       | Inimplemented    |         |       |          |               |          |           | —                    | _                               |

## TABLE 3-15: SPECIAL EUNCTION DEGISTED SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

DS40001782C-page 45

| U-0              | R-0/q                                  | R-q/q                                               | R-0/q             | R-0/q           | R-q/q             | R-0/q            | R-0/q        |  |  |

|------------------|----------------------------------------|-----------------------------------------------------|-------------------|-----------------|-------------------|------------------|--------------|--|--|

| —                | PLLR                                   | OSTS                                                | HFIOFR            | HFIOFL          | MFIOFR            | LFIOFR           | HFIOFS       |  |  |

| bit 7            |                                        |                                                     |                   |                 |                   |                  | bit C        |  |  |

|                  |                                        |                                                     |                   |                 |                   |                  |              |  |  |

| Legend:          |                                        |                                                     |                   |                 |                   |                  |              |  |  |

| R = Readable     | e bit                                  | W = Writable                                        | bit               | U = Unimpler    | nented bit, reac  | l as '0'         |              |  |  |

| u = Bit is unc   | hanged                                 | x = Bit is unkr                                     | nown              | -n/n = Value a  | at POR and BO     | R/Value at all o | other Resets |  |  |

| '1' = Bit is set | t                                      | '0' = Bit is cle                                    | ared              | q = Condition   | al                |                  |              |  |  |

|                  |                                        |                                                     |                   |                 |                   |                  |              |  |  |

| bit 7            | •                                      | ted: Read as '                                      | 0'                |                 |                   |                  |              |  |  |

| bit 6            | PLLR 4x PLL                            | •                                                   |                   |                 |                   |                  |              |  |  |

|                  | 1 = 4x PLL i<br>0 = 4x PLL i           |                                                     |                   |                 |                   |                  |              |  |  |

| bit 5            |                                        | ator Start-up Ti                                    | mer Status hit    |                 |                   |                  |              |  |  |

|                  |                                        | •                                                   |                   | FOSC<1.0>1      | oits of the Confi | guration Word    | s            |  |  |

|                  |                                        | from an intern                                      |                   |                 |                   | guiation word    | 5            |  |  |

| bit 4            | HFIOFR: Hig                            | h-Frequency Ir                                      | iternal Oscillate | or Ready bit    |                   |                  |              |  |  |

|                  | 1 = HFINTO                             |                                                     |                   |                 |                   |                  |              |  |  |

|                  | 0 = HFINTO                             | SC is not ready                                     | 1                 |                 |                   |                  |              |  |  |

| bit 3            | •                                      | h-Frequency In                                      |                   | or Locked bit   |                   |                  |              |  |  |

|                  |                                        | SC is at least 2<br>SC is not 2% a                  |                   |                 |                   |                  |              |  |  |

| bit 2            |                                        |                                                     |                   | illator Poady b | i+                |                  |              |  |  |

|                  | 1 = MFINTO                             | dium-Frequend                                       | y memai Osc       | illator Ready D | it.               |                  |              |  |  |

|                  |                                        | SC is not read                                      | /                 |                 |                   |                  |              |  |  |

| bit 1            | LFIOFR: Low                            | LFIOFR: Low-Frequency Internal Oscillator Ready bit |                   |                 |                   |                  |              |  |  |

|                  | 1 = LFINTOS                            | SC is ready                                         |                   | -               |                   |                  |              |  |  |

|                  | 0 = LFINTOS                            | SC is not ready                                     |                   |                 |                   |                  |              |  |  |

| bit 0            | HFIOFS: Hig                            | h-Frequency Ir                                      | ternal Oscillato  | or Stable bit   |                   |                  |              |  |  |

|                  | 1 = HFINTOSC is at least 0.5% accurate |                                                     |                   |                 |                   |                  |              |  |  |

|                  | 0 = HFINTO                             | SC is not 0.5%                                      | accurate          |                 |                   |                  |              |  |  |

# REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

# 12.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

**Note:** The I<sup>2</sup>C default input pins are I<sup>2</sup>C and SMBus compatible and are the only pins on the device with this compatibility.

# 12.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 12-1.

EXAMPLE 12-1: PPS LOCK/UNLOCK SEQUENCE

| the second destruction with a            |

|------------------------------------------|

| ; suspend interrupts                     |

| bcf INTCON,GIE                           |

| ; BANKSEL PPSLOCK ; set bank             |

| ; required sequence, next 5 instructions |

| movlw 0x55                               |

| movwf PPSLOCK                            |

| movlw 0xAA                               |

| movwf PPSLOCK                            |

| ; Set PPSLOCKED bit to disable writes or |

| ; Clear PPSLOCKED bit to enable writes   |

| bsf PPSLOCK, PPSLOCKED                   |

| ; restore interrupts                     |

| bsf INTCON,GIE                           |

|                                          |

# 12.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

# 12.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

# 12.7 Effects of a Reset

A device Power-On-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in Table 12-1.

| Peripheral | Conditions                                                        | Description                                                        |

|------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 010 and<br>IRCF<3:0> = 000x                           | INTOSC is active and device is not in Sleep.                       |

|            | BOREN<1:0> = 11                                                   | BOR always enabled.                                                |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                     | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                                     | BOR under software control, BOR Fast Start enabled.                |

| LDO        | All PIC16F1574/5/8/9 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the Low-Power Regulator when in Sleep mode. |

# TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

# 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

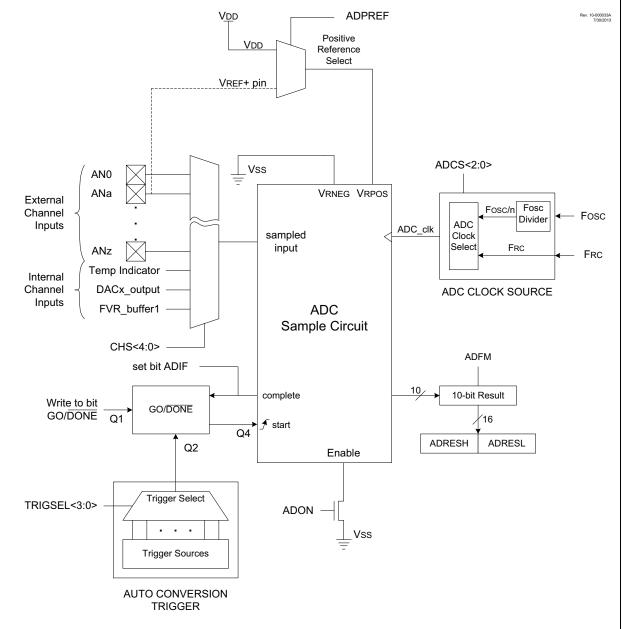

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC. The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

# 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACxCON1 register.

The DAC output voltage can be determined by using Equation 17-1.

# 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 27-16.

# 17.3 DAC Voltage Reference Output

The unbuffered DAC voltage can be output to the DACxOUTn pin(s) by setting the respective DACOEn bit(s) of the DACxCON0 register. Selecting the DAC reference voltage for output on either DACxOUTn pin automatically overrides the digital output buffer, the weak pull-up and digital input threshold detector functions of that pin.

Reading the DACxOUTn pin when it has been configured for DAC reference voltage output will always return a '0'.

**Note:** The unbuffered DAC output (DACxOUTn) is not intended to drive an external load.

# 17.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACxCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 17.5 Effects of a Reset

A device Reset affects the following:

- DACx is disabled.

- DACx output voltage is removed from the DACxOUTn pin(s).

- The DACR<4:0> range select bits are cleared.

## EQUATION 17-1: DAC OUTPUT VOLTAGE

## <u>IF DACEN = 1</u>

$$DACx\_output = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE-$$

**Note:** See the DACxCON0 register for the available VSOURCE+ and VSOURCE- selections.

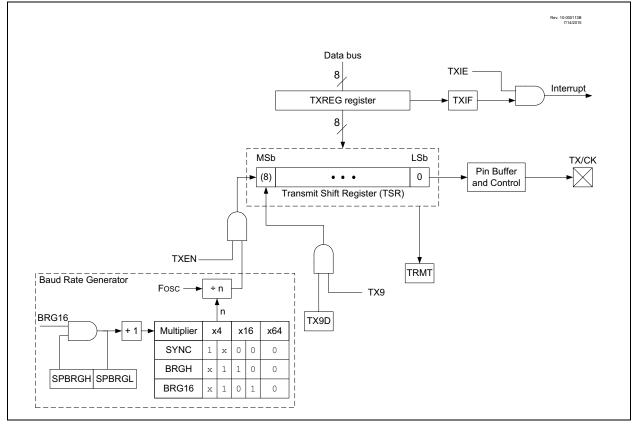

# 22.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- · Two-character input buffer

- · One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- · Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 22-1 and Figure 22-2.

#### FIGURE 22-1: EUSART TRANSMIT BLOCK DIAGRAM

# 23.4 Reload Operation

Four of the PWM module control register pairs and one control bit are double buffered so that all can be updated simultaneously. These include:

- PWMxPHH:PWMxPHL register pair

- PWMxDCH:PWMxDCL register pair

- PWMxPRH:PWMxPRL register pair

- PWMxOFH:PWMxOFL register pair

- OFO control bit

When written to, these registers do not immediately affect the operation of the PWM. By default, writes to these registers will not be loaded into the PWM operating buffer registers until after the arming conditions are met. The arming control has two methods of operation:

- · Immediate

- Triggered

The LDT bit of the PWMxLDCON register controls the arming method. Both methods require the LDA bit to be set. All four buffer pairs will load simultaneously at the loading event.

#### 23.4.1 IMMEDIATE RELOAD

When the LDT bit is clear then the immediate mode is selected and the buffers will be loaded at the first period event after the LDA bit is set. Immediate reloading is used when a PWM module is operating stand-alone or when the PWM module is operating as a master to other slave PWM modules.

#### 23.4.2 TRIGGERED RELOAD

When the LDT bit is set then the Triggered mode is selected and a trigger event is required for the LDA bit to take effect. The trigger source is the buffer load event of one of the other PWM modules in the device. The triggering source is selected by the LDS<1:0> bits of the PWMxLDCON register. The buffers will be loaded at the first period event following the trigger event. Triggered reloading is used when a PWM module is operating as a slave to another PWM and it is necessary to synchronize the buffer reloads in both modules.

Note 1: The buffer load operation clears the LDA bit.

2: If the LDA bit is set at the same time as PWMxTMR = PWMxPR, the LDA bit is ignored until the next period event. Such is the case when triggered reload is selected and the triggering event occurs simultaneously with the target's period event

# 23.5 Operation in Sleep Mode

Each PWM module will continue to operate in Sleep mode when either the HFINTOSC or LFINTOSC is selected as the clock source by PWMxCLKCON<1:0>.

#### 23.6 Interrupts

Each PWM module has four independent interrupts based on the phase, duty cycle, period, and offset match events. The interrupt flag is set on the rising edge of each of these signals. Refer to Figures 23-8 and 23-12 for detailed timing diagrams of the match signals.

# 23.7 Register Definitions: PWM Control

Long bit name prefixes for the 16-bit PWM peripherals are shown in Table 23-1. Refer to **Section 1.1 "Register and Bit Naming Conventions**" for more information

#### TABLE 23-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| PWM1       | PWM1            |

| PWM2       | PWM2            |

| PWM3       | PWM3            |

| PWM4       | PWM4            |

## REGISTER 23-1: PWMxCON: PWM CONTROL REGISTER

| R/W-0/0 | U-0 | R/HS/HC-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | U-0 | U-0   |

|---------|-----|-------------|---------|-----------|---------|-----|-------|

| EN      | —   | OUT         | POL     | MODE<1:0> |         | —   | _     |

| bit 7   |     |             |         |           |         |     | bit 0 |

| Legend:      |                  |                               |                                                       |

|--------------|------------------|-------------------------------|-------------------------------------------------------|

| HC = Bit i   | s cleared by ha  | rdware                        | HS = Bit is set by hardware                           |

| R = Read     | able bit         | W = Writable bit              | U = Unimplemented bit, read as '0'                    |

| u = Bit is   | unchanged        | x = Bit is unknown            | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is | set              | '0' = Bit is cleared          |                                                       |

|              |                  |                               |                                                       |

| bit 7        | EN: PWM          | Module Enable bit             |                                                       |

|              |                  | le is enabled                 |                                                       |

|              | 0 = Modu         | le is disabled                |                                                       |

| bit 6        | Unimplen         | nented: Read as '0'           |                                                       |

| bit 5        | OUT: Outp        | out State of the PWM module   |                                                       |

| bit 4        | POL: PWI         | M Output Polarity Control bit |                                                       |

|              | 1 = PWM          | output active state is low    |                                                       |

|              | 0 = PWM          | output active state is high   |                                                       |

| bit 3-2      | MODE<1:          | 0>: PWM Mode Control bits     |                                                       |

|              | 11 = Cent        | er-Aligned mode               |                                                       |

|              | 10 <b>= Togg</b> | le On Match mode              |                                                       |

|              | 01 = Set (       | On Match mode                 |                                                       |

|              | 00 = Stan        | dard PWM mode                 |                                                       |

bit 1-0 Unimplemented: Read as '0'

# PIC16(L)F1574/5/8/9

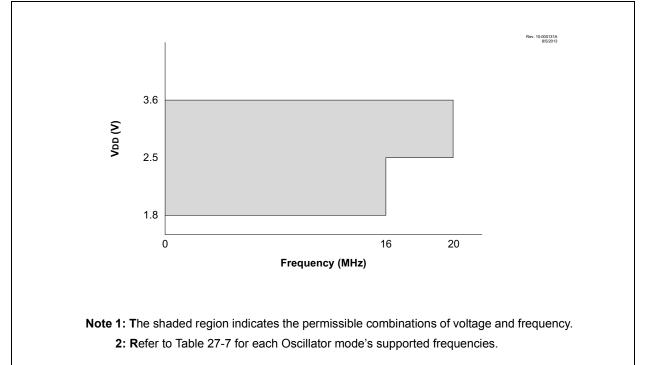

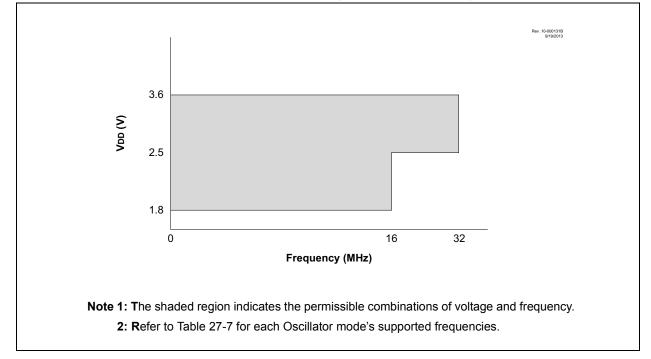

#### FIGURE 27-2: VOLTAGE FREQUENCY GRAPH, -40°C ≤ TA ≤ +125°C, PIC16LF1574/5/8/9 ONLY

# TABLE 27-4: I/O PORTS

| Param.<br>No. | Sym. | Characteristic                                   | Min.              | Тур† | Max.     | Units | Conditions                                                                 |  |  |  |

|---------------|------|--------------------------------------------------|-------------------|------|----------|-------|----------------------------------------------------------------------------|--|--|--|

|               | VIL  | Input Low Voltage                                |                   |      |          |       |                                                                            |  |  |  |

|               |      | I/O PORT:                                        |                   |      |          |       |                                                                            |  |  |  |

| D030          |      | with TTL buffer                                  | _                 |      | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

| D030A         |      |                                                  | _                 |      | 0.15 VDD | V     | $1.8V \le V \text{DD} \le 4.5V$                                            |  |  |  |

| D031          |      | with Schmitt Trigger buffer                      | _                 |      | 0.2 VDD  | V     | $2.0V \le V\text{DD} \le 5.5V$                                             |  |  |  |

|               |      | with I <sup>2</sup> C levels                     | _                 | _    | 0.3 Vdd  | V     |                                                                            |  |  |  |

|               |      | with SMbus levels                                | _                 |      | 0.8      | V     | $2.7V \le V\text{DD} \le 5.5V$                                             |  |  |  |

| D032          |      | MCLR                                             | _                 |      | 0.2 VDD  | V     |                                                                            |  |  |  |

|               | VIH  |                                                  |                   |      |          |       |                                                                            |  |  |  |

|               |      | I/O PORT:                                        |                   |      |          |       |                                                                            |  |  |  |

| D040          |      | with TTL buffer                                  | 2.0               | _    | —        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

| D040A         |      |                                                  | 0.25 VDD +<br>0.8 | _    | -        | V     | $1.8V \le V\text{DD} \le 4.5V$                                             |  |  |  |

| D041          |      | with Schmitt Trigger buffer                      | 0.8 Vdd           | _    | —        | V     | $2.0V \le V \text{DD} \le 5.5 V$                                           |  |  |  |

|               |      | with I <sup>2</sup> C levels                     | 0.7 Vdd           | _    | —        | V     |                                                                            |  |  |  |

|               |      | with SMbus levels                                | 2.1               | _    | —        | V     | $2.7V \le V\text{DD} \le 5.5V$                                             |  |  |  |

| D042          |      | MCLR                                             | 0.8 Vdd           | _    | —        | V     |                                                                            |  |  |  |

|               | lı∟  | Input Leakage Current <sup>(1)</sup>             |                   |      |          |       | ·                                                                          |  |  |  |

| D060          |      | I/O Ports                                        | —                 | ± 5  | ± 125    | nA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 85°C                    |  |  |  |

|               |      |                                                  | —                 | ± 5  | ± 1000   | nA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance, 125°C                    |  |  |  |

| D061          |      | MCLR <sup>(2)</sup>                              | —                 | ± 50 | ± 200    | nA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance, 85°C                     |  |  |  |

|               | IPUR | Weak Pull-up Current                             |                   |      |          |       | ·                                                                          |  |  |  |

| D070*         |      |                                                  | 25                | 100  | 200      | μΑ    | VDD = 3.3V, VPIN = VSS                                                     |  |  |  |

|               |      |                                                  | 25                | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                     |  |  |  |

|               | Vol  | Output Low Voltage                               |                   |      |          |       |                                                                            |  |  |  |

| D080          |      | I/O Ports                                        | _                 | _    | 0.6      | v     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |  |

| D090          | Voн  | Output High Voltage                              |                   |      |          |       |                                                                            |  |  |  |

|               |      | I/O Ports                                        | Vdd - 0.7         | _    | _        | v     | Іон = 3.5 mA, VDD = 5V<br>Іон = 3 mA, VDD = 3.3V<br>Іон = 1 mA, VDD = 1.8V |  |  |  |

|               |      | Capacitive Loading Specifications on Output Pins |                   |      |          |       |                                                                            |  |  |  |

| D101A*        | CIO  | All I/O pins                                     | _                 | _    | 50       | pF    |                                                                            |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

# 27.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| T                                          |                                       |     |                |  |  |  |  |

|--------------------------------------------|---------------------------------------|-----|----------------|--|--|--|--|

| F                                          | Frequency                             | Т   | Time           |  |  |  |  |

|                                            |                                       |     |                |  |  |  |  |

| Lowercase letters (pp) and their meanings: |                                       |     |                |  |  |  |  |

| рр                                         |                                       |     |                |  |  |  |  |

| CC                                         | CCP1                                  | OSC | CLKIN          |  |  |  |  |

| ck                                         | CLKOUT                                | rd  | RD             |  |  |  |  |

| CS                                         | CS                                    | rw  | RD or WR       |  |  |  |  |

| di                                         | SDIx                                  | SC  | SCKx           |  |  |  |  |

| do                                         | SDO                                   | SS  | SS             |  |  |  |  |

| dt                                         | Data in                               | tO  | ТОСКІ          |  |  |  |  |

| io                                         | I/O PORT                              | t1  | T1CKI          |  |  |  |  |

| mc                                         | MCLR                                  | wr  | WR             |  |  |  |  |

| Uppero                                     | Uppercase letters and their meanings: |     |                |  |  |  |  |

| S                                          |                                       |     |                |  |  |  |  |

| F                                          | Fall                                  | Р   | Period         |  |  |  |  |

| Н                                          | High                                  | R   | Rise           |  |  |  |  |

| I                                          | Invalid (High-impedance)              | V   | Valid          |  |  |  |  |

| L                                          | Low                                   | Z   | High-impedance |  |  |  |  |

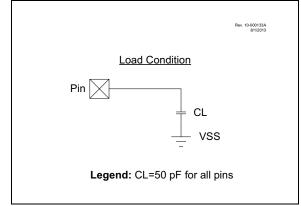

# FIGURE 27-4: LOAD CONDITIONS

# PIC16(L)F1574/5/8/9

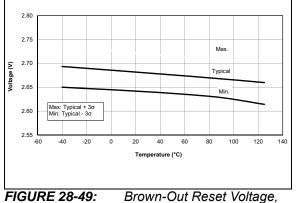

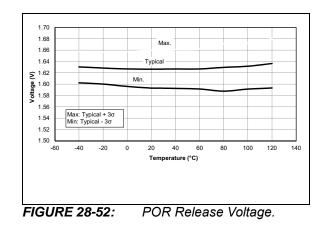

BORV = 0.

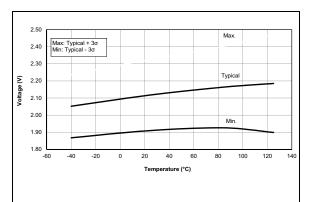

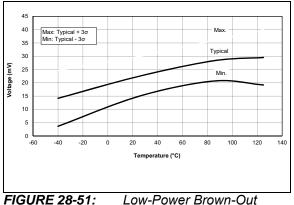

FIGURE 28-50: Low-Power Brown-Out Reset Voltage, LPBOR = 0.

Max.

Typical

Temperature (°C)

Min.

Reset Hysteresis, LPBOR = 0.

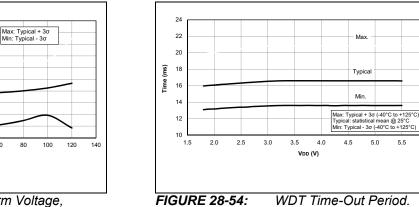

FIGURE 28-53: POR Rearm Voltage, PIC16F1574/5/8/9 Only.

-40

-20 0 20 40 60 80

1.54 1.52

1.50

1.48 **S**<sup>1.46</sup> 1.44 1.42

1.40

1.38

1.36

1.34

-60

5.0 5.5 6.0

# 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

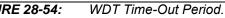

# Package Marking Information (Continued)

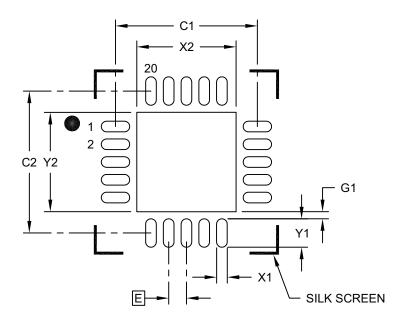

# 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |          |      |      |

|---------------------------------|-------------|----------|------|------|

| Dimension                       | MIN         | NOM      | MAX  |      |

| Contact Pitch                   | E           | 0.50 BSC |      |      |

| Optional Center Pad Width       | X2          |          |      | 2.80 |

| Optional Center Pad Length      | Y2          |          |      | 2.80 |

| Contact Pad Spacing             | C1          |          | 4.00 |      |

| Contact Pad Spacing             | C2          |          | 4.00 |      |

| Contact Pad Width (X20)         | X1          |          |      | 0.30 |

| Contact Pad Length (X20)        | Y1          |          |      | 0.80 |

| Contact Pad to Center Pad (X20) | G1          | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2255A

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0190-2

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.