# Microchip Technology - PIC16LF1578-E/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1578-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS

| 9.0  Watchdog Timer (WDT)  97    10.0  Flash Program Memory Control  101    11.0  I/O Ports  117    11.0  Peripheral Pin Select (PPS) Module  135    11.1  Interrupt-On-Change  141    14.0  Fixed Voltage Reference (FVR)  147    15.0  Interrupt-On-Change  141    14.0  Fixed Voltage Reference (FVR)  147    15.0  Temperature Indicator Module  152    16.0  Analog-to-Digital Converter (DAC) Module  152    17.0  Timer0 Module  166    18.0  Comparator Module  169    19.0  Timer1 Module with Gate Control.  176    10.1  Timer2 Module  189    21.0  Timer1 Module with Gate Control.  179    21.0  Timer1 Module  189    22.0  Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)  192    23.0  16-bit Pulse-Width Modulation (PWM) Module  220    24.0  Complementary Waveform Generator (CWG) Module  220    25.0  In-Circuit Serial Programming™ (ICSP™)  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.0   | Device Overview                                                           | 10    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------|-------|

| 4.0  Device Configuration  55    5.0  Oscillator Module  61    0.  Resets  73    7.0  Interrupts  81    8.0  Power-Down Mode (Sleep)  94    9.0  Watchdog Timer (WDT)  97    10.0  Flash Program Memory Control  101    11.0  I/O Ports  101    11.0  I/O Ports  117    12.0  Peripheral Pin Select (PPS) Module  135    13.0  Interrupt-On-Change  141    14.1  Fixed Voltage Reference (FVR)  141    15.0  Temperature Indicator Module  150    16.0  Analog-to-Digital Converter (ADC) Module  152    17.0  5-Bit Digital-to-Analog Converter (DAC) Module  169    19.0  Timer 0 Module  169    19.0  Timer 1 Module with Gate Control  176    10.1  Timer 2 Module  189    20.1  Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)  192    21.0  Timer 2 Module  260    21.0  In-circuit Serial Programming ™ (ICSP ™) </td <td>2.0</td> <td>Enhanced Mid-Range CPU</td> <td> 17</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.0   | Enhanced Mid-Range CPU                                                    | 17    |

| 5.0  Oscillator Module  61    6.0  Resets  73    7  Interrupts  81    8.0  Power-Down Mode (Sleep)  94    9.0  Watchdog Timer (WDT)  97    10.0  Flash Program Memory Control  101    110  I/O Ports  117    12.0  Peripheral Pin Select (PPS) Module  135    13.0  Interrupt-On-Change  141    14.0  Fixed Voltage Reference (FVR)  141    15.0  Temperature Indicator Module  150    16.0  Analog-to-Digital Converter (ADC) Module  150    17.0  5-Bit Digital-to-Analog Converter (DAC) Module  166    18.0  Comparator Module  169    19.0  Timer1 Module with Gate Control.  179    21.0  Timer2 Module  189    22.0  Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)  192    23.0  16-bit Pulse-Width Modulation (PWM) Module  220    24.0  Complementary Waveform Generator (CWG) Module  246    25.0  Instruction Set Summary  258                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.0   | Memory Organization                                                       | 19    |

| 6.0Resets737.0Interrupts818.0Power-Down Mode (Sleep)949.0Watchdog Timer (WDT)9710.0Flash Program Memory Control10111.0I/O Ports11712.0Peripheral Pin Select (PPS) Module13513.0Interrupt-On-Change14114.1Fixed Voltage Reference (FVR)14715.0Temperature Indicator Module15016.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer Of Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PVM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instructions Set Summary26027.0Electrical Specifications27428.0D cand AC Characteristics Graphs and Charts39829.0Development Support312310.Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Support339319Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.0   | Device Configuration                                                      | 55    |

| 7.0  Interrupts  81    8.0  Power-Down Mode (Sleep)  94    9.0  Watchdog Timer (WDT)  97    10.0  Flash Program Memory Control  101    11.0  I/O Ports  117    12.0  Peripheral Pin Select (PPS) Module  135    13.0  Interrupt-On-Change  141    14.0  Fixed Voltage Reference (FVR)  147    15.0  Temperature Indicator Module  152    16.0  Analog-to-Digital Converter (ADC) Module  152    17.0  5-Bit Digital-to-Analog Converter (DAC) Module  166    18.0  Comparator Module  169    19.0  Timer0 Module  176    0.0  Timer1 Module with Gate Control.  179    10.0  Timer2 Module  189    22.0  Enhanced Universal Synchronous Receiver Transmitter (EUSART)  192    23.0  16-bit Pulse-Widt Modulation (PWM) Module  220    24.0  Complementary Waveform Generator (CWG) Module  246    25.0  In-Circuit Serial Programming™ (ICSP™)  258    26.0  Instruction Set Summary  258                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.0   | Oscillator Module                                                         | 61    |

| 8.0  Power-Down Mode (Sleep)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.0   | Resets                                                                    | 73    |

| 9.0  Watchdog Timer (WDT)  97    10.0  Flash Program Memory Control  101    11.0  I/O Ports  117    11.0  Peripheral Pin Select (PPS) Module  135    13.0  Interrupt-On-Change  141    14.0  Fixed Voltage Reference (FVR)  147    15.0  Temperature Indicator Module  150    16.0  Analog-to-Digital Converter (ADC) Module  152    17.0  5-Bit Digital-to-Analog Converter (DAC) Module  166    18.0  Comparator Module  169    19.0  Timer0 Module  179    10.0  Timer1 Module with Gate Control.  179    10.1  Timer2 Module  189    21.0  Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)  192    19.1  Timer2 Module  220    22.0  Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)  192    23.0  16-bit Pulse-Width Modulation (PWM) Module  220    24.0  Complementary Waveform Generator (CWG) Module  226    25.0  In-Circuit Serial Programming ™ (ICSP™)  258    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.0   | Interrupts                                                                | 81    |

| 10.0  Flash Program Memory Control  101    11.0  I/O Ports  117    12.0  Peripheral Pin Select (PPS) Module  135    13.0  Interrupt-On-Change  141    14.0  Fixed Voltage Reference (FVR)  147    15.0  Temperature Indicator Module  150    16.0  Analog-to-Digital Converter (ADC) Module  152    17.0  5-Bit Digital-to-Analog Converter (DAC) Module  166    18.0  Comparator Module  169    19.0  Timer0 Module  176    20.0  Timer1 Module with Gate Control  176    21.0  Timer2 Module  189    22.0  Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)  192    23.0  16-bit Pulse-Width Modulation (PWM) Module  220    24.0  Complementary Waveform Generator (CWG) Module  226    25.0  In-Circuit Serial Programming™ (ICSP™)  258    26.0  Instruction Set Summary  260    27.0  Electrical Specifications  274    28.0  Dc and AC Characteristics Graphs and Charts  398    28.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8.0   | Power-Down Mode (Sleep)                                                   | 94    |

| 11.0  I/O Ports  117    12.0  Peripheral Pin Select (PPS) Module  135    13.0  Interrupt-On-Change  141    14.0  Fixed Voltage Reference (FVR)  147    14.0  Fixed Voltage Reference (FVR)  147    15.0  Temperature Indicator Module  150    16.0  Analog-to-Digital Converter (ADC) Module  152    17.0  5-Bit Digital-to-Analog Converter (DAC) Module  166    18.0  Comparator Module  166    18.0  Comparator Module  166    19.0  Timer0 Module  176    20.1  Timer1 Module with Gate Control  179    21.0  Timer2 Module  189    22.0  Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)  192    23.0  16-bit Pulse-Width Modulation (PWM) Module  220    24.0  Complementary Waveform Generator (CWG) Module  246    25.0  In-Circuit Serial Programming™ (ICSP™)  258    26.0  Instruction Set Summary  260    27.0  Electrical Specifications  374    28.0  DC and AC Charact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.0   | Watchdog Timer (WDT)                                                      | 97    |

| 12.0  Peripheral Pin Select (PPS) Module  135    13.0  Interrupt-On-Change  141    14.0  Fixed Voltage Reference (FVR)  147    15.0  Temperature Indicator Module  150    16.0  Analog-to-Digital Converter (ADC) Module  152    17.0  5-Bit Digital-to-Analog Converter (DAC) Module  166    18.0  Comparator Module  169    19.0  Timer0 Module  176    20.0  Timer1 Module with Gate Control  179    21.0  Timer2 Module  189    22.0  In-bit Pulse-Width Modulation (PWM) Module  220    23.0  16-bit Pulse-Width Modulation (PWM) Module  220    24.0  Complementary Waveform Generator (CWG) Module  246    25.0  In-Circuit Serial Programming™ (ICSP™)  258    26.0  Instruction Set Summary  260    27.0  Electrical Specifications  274    26.0  Characteristics Graphs and Charts  398    29.0  Development Support  312    30.0  Packaging Information  316    312  On Packaging Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10.0  | Flash Program Memory Control                                              | . 101 |

| 13.0Interrupt-On-Change14114.0Fixed Voltage Reference (FVR)14714.0Fixed Voltage Reference (FVR)14715.0Temperature Indicator Module15016.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27420.0Characteristics Graphs and Charts39829.0Development Support316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Change Notification Service339Customer Support339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11.0  |                                                                           |       |

| 14.0Fixed Voltage Reference (FVR)14715.0Temperature Indicator Module15016.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module16920.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support.316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12.0  | Peripheral Pin Select (PPS) Module                                        | . 135 |

| 15.0Temperature Indicator Module15016.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module17920.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13.0  | Interrupt-On-Change                                                       | . 141 |

| 16.0Analog-to-Digital Converter (ADC) Module15217.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Packaging Information316Appendix A: Data Sheet Revision History338Customer Change Notification Service339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14.0  | Fixed Voltage Reference (FVR)                                             | . 147 |

| 17.05-Bit Digital-to-Analog Converter (DAC) Module16618.0Comparator Module16919.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26827.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support.31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15.0  | Temperature Indicator Module                                              | . 150 |

| 18.0Comparator Module16919.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support.311230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16.0  | Analog-to-Digital Converter (ADC) Module                                  | . 152 |

| 19.0Timer0 Module17620.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History339Customer Change Notification Service339Customer Support339Customer Support339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17.0  | 5-Bit Digital-to-Analog Converter (DAC) Module                            | . 166 |

| 20.0Timer1 Module with Gate Control17921.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18.0  | Comparator Module                                                         | . 169 |

| 21.0Timer2 Module18922.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19.0  | Timer0 Module                                                             | . 176 |

| 22.0Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)19223.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20.0  | Timer1 Module with Gate Control                                           | . 179 |

| 23.016-bit Pulse-Width Modulation (PWM) Module22024.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                           |       |

| 24.0Complementary Waveform Generator (CWG) Module24625.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | . 192 |

| 25.0In-Circuit Serial Programming™ (ICSP™)25826.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23.0  | 16-bit Pulse-Width Modulation (PWM) Module                                | . 220 |

| 26.0Instruction Set Summary26027.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24.0  | Complementary Waveform Generator (CWG) Module                             | . 246 |

| 27.0Electrical Specifications27428.0DC and AC Characteristics Graphs and Charts39829.0Development Support31230.0Packaging Information316Appendix A: Data Sheet Revision History338The Microchip Website339Customer Change Notification Service339Customer Support339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25.0  | In-Circuit Serial Programming™ (ICSP™)                                    | . 258 |

| 28.0  DC and AC Characteristics Graphs and Charts  398    29.0  Development Support  312    30.0  Packaging Information  316    Appendix A: Data Sheet Revision History  338    The Microchip Website  339    Customer Change Notification Service  339    Customer Support  339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26.0  | Instruction Set Summary                                                   | . 260 |

| 29.0  Development Support  312    30.0  Packaging Information  316    Appendix A: Data Sheet Revision History  338    The Microchip Website  339    Customer Change Notification Service  339    Customer Support  339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27.0  | Electrical Specifications                                                 | . 274 |

| 30.0  Packaging Information  316    Appendix A: Data Sheet Revision History  338    The Microchip Website  339    Customer Change Notification Service  339    Customer Support  339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28.0  |                                                                           |       |

| Appendix A: Data Sheet Revision History  338    The Microchip Website  339    Customer Change Notification Service  339    Customer Support  339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29.0  | Development Support                                                       | . 312 |

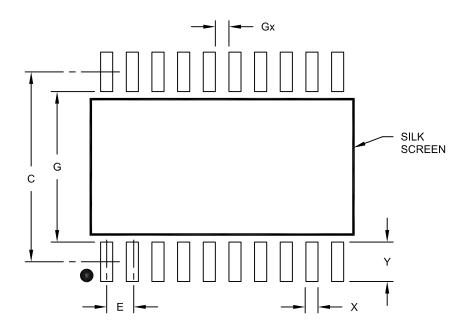

| The Microchip Website                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30.0  | Packaging Information                                                     | . 316 |

| Customer Change Notification Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                           |       |

| Customer Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                                           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | •                                                                         |       |

| Deside at late at late Original and the Original Action of the Origi |       | ••                                                                        |       |

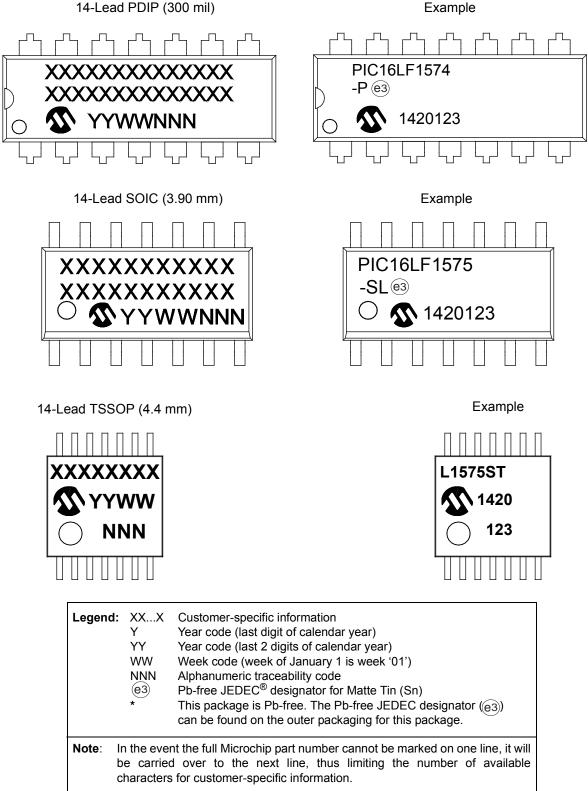

| Product identification System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Produ | uct Identification System                                                 | . 340 |

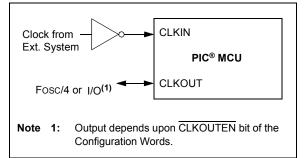

# 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 oscillator during run-time, or