Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1578-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-15: SPECIAL FUNCTION REGISTER SUMMARY

| Address | Name                        | Bit 7                                                                                                       | Bit 6                             | Bit 5  | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|---------|-------|--------|--------|-----------|----------------------|---------------------------------|

| Bank 0  |                             |                                                                                                             |                                   |        |         |       |        |        |           |                      |                                 |

| 00Ch    | PORTA                       | _                                                                                                           | _                                 | RA5    | RA4     | RA3   | RA2    | RA1    | RA0       | xx xxxx              | xx xxxx                         |

| 00Dh    | PORTB <sup>(1)</sup>        | RB7                                                                                                         | RB6                               | RB5    | RB4     | —     | —      |        | —         | xxxx                 | xxxx                            |

| 00Eh    | PORTC                       | RC7 <sup>(1)</sup>                                                                                          | RC6 <sup>(1)</sup>                | RC5    | RC4     | RC3   | RC2    | RC1    | RC0       | xxxx xxxx            | xxxx xxxx                       |

| 00Fh    | —                           | Unimplemen                                                                                                  | nted                              |        |         |       |        |        |           | _                    | _                               |

| 010h    | —                           | Unimplemen                                                                                                  | nted                              |        |         |       |        |        |           | _                    | _                               |

| 011h    | PIR1                        | TMR1GIF                                                                                                     | ADIF                              | RCIF   | TXIF    | —     | —      | TMR2IF | TMR1IF    | 000000               | 000000                          |

| 012h    | PIR2                        | _                                                                                                           | C2IF                              | C1IF   | _       | —     | —      | _      | —         | -00                  | -00                             |

| 013h    | PIR3                        | PWM4IF                                                                                                      | PWM3IF                            | PWM2IF | PWM1IF  | —     | —      | _      | —         | 0000                 | 0000                            |

| 014h    | —                           |                                                                                                             |                                   |        |         |       |        |        |           | —                    | —                               |

| 015h    | TMR0                        | Holding Register for the 8-bit Timer0 Count                                                                 |                                   |        |         |       |        |        | xxxx xxxx | uuuu uuuu            |                                 |

| 016h    | TMR1L                       | Holding Register for the Least Significant Byte of the 16-bit TMR1 Count                                    |                                   |        |         |       |        |        |           | xxxx xxxx            | uuuu uuuu                       |

| 017h    | TMR1H                       | Holding Register for the Most Significant Byte of the 16-bit TMR1 Count                                     |                                   |        |         |       |        |        |           | xxxx xxxx            | uuuu uuuu                       |

| 018h    | T1CON                       | TMR1C                                                                                                       | S<1:0>                            | T1CK   | PS<1:0> | —     | T1SYNC | _      | TMR10N    | 0000 -0-0            | uuuu -u-u                       |

| 019h    | T1GCON                      | TMR1GE         T1GPOL         T1GTM         T1GSPM         T1GGO/<br>DONE         T1GVAL         T1GSS<1:0> |                                   |        |         |       |        |        | 0000 0x00 | uuuu uxuu            |                                 |

| 01Ah    | TMR2 Timer2 Module Register |                                                                                                             |                                   |        |         |       |        |        | 0000 0000 | 0000 0000            |                                 |

| 01Bh    | PR2                         | Timer2 Period Register                                                                                      |                                   |        |         |       |        |        | 1111 1111 | 1111 1111            |                                 |

| 01Ch    | T2CON                       | _                                                                                                           | - T20UTPS<3:0> TMR20N T2CKPS<1:0> |        |         |       |        |        |           | -000 0000            | -000 0000                       |

| 01Dh    | _                           | Unimplemented                                                                                               |                                   |        |         |       |        |        | _         | _                    |                                 |

| 01Eh    | —                           | Unimplemented                                                                                               |                                   |        |         |       |        |        |           | _                    |                                 |

| 01Fh    | —                           | Unimplemer                                                                                                  | nted                              |        |         |       |        |        |           | _                    | _                               |

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16(L)F1578/9 only.

2:

PIC16F1574/5/8/9 only.

3: Unimplemented, read as '1'.

| TABLE 3-15: S | SPECIAL FUNCTION REGISTER SUMMAI | RY (CONTINUED) |

|---------------|----------------------------------|----------------|

|---------------|----------------------------------|----------------|

| Address | Name                   | Bit 7                                               | Bit 6                                          | Bit 5                           | Bit 4  | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------------------|-----------------------------------------------------|------------------------------------------------|---------------------------------|--------|-------|-------|-----------|-----------|----------------------|---------------------------------|

| Bank 3  |                        |                                                     |                                                |                                 |        |       |       |           |           |                      |                                 |

| 18Ch    | ANSELA                 | _                                                   | _                                              | _                               | ANSA4  | —     | ANSA2 | ANSA1     | ANSA0     | 1 -111               | 1 -111                          |

| 18Dh    | ANSELB <sup>(1)</sup>  | _                                                   | _                                              | ANSB5                           | ANSB4  | —     | —     | _         | —         | 11                   | 11                              |

| 18Eh    | ANSELC                 | ANSC7 <sup>(1)</sup>                                | ANSC6 <sup>(1)</sup>                           | _                               | _      | ANSC3 | ANSC2 | ANSC1     | ANSC0     | 11 1111              | 11 1111                         |

| 18Fh    | —                      | Unimplemen                                          | nted                                           |                                 |        |       |       |           |           | _                    | _                               |

| 190h    | _                      | Unimplemer                                          | nted                                           |                                 |        |       |       |           |           | _                    | _                               |

| 191h    | PMADRL                 | Flash Progra                                        | Flash Program Memory Address Register Low Byte |                                 |        |       |       |           |           | 0000 0000            | 0000 0000                       |

| 192h    | PMADRH                 |                                                     |                                                |                                 |        |       |       |           | 1000 0000 | 1000 0000            |                                 |

| 193h    | PMDATL                 | Flash Program Memory Read Data Register Low Byte    |                                                |                                 |        |       |       |           | xxxx xxxx | uuuu uuuu            |                                 |

| 194h    | PMDATH                 | — Flash Program Memory Read Data Register High Byte |                                                |                                 |        |       |       |           | xx xxxx   | uu uuuu              |                                 |

| 195h    | PMCON1                 | (3)                                                 | CFGS                                           | CFGS LWLO FREE WRERR WREN WR RD |        |       |       |           | 1000 x000 | 1000 q000            |                                 |

| 196h    | PMCON2                 | Flash Progra                                        | am Memory (                                    | Control Regis                   | ster 2 | •     | •     |           | •         | 0000 0000            | 0000 0000                       |

| 197h    | VREGCON <sup>(2)</sup> | _                                                   | — — — — — VREGPM Reserved                      |                                 |        |       |       |           | 01        | 01                   |                                 |

| 198h    | _                      | Unimplemer                                          | Unimplemented                                  |                                 |        |       |       |           |           | _                    | _                               |

| 199h    | RCREG                  | USART Rec                                           | USART Receive Data Register                    |                                 |        |       |       |           |           | 0000 0000            | 0000 0000                       |

| 19Ah    | TXREG                  | USART Transmit Data Register                        |                                                |                                 |        |       |       |           | 0000 0000 | 0000 0000            |                                 |

| 19Bh    | SPBRGL                 | Baud Rate Generator Data Register Low               |                                                |                                 |        |       |       | 0000 0000 | 0000 0000 |                      |                                 |

| 19Ch    | SPBRGH                 | Baud Rate Generator Data Register High              |                                                |                                 |        |       |       |           | 0000 0000 | 0000 0000            |                                 |

| 19Dh    | RCSTA                  | SPEN                                                | RX9                                            | SREN                            | CREN   | ADDEN | FERR  | OERR      | RX9D      | 0000 000x            | 0000 000x                       |

| 19Eh    | TXSTA                  | CSRC                                                | TX9                                            | TXEN                            | SYNC   | SENDB | BRGH  | TRMT      | TX9D      | 0000 0010            | 0000 0010                       |

| 19Fh    | BAUDCON                | ABDOVF                                              | RCIDL                                          | -                               | SCKP   | BRG16 | —     | WUE       | ABDEN     | 01-0 0-00            | 01-0 0-00                       |

Legend: x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. Note 1: PIC16(L)F1578/9 only.

PIC16F1574/5/8/9 only.

Unimplemented, read as '1'.

## 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

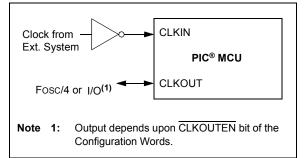

#### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the CLKIN input. CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through the Fosc bits in the Configuration Words:

- ECH High power, 4-20 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

The Oscillator Start-up Timer (OST), when available, is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-On Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

#### 5.2.2.7 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<1:0> = 00).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<1:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

#### 5.2.2.8 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-3). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-3 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables of **Section 27.0 "Electrical Specifications"**.

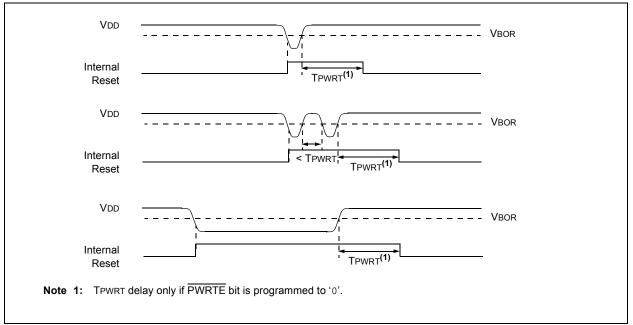

## 6.3 Register Definitions: BOR Control

#### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-Out Reset Enable bit                                          |

|---------|--------------------------------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words = 01:                                          |

|         | 1 = BOR Enabled                                                                      |

|         | 0 = BOR Disabled                                                                     |

|         | If BOREN <1:0> in Configuration Words <u>≠ 01</u> :                                  |

|         | SBOREN is read/write, but has no effect on the BOR                                   |

| bit 6   | BORFS: Brown-Out Reset Fast Start bit <sup>(1)</sup>                                 |

|         | If BOREN <1:0> = 10 (Disabled in Sleep) or BOREN<1:0> = 01 (Under software control): |

|         | 1 = Band gap is forced on always (covers sleep/wake-up/operating cases)              |

|         | 0 = Band gap operates normally, and may turn off                                     |

|         | <u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u>    |

|         | BORFS is Read/Write, but has no effect.                                              |

| bit 5-1 | Unimplemented: Read as '0'                                                           |

| bit 0   | BORRDY: Brown-Out Reset Circuit Ready Status bit                                     |

|         | 1 = The Brown-out Reset circuit is active                                            |

|         | 0 = The Brown-out Reset circuit is inactive                                          |

| Note di | DODEN 41/02 hits are leasted in Canfiguration Wards                                  |

#### **Note 1:** BOREN<1:0> bits are located in Configuration Words.

© 2016 Microchip Technology Inc.

# PIC16(L)F1574/5/8/9

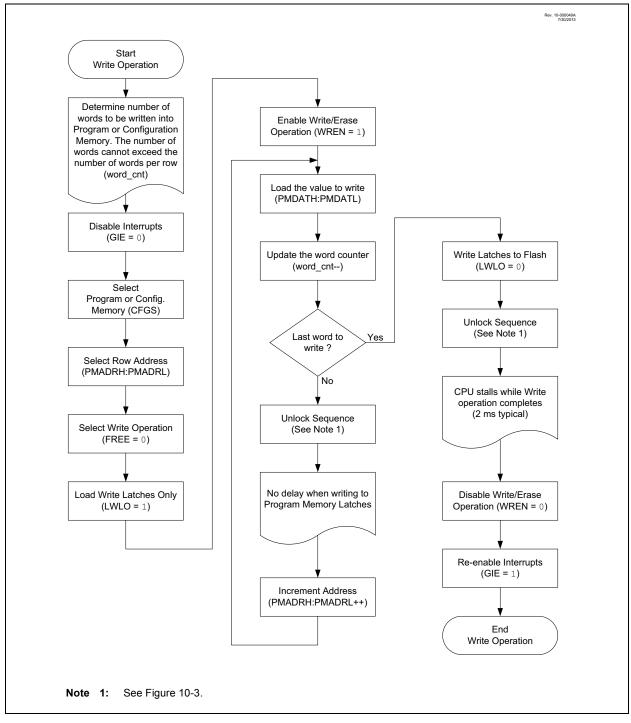

#### EXAMPLE 10-3: WRITING TO FLASH PROGRAM MEMORY

| ; This               | write rout:    | ine assumes the f | ollowing:                                                  |

|----------------------|----------------|-------------------|------------------------------------------------------------|

|                      |                |                   | starting at the address in DATA_ADDR                       |

| ; 2. Ea              | ach word of    | data to be writt  | en is made up of two adjacent bytes in DATA_ADDR,          |

| ; store              | ed in little   | e endian format   |                                                            |

| ; 3. A               | valid star     | ting address (the | Least Significant bits = 00000) is loaded in ADDRH:ADDRL   |

| ; 4. AI              | DDRH and ADI   | DRL are located i | n shared data memory 0x70 - 0x7F (common RAM)              |

| ;                    |                |                   |                                                            |

|                      | BCF            | INTCON,GIE        | ; Disable ints so required sequences will execute properly |

|                      | BANKSEL        | PMADRH            | ; Bank 3                                                   |

|                      | MOVF           | ADDRH,W           | ; Load initial address                                     |

|                      | MOVWF          | PMADRH            | ;                                                          |

|                      | MOVF           | ADDRL,W           | ;                                                          |

|                      | MOVWF          | PMADRL            | ;                                                          |

|                      | MOVLW          | _                 | ; Load initial data address                                |

|                      | MOVWF          | FSROL             | ;                                                          |

|                      | MOVLW          | _                 | ; Load initial data address                                |

|                      | MOVWF          | FSR0H             | i and a set                                                |

|                      | BCF            |                   | ; Not configuration space                                  |

|                      | BSF            |                   | ; Enable writes                                            |

| TOOD                 | BSF            | PMCON1,LWLO       | ; Only Load Write Latches                                  |

| LOOP                 | MOUTH          | FCDOLL            | · Load first data buto into lower                          |

|                      | MOVIW<br>MOVWF | FSR0++<br>PMDATL  | ; Load first data byte into lower<br>:                     |

|                      | MOVWF<br>MOVIW |                   | '<br>; Load second data byte into upper                    |

|                      | MOVWF          |                   | ;                                                          |

|                      | HOVWE          | INDAIN            | '                                                          |

|                      | MOVF           | PMADRL,W          | ; Check if lower bits of address are '00000'               |

|                      | XORLW          |                   | ; Check if we're on the last of 32 addresses               |

|                      | ANDLW          |                   | ;                                                          |

|                      | BTFSC          |                   | ; Exit if last of 32 words,                                |

|                      | GOTO           | START_WRITE       | ;                                                          |

|                      |                |                   |                                                            |

|                      | MOVLW          |                   | ; Start of required write sequence:                        |

|                      | MOVWF          |                   | ; Write 55h                                                |

| ed                   | MOVLW          |                   | ;<br>                                                      |

| Required<br>Sequence | MOVWF          |                   | ; Write AAh                                                |

| seq.                 | BSF            |                   | ; Set WR bit to begin write                                |

| щω                   | NOP            |                   | ; NOP instructions are forced as processor                 |

|                      | NOD            |                   | ; loads program memory write latches                       |

|                      | NOP            |                   | ;                                                          |

|                      | INCF           | PMADRL, F         | ; Still loading latches Increment address                  |

|                      | GOTO           | LOOP              | ; Write next latches                                       |

|                      |                |                   |                                                            |

| START_V              | VRITE          |                   |                                                            |

|                      | BCF            | PMCON1,LWLO       | ; No more loading latches - Actually start Flash program   |

|                      |                |                   | ; memory write                                             |

|                      | MOUT           | r r b             |                                                            |

|                      | MOVLW          |                   | ; Start of required write sequence:                        |

| 0)                   | MOVWF<br>MOVLW | PMCON2<br>0AAh    | ; Write 55h<br>:                                           |

| Required<br>Sequence | MOVLW<br>MOVWF |                   | ,<br>; Write AAh                                           |

| inb                  | BSF            |                   | ; Set WR bit to begin write                                |

| Sec                  | NOP            |                   | ; NOP instructions are forced as processor writes          |

|                      | 1101           |                   | ; all the program memory write latches simultaneously      |

|                      | NOP            |                   | i to program memory.                                       |

|                      |                |                   | ; After NOPs, the processor                                |

|                      |                |                   | ; stalls until the self-write process in complete          |

|                      |                |                   | ; after write processor continues with 3rd instruction     |

|                      | BCF            |                   | ; Disable writes                                           |

|                      | BSF            | INTCON,GIE        | ; Enable interrupts                                        |

|                      |                |                   |                                                            |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|---------|---------|---------|---------|-------|-------|-------|-------|---------------------|

| ANSELB  | —       | —       | ANSB5   | ANSB4   | —     | —     | —     | —     | 127                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | —     | —     | _     | _     | 128                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | —     | —     | _     | _     | 126                 |

| ODCONB  | ODB7    | ODB6    | ODB5    | ODB4    | —     | —     | _     | _     | 128                 |

| PORTB   | RB7     | RB6     | RB5     | RB4     | —     | —     | _     | _     | 126                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | —     | —     | _     | _     | 128                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | _     | —     | —     | —     | 128                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   |       | —     | _     | _     | 127                 |

|  | TABLE 11-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--|-------------|--------------------------------------------|

|--|-------------|--------------------------------------------|

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

#### 12.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

**Note:** The I<sup>2</sup>C default input pins are I<sup>2</sup>C and SMBus compatible and are the only pins on the device with this compatibility.

#### 12.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 12-1.

EXAMPLE 12-1: PPS LOCK/UNLOCK SEQUENCE

| the second destruction with a            |

|------------------------------------------|

| ; suspend interrupts                     |

| bcf INTCON,GIE                           |

| ; BANKSEL PPSLOCK ; set bank             |

| ; required sequence, next 5 instructions |

| movlw 0x55                               |

| movwf PPSLOCK                            |

| movlw 0xAA                               |

| movwf PPSLOCK                            |

| ; Set PPSLOCKED bit to disable writes or |

| ; Clear PPSLOCKED bit to enable writes   |

| bsf PPSLOCK, PPSLOCKED                   |

| ; restore interrupts                     |

| bsf INTCON,GIE                           |

|                                          |

#### 12.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

## 12.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

## 12.7 Effects of a Reset

A device Power-On-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in Table 12-1.

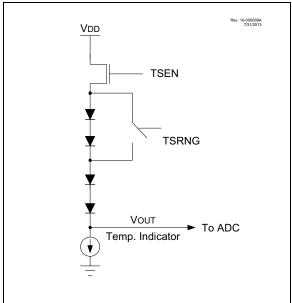

## 15.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, "Use and Calibration of the Internal Temperature Indicator" (DS01333) for more details regarding the calibration process.

#### 15.1 Circuit Operation

Figure 15-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 15-1 describes the output characteristics of the temperature indicator.

#### EQUATION 15-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

# FIGURE 15-1: TEMPERATURE CIRCUIT DIAGRAM

## 15.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 15-1 shows the recommended minimum VDD vs. range setting.

TABLE 15-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

## **15.3** Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 16.0 "Analog-to-Digital Converter (ADC) Module**" for detailed information.

## 15.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

| Name   | Bit 7                    | Bit 6  | Bit 5     | Bit 4    | Bit 3 | Bit 2   | Bit 1    | Bit 0    | Register<br>on Page |

|--------|--------------------------|--------|-----------|----------|-------|---------|----------|----------|---------------------|

| ADCON0 | —                        |        |           | CHS<4:0> |       |         | GO/DONE  | ADON     | 158                 |

| ADCON1 | ADFM                     |        | ADCS<2:0> |          | —     | —       | ADPRE    | F<1:0>   | 159                 |

| ADCON2 |                          | TRIGSE | EL<3:0>   |          | —     | _       | —        |          | 160                 |

| ADRESH | ADC Result Register High |        |           |          |       |         |          | 161, 162 |                     |

| ADRESL | ADC Result Register Low  |        |           |          |       |         | 161, 162 |          |                     |

| ANSELA | _                        | _      | _         | ANSA4    | —     | ANSA2   | ANSA1    | ANSA0    | 121                 |

| INTCON | GIE                      | PEIE   | TMR0IE    | INTE     | IOCIE | TMR0IF  | INTF     | IOCIF    | 86                  |

| PIE1   | TMR1GIE                  | ADIE   | RCIE      | TXIE     | —     | —       | TMR2IE   | TMR1IE   | 87                  |

| PIR1   | TMR1GIF                  | ADIF   | RCIF      | TXIF     | —     | —       | TMR2IF   | TMR1IF   | 90                  |

| TRISA  |                          |        | TRISA5    | TRISA4   | —(1)  | TRISA2  | TRISA1   | TRISA0   | 120                 |

| FVRCON | FVREN                    | FVRRDY | TSEN      | TSRNG    | CDAFV | ′R<1:0> | ADFV     | R<1:0>   | 149                 |

TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

**Note 1:** Unimplemented, read as '1'.

| Name    | Bit 7                         | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|-------|--------|-------|-------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL | —      | SCKP  | BRG16 | —      | WUE    | ABDEN  | 204                 |

| INTCON  | GIE                           | PEIE  | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1    | TMR1GIE                       | ADIE  | RCIE   | TXIE  | —     | _      | TMR2IE | TMR1IE | 87                  |

| PIR1    | TMR1GIF                       | ADIF  | RCIF   | TXIF  | —     | —      | TMR2IF | TMR1IF | 90                  |

| RCSTA   | SPEN                          | RX9   | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 203*                |

| SPBRGL  | BRG<7:0>                      |       |        |       |       |        |        | 205*   |                     |

| SPBRGH  | BRG<15:8>                     |       |        |       |       |        | 205*   |        |                     |

| TXREG   | EUSART Transmit Data Register |       |        |       |       |        | 194    |        |                     |

| TXSTA   | CSRC                          | TX9   | TXEN   | SYNC  | SENDB | BRGH   | TRMT   | TX9D   | 202                 |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous transmission.

\* Page provides register information.

| R/W-0/0          | R-1/1                                                           | U-0                                                                                                     | R/W-0/0                              | R/W-0/0           | U-0          | R/W-0/0           | R/W-0/0      |  |  |  |  |

|------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|--------------|-------------------|--------------|--|--|--|--|

| ABDOVF           | RCIDL                                                           |                                                                                                         | SCKP                                 | BRG16             | _            | WUE               | ABDEN        |  |  |  |  |

| bit 7            | •                                                               |                                                                                                         |                                      |                   |              |                   | bit C        |  |  |  |  |

|                  |                                                                 |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

| Legend:          |                                                                 |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

| R = Readable     | e bit                                                           | W = Writable                                                                                            | e bit                                | U = Unimplem      |              |                   |              |  |  |  |  |

| u = Bit is unch  | nanged                                                          | x = Bit is un                                                                                           | known                                | -n/n = Value at   | POR and BC   | DR/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is set |                                                                 | '0' = Bit is cl                                                                                         | eared                                |                   |              |                   |              |  |  |  |  |

| bit 7            |                                                                 | Auto-Baud Dete                                                                                          | ect Overflow bit                     |                   |              |                   |              |  |  |  |  |

| Sit 1            | Asynchrono                                                      |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

|                  |                                                                 | ud timer overflo                                                                                        | owed                                 |                   |              |                   |              |  |  |  |  |

|                  |                                                                 | ud timer did no                                                                                         | t overflow                           |                   |              |                   |              |  |  |  |  |

|                  | <u>Synchronou</u><br>Don't care                                 | <u>is mode</u> :                                                                                        |                                      |                   |              |                   |              |  |  |  |  |

| bit 6            |                                                                 | ceive Idle Flag I                                                                                       | oit                                  |                   |              |                   |              |  |  |  |  |

|                  | <u>Asynchrono</u>                                               | •                                                                                                       |                                      |                   |              |                   |              |  |  |  |  |

|                  | 1 = Receive                                                     |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

|                  |                                                                 | <ul> <li>0 = Start bit has been received and the receiver is receiving<br/>Synchronous mode:</li> </ul> |                                      |                   |              |                   |              |  |  |  |  |

|                  | Don't care                                                      |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

| bit 5            | Unimpleme                                                       | ented: Read as                                                                                          | ·'0'                                 |                   |              |                   |              |  |  |  |  |

| bit 4            | SCKP: Syne                                                      | chronous Clock                                                                                          | Polarity Select                      | bit               |              |                   |              |  |  |  |  |

|                  | Asynchronous mode:                                              |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

|                  |                                                                 |                                                                                                         | to the TX/CK pi<br>data to the TX/0  |                   |              |                   |              |  |  |  |  |

|                  | Synchronous mode:                                               |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

|                  |                                                                 |                                                                                                         | ng edge of the c<br>ng edge of the c |                   |              |                   |              |  |  |  |  |

| bit 3            | BRG16: 16-                                                      | -bit Baud Rate                                                                                          | Generator bit                        |                   |              |                   |              |  |  |  |  |

|                  |                                                                 | Baud Rate Generaud Rate Generation                                                                      |                                      |                   |              |                   |              |  |  |  |  |

| bit 2            | Unimpleme                                                       | ented: Read as                                                                                          | '0'                                  |                   |              |                   |              |  |  |  |  |

| bit 1            | WUE: Wake                                                       | WUE: Wake-up Enable bit                                                                                 |                                      |                   |              |                   |              |  |  |  |  |

|                  | Asynchronous mode:                                              |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

|                  | automat                                                         | ically clear afte                                                                                       | r RCIF is set.                       | lo character will | be received, | RCIF bit will be  | set. WUE wil |  |  |  |  |

|                  | 0 = Receiver is operating normally<br><u>Synchronous mode</u> : |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

|                  | Don't care                                                      | is mode.                                                                                                |                                      |                   |              |                   |              |  |  |  |  |

| bit 0            | ABDEN: Auto-Baud Detect Enable bit                              |                                                                                                         |                                      |                   |              |                   |              |  |  |  |  |

|                  |                                                                 | Asynchronous mode:                                                                                      |                                      |                   |              |                   |              |  |  |  |  |

|                  | -                                                               |                                                                                                         | de is enabled (c                     | lears when auto   | -baud is com | iplete)           |              |  |  |  |  |

|                  | 0 = Auto-Ba                                                     | aud Detect mod                                                                                          |                                      |                   |              | -                 |              |  |  |  |  |

|                  |                                                                 | Synchronous mode:                                                                                       |                                      |                   |              |                   |              |  |  |  |  |

|                  | Don't care                                                      | <u>io mode</u> .                                                                                        |                                      |                   |              |                   |              |  |  |  |  |

#### REGISTER 22-3: BAUDCON: BAUD RATE CONTROL REGISTER

#### 22.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|

|       | the corresponding ANSEL bit must be        |  |  |  |  |

|       | cleared for the receiver to function.      |  |  |  |  |

#### 22.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

Note: If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

#### 22.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters

will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 22.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

# 22.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | PH<     | 15:8>          |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | mented bit, read | d as '0'       |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

#### REGISTER 23-7: PWMxPHH: PWMx PHASE COUNT HIGH REGISTER

bit 7-0 **PH<15:8>**: PWM Phase High bits Upper eight bits of PWM phase count

#### REGISTER 23-8: PWMxPHL: PWMx PHASE COUNT LOW REGISTER

| R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------------|---------|---------|---------|---------|---------|---------|---------|

|             |         |         | PH<     | 7:0>    |         |         |         |

| bit 7 bit 0 |         |         |         |         |         | bit 0   |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PH<7:0>**: PWM Phase Low bits Lower eight bits of PWM phase count

Г

## 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- Multiple projects

- · Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- Local file history feature

- · Built-in support for Bugzilla issue tracker

#### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

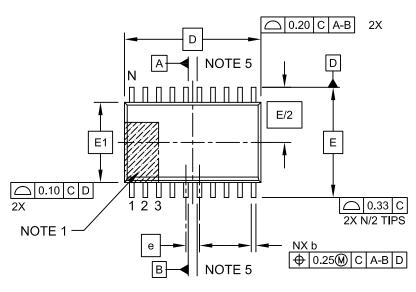

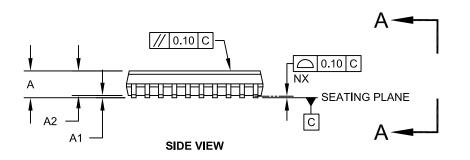

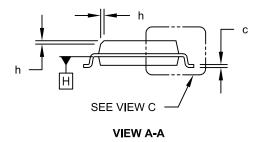

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2

# APPENDIX A: DATA SHEET REVISION HISTORY

## **Revision A (2/2015)**

Initial release of this document.

## **Revision B (09/2015)**

Added Section 5.4: Clock Switching Before Sleep.

Updated Low-Power Features and Memory sections on cover page.

Updated Examples 3-2 and 16-1; Figures 8-1, 22-1, and 23-8 through 23-13; Registers 8-1, 23-6, 24-2, and 24-3; Sections 8.2.2, 16.2.6, 22.0, 23.3.3, 24.9.1.2, 24.11.1 and 27.1; and Tables 27-1, 27-2, 27-3, 27-8 and 27-11.

## **Revision C (01/2016)**

Added graphs to chapter "DC and AC Characteristics Graphs and Charts". Other minor corrections.

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support