Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1579-e-gz |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- · Indirect Addressing

# 3.1 **Program Memory Organization**

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (See Figure 3-1).

# 3.2 High-Endurance Flash

This device has a 128-byte section of high-endurance Program Flash Memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash **Program Memory Overview**" for more information on writing data to PFM. See Section 3.3.2 "Special Function Register" for more information about using the SFR registers to read byte data stored in PFM.

### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device          | Program Memory<br>Space (Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |

|-----------------|---------------------------------|--------------------------------|-------------------------------------------------------------|

| PIC16(L)F1574/8 | 4,096                           | 0FFFh                          | 0F80h-0FFFh                                                 |

| PIC16(L)F1575/9 | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |

Note 1: High-endurance Flash applies to the low byte of each address in the range.

| REGISTER        | 4-2: CON                                | FIGURATION                                                    | WORD 2                                        |                                     |                  |                                              |            |

|-----------------|-----------------------------------------|---------------------------------------------------------------|-----------------------------------------------|-------------------------------------|------------------|----------------------------------------------|------------|

|                 |                                         | R/P-1                                                         | R/P-1                                         | R/P-1                               | R/P-1            | R/P-1                                        | R/P-1      |

|                 |                                         | LVP <sup>(1)</sup>                                            | DEBUG <sup>(2)</sup>                          | BORV <sup>(3)</sup>                 | STVREN           | PLLEN                                        |            |

|                 |                                         | bit 13                                                        |                                               |                                     |                  |                                              | bit 8      |

| U-1             | U-1                                     | U-1                                                           | U-1                                           | U-1                                 | R/P-1            | R/P-1                                        | R/P-1      |

| _               |                                         |                                                               |                                               |                                     | PPS1WAY          | WRT                                          | <1:0>      |

| bit 7           |                                         |                                                               |                                               |                                     |                  | •                                            | bit 0      |

|                 |                                         |                                                               |                                               |                                     |                  |                                              |            |

| Legend:         |                                         |                                                               |                                               |                                     |                  |                                              |            |

| R = Readab      |                                         | P = Programr                                                  |                                               |                                     | nented bit, read |                                              |            |

| '0' = Bit is cl | eared                                   | '1' = Bit is set                                              |                                               | n = Value whe                       | en blank or afte | r Bulk Erase                                 |            |

| bit 13          | 1 = ON -<br>0 = OFF -                   | ltage Program<br>Low-voltage<br>Configuration<br>High Voltage | programming<br>bit is ignored.<br>on MCLR/VPP | enabled. MC                         | •                |                                              | CLR. MCLRE |

| bit 12          | 1 = OFF -<br>0 = ON -                   | bugger Mode bi<br>In-Circuit Debu<br>In-Circuit Debu          | igger disabled;<br>igger enabled;             | ICSPCLK and                         |                  |                                              |            |

| bit 11          | 1 = OFF -                               | Low-Power Bro<br>Low-power Bro<br>Low-power Bro               | own-out Reset                                 | is disabled                         |                  |                                              |            |

| bit 10          | 1 = LOW -                               | n-out Reset Vol<br>Brown-out Res<br>Brown-out Res             | et voltage (VB                                | OR), <mark>low trip po</mark> i     |                  |                                              |            |

| bit 9           | 1 = ON -                                | ack Overflow/U<br>Stack Overflow<br>Stack Overflow            | or Underflow                                  | will cause a Re                     |                  |                                              |            |

| bit 8           |                                         | Enable bit<br>4xPLL enabled<br>4xPLL disabled                 |                                               |                                     |                  |                                              |            |

| bit 7-3         | Unimplemer                              | nted: Read as '                                               | 1'                                            |                                     |                  |                                              |            |

| bit 2           | <b>PPS1WAY</b> : F<br>1 = ON<br>0 = OFF | PPSLOCK is se                                                 | bit can only be<br>et, all future cha         | set once after a<br>inges to PPS re | gisters are prev | quence is execu<br>ented<br>d an unlocking s |            |

| <b>2</b> : ⊤    | his bit cannot b<br>he DEBUG bit i      | e programmed<br>n Configuration                               | Words is man                                  | aged automatic                      | ally by device   | development to                               | •          |

# REGISTER 4-2: CONFIGURATION WORD 2

- debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

- **3:** See VBOR parameter for specific trip point voltages.

## 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section

5.3 "Clock Switching" for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase Lock Loop, HFPLL that can produce one of three internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 2. The **MFINTOSC** (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

# 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.8 "Internal Oscillator Clock Switch Timing"** for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

# 5.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.8 "Internal Oscillator Clock Switch Timing"** for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium-Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

| TABLE 6-5: | SUMMARY OF REGISTERS ASSOCIATED WITH RESETS |

|------------|---------------------------------------------|

|            |                                             |

| Name   | Bit 7  | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|------------|-------|-------|-------|--------|--------|---------------------|

| BORCON | SBOREN | BORFS  |            |       | —     |       |        | BORRDY | 75                  |

| PCON   | STKOVF | STKUNF | _          | RWDT  | RMCLR | RI    | POR    | BOR    | 79                  |

| STATUS | —      | _      | _          | TO    | PD    | Z     | DC     | С      | 23                  |

| WDTCON |        |        | WDTPS<4:0> |       |       |       | SWDTEN | 99     |                     |

**Legend:** — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3  | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|-----------|----------|-----------|---------|---------------------|

|         | 13:8 |         | —       | _        | _        | CLKOUTEN  | BORE     | N<1:0>    | _       | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WD       | WDTE<1:0> |          | FOSC<1:0> |         | 56                  |

|         | 13:8 | _       | _       | LVP      | DEBUG    | LPBOREN   | BORV     | STVREN    | PLLEN   | 67                  |

| CONFIG2 | 7:0  | —       | —       |          |          | _         | PPS1WAY  | WRT       | <1:0>   | 57                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

# 13.6 Register Definitions: Interrupt-on-Change Control

#### **REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER**

| U-0                                   | U-0 | R/W-0/0            | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|---------------------------------------|-----|--------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| _                                     | _   | IOCAP5             | IOCAP4  | IOCAP3                                                | IOCAP2  | IOCAP1  | IOCAP0  |  |

| bit 7                                 |     |                    |         | -                                                     |         |         | bit 0   |  |

|                                       |     |                    |         |                                                       |         |         |         |  |

| Legend:                               |     |                    |         |                                                       |         |         |         |  |

| R = Readable bit                      |     | W = Writable bi    | t       | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchan                     | ged | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         | Resets  |  |

| '1' = Bit is set '0' = Bit is cleared |     |                    |         |                                                       |         |         |         |  |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

| —                | —       | —                 | _       | —              |                  | ADRE             | S<9:8>       |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

|                  |         |                   |         |                |                  |                  |              |

# REGISTER 16-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

bit 7-2 **Reserved**: Do not use.

| bit 1-0 | ADRES<9:8>: ADC Result Register bits       |

|---------|--------------------------------------------|

|         | Upper two bits of 10-bit conversion result |

# REGISTER 16-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADRES   | 6<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits Lower eight bits of 10-bit conversion result

# 22.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate.

The Auto-Baud Detect feature (see **Section 22.4.1 "Auto-Baud Detect"**) can be used to compensate for changes in the INTOSC frequency.

There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

# 22.3 Register Definitions: EUSART Control

# REGISTER 22-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-/0           | R/W-0/0                                                                                 | R/W-0/0                                               | R/W-0/0         | R/W-0/0        | R/W-0/0          | R-1/1            | R/W-0/0      |

|------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|----------------|------------------|------------------|--------------|

| CSRC             | TX9                                                                                     | TXEN <sup>(1)</sup>                                   | SYNC            | SENDB          | BRGH             | TRMT             | TX9D         |

| bit 7            |                                                                                         |                                                       |                 |                | •                |                  | bit 0        |

|                  |                                                                                         |                                                       |                 |                |                  |                  |              |

| Legend:          |                                                                                         |                                                       |                 |                |                  |                  |              |

| R = Readable     | bit                                                                                     | W = Writable                                          | bit             | U = Unimplei   | mented bit, read | as '0'           |              |

| u = Bit is unch  | anged                                                                                   | x = Bit is unk                                        | nown            | -n/n = Value   | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                                                                                         | '0' = Bit is cle                                      | ared            |                |                  |                  |              |

| bit 7            | Asynchronou<br>Don't care<br>Synchronous<br>1 = Master                                  |                                                       | nerated intern  |                | )                |                  |              |

| bit 6            | <b>TX9:</b> 9-bit Tr<br>1 = Selects                                                     | ansmit Enable  <br>9-bit transmiss<br>8-bit transmiss | oit<br>ion      | ,              |                  |                  |              |

| bit 5            | <b>TXEN:</b> Trans<br>1 = Transmi<br>0 = Transmi                                        |                                                       | 1)              |                |                  |                  |              |

| bit 4            | SYNC: EUS<br>1 = Synchro<br>0 = Asynchr                                                 |                                                       | ect bit         |                |                  |                  |              |

| bit 3            | Asynchronou<br>1 = Send Sy                                                              | nc Break on ne<br>eak transmissic                     | ext transmissio | on (cleared by | hardware upon o  | completion)      |              |

| bit 2            | BRGH: High<br>Asynchronou<br>1 = High spe<br>0 = Low spe<br>Synchronous<br>Unused in th | eed<br>eed<br><u>s mode:</u>                          | ect bit         |                |                  |                  |              |

| bit 1            |                                                                                         | smit Shift Regis<br>pty                               | ter Status bit  |                |                  |                  |              |

| bit 0            |                                                                                         | bit of Transmit<br>ess/data bit or a                  |                 |                |                  |                  |              |

| U-0              | U-0                                                                                                                                             | U-0                                                                      | U-0                   | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|-----------------|-------------------|------------------|-----------|

| _                | _                                                                                                                                               | _                                                                        | —                     | OFIE            | PHIE              | DCIE             | PRIE      |

| bit 7            |                                                                                                                                                 |                                                                          |                       |                 |                   |                  | bit 0     |

| [                |                                                                                                                                                 |                                                                          |                       |                 |                   |                  |           |

| Legend:          |                                                                                                                                                 |                                                                          |                       |                 |                   |                  |           |

| R = Readable     | e bit                                                                                                                                           | W = Writable b                                                           | it                    | U = Unimpleme   | ented bit, read a | is '0'           |           |

| u = Bit is unc   | hanged                                                                                                                                          | x = Bit is unkno                                                         | own                   | -n/n = Value at | POR and BOR       | Value at all oth | er Resets |

| '1' = Bit is set | t                                                                                                                                               | '0' = Bit is clea                                                        | red                   |                 |                   |                  |           |

| bit 7-4<br>bit 3 | <b>OFIE</b> : Offset I<br>1 = Interrupt (<br>0 = Do not int                                                                                     | ed: Read as '0'<br>nterrupt Enable<br>CPU on Offset M<br>errupt CPU on 0 | latch<br>Offset Match |                 |                   |                  |           |

| bit 2            | <ul> <li>PHIE: Phase Interrupt Enable bit</li> <li>1 = Interrupt CPU on Phase Match</li> <li>0 = Do not Interrupt CPU on Phase Match</li> </ul> |                                                                          |                       |                 |                   |                  |           |

| bit 1            | 1 = Interrupt C                                                                                                                                 | ycle Interrupt Er<br>CPU on Duty Cy<br>errupt CPU on I                   | cle Match             | h               |                   |                  |           |

| bit 0            | 1 = Interrupt (                                                                                                                                 | Interrupt Enable<br>CPU on Period I<br>errupt CPU on I                   | Match                 |                 |                   |                  |           |

# **REGISTER 23-2: PWMxINTE: PWM INTERRUPT ENABLE REGISTER**

### REGISTER 23-3: PWMxINTF: PWM INTERRUPT REQUEST REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|------------|------------|------------|------------|

|       |     | _   | _   | OFIF       | PHIF       | DCIF       | PRIF       |

| bit 7 | •   |     |     | •          | •          |            | bit 0      |

| Legend:                     |                      |                                                       |

|-----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by hard | dware                | HS = Bit is set by hardware                           |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged        | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set            | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                                           |

|---------|----------------------------------------------------------------------|

| bit 3   | OFIF: Offset Interrupt Flag bit <sup>(1)</sup>                       |

|         | 1 = Offset Match Event occurred                                      |

|         | 0 = Offset Match Event did not occur                                 |

| bit 2   | PHIF: Phase Interrupt Flag bit <sup>(1)</sup>                        |

|         | 1 = Phase Match Event occurred                                       |

|         | 0 = Phase Match Event did not occur                                  |

| bit 1   | DCIF: Duty Cycle Interrupt Flag bit <sup>(1)</sup>                   |

|         | 1 = Duty Cycle Match Event occurred                                  |

|         | 0 = Duty Cycle Match Event did not occur                             |

| bit 0   | PRIF: Period Interrupt Flag bit <sup>(1)</sup>                       |

|         | 1 = Period Match Event occurred                                      |

|         | 0 = Period Match Event did not occur                                 |

| Note 1: | Bit is forced clear by hardware while module is disabled (EN = $0$ ) |

Bit is forced clear by hardware while module is disabled (EN = 0).

| R/W-0/0            | R/W-0/0                                                                                                                                                                                                    | U-0                                                                                                                                                    | U-0                                                                                                                          | U-0              | U-0                                     | R/W-0/0          | R/W-0/0        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|------------------|----------------|

| LDA <sup>(1)</sup> | LDT                                                                                                                                                                                                        | _                                                                                                                                                      | _                                                                                                                            | _                | _                                       | LDS              | <1:0>          |

| bit 7              |                                                                                                                                                                                                            |                                                                                                                                                        |                                                                                                                              |                  |                                         |                  | bit 0          |

|                    |                                                                                                                                                                                                            |                                                                                                                                                        |                                                                                                                              |                  |                                         |                  |                |

| Legend:            |                                                                                                                                                                                                            |                                                                                                                                                        |                                                                                                                              |                  |                                         |                  |                |

| R = Reada          | ble bit                                                                                                                                                                                                    | W = Writable                                                                                                                                           | bit                                                                                                                          | U = Unimplem     | nented bit, read                        | as '0'           |                |

| u = Bit is u       | nchanged                                                                                                                                                                                                   | x = Bit is unkr                                                                                                                                        | iown                                                                                                                         | -n/n = Value a   | t POR and BO                            | R/Value at all o | other Resets   |

| '1' = Bit is s     | set                                                                                                                                                                                                        | '0' = Bit is clea                                                                                                                                      | ared                                                                                                                         |                  |                                         |                  |                |

| bit 7<br>bit 6     | $\frac{ f LDT = 1}{1}$<br>1 = Load the<br>0 = Do not lo<br>$\frac{ f LDT = 0}{1}$<br>1 = Load OF,<br>0 = Do not lo<br><b>LDT:</b> Load But<br>1 = Load buf<br>0 = Load on<br>Load the OFx<br>Reload intern | ad buffers/load<br>PH, DC and P<br>ad buffers or lo<br>uffer on Trigger<br>fers on trigger e<br>trigger disabled<br>t, PHx, DCx and<br>al double buffe | and PRx buffe<br>has completed<br>R buffers at the<br>ad has comple<br>bit<br>enabled<br>d PRx buffers a<br>rs at the end of | e end of the cur | rrent period<br><b>ery</b> period after | r the selected t |                |

| bit 5-2            | Unimplemen                                                                                                                                                                                                 | ted: Read as 'd                                                                                                                                        | )'                                                                                                                           |                  |                                         |                  |                |

| bit 1-0            | LDS<1:0>: Lo<br>11 = LD4_trig<br>10 = LD3_trig<br>01 = LD2_trig<br>00 = LD1_trig                                                                                                                           | )ger <sup>(2)</sup><br>)ger <sup>(2)</sup>                                                                                                             | urce Select bits                                                                                                             | 3                |                                         |                  |                |

|                    | This bit is cleared<br>arming event.                                                                                                                                                                       | -                                                                                                                                                      | after a reload                                                                                                               |                  | n be cleared in                         | software to cle  | ar an existing |

# REGISTER 23-5: PWMxLDCON: PWM RELOAD TRIGGER SOURCE SELECT REGISTER

2: The LD\_trigger corresponding to the PWM used becomes reserved.

### REGISTER 23-11: PWMxPRH: PWMx PERIOD COUNT HIGH REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | PR<     | :15:8>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **PR<15:8>**: PWM Period High bits Upper eight bits of PWM period count

# REGISTER 23-12: PWMxPRL: PWMx PERIOD COUNT LOW REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PR<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PR<7:0>**: PWM Period Low bits Lower eight bits of PWM period count

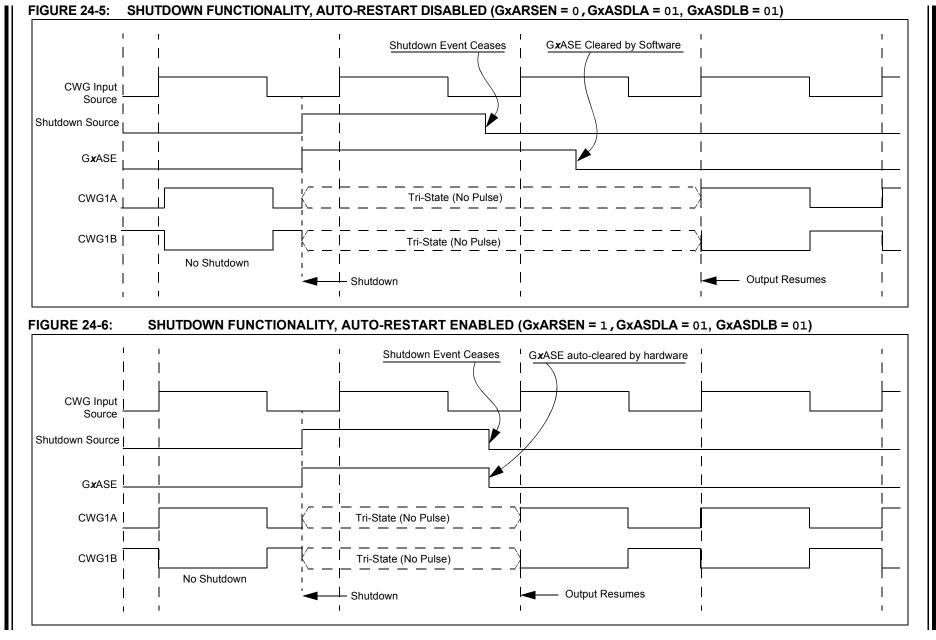

# 24.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces a complementary waveform with dead-band delay from a selection of input sources.

The CWG module has the following features:

- · Selectable dead-band clock source control

- · Selectable input sources

- · Output enable control

- · Output polarity control

- Dead-band control with independent 6-bit rising and falling edge dead-band counters

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

# 24.1 Fundamental Operation

The CWG generates two output waveforms from the selected input source.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 24.5 "Dead-Band Control"**. A typical operating waveform, with dead band, generated from a single input signal is shown in Figure 24-2.

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 24.9 "Auto-Shutdown Control"**.

# 24.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the G1CS0 bit of the CWGxCON0 register (Register 24-1).

# 24.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources in Table 24-1.

| TABLE 24-1: | SELECTABLE INPUT |

|-------------|------------------|

|             | SOURCES          |

| Source Peripheral | Signal Name |  |  |  |  |

|-------------------|-------------|--|--|--|--|

| CWG input pin     | CWGxIN pin  |  |  |  |  |

| Comparator C1     | C1OUT_sync  |  |  |  |  |

| Comparator C2     | C2OUT_sync  |  |  |  |  |

| PWM1              | PWM1_output |  |  |  |  |

| PWM2              | PWM2_output |  |  |  |  |

| PWM3              | PWM3_output |  |  |  |  |

| PWM4              | PWM4_output |  |  |  |  |

The input sources are selected using the GxIS<2:0> bits in the CWGxCON1 register (Register 24-2).

# 24.4 Output Control

Immediately after the CWG module is enabled, the complementary drive is configured with both CWGxA and CWGxB drives cleared.

# 24.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the GxPOLA and GxPOLB bits of the CWGxCON0 register.

© 2016 Microchip Technology Inc

PIC16(L)F1574/5/8/9

# PIC16(L)F1574/5/8/9

| LSLF                                                                                                                                                                                                                                                                                 | Logical Left Shift                     | MOVF             | Move f                                                                                                                                                                                              |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                                                                                                                                                                                                                                                              | yntax: [ label ] LSLF f {,d}           |                  | [ <i>label</i> ] MOVF f,d                                                                                                                                                                           |  |  |

| Operands:                                                                                                                                                                                                                                                                            | $0 \le f \le 127$<br>d $\in [0,1]$     | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                  |  |  |

| Operation:                                                                                                                                                                                                                                                                           | $(f < 7 >) \rightarrow C$              | Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                            |  |  |

|                                                                                                                                                                                                                                                                                      | $(f < 6:0 >) \rightarrow dest < 7:1 >$ | Status Affected: | Z                                                                                                                                                                                                   |  |  |

| $0 \rightarrow dest < 0>$ Status Affected: C, Z Description: The contents of register 'f' are shifted one bit to the left through the Carry flag. A '0' is shifted into the LSb. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |                                        | Description:     | The contents of register f is moved to a destination dependent upon the                                                                                                                             |  |  |

|                                                                                                                                                                                                                                                                                      |                                        |                  | status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ , the<br>destination is file register f itself. $d = 1$<br>is useful to test a file register since<br>status flag Z is affected. |  |  |

|                                                                                                                                                                                                                                                                                      | C                                      | Words:           | 1                                                                                                                                                                                                   |  |  |

|                                                                                                                                                                                                                                                                                      |                                        | Cycles:          | 1                                                                                                                                                                                                   |  |  |

|                                                                                                                                                                                                                                                                                      |                                        | Example:         | MOVF FSR, 0                                                                                                                                                                                         |  |  |

| LSRF                                                                                                                                                                                                                                                                                 | Logical Right Shift                    |                  | After Instruction<br>W = value in FSR register                                                                                                                                                      |  |  |

| Syntax:                                                                                                                                                                                                                                                                              | [ <i>label</i> ]LSRF f{,d}             |                  | Z = 1                                                                                                                                                                                               |  |  |

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} 0 \rightarrow dest < 7 > \\ (f < 7:1 >) \rightarrow dest < 6:0 >, \\ (f < 0 >) \rightarrow C, \end{array}$                                                                                                         |

| Status Affected: | C, Z                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. A '0' is shifted into the MSb. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is stored back in register 'f'. |

|                  | 0 → register f C                                                                                                                                                                                                                     |

## TABLE 27-14: ADC CONVERSION REQUIREMENTS

| Param.<br>No. | Sym. | Characteristic                                                     | Min. | Тур†                      | Max. | Units | Conditions                                   |

|---------------|------|--------------------------------------------------------------------|------|---------------------------|------|-------|----------------------------------------------|

| AD130*        | Tad  | ADC Clock Period (TADC)                                            | 1.0  | _                         | 6.0  | μS    | Fosc-based                                   |

|               |      | ADC Internal FRC Oscillator Period (TFRC)                          | 1.0  | 2.0                       | 6.0  | μS    | ADCS<2:0> = x11 (ADC FRC mode)               |

| AD131         | TCNV | Conversion Time<br>(not including Acquisition Time) <sup>(1)</sup> | —    | 11                        | —    | TAD   | Set GO/DONE bit to conversion complete       |

| AD132*        | TACQ | Acquisition Time                                                   | _    | 5.0                       | _    | μS    |                                              |

| AD133*        | Тнср | Holding Capacitor Disconnect Time                                  | _    | 1/2 TAD<br>1/2 TAD + 1TCY | _    |       | Fosc-based<br>ADCS<2:0> = x11 (ADC FRC mode) |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not † tested.

Note 1: The ADRES register may be read on the following TCY cycle.

# TABLE 27-15: COMPARATOR SPECIFICATIONS<sup>(1)</sup>

| Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |                      |                                           |      |      |      |       |                           |

|-------------------------------------------------------------------------|----------------------|-------------------------------------------|------|------|------|-------|---------------------------|

| Param.<br>No.                                                           | Sym.                 | Characteristics                           | Min. | Тур. | Max. | Units | Comments                  |

| CM01                                                                    | VIOFF                | Input Offset Voltage                      |      | ±7.5 | ±60  | mV    | CxSP = 1,<br>VICM = VDD/2 |

| CM02                                                                    | VICM                 | Input Common Mode Voltage                 | 0    |      | Vdd  | V     |                           |

| CM03                                                                    | CMRR                 | Common Mode Rejection Ration              | _    | 50   | _    | dB    |                           |

| CM04A                                                                   |                      | Response Time Rising Edge                 | _    | 400  | 800  | ns    | CxSP = 1                  |

| CM04B                                                                   | TRESP <sup>(2)</sup> | Response Time Falling Edge                | _    | 200  | 400  | ns    | CxSP = 1                  |

| CM04C                                                                   | TRESP-7              | Response Time Rising Edge                 | _    | 1200 | _    | ns    | CxSP = 0                  |

| CM04D                                                                   |                      | Response Time Falling Edge                | _    | 550  | _    | ns    | CxSP = 0                  |

| CM05*                                                                   | Тмс2о∨               | Comparator Mode Change to<br>Output Valid | _    | —    | 10   | μS    |                           |

| CM06                                                                    | CHYSTER              | Comparator Hysteresis                     |      | 25   |      | mV    | CxHYS = 1,<br>CxSP = 1    |

\* These parameters are characterized but not tested.

Note 1: See Section 28.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

2: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

# TABLE 27-16: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS<sup>(1)</sup>

| <b>Operating Conditions (unless otherwise stated)</b><br>VDD = 3.0V, TA = 25°C |      |                              |   |        |       |     |  |

|--------------------------------------------------------------------------------|------|------------------------------|---|--------|-------|-----|--|

| Param.<br>No.Sym.CharacteristicsMin.Typ.Max.UnitsComments                      |      |                              |   |        |       |     |  |

| DAC01*                                                                         | CLSB | Step Size                    | — | VDD/32 | _     | V   |  |

| DAC02*                                                                         | CACC | Absolute Accuracy            | — | —      | ± 1/2 | LSb |  |

| DAC03*                                                                         | CR   | Unit Resistor Value (R)      | — | 5K     | _     | Ω   |  |

| DAC04*                                                                         | CST  | Settling Time <sup>(2)</sup> | _ | —      | 10    | μS  |  |

\* These parameters are characterized but not tested.

Note 1: See Section 28.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

**2:** Settling time measured while DACR<4:0> transitions from '0000' to '1111'.

# PIC16(L)F1574/5/8/9

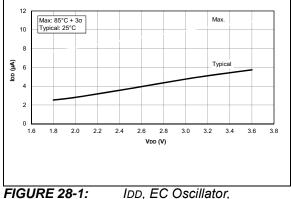

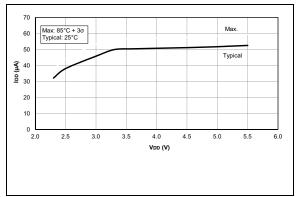

FIGURE 28-1: IDD, EC Oscillato Low-Power Mode, Fosc = 32 kHz, PIC16LF1574/5/8/9 Only.

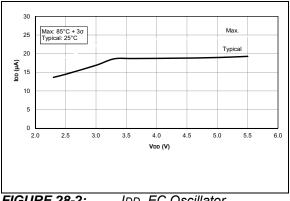

FIGURE 28-2: IDD, EC Oscillator, Low-Power Mode, Fosc = 32 kHz, PIC16F1574/5/8/9 Only.

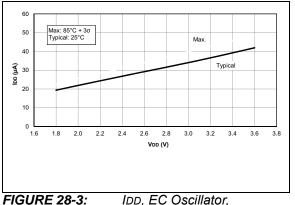

Low-Power Mode, Fosc = 500 kHz, PIC16LF1574/5/8/9 Only.

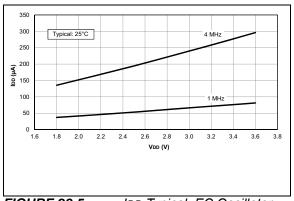

FIGURE 28-5:IDD Typical, EC Oscillator,Medium Power Mode, PIC16LF1574/5/8/9 Only.

FIGURE 28-4: IDD, EC Oscillator, Low-Power Mode, Fosc = 500 kHz, PIC16F1574/5/8/9 Only.

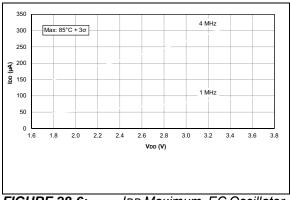

FIGURE 28-6: IDD Maximum, EC Oscillator, Medium Power Mode, PIC16LF1574/5/8/9 Only.

# 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

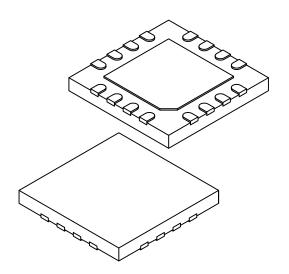

# 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |                |          |      |  |  |

|-------------------------|-------------|----------------|----------|------|--|--|

| Dimension               | MIN         | NOM            | MAX      |      |  |  |

| Number of Pins          | N           | 16             |          |      |  |  |

| Pitch                   | е           |                | 0.65 BSC |      |  |  |

| Overall Height          | Α           | 0.45           | 0.50     | 0.55 |  |  |

| Standoff                | A1          | 0.00           | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.127 REF      |          |      |  |  |

| Overall Width           | E           | 4.00 BSC       |          |      |  |  |

| Exposed Pad Width       | E2          | 2.50           | 2.60     | 2.70 |  |  |

| Overall Length          | D           | 4.00 BSC       |          |      |  |  |

| Exposed Pad Length      | D2          | 2.50 2.60 2.70 |          |      |  |  |

| Terminal Width          | b           | 0.25           | 0.30     | 0.35 |  |  |

| Terminal Length         | L           | 0.30           | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | К           | 0.20           | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-257A Sheet 2 of 2