Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | LINbus, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1579-i-gz |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

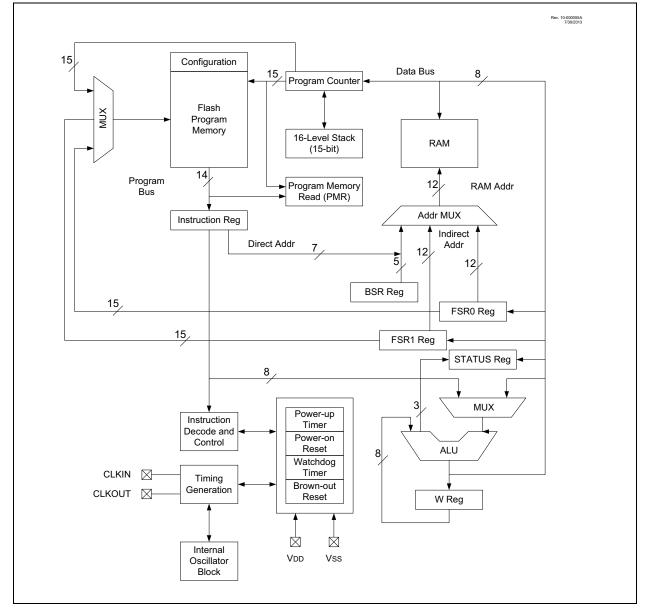

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

FIGURE 2-1: CORE BLOCK DIAGRAM

- Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

## 4.7 Register Definitions: Device ID

#### R R R R R R DEV<13:8> bit 13 bit 8 R R R R R R R R DEV<7:0> bit 7 bit 0

#### REGISTER 4-3: DEVICEID: DEVICE ID REGISTER<sup>(1)</sup>

#### Legend:

| - |                  |  |

|---|------------------|--|

|   | R = Readable bit |  |

|   |                  |  |

| '0' = Bit is cleared | '1' = Bit is set | x = Bit is unknown |

|----------------------|------------------|--------------------|

|                      |                  |                    |

#### bit 13-0 **DEV<13:0>:** Device ID bits

Refer to Table 4-1 to determine what these bits will read on which device. A value of 3FFFh is invalid.

Note 1: This location cannot be written.

## REGISTER 4-4: REVISIONID: REVISION ID REGISTER<sup>(1)</sup>

| R      | R        | R    | R        | R | R     |

|--------|----------|------|----------|---|-------|

|        |          | REV< | 13:8>    |   |       |

| bit 13 |          |      |          |   | bit 8 |

|        |          |      |          |   |       |

| -      | <b>D</b> |      | <b>D</b> |   |       |

| R           | R | R | R | R | R | R | R |  |

|-------------|---|---|---|---|---|---|---|--|

| REV<7:0>    |   |   |   |   |   |   |   |  |

| bit 7 bit 0 |   |   |   |   |   |   |   |  |

| Legend:              |                  |                    |  |

|----------------------|------------------|--------------------|--|

| R = Readable bit     |                  |                    |  |

| '0' = Bit is cleared | '1' = Bit is set | x = Bit is unknown |  |

bit 13-0 **REV<13:0>:** Revision ID bits These bits are used to identify the device revision.

**Note 1:** This location cannot be written.

#### TABLE 4-1: DEVICE ID VALUES

| DEVICE      | Device ID | Revision ID |

|-------------|-----------|-------------|

| PIC16F1574  | 3000h     | 2xxxh       |

| PIC16F1575  | 3001h     | 2xxxh       |

| PIC16F1578  | 3002h     | 2xxxh       |

| PIC16F1579  | 3003h     | 2xxxh       |

| PIC16LF1574 | 3004h     | 2xxxh       |

| PIC16LF1575 | 3005h     | 2xxxh       |

| PIC16LF1578 | 3006h     | 2xxxh       |

| PIC16LF1579 | 3007h     | 2xxxh       |

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6 | Bit 5                   | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|-------|-------------------------|-------|-------|-------|--------|--------|---------------------|

| OSCCON  | SPLLEN |       | IRCF<3:0>               |       |       |       | SCS    | <1:0>  | 69                  |

| OSCSTAT | _      | PLLR  | PLLR OSTS HFIOFR HFIOFL |       |       |       | LFIOFR | HFIOFS | 70                  |

| OSCTUNE | _      | _     |                         |       | TUN<  | <5:0> |        |        | 71                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 5-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         |         |          | —        | CLKOUTEN | BORE     | N<1:0>  | —       | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | _        | FOSC    | C<1:0>  | 56                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

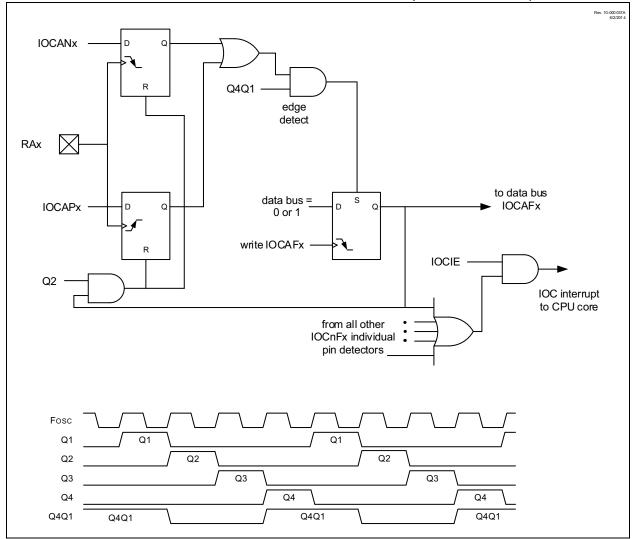

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

## 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

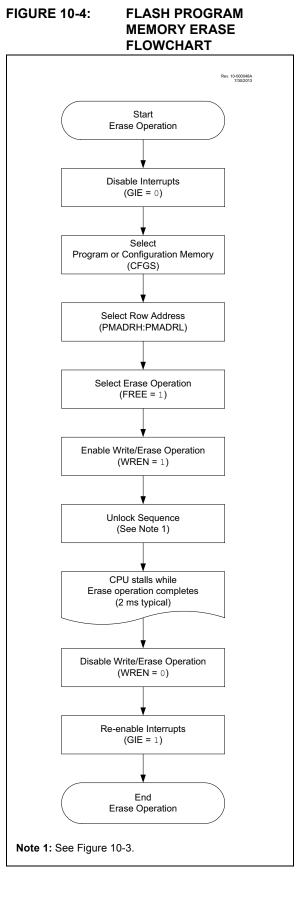

# 10.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

See Example 10-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

#### **10.6 Register Definitions: Flash Program Memory Control**

#### REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u              | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u           | R/W-x/u              | R/W-x/u                | R/W-x/u |

|----------------------|---------|----------------------|---------|-------------------|----------------------|------------------------|---------|

|                      |         |                      | PMDA    | T<7:0>            |                      |                        |         |

| bit 7                |         |                      |         |                   |                      |                        | bit 0   |

|                      |         |                      |         |                   |                      |                        |         |

| Legend:              |         |                      |         |                   |                      |                        |         |

| R = Readable bit     |         | W = Writable bit     |         | U = Unimpleme     | nted bit, read as '0 | ,                      |         |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at F | POR and BOR/Valu     | ue at all other Resets | S       |

| '1' = Bit is set     |         | '0' = Bit is cleared |         |                   |                      |                        |         |

bit 7-0

**PMDAT<7:0>**: Read/write value for Least Significant bits of program memory

#### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | PMDA    | T<13:8> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0              | R/W-0/0 | R/W-0/0              | R/W-0/0                                       | R/W-0/0           | R/W-0/0          | R/W-0/0              | R/W-0/0 |

|----------------------|---------|----------------------|-----------------------------------------------|-------------------|------------------|----------------------|---------|

|                      |         |                      | PMAD                                          | R<7:0>            |                  |                      |         |

| bit 7                |         |                      |                                               |                   |                  |                      | bit 0   |

|                      |         |                      |                                               |                   |                  |                      |         |

| Legend:              |         |                      |                                               |                   |                  |                      |         |

| R = Readable bit     |         | W = Writable bit     | itable bit U = Unimplemented bit, read as '0' |                   |                  |                      |         |

| u = Bit is unchanged |         | x = Bit is unknown   |                                               | -n/n = Value at F | POR and BOR/Valu | ie at all other Rese | ets     |

| '1' = Bit is set     |         | '0' = Bit is cleared |                                               |                   |                  |                      |         |

bit 7-0 PMADR<7:0>: Specifies the Least Significant bits for program memory address

#### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1                 | R/W-0/0 | R/W-0/0              | R/W-0/0 | R/W-0/0           | R/W-0/0              | R/W-0/0             | R/W-0/0 |

|---------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

| (1)                 |         |                      |         | PMADR<14:8>       |                      |                     |         |

| bit 7               |         |                      |         |                   |                      |                     | bit 0   |

|                     |         |                      |         |                   |                      |                     |         |

| Legend:             |         |                      |         |                   |                      |                     |         |

| R = Readable bit    |         | W = Writable bit     |         | U = Unimplemer    | nted bit, read as '0 | 3                   |         |

| u = Bit is unchange | ed      | x = Bit is unknown   |         | -n/n = Value at F | OR and BOR/Val       | ue at all other Res | ets     |

| '1' = Bit is set    |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7 Unimplemented: Read as '1'

bit 6-0 PMADR<14:8>: Specifies the Most Significant bits for program memory address

**Note 1:** Unimplemented, read as '1'.

| U-0              | U-0   | R/W-1/1           | R/W-1/1 | R/W-1/1                            | R/W-1/1       | R/W-1/1          | R/W-1/1      |  |  |

|------------------|-------|-------------------|---------|------------------------------------|---------------|------------------|--------------|--|--|

| _                | _     | WPUA5             | WPUA4   | WPUA3                              | WPUA2         | WPUA1            | WPUA0        |  |  |

| bit 7            |       |                   |         |                                    |               |                  | bit 0        |  |  |

|                  |       |                   |         |                                    |               |                  |              |  |  |

| Legend:          |       |                   |         |                                    |               |                  |              |  |  |

| R = Readable     | bit   | W = Writable      | bit     | U = Unimplemented bit, read as '0' |               |                  |              |  |  |

| u = Bit is uncha | anged | x = Bit is unkr   | nown    | -n/n = Value a                     | at POR and BO | R/Value at all o | other Resets |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared    |                                    |               |                  |              |  |  |

| '1' = Bit is set |       | ʻ0' = Bit is clea | ared    |                                    |               |                  |              |  |  |

#### REGISTER 11-5: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 WPUA<5:0>: Weak Pull-up Register bits<sup>(3)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

- **3:** For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

#### REGISTER 11-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | ODA5    | ODA4    | —   | ODA2    | ODA1    | ODA0    |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>ODA&lt;5:4&gt;:</b> PORTA Open-Drain Enable bits<br>For RA<5:4> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0 | <b>ODA&lt;2:0&gt;:</b> PORTA Open-Drain Enable bits<br>For RA<2:0> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

| REGISTER 13-4: | IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER <sup>(1)</sup> |

|----------------|------------------------------------------------------------------------|

|----------------|------------------------------------------------------------------------|

| R/W-0/0           | R/W-0/0 | R/W-0/0             | R/W-0/0 | U-0                                | U-0            | U-0                 | U-0   |  |  |

|-------------------|---------|---------------------|---------|------------------------------------|----------------|---------------------|-------|--|--|

| IOCBP7            | IOCBP6  | IOCBP5              | IOCBP4  | _                                  | —              | —                   | —     |  |  |

| bit 7             |         |                     |         |                                    |                |                     | bit 0 |  |  |

|                   |         |                     |         |                                    |                |                     |       |  |  |

| Legend:           |         |                     |         |                                    |                |                     |       |  |  |

| R = Readable bi   | t       | W = Writable bit    | :       | U = Unimplemented bit, read as '0' |                |                     |       |  |  |

| u = Bit is unchar | nged    | x = Bit is unknow   | wn      | -n/n = Value at                    | POR and BOR/Va | lue at all other Re | esets |  |  |

| '1' = Bit is set  |         | '0' = Bit is cleare | ed      |                                    |                |                     |       |  |  |

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

#### REGISTER 13-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER<sup>(1)</sup>

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | —   | -   | _   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 **IOCBN<7:4>**: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

- bit 3-0 Unimplemented: Read as '0'

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

#### REGISTER 13-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER<sup>(1)</sup>

| R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0   |

|------------|------------|------------|------------|-----|-----|-----|-------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | —   | —   | —   | —     |

| bit 7      | -          |            |            |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | IOCBF<7:4>: Interrupt-on-Change PORTB Flag bits                                                      |

|---------|------------------------------------------------------------------------------------------------------|

|         | 1 = An enabled change was detected on the associated pin.                                            |

|         | Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was |

|         | detected on RBx.                                                                                     |

|         | 0 = No change was detected, or the user cleared the detected change.                                 |

|         |                                                                                                      |

bit 3-0 Unimplemented: Read as '0'

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

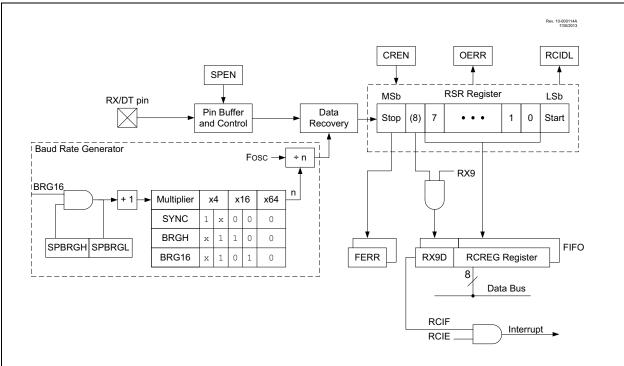

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

## TABLE 23-2: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

| Name                    | Bit 7               | Bit 6  | Bit 5    | Bit 4  | Bit 3     | Bit 2     | Bit 1     | Bit 0     | Register<br>on Page |  |

|-------------------------|---------------------|--------|----------|--------|-----------|-----------|-----------|-----------|---------------------|--|

| OSCCON                  | SPLLEN              |        | IRC      | F<3:0> | •         | _         | SCS       | <1:0>     | 69                  |  |

| PIE3                    | PWM4IE              | PWM3IE | PWM2IE   | PWM1IE | _         |           |           |           | 89                  |  |

| PIR3                    | PWM4IF              | PWM3IF | PWM2IF   | PWM1IF | _         | _         | _         | _         | 92                  |  |

| PWMEN                   | -                   | —      | —        | _      | PWM4EN_A  | PWM3EN_A  | PWM2EN_A  | PWM1EN_A  | 243                 |  |

| PWMLD                   | _                   | _      | _        | _      | PWM4LDA_A | PWM3LDA_A | PWM2LDA_A | PWM1LDA_A | 243                 |  |

| PWMOUT                  | _                   | _      | _        | _      | PWM4OUT_A | PWM3OUT_A | PWM2OUT_A | PWM1OUT_A | 243                 |  |

| PWM1PHL                 |                     |        |          | F      | PH<7:0>   | . –       | . –       |           | 238                 |  |

| PWM1PHH                 | PH<15:8>            |        |          |        |           |           |           |           |                     |  |

| PWM1DCL                 |                     |        |          | C      | )C<7:0>   |           |           |           | 239                 |  |

| PWM1DCH                 |                     |        |          | D      | C<15:8>   |           |           |           | 239                 |  |

| PWM1PRL                 |                     |        |          | F      | PR<7:0>   |           |           |           | 240                 |  |

| PWM1PRH                 |                     |        |          | Р      | R<15:8>   |           |           |           | 240                 |  |

| PWM10FL                 |                     |        |          |        | )F<7:0>   |           |           |           | 241                 |  |

| PWM10FH                 |                     |        |          |        | F<15:8>   |           |           |           | 241                 |  |

| PWM1TMRL                |                     |        |          |        | MR<7:0>   |           |           |           | 242                 |  |

| PWM1TMRH                |                     |        |          |        | /IR<15:8> |           |           |           | 242                 |  |

| PWM1CON                 | EN                  | _      | OUT      | POL    | T         | E<1:0>    | _         | _         | 233                 |  |

| PWM1INTE                | _                   | _      | _        | _      | OFIE      | PHIE      | DCIE      | PRIE      | 233                 |  |

| PWM1INTF                |                     |        |          |        | OFIE      | PHIF      | DCIF      | PRIF      | 234                 |  |

| PWM1CLKCON              |                     |        | PS<2:0>  |        | -         |           | -         | :1:0>     | 235                 |  |

| PWM1CLRCON<br>PWM1LDCON | LDA                 | LDT    | F 3 2.02 |        |           |           | LDS       | 235       |                     |  |

| PWM10FCON               | LDA                 | OFM    | <1:0>    | OFO    |           |           | OFS       | 230       |                     |  |

|                         |                     | OTIV   | <1.02    |        |           | —         | 013       | <1.02     | 237                 |  |

| PWM2PHL                 | PH<7:0><br>PH<15:8> |        |          |        |           |           |           |           |                     |  |

| PWM2PHH                 |                     |        |          |        |           |           |           |           | 238                 |  |

| PWM2DCL                 |                     |        |          |        | )C<7:0>   |           |           |           | 239                 |  |

| PWM2DCH                 |                     |        |          |        | C<15:8>   |           |           |           | 239                 |  |

| PWM2PRL                 |                     |        |          |        | PR<7:0>   |           |           |           | 240                 |  |

| PWM2PRH                 |                     |        |          |        | R<15:8>   |           |           |           | 240                 |  |

| PWM2OFL                 |                     |        |          |        | )F<7:0>   |           |           |           | 241                 |  |

| PWM2OFH                 |                     |        |          |        | F<15:8>   |           |           |           | 241                 |  |

| PWM2TMRL                |                     |        |          |        | VIR<7:0>  |           |           |           | 242                 |  |

| PWM2TMRH                |                     |        |          | -      | 1R<15:8>  |           |           |           | 242                 |  |

| PWM2CON                 | EN                  | —      | OUT      | POL    |           | E<1:0>    | -         | -         | 233                 |  |

| PWM2INTE                |                     | _      | —        |        | OFIE      | PHIE      | DCIE      | PRIE      | 234                 |  |

| PWM2INTF                |                     |        |          | —      | OFIF      | PHIF      | DCIF      | PRIF      | 234                 |  |

| PWM2CLKCON              | —                   |        | PS<2:0>  |        | _         | —         | -         | <1:0>     | 235                 |  |

| PWM2LDCON               | LDA                 | LDT    | —        | -      | _         | _         | -         | <1:0>     | 236                 |  |

| PWM2OFCON               | —                   | OFM    | <1:0>    | OFO    | -         | —         | OFS       | <1:0>     | 237                 |  |

| PWM3PHL                 |                     |        |          |        | PH<7:0>   |           |           |           | 238                 |  |

| PWM3PHH                 |                     |        |          |        | H<15:8>   |           |           |           | 238                 |  |

| PWM3DCL                 |                     |        |          |        | )C<7:0>   |           |           |           | 239                 |  |

| PWM3DCH                 |                     |        |          |        | C<15:8>   |           |           |           | 239                 |  |

| PWM3PRL                 |                     |        |          |        | PR<7:0>   |           |           |           | 240                 |  |

| PWM3PRH                 |                     |        |          |        | R<15:8>   |           |           |           | 240                 |  |

| PWM3OFL                 |                     |        |          |        | )F<7:0>   |           |           |           | 241                 |  |

| PWM3OFH                 |                     |        |          |        | F<15:8>   |           |           |           | 241                 |  |

| PWM3TMRL                |                     |        |          | T      | VIR<7:0>  |           |           |           | 242                 |  |

| PWM3TMRH                |                     |        | 1        | TN     | 1R<15:8>  |           |           |           | 242                 |  |

| PWM3CON                 | EN                  | —      | OUT      | POL    | MODE      | =<1:0>    | —         | —         | 233                 |  |

| PWM3INTE                | _                   | —      | —        | —      | OFIE      | PHIE      | DCIE      | PRIE      | 234                 |  |

| PWM3INTF                | _                   | _      | —        |        | OFIF      | PHIF      | DCIF      | PRIF      | 234                 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PWM.

| Name     | Bit 7 | Bit 6   | Bit 5  | Bit 4                  | Bit 3    | Bit 2    | Bit 1     | Bit 0  | Register<br>on Page |

|----------|-------|---------|--------|------------------------|----------|----------|-----------|--------|---------------------|

| ANSELA   | _     | _       | _      | ANSA4                  | —        | ANSA2    | ANSA1     | ANSA0  | 121                 |

| CWG1CON0 | G1EN  | _       | _      | G1POLB                 | G1POLA   | _        | _         | G1CS0  | 253                 |

| CWG1CON1 | G1ASD | LB<1:0> | G1ASD  | G1ASDLA<1:0> G1IS<2:0> |          |          |           | 254    |                     |

| CWG1CON2 | G1ASE | G1ARSEN | _      | —                      | G1ASDSC2 | G1ASDSC1 | G1ASDSPPS | _      | 255                 |

| CWG1DBF  | _     | _       |        | CWG1DBF<5:0>           |          |          |           |        |                     |

| CWG1DBR  | _     | _       |        | CWG1DBR<5:0>           |          |          |           |        |                     |

| TRISA    |       | —       | TRISA5 | TRISA4                 | _(1)     | TRISA2   | TRISA1    | TRISA0 | 120                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by CWG. **Note 1:** Unimplemented, read as '1'.

## TABLE 27-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup>

| PIC16LF | 1574/5/8/9      | Standard Operating Conditions (unless otherwise stated) |                                         |      |       |            |                                            |  |  |  |  |  |

|---------|-----------------|---------------------------------------------------------|-----------------------------------------|------|-------|------------|--------------------------------------------|--|--|--|--|--|

| PIC16F1 | 574/5/8/9       |                                                         |                                         |      |       |            |                                            |  |  |  |  |  |

| Param.  | Device          | Min.                                                    | Typt                                    | Max. | Units | Conditions |                                            |  |  |  |  |  |

| No.     | Characteristics |                                                         | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | _    |       | Vdd        | Note                                       |  |  |  |  |  |

| D013    |                 | _                                                       | 41                                      | 51   | μA    | 1.8        | Fosc = 1 MHz,                              |  |  |  |  |  |

|         |                 | —                                                       | 69                                      | 80   | μA    | 3.0        | External Clock (ECM),<br>Medium Power mode |  |  |  |  |  |

| D013    |                 | —                                                       | 79                                      | 107  | μA    | 2.3        | Fosc = 1 MHz,                              |  |  |  |  |  |

|         |                 |                                                         | 105                                     | 138  | μA    | 3.0        | External Clock (ECM),                      |  |  |  |  |  |

|         |                 |                                                         | 151                                     | 184  | μA    | 5.0        | Medium Power mode                          |  |  |  |  |  |

| D014    |                 |                                                         | 134                                     | 152  | μA    | 1.8        | Fosc = 4 MHz,                              |  |  |  |  |  |

|         |                 | -                                                       | 234                                     | 268  | μA    | 3.0        | External Clock (ECM),<br>Medium Power mode |  |  |  |  |  |

| D014    |                 |                                                         | 201                                     | 255  | μA    | 2.3        | Fosc = 4 MHz,                              |  |  |  |  |  |

|         |                 | —                                                       | 270                                     | 329  | μA    | 3.0        | External Clock (ECM),<br>Medium Power mode |  |  |  |  |  |

|         |                 | —                                                       | 344                                     | 431  | μA    | 5.0        |                                            |  |  |  |  |  |

| D015    |                 | —                                                       | 7                                       | 19   | μA    | 1.8        | Fosc = 31 kHz,                             |  |  |  |  |  |

|         |                 | —                                                       | 9                                       | 20   | μA    | 3.0        | LFINTOSC,<br>-40°C ≤ Ta ≤ +85°C            |  |  |  |  |  |

| D015    |                 |                                                         | 15                                      | 25   | μA    | 2.3        | Fosc = 31 kHz,                             |  |  |  |  |  |

|         |                 | _                                                       | 18                                      | 28   | μA    | 3.0        | └ LFINTOSC,<br>40°C ≤ TA ≤ +85°C           |  |  |  |  |  |

|         |                 | _                                                       | 20                                      | 29   | μA    | 5.0        | $=-40$ C $\leq$ 1A $\leq$ +65 C            |  |  |  |  |  |

| D016    |                 | —                                                       | 128                                     | 174  | μA    | 1.8        | Fosc = 500 kHz,                            |  |  |  |  |  |

|         |                 | _                                                       | 153                                     | 203  | μA    | 3.0        | MFINTOSC                                   |  |  |  |  |  |

| D016    |                 | —                                                       | 166                                     | 241  | μA    | 2.3        | Fosc = 500 kHz,                            |  |  |  |  |  |

|         |                 |                                                         | 187                                     | 273  | μA    | 3.0        | MFINTOSC                                   |  |  |  |  |  |

|         |                 | _                                                       | 249                                     | 332  | μA    | 5.0        |                                            |  |  |  |  |  |

| D017*   |                 | _                                                       | 0.6                                     | 0.7  | mA    | 1.8        | Fosc = 8 MHz,                              |  |  |  |  |  |

|         |                 | _                                                       | 0.9                                     | 1.1  | mA    | 3.0        | HFINTOSC                                   |  |  |  |  |  |

| D017*   |                 | —                                                       | 0.7                                     | 1.0  | mA    | 2.3        | Fosc = 8 MHz,                              |  |  |  |  |  |

|         |                 | _                                                       | 1.0                                     | 1.1  | mA    | 3.0        | HFINTOSC                                   |  |  |  |  |  |

|         |                 | _                                                       | 1.1                                     | 1.2  | mA    | 5.0        |                                            |  |  |  |  |  |

| D018    |                 | _                                                       | 0.9                                     | 1.0  | mA    | 1.8        | Fosc = 16 MHz,                             |  |  |  |  |  |

|         |                 | _                                                       | 1.3                                     | 1.4  | mA    | 3.0        | HFINTOSC                                   |  |  |  |  |  |

| D018    |                 | _                                                       | 1.1                                     | 1.3  | mA    | 2.3        | Fosc = 16 MHz,                             |  |  |  |  |  |

|         |                 | _                                                       | 1.3                                     | 1.5  | mA    | 3.0        | HFINTOSC                                   |  |  |  |  |  |

|         |                 | _                                                       | 1.5                                     | 1.8  | mA    | 5.0        | -                                          |  |  |  |  |  |

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: CLKIN = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: PLL required for 32 MHz operation.

## TABLE 27-5: MEMORY PROGRAMMING SPECIFICATIONS

| Param.<br>No. | Sym.   | Characteristic                               | Min.   | Тур† | Max.   | Units | Conditions                                                           |

|---------------|--------|----------------------------------------------|--------|------|--------|-------|----------------------------------------------------------------------|

|               |        | Program Memory<br>Programming Specifications |        |      |        |       |                                                                      |

| D110          | VIHH   | Voltage on MCLR/VPP pin                      | 8.0    |      | 9.0    | V     | (Note 2)                                                             |

| D111          | IDDP   | Supply Current during<br>Programming         | _      | —    | 10     | mA    |                                                                      |

| D112          | VBE    | VDD for Bulk Erase                           | 2.7    |      | VDDMAX | V     |                                                                      |

| D113          | VPEW   | VDD for Write or Row Erase                   | VDDMIN |      | VDDMAX | V     |                                                                      |

| D114          | IPPPGM | Current on MCLR/VPP during<br>Erase/Write    | -      | 1.0  | —      | mA    |                                                                      |

| D115          | IDDPGM | Current on VDD during<br>Erase/Write         | —      | 5.0  | —      | mA    |                                                                      |

|               |        | Program Flash Memory                         |        |      |        |       |                                                                      |

| D121          | Eр     | Cell Endurance                               | 10K    | —    | —      | E/W   | -40°C ≤ TA ≤ +85°C<br>(Note 1)                                       |

| D122          | Vprw   | VDD for Read/Write                           | VDDMIN | —    | VDDMAX | V     |                                                                      |

| D123          | Tiw    | Self-timed Write Cycle Time                  | _      | 2    | 2.5    | ms    |                                                                      |

| D124          | TRETD  | Characteristic Retention                     | —      | 40   | _      | Year  | Provided no other specifications are violated                        |

| D125          | EHEFC  | High-Endurance Flash Cell                    | 100K   | _    | —      | E/W   | $0^{\circ}C \le TA \le +60^{\circ}C$ , lower byte last 128 addresses |

#### Standard Operating Conditions (unless otherwise stated)

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Self-write and Block Erase.

**2**: Required only if single-supply programming is disabled.

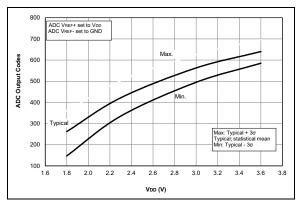

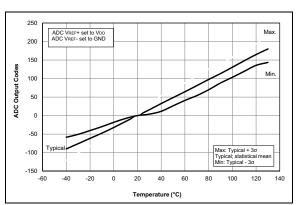

**FIGURE 28-67:** Temperature Indicator Initial Offset, Low Range, Temp = 20°C, LF Devices Only.

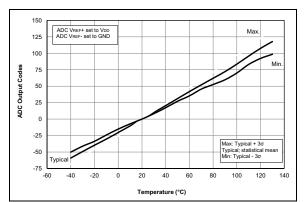

**FIGURE 28-68:** Temperature Indicator Slope Normalized TO 20°C, High Range, VDD = 5.5V, F Devices Only.

**FIGURE 28-69:** Temperature Indicator Slope Normalized TO 20°C, High Range, VDD = 3.6V, F Devices Only.

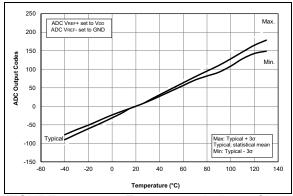

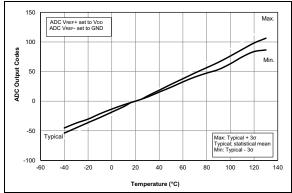

**FIGURE 28-71:** Temperature Indicator Slope Normalized TO 20°C, Low Range, VDD = 1.8V, LF Devices Only.

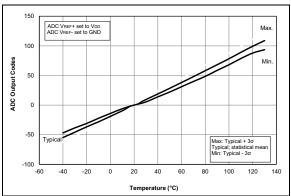

**FIGURE 28-70:** Temperature Indicator Slope Normalized TO 20°C, Low Range, VDD = 3.0V, F Devices Only.

**FIGURE 28-72:** Temperature Indicator Slope Normalized TO 20°C, Low Range, VDD = 3.0V, LF Devices Only.

#### 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

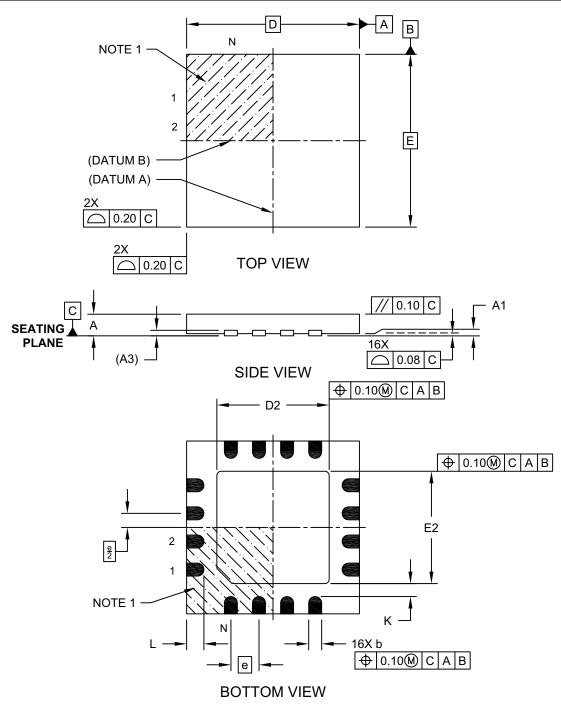

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N                   | MILLIMETERS |          |      |  |  |

|--------------------------|---------------------|-------------|----------|------|--|--|

| Dimension                | MIN                 | NOM         | MAX      |      |  |  |

| Number of Pins           | Number of Pins N 14 |             |          |      |  |  |

| Pitch                    | е                   |             | 0.65 BSC |      |  |  |

| Overall Height           | А                   | I           | -        | 1.20 |  |  |

| Molded Package Thickness | A2                  | 0.80        | 1.00     | 1.05 |  |  |

| Standoff                 | A1                  | 0.05        | -        | 0.15 |  |  |

| Overall Width            | E 6.40 BSC          |             |          |      |  |  |

| Molded Package Width     | E1                  | 4.30        | 4.40     | 4.50 |  |  |

| Molded Package Length    | D                   | 4.90        | 5.00     | 5.10 |  |  |

| Foot Length              | L                   | 0.45        | 0.60     | 0.75 |  |  |

| Footprint                | (L1)                | 1.00 REF    |          |      |  |  |

| Foot Angle               | φ                   | 0°          | -        | 8°   |  |  |

| Lead Thickness           | С                   | 0.09        | -        | 0.20 |  |  |

| Lead Width               | b                   | 0.19        | -        | 0.30 |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2

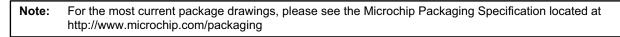

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-257A Sheet 1 of 2

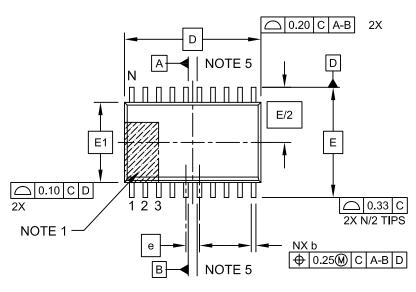

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2

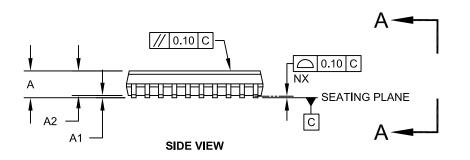

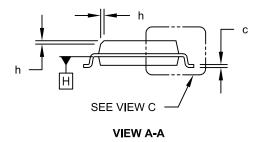

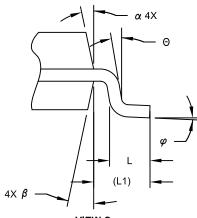

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| VI | EW | С |  |

|----|----|---|--|

|    |    |   |  |

| l                        | MILLIMETERS |           |          |      |  |  |

|--------------------------|-------------|-----------|----------|------|--|--|

| Dimension Lim            | its         | MIN       | NOM      | MAX  |  |  |

| Number of Pins           | N           |           | 20       |      |  |  |

| Pitch                    | е           |           | 1.27 BSC |      |  |  |

| Overall Height           | Α           | -         | -        | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05      | -        | -    |  |  |

| Standoff §               | A1          | 0.10      | -        | 0.30 |  |  |

| Overall Width            | E           | 10.30 BSC |          |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |          |      |  |  |

| Overall Length           | D           | 12.80 BSC |          |      |  |  |

| Chamfer (Optional)       | h           | 0.25      | -        | 0.75 |  |  |

| Foot Length              | L           | 0.40      | -        | 1.27 |  |  |

| Footprint                | L1          |           | 1.40 REF |      |  |  |

| Lead Angle               | Θ           | 0°        | -        | -    |  |  |

| Foot Angle               | $\varphi$   | 0°        | -        | 8°   |  |  |

| Lead Thickness           | С           | 0.20      | -        | 0.33 |  |  |

| Lead Width               | b           | 0.31      | -        | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°        | -        | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -        | 15°  |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2