Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | LINbus, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1579t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-2:PIC16(L)F1574/5 PINOUT DESCRIPTION (CONTINUED)

| Name                                         | Function          | Input<br>Type | Output<br>Type | Description                                          |

|----------------------------------------------|-------------------|---------------|----------------|------------------------------------------------------|

| RC4/ADCACT <sup>(1)</sup> /CK <sup>(1)</sup> | RC4               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

|                                              | ADCACT            | TTL/ST        | —              | ADC Auto-conversion Trigger input.                   |

|                                              | СК                | ST            | CMOS           | USART synchronous clock.                             |

| RC5/RX <sup>(1,3)</sup>                      | RC5               | TTL/ST        | CMOS/OD        | General purpose input with IOC and WPU.              |

|                                              | RX                | ST            | _              | USART asynchronous input.                            |

| OUT <sup>(2)</sup>                           | C10UT             | _             | CMOS           | Comparator output.                                   |

|                                              | C2OUT             | _             | CMOS           | Comparator output.                                   |

|                                              | PWM10UT           | -             | CMOS           | PWM1 output.                                         |

|                                              | PWM2OUT           | -             | CMOS           | PWM2 output.                                         |

|                                              | PWM3OUT           | _             | CMOS           | PWM3 output.                                         |

|                                              | PWM4OUT           | -             | CMOS           | PWM4 output.                                         |

|                                              | CWG1A             | _             | CMOS           | Complementary Output Generator Output A.             |

|                                              | CWG1B             | _             | CMOS           | Complementary Output Generator Output B.             |

|                                              | TX/CK             | -             | CMOS           | USART asynchronous TX data/synchronous clock output. |

|                                              | DT <sup>(3)</sup> | _             | CMOS           | USART synchronous data output.                       |

| VDD                                          | Vdd               | Power         | —              | Positive supply.                                     |

| Vss                                          | Vss               | Power         | —              | Ground reference.                                    |

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal

Levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-1.

3: These USART functions are bidirectional. The output pin selections must be the same as the input pin selections.

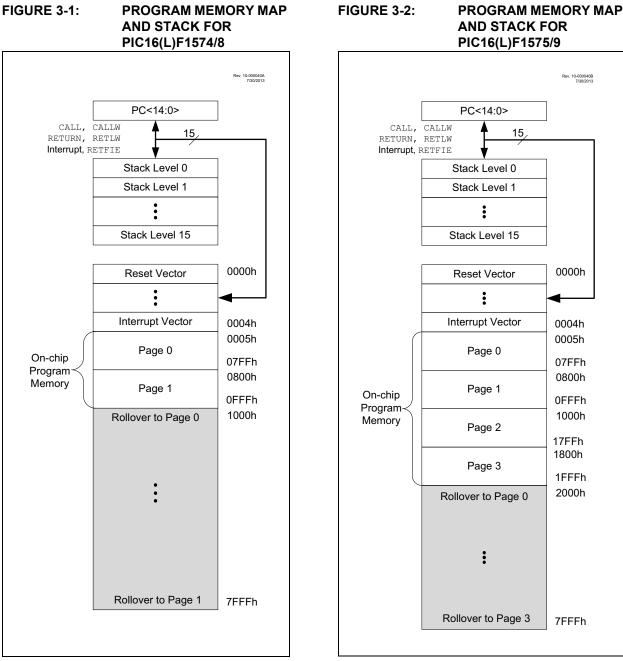

# PIC16(L)F1574/5/8/9

15

0000h

0004h

0005h

07FFh

0800h

0FFFh

1000h

17FFh 1800h

1FFFh 2000h

7FFFh

## TABLE 3-5: PIC16(L)F1578 MEMORY MAP, BANKS 0-7

|       | BANK0                         |        | ,<br>BANK1                    |      | BANK2                         |      | BANK3                         |       | BANK4                         |        | BANK5                         |                      | BANK6                                      |        | BANK7                         |

|-------|-------------------------------|--------|-------------------------------|------|-------------------------------|------|-------------------------------|-------|-------------------------------|--------|-------------------------------|----------------------|--------------------------------------------|--------|-------------------------------|

| 000h  | Core Registers<br>(Table 3-2) | 080h   | Core Registers<br>(Table 3-2) | 100h | Core Registers<br>(Table 3-2) | 180h | Core Registers<br>(Table 3-2) | 200h  | Core Registers<br>(Table 3-2) | 280h   | Core Registers<br>(Table 3-2) | 300h                 | Core Registers<br>(Table 3-2)              | 380h   | Core Registers<br>(Table 3-2) |

| 00Bh  |                               | 08Bh   |                               | 10Bh |                               | 18Bh |                               | 20Bh  |                               | 28Bh   |                               | 30Bh                 |                                            | 38Bh   |                               |

| 00Ch  | PORTA                         | 08Ch   | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch  | WPUA                          | 28Ch   | ODCONA                        | 30Ch                 | SLRCONA                                    | 38Ch   | INLVLA                        |

| 00Dh  | PORTB                         | 08Dh   | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh  | WPUB                          | 28Dh   | ODCONB                        | 30Dh                 | SLRCONB                                    | 38Dh   | INLVLB                        |

| 00Eh  | PORTC                         | 08Eh   | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh  | WPUC                          | 28Eh   | ODCONC                        | 30Eh                 | SLRCONC                                    | 38Eh   | INLVLC                        |

| 00Fh  | _                             | 08Fh   | -                             | 10Fh | _                             | 18Fh | _                             | 20Fh  | _                             | 28Fh   | _                             | 30Fh                 | _                                          | 38Fh   | —                             |

| 010h  | _                             | 090h   | -                             | 110h | _                             | 190h | _                             | 210h  | _                             | 290h   | _                             | 310h                 | _                                          | 390h   | —                             |

| 011h  | PIR1                          | 091h   | PIE1                          | 111h | CM1CON0                       | 191h | PMADRL                        | 211h  | —                             | 291h   | —                             | 311h                 | —                                          | 391h   | IOCAP                         |

| 012h  | PIR2                          | 092h   | PIE2                          | 112h | CM1CON1                       | 192h | PMADRH                        | 212h  | —                             | 292h   | —                             | 312h                 | —                                          | 392h   | IOCAN                         |

| 013h  | PIR3                          | 093h   | PIE3                          | 113h | CM2CON0                       | 193h | PMDATL                        | 213h  | _                             | 293h   | _                             | 313h                 | —                                          | 393h   | IOCAF                         |

| 014h  | —                             | 094h   | —                             | 114h | CM2CON1                       | 194h | PMDATH                        | 214h  | _                             | 294h   | _                             | 314h                 | —                                          | 394h   | IOCBP                         |

| 015h  | TMR0                          | 095h   | OPTION_REG                    | 115h | CMOUT                         | 195h | PMCON1                        | 215h  | _                             | 295h   | _                             | 315h                 | —                                          | 395h   | IOCBN                         |

| 016h  | TMR1L                         | 096h   | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h  | _                             | 296h   | _                             | 316h                 |                                            | 396h   | IOCBF                         |

| 017h  | TMR1H                         | 097h   | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(1)</sup>        | 217h  | _                             | 297h   | _                             | 317h                 | _                                          | 397h   | IOCCP                         |

| 018h  | T1CON                         | 098h   | OSCTUNE                       | 118h | DACCON0                       | 198h | —                             | 218h  | —                             | 298h   | —                             | 318h                 | —                                          | 398h   | IOCCN                         |

| 019h  | T1GCON                        | 099h   | OSCCON                        | 119h | DACCON1                       | 199h | RCREG                         | 219h  | _                             | 299h   | _                             | 319h                 | —                                          | 399h   | IOCCF                         |

| 01Ah  | TMR2                          | 09Ah   | OSCSTAT                       | 11Ah | —                             | 19Ah | TXREG                         | 21Ah  | —                             | 29Ah   | —                             | 31Ah                 |                                            | 39Ah   | —                             |

| 01Bh  | PR2                           | 09Bh   | ADRESL                        | 11Bh | —                             | 19Bh | SPBRGL                        | 21Bh  | —                             | 29Bh   | —                             | 31Bh                 |                                            | 39Bh   | —                             |

| 01Ch  | T2CON                         | 09Ch   | ADRESH                        | 11Ch | —                             | 19Ch | SPBRGH                        | 21Ch  | —                             | 29Ch   | —                             | 31Ch                 | _                                          | 39Ch   | —                             |

| 01Dh  | —                             | 09Dh   | ADCON0                        | 11Dh | —                             | 19Dh | RCSTA                         | 21Dh  | —                             | 29Dh   | —                             | 31Dh                 | —                                          | 39Dh   | —                             |

| 01Eh  |                               | 09Eh   | ADCON1                        | 11Eh | —                             | 19Eh | TXSTA                         | 21Eh  | _                             | 29Eh   | _                             | 31Eh                 |                                            | 39Eh   | —                             |

| 01Fh  | _                             | 09Fh   | ADCON2                        | 11Fh | —                             | 19Fh | BAUDCON                       | 21Fh  | _                             | 29Fh   | _                             | 31Fh                 | _                                          | 39Fh   | _                             |

| 020h  | General<br>Purpose            | 0A0h   | General<br>Purpose            | 120h | General<br>Purpose            | 1A0h | General<br>Purpose            | 220h  | General<br>Purpose            | 2A0h   | General<br>Purpose            | 320h<br>32Fh<br>330h | General<br>Purpose<br>Register<br>16 Bytes | 3A0h   | Unimplemented<br>Read as '0'  |

| 06Fh  | Register<br>80 Bytes          | 0EFh   | Register<br>80 Bytes          | 16Fh | Register<br>80 Bytes          | 1EFh | Register<br>80 Bytes          | 26Fh  | Register<br>80 Bytes          | 2EFh   | Register<br>80 Bytes          | 36Fh                 | Unimplemented<br>Read as '0'               | 3EFh   | Read as 0                     |

| 070h  |                               | 0F0h   |                               | 170h |                               | 1F0h |                               | 270h  |                               | 2F0h   |                               | 370h                 |                                            | 3F0h   |                               |

| 0.011 | Common RAM                    | 5. 611 | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         | 2.011 | Accesses<br>70h – 7Fh         | 2. 011 | Accesses<br>70h – 7Fh         | 0.011                | Accesses<br>70h – 7Fh                      | 5. 0.1 | Accesses<br>70h – 7Fh         |

| 07Fh  |                               | 0FFh   |                               | 17Fh |                               | 1FFh |                               | 27Fh  |                               | 2FFh   |                               | 37Fh                 |                                            | 3FFh   |                               |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1578.

## 3.3.6 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-14 can be addressed from any Bank.

| Addr            | Name      | Bit 7                                                    | Bit 6                                                                                                     | Bit 5         | Bit 4        | Bit 3        | Bit 2         | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|-----------------|-----------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------|--------------|--------------|---------------|--------|-----------|----------------------|---------------------------|

| Bank            | Bank 0-31 |                                                          |                                                                                                           |               |              |              |               |        |           |                      |                           |

| x00h or<br>x80h | INDF0     |                                                          | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |               |              |              |               |        |           |                      | uuuu uuuu                 |

| x01h or<br>x81h | INDF1     |                                                          | this location<br>ical register)                                                                           |               | nts of FSR1H | /FSR1L to ad | ddress data i | memory |           | xxxx xxxx            | uuuu uuuu                 |

| x02h or<br>x82h | PCL       | Program C                                                | ounter (PC) I                                                                                             | Least Signifi | cant Byte    |              |               |        |           | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h | STATUS    | _                                                        |                                                                                                           |               | TO           | PD           | Z             | DC     | С         | 1 1000               | q quuu                    |

| x04h or<br>x84h | FSR0L     | Indirect Data Memory Address 0 Low Pointer               |                                                                                                           |               |              |              |               |        |           | 0000 0000            | uuuu uuuu                 |

| x05h or<br>x85h | FSR0H     | Indirect Da                                              | Indirect Data Memory Address 0 High Pointer                                                               |               |              |              |               |        |           | 0000 0000            | 0000 0000                 |

| x06h or<br>x86h | FSR1L     | Indirect Da                                              | Indirect Data Memory Address 1 Low Pointer                                                                |               |              |              |               |        |           | 0000 0000            | uuuu uuuu                 |

| x07h or<br>x87h | FSR1H     | Indirect Da                                              | ta Memory A                                                                                               | ddress 1 Hig  | gh Pointer   |              |               |        |           | 0000 0000            | 0000 0000                 |

| x08h or<br>x88h | BSR       | _                                                        | -                                                                                                         | _             |              |              | BSR<4:0>      |        |           | 0 0000               | 0 0000                    |

| x09h or<br>x89h | WREG      | Working Register                                         |                                                                                                           |               |              |              |               |        |           | 0000 0000            | uuuu uuuu                 |

| x0Ahor<br>x8Ah  | PCLATH    | Write Buffer for the upper 7 bits of the Program Counter |                                                                                                           |               |              |              |               |        | -000 0000 | -000 0000            |                           |

| x0Bhor<br>x8Bh  | INTCON    | GIE                                                      | PEIE                                                                                                      | TMR0IE        | INTE         | IOCIE        | TMR0IF        | INTF   | IOCIF     | 0000 0000            | 0000 0000                 |

#### TABLE 3-14: CORE FUNCTION REGISTERS SUMMARY

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

| U-0                                     | U-0               | R/W-0/0              | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|-----------------------------------------|-------------------|----------------------|-----------------|------------------|------------------|----------------|--------------|

|                                         | _                 |                      |                 | TUN              | <5:0>            |                |              |

| bit 7                                   |                   |                      |                 |                  |                  |                | bit 0        |

|                                         |                   |                      |                 |                  |                  |                |              |

| Legend:                                 |                   |                      |                 |                  |                  |                |              |

| R = Readab                              | le bit            | W = Writable         | bit             | U = Unimpler     | nented bit, read | d as '0'       |              |

| u = Bit is unchanged x = Bit is unknown |                   |                      |                 | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is se                         | et                | '0' = Bit is cleared |                 |                  |                  |                |              |

|                                         |                   |                      |                 |                  |                  |                |              |

| bit 7-6                                 | Unimpleme         | nted: Read as '      | 0'              |                  |                  |                |              |

| bit 5-0                                 | TUN<5:0>:         | Frequency Tunir      | ng bits         |                  |                  |                |              |

|                                         | 100000 = N        | Ainimum frequer      | псу             |                  |                  |                |              |

|                                         | •                 |                      |                 |                  |                  |                |              |

|                                         | •                 |                      |                 |                  |                  |                |              |

|                                         | 111111 =          |                      |                 |                  |                  |                |              |

|                                         | 000000 = <b>C</b> | Oscillator module    | e is running at | the factory-cali | brated frequen   | cy.            |              |

|                                         | 000001 =          |                      |                 |                  |                  |                |              |

|                                         | •                 |                      |                 |                  |                  |                |              |

|                                         | •                 |                      |                 |                  |                  |                |              |

|                                         | 011110 =          |                      |                 |                  |                  |                |              |

|                                         | 011111 = 🛚        | Maximum freque       | ncy             |                  |                  |                |              |

### REGISTER 5-3: OSCTUNE: OSCILLATOR TUNING REGISTER

## 9.6 Register Definitions: Watchdog Control

| U-0                                   | U-0                                                          | R/W-0/0                                                        | R/W-1/1        | R/W-0/0           | R/W-1/1        | R/W-1/1  | R/W-0/0      |

|---------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|----------------|-------------------|----------------|----------|--------------|

| _                                     | —                                                            |                                                                |                | WDTPS<4:0>        |                |          | SWDTEN       |

| oit 7                                 |                                                              |                                                                |                |                   |                |          | bit (        |

| .egend:                               |                                                              |                                                                |                |                   |                |          |              |

| R = Readable                          | e bit                                                        | W = Writable                                                   | bit            | U = Unimpleme     | ented bit, rea | d as '0' |              |

|                                       |                                                              | x = Bit is unkr                                                | nown           | -n/n = Value at   |                |          | other Resets |

| '1' = Bit is set '0' = Bit is cleared |                                                              |                                                                |                |                   |                |          |              |

|                                       |                                                              |                                                                |                |                   |                |          |              |

| it 7-6                                | -                                                            | <b>nted:</b> Read as '<br><b>)&gt;:</b> Watchdog Ti            |                | alaat hita(1)     |                |          |              |

| oit 5-1                               |                                                              | -                                                              | Ther Period S  | elect bits, ,     |                |          |              |

|                                       |                                                              | Prescale Rate                                                  |                | interval (1:22)   |                |          |              |

|                                       | 11111 = R                                                    | eserved. Results                                               |                | intervar (1.52)   |                |          |              |

|                                       | •                                                            |                                                                |                |                   |                |          |              |

|                                       | •                                                            |                                                                |                |                   |                |          |              |

|                                       | 10011 = R                                                    | eserved. Results                                               | s in minimum   | interval (1:32)   |                |          |              |

|                                       | 10010 = <b>1</b> :                                           | 8388608 (2 <sup>23</sup> ) (                                   | Interval 256s  | nominal)          |                |          |              |

|                                       | 10001 = 1:4194304 (2 <sup>22</sup> ) (Interval 128s nominal) |                                                                |                |                   |                |          |              |

|                                       | 10000 = <b>1</b> :                                           | 2097152 (2 <sup>21</sup> ) (1<br>1048576 (2 <sup>20</sup> ) (1 | Interval 64s r | iominal)          |                |          |              |

|                                       | 01111 = 1:                                                   | 1048576 (2 <sup>20</sup> ) (1                                  | Interval 32s r | nominal)          |                |          |              |

|                                       | 01110 = 1:                                                   | 524288 (2 <sup>19</sup> ) (In                                  | iterval 16s no | ominal)           |                |          |              |

|                                       |                                                              | 262144 (2 <sup>18</sup> ) (In<br>131072 (2 <sup>17</sup> ) (In |                |                   |                |          |              |

|                                       |                                                              | 65536 (Interval                                                |                | ,                 |                |          |              |

|                                       |                                                              | 32768 (Interval                                                |                |                   |                |          |              |

|                                       |                                                              | 16384 (Interval                                                |                | nal)              |                |          |              |

|                                       |                                                              | 8192 (Interval 2                                               |                |                   |                |          |              |

|                                       |                                                              | 4096 (Interval 1                                               |                |                   |                |          |              |

|                                       |                                                              | 2048 (Interval 6                                               |                |                   |                |          |              |

|                                       |                                                              | 1024 (Interval 3                                               |                | ·                 |                |          |              |

|                                       |                                                              | 512 (Interval 16<br>256 (Interval 8 r                          |                |                   |                |          |              |

|                                       |                                                              | 128 (Interval 4 r                                              |                |                   |                |          |              |

|                                       |                                                              | 64 (Interval 2 m                                               | ,              |                   |                |          |              |

|                                       |                                                              | 32 (Interval 1 m                                               | ,              |                   |                |          |              |

| oit O                                 | SWDTEN: S                                                    | Software Enable/                                               | Disable for V  | Vatchdog Timer bi | it             |          |              |

|                                       | <u>If WDTE&lt;1:</u> (                                       | )> = 1x:                                                       |                | ·                 |                |          |              |

|                                       | This bit is ig                                               | nored.                                                         |                |                   |                |          |              |

|                                       | If WDTE<1:                                                   |                                                                |                |                   |                |          |              |

|                                       | 1 = WDT is                                                   |                                                                |                |                   |                |          |              |

|                                       | 0 = WDT is<br><u>If WDTE&lt;1:</u> (                         |                                                                |                |                   |                |          |              |

|                                       |                                                              |                                                                |                |                   |                |          |              |

#### REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-1           | R/W-0/0           | R/W-0/0                                                                                                                                                                                       | R/W/HC-0/0            | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0           | R/S/HC-0/0           | R/S/HC-0/0       |  |

|---------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|-------------------|----------------------|------------------|--|

| (1)           | CFGS              | LWLO <sup>(3)</sup>                                                                                                                                                                           | FREE                  | WRERR                     | WREN              | WR                   | RD               |  |

| bit 7         |                   |                                                                                                                                                                                               |                       |                           |                   |                      | bit (            |  |

| Legend:       |                   |                                                                                                                                                                                               |                       |                           |                   |                      |                  |  |

| R = Reada     | able bit          | W = Writable b                                                                                                                                                                                | it                    | U = Unimpleme             | nted bit, read as | s 'O'                |                  |  |

|               | n only be set     | x = Bit is unkno                                                                                                                                                                              |                       | •                         | -                 | √alue at all other Ⅰ | Resets           |  |

| '1' = Bit is  | set               | '0' = Bit is clea                                                                                                                                                                             | red                   | HC = Bit is clear         |                   |                      |                  |  |

| <b>h</b> :+ 7 |                   | tod. Dood on (1)                                                                                                                                                                              |                       |                           |                   |                      |                  |  |

| bit 7         | -                 | ted: Read as '1'                                                                                                                                                                              |                       |                           |                   |                      |                  |  |

| bit 6         | •                 | guration Select bit<br>Configuration, Use                                                                                                                                                     |                       | ID Registers              |                   |                      |                  |  |

|               |                   | Flash program me                                                                                                                                                                              |                       | ID Registers              |                   |                      |                  |  |

| bit 5         | LWLO: Load        | Write Latches On                                                                                                                                                                              | ly bit <sup>(3)</sup> |                           |                   |                      |                  |  |

|               |                   | 1 = Only the addressed program memory write latch is loaded/updated on the next WR command                                                                                                    |                       |                           |                   |                      |                  |  |

|               |                   | ressed program m                                                                                                                                                                              | •                     | h is loaded/update        | ed and a write of | all program mem      | ory write latche |  |

|               |                   | itiated on the nex                                                                                                                                                                            |                       |                           |                   |                      |                  |  |

| bit 4         | •                 | am Flash Erase E                                                                                                                                                                              |                       |                           |                   |                      |                  |  |

|               |                   | s an erase operati<br>s an write operatio                                                                                                                                                     |                       |                           | rdware cleared    | upon completion)     |                  |  |

| bit 3         |                   | gram/Erase Error                                                                                                                                                                              |                       |                           |                   |                      |                  |  |

|               |                   | n indicates an im                                                                                                                                                                             |                       | or erase sequend          | e attempt or te   | rmination (bit is s  | et automatical   |  |

|               |                   | et attempt (write '                                                                                                                                                                           | ,                     | ,                         |                   |                      |                  |  |

|               | 0 = The prog      | gram or erase ope                                                                                                                                                                             | ration completed      | d normally.               |                   |                      |                  |  |

| bit 2         | •                 | am/Erase Enable                                                                                                                                                                               |                       |                           |                   |                      |                  |  |

|               | •                 | rogram/erase cyc<br>programming/eras                                                                                                                                                          |                       | lach                      |                   |                      |                  |  |

| bit 1         | WR: Write Co      | 0 0                                                                                                                                                                                           | ing of program i      | 10311                     |                   |                      |                  |  |

|               |                   | a program Flash                                                                                                                                                                               | orogram/erase o       | peration                  |                   |                      |                  |  |

|               |                   | ration is self-timed                                                                                                                                                                          | 0                     | •                         | re once operatio  | on is complete.      |                  |  |

|               |                   | bit can only be se                                                                                                                                                                            | , ,                   |                           |                   |                      |                  |  |

|               | 0 = Program       | /erase operation                                                                                                                                                                              | to the Flash is co    | omplete and inact         | ive.              |                      |                  |  |

| bit 0         | RD: Read Co       |                                                                                                                                                                                               |                       |                           |                   |                      |                  |  |

|               |                   | a program Flash r                                                                                                                                                                             | ead. Read takes       | s one cycle. RD is        | cleared in hard   | lware. The RD bit    | can only be se   |  |

|               | •                 | red) in software.<br>t initiate a prograr                                                                                                                                                     | n Flash read.         |                           |                   |                      |                  |  |

| Note 1:       | Unimplemented bit |                                                                                                                                                                                               |                       |                           |                   |                      |                  |  |

| 2:            | •                 |                                                                                                                                                                                               | by hardware whe       | en a program mer          | nory write or era | ase operation is st  | arted (WR = 1    |  |

| 3:            |                   | e WRERR bit is automatically set by hardware when a program memory write or erase operation is started (WR = 1<br>the LWLO bit is ignored during a program memory erase operation (FREE = 1). |                       |                           |                   |                      |                  |  |

## REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

| U-0                                   | U-0       | R/W-x/u         | R/W-x/u | U-0                                | R/W-x/u        | R/W-x/u          | R/W-x/u     |  |  |

|---------------------------------------|-----------|-----------------|---------|------------------------------------|----------------|------------------|-------------|--|--|

| —                                     | _         | LATA5           | LATA4   | —                                  | LATA2          | LATA1            | LATA0       |  |  |

| bit 7                                 |           |                 |         |                                    |                |                  | bit 0       |  |  |

|                                       |           |                 |         |                                    |                |                  |             |  |  |

| Legend:                               |           |                 |         |                                    |                |                  |             |  |  |

| R = Readable b                        | oit       | W = Writable    | bit     | U = Unimplemented bit, read as '0' |                |                  |             |  |  |

| u = Bit is uncha                      | anged     | x = Bit is unkr | nown    | -n/n = Value a                     | at POR and BOF | R/Value at all o | ther Resets |  |  |

| '1' = Bit is set '0' = Bit is cleared |           |                 |         |                                    |                |                  |             |  |  |

|                                       |           |                 |         |                                    |                |                  |             |  |  |

| bit 7-6                               | Unimpleme | nted: Read as ' | כ'      |                                    |                |                  |             |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 5-4 | LATA<5:4>: RA<5:4> Output Latch Value bits <sup>(1)</sup> |

- bit 3 Unimplemented: Read as '0'

- bit 2-0 LATA<2:0>: RA<2:0> Output Latch Value bits<sup>(1)</sup>

- **Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|---------|-----|---------|---------|---------|

| —     | —   |     | ANSA4   | _   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ANSA4: Analog Select between Analog or Digital Function on pins RA4, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul>                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to                                                                                                                                                                                                           |

allow external control of the voltage on the pin.

| R/W-1/1              | R/W-1/1                                                                                                                                                                                                                                                                                                                                | U-0                | U-0              | R/W-1/1                                                                  | R/W-1/1          | R/W-1/1                 | R/W-1/1                    |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|--------------------------------------------------------------------------|------------------|-------------------------|----------------------------|--|

| ANSC7 <sup>(2)</sup> | ANSC6 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                   |                    | _                | ANSC3                                                                    | ANSC2            | ANSC1                   | ANSC0                      |  |

| bit 7                |                                                                                                                                                                                                                                                                                                                                        |                    |                  |                                                                          |                  |                         | bit C                      |  |

|                      |                                                                                                                                                                                                                                                                                                                                        |                    |                  |                                                                          |                  |                         |                            |  |

| Legend:              |                                                                                                                                                                                                                                                                                                                                        |                    |                  |                                                                          |                  |                         |                            |  |

| R = Readable         | bit                                                                                                                                                                                                                                                                                                                                    | W = Writable       | bit              | U = Unimpler                                                             | nented bit, read | d as '0'                |                            |  |

| u = Bit is unchanged |                                                                                                                                                                                                                                                                                                                                        | x = Bit is unknown |                  | -n/n = Value at POR and BOR/Value at all other Resets                    |                  |                         |                            |  |

| '1' = Bit is set     |                                                                                                                                                                                                                                                                                                                                        | '0' = Bit is clea  | ared             |                                                                          |                  |                         |                            |  |

| bit 7-6              | 0 = Digital I/                                                                                                                                                                                                                                                                                                                         | O. Pin is assigr   | ned to port or o | og or Digital Fu<br>digital special fu<br>og input <sup>(1)</sup> . Digi | inction.         |                         | ectively <sup>(1, 2)</sup> |  |

| bit 5-4              | bit 5-4 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                     |                    |                  |                                                                          |                  |                         |                            |  |

| bit 3-0              | <ul> <li><b>ANSC&lt;3:0&gt;</b>: Analog Select between Analog or Digital Function on pins RC&lt;3:0&gt;, respectively<sup>(1)</sup></li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |                    |                  |                                                                          |                  | ectively <sup>(1)</sup> |                            |  |

| Note 1: Wh           | nen setting a pir                                                                                                                                                                                                                                                                                                                      | •                  | •                | esponding TRIS                                                           | S bit must be se | et to Input mod         | e in order to              |  |

allow external control of the voltage on the pin. 2: ANSC<7:6> are available on PIC16(L)F1578/9 only.

#### REGISTER 11-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| WPUC7 <sup>(3)</sup> | WPUC6 <sup>(3)</sup> | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(3)</sup>

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

3: WPUC<7:6> are available on PIC16(L)F1578/9 only.

| REGISTER 13-4: | IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER <sup>(1)</sup> |

|----------------|------------------------------------------------------------------------|

|----------------|------------------------------------------------------------------------|

| R/W-0/0                               | R/W-0/0 | R/W-0/0           | R/W-0/0 | U-0             | U-0                  | U-0                 | U-0   |

|---------------------------------------|---------|-------------------|---------|-----------------|----------------------|---------------------|-------|

| IOCBP7                                | IOCBP6  | IOCBP5            | IOCBP4  | _               | —                    | —                   | —     |

| bit 7                                 |         |                   |         |                 |                      |                     | bit 0 |

|                                       |         |                   |         |                 |                      |                     |       |

| Legend:                               |         |                   |         |                 |                      |                     |       |

| R = Readable bi                       | t       | W = Writable bit  | :       | U = Unimpleme   | ented bit, read as ' | כי                  |       |

| u = Bit is unchar                     | nged    | x = Bit is unknow | wn      | -n/n = Value at | POR and BOR/Va       | lue at all other Re | esets |

| '1' = Bit is set '0' = Bit is cleared |         |                   | ed      |                 |                      |                     |       |

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

#### REGISTER 13-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER<sup>(1)</sup>

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | —   | -   | _   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 **IOCBN<7:4>**: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

- bit 3-0 Unimplemented: Read as '0'

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

#### REGISTER 13-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER<sup>(1)</sup>

| R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0   |

|------------|------------|------------|------------|-----|-----|-----|-------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | —   | —   | —   | —     |

| bit 7      | -          |            |            |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | IOCBF<7:4>: Interrupt-on-Change PORTB Flag bits                                                      |

|---------|------------------------------------------------------------------------------------------------------|

|         | 1 = An enabled change was detected on the associated pin.                                            |

|         | Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was |

|         | detected on RBx.                                                                                     |

|         | 0 = No change was detected, or the user cleared the detected change.                                 |

|         |                                                                                                      |

bit 3-0 Unimplemented: Read as '0'

Note 1: PORTB functions available on PIC16(L)F1578/9 devices only.

| Name                 | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------------------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELA               | _                     | _                     | _      | ANSA4  | —      | ANSA2  | ANSA1  | ANSA0  | 121                 |

| INTCON               | GIE                   | PEIE                  | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 86                  |

| IOCAF                | —                     | _                     | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 143                 |

| IOCAN                | _                     | _                     | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 143                 |

| IOCAP                | —                     | _                     | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 143                 |

| IOCBP <sup>(2)</sup> | IOCBP7                | IOCBP6                | IOCBP5 | IOCBP4 | _      | _      | _      | _      | 144                 |

| IOCBN <sup>(2)</sup> | IOCBN7                | IOCBN6                | IOCBN5 | IOCBN4 | _      | _      | _      | _      | 144                 |

| IOCBF <sup>(2)</sup> | IOCBF7                | IOCBF6                | IOCBF5 | IOCBF4 | _      | _      | _      | _      | 144                 |

| IOCCP                | IOCCP7 <sup>(2)</sup> | IOCCP6 <sup>(2)</sup> | IOCCP5 | IOCCP4 | IOCCP3 | IOCCP2 | IOCCP1 | IOCCP0 | 145                 |

| IOCCN                | IOCCN7 <sup>(2)</sup> | IOCCN6 <sup>(2)</sup> | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 | 145                 |

| IOCCF                | IOCCF7 <sup>(2)</sup> | IOCCF6 <sup>(2)</sup> | IOCCF5 | IOCCF4 | IOCCF3 | IOCCF2 | IOCCF1 | IOCCF0 | 145                 |

| TRISA                | _                     | _                     | TRISA5 | TRISA4 | —(1)   | TRISA2 | TRISA1 | TRISA0 | 120                 |

| TRISC                | TRISC7 <sup>(2)</sup> | TRISC7 <sup>(2)</sup> | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 131                 |

### TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1578/9 only.

#### 23.3 Offset Modes

The Offset modes provide the means to adjust the waveform of a slave PWM module relative to the waveform of a master PWM module in the same device.

#### 23.3.1 INDEPENDENT RUN MODE

In Independent Run mode (OFM = 00), the PWM module is unaffected by the other PWM modules in the device. The PWMxTMR associated with the PWM module in this mode starts counting as soon as the EN bit associated with this PWM module is set and continues counting until the EN bit is cleared. Period events reset the PWMxTMR to zero after which the timer continues to count.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 23-8.

#### 23.3.2 SLAVE RUN MODE WITH SYNC START

In Slave Run mode with Sync Start (OFM = 01), the slave PWMxTMR waits for the master's OF\_match event. When this event occurs, if the EN bit is set, the PWMxTMR begins counting and continues to count until software clears the EN bit. Slave period events reset the PWMxTMR to zero after which the timer continues to count.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 23-9.

#### 23.3.3 ONE-SHOT SLAVE MODE WITH SYNC START

In One-Shot Slave mode with Synchronous Start (OFM = 10), the slave PWMxTMR waits until the master's OF\_match event. The timer then begins counting, starting from the value that is already in the timer and continues to count until the period match event. When the period event occurs, the timer resets to zero and stops counting. The timer then waits until the next master OF\_match event, after which it begins counting again to repeat the cycle. An OF\_match event that occurs before the slave PWM has completed the previously triggered period will be ignored. A slave period that is greater than the master period, but less than twice the master period, will result in a slave output every other master period.

Note: During the time the slave timers are resetting to zero, if another Offset Match event is received, it is possible that the slave PWM would not recognize this match event and the slave timers would fail to begin counting again. This would result in missing duty cycles from the output of the slave PWM. To prevent this from happening, avoid using the same period for both the master and slave PWM's.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 23-10.

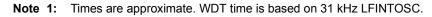

#### 23.3.4 CONTINUOUS RUN SLAVE MODE WITH SYNC START AND TIMER RESET

In Continuous Run Slave mode with Synchronous Start and Timer Reset (OFM = 11) the slave PWMxTMR is inhibited from counting after the slave PWM enable is set. The first master OF match event starts the slave PWMxTMR. Subsequent master OF\_match events reset the slave PWMxTMR timer value back to 1 after which the slave PWMxTMR continues to count. The next master OF match event resets the slave PWMxTMR back to 1 to repeat the cycle. Slave period events that occur before the master's OF match event will reset the slave PWMxTMR to zero after which the timer will continue to count. Slaves operating in this mode must have a PWMxPH register pair value equal to or greater than 1, otherwise, the phase match event will not occur precluding the start of the PWM output duty cycle.

The offset timing will persist If both the master and slave PWMxPR values are the same and the Slave Offset mode is changed to Independent Run mode while the PWM module is operating.

A detailed timing diagram of this mode used in Standard PWM mode is shown in Figure 23-11.

| Note: | Unexpected results will occur if the slave |

|-------|--------------------------------------------|

|       | PWM_clock is a higher frequency than the   |

|       | master PWM_clock.                          |

#### 23.3.5 OFFSET MATCH IN CENTER-ALIGNED MODE

When a master is operating in Center-Aligned mode the offset match event depends on which direction the PWMxTMR is counting. Clearing the OFO bit of the PWMxOFCON register will cause the OF\_match event to occur when the timer is counting up. Setting the OFO bit of the PWMxOFCON register will cause the OF\_match event to occur when the timer is counting down. The OFO bit is ignored in non-center-aligned modes.

The OFO bit is double buffered and requires setting the LDA bit to take effect when the PWM module is operating.

Detailed timing diagrams of Center-Aligned mode using offset match control in Independent Slave with Sync Start mode can be seen in Figure 23-12 and Figure 23-13.

PIC16(L)F1574/5/8/9

| Name     | Bit 7 | Bit 6   | Bit 5        | Bit 4  | Bit 3    | Bit 2    | Bit 1     | Bit 0  | Register<br>on Page |

|----------|-------|---------|--------------|--------|----------|----------|-----------|--------|---------------------|

| ANSELA   | _     | _       | _            | ANSA4  | —        | ANSA2    | ANSA1     | ANSA0  | 121                 |

| CWG1CON0 | G1EN  | _       | _            | G1POLB | G1POLA   | _        | _         | G1CS0  | 253                 |

| CWG1CON1 | G1ASD | LB<1:0> | G1ASDLA<1:0> |        |          |          | 254       |        |                     |

| CWG1CON2 | G1ASE | G1ARSEN | _            | —      | G1ASDSC2 | G1ASDSC1 | G1ASDSPPS | _      | 255                 |

| CWG1DBF  | _     | _       | CWG1DBF<5:0> |        |          |          |           | 256    |                     |

| CWG1DBR  | _     | _       | CWG1DBR<5:0> |        |          |          |           | 256    |                     |

| TRISA    |       | —       | TRISA5       | TRISA4 | _(1)     | TRISA2   | TRISA1    | TRISA0 | 120                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by CWG. **Note 1:** Unimplemented, read as '1'.

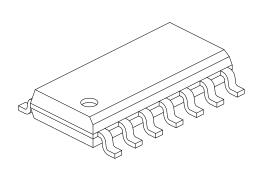

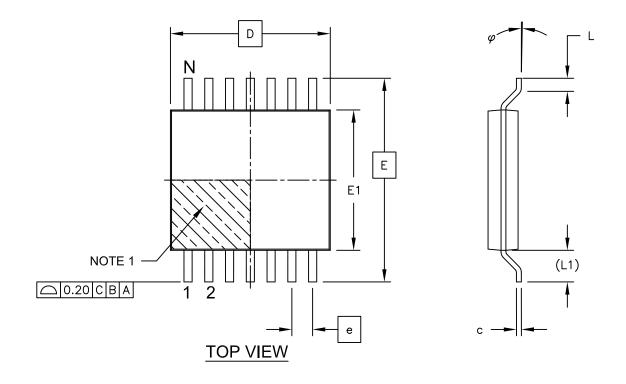

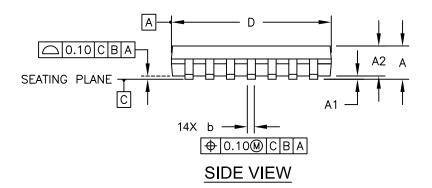

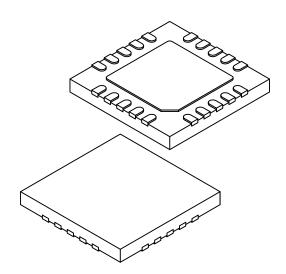

#### 30.2 Package Details

The following sections give the technical details of the packages.

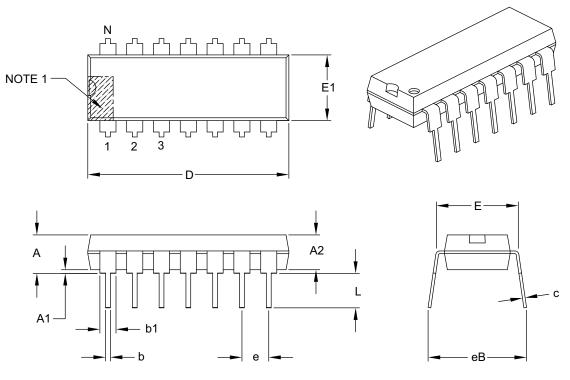

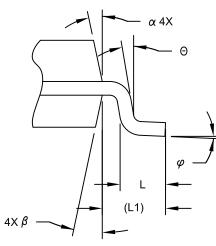

#### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      |      | INCHES   |      |  |

|----------------------------|------------|------|----------|------|--|

| Dimens                     | ion Limits | MIN  | NOM      | MAX  |  |

| Number of Pins             | Ν          | 14   |          |      |  |

| Pitch                      | е          |      | .100 BSC |      |  |

| Top to Seating Plane       | А          | -    | -        | .210 |  |

| Molded Package Thickness   | A2         | .115 | .130     | .195 |  |

| Base to Seating Plane      | A1         | .015 | -        | _    |  |

| Shoulder to Shoulder Width | E          | .290 | .310     | .325 |  |

| Molded Package Width       | E1         | .240 | .250     | .280 |  |

| Overall Length             | D          | .735 | .750     | .775 |  |

| Tip to Seating Plane       | L          | .115 | .130     | .150 |  |

| Lead Thickness             | С          | .008 | .010     | .015 |  |

| Upper Lead Width           | b1         | .045 | .060     | .070 |  |

| Lower Lead Width           | b          | .014 | .018     | .022 |  |

| Overall Row Spacing §      | eB         | -    | -        | .430 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.