##

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                               |

| Core Processor             | V850ES                                                                                 |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 48MHz                                                                                  |

| Connectivity               | CANbus, CSI, EBI/EMI, I <sup>2</sup> C, UART/USART, USB                                |

| Peripherals                | DMA, LVD, PWM, WDT                                                                     |

| Number of I/O              | 32                                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 8K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                           |

| Data Converters            | A/D 6x10b; D/A 1x8b                                                                    |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 48-LQFP                                                                                |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3814ga-r-gam-ax |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### (5) TAAn I/O control register 2 (TAAnIOC2)

The TAAnIOC2 register is an 8-bit register that controls the valid edge of the external event count input signal (TIAAn0 pin) and external trigger input signal (TIAAn0 pin).

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

|                       | set: 00H | R/W                                                                                                         | Address:                                                                                                   |                                                                                                | C2 FFFFF6<br>C2 FFFFF6                                                                                                | 534H, TAA1I<br>554H                                                                                                      | OC2 FFF                                                                 | FF644H,                                          |

|-----------------------|----------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------|

|                       | 7        | 6                                                                                                           | 5                                                                                                          | 4                                                                                              | 3                                                                                                                     | 2                                                                                                                        | 1                                                                       | 0                                                |

| TAAnIOC2 (n = 0 to 2) | 0        | 0                                                                                                           | 0                                                                                                          | 0                                                                                              | TAAnEES1                                                                                                              | TAAnEES0 T                                                                                                               | AAnETS1                                                                 | TAAnETS0                                         |

|                       | TAAnEES1 | TAAnEES0                                                                                                    | External e                                                                                                 | vent coun                                                                                      | t input signal                                                                                                        | (TIAAn0 pin                                                                                                              | ) valid edg                                                             | ge setting                                       |

|                       | 0        | 0                                                                                                           | No edge o                                                                                                  | detection                                                                                      | (external ev                                                                                                          | ent count inv                                                                                                            | valid)                                                                  |                                                  |

|                       | 0        | 1                                                                                                           | Detection                                                                                                  | of rising                                                                                      | edge                                                                                                                  |                                                                                                                          |                                                                         |                                                  |

|                       | 1        | 0                                                                                                           | Detection                                                                                                  | of falling                                                                                     | edge                                                                                                                  |                                                                                                                          |                                                                         |                                                  |

|                       | 1        | 1                                                                                                           | Detection                                                                                                  | of both e                                                                                      | dges                                                                                                                  |                                                                                                                          |                                                                         |                                                  |

|                       |          |                                                                                                             |                                                                                                            |                                                                                                |                                                                                                                       |                                                                                                                          |                                                                         |                                                  |

|                       |          | TAAnETS0                                                                                                    | External                                                                                                   | trigger in                                                                                     | put signal (T                                                                                                         | וAAn0 pin) א                                                                                                             | alid edge                                                               | setting                                          |

|                       | 0        | 0                                                                                                           | No edge o                                                                                                  | detection                                                                                      | (external trig                                                                                                        | ger invalid)                                                                                                             |                                                                         |                                                  |

|                       | 0        | 1                                                                                                           | Detection                                                                                                  |                                                                                                | •                                                                                                                     |                                                                                                                          |                                                                         |                                                  |

|                       | 1        | 0                                                                                                           | Detection                                                                                                  | •                                                                                              | •                                                                                                                     |                                                                                                                          |                                                                         |                                                  |

|                       |          | I                                                                                                           | Detection                                                                                                  | of both e                                                                                      | dges                                                                                                                  |                                                                                                                          |                                                                         |                                                  |

|                       | Cautions | <ol> <li>Rewring TAAr<br/>same<br/>rewring to 0 a</li> <li>The Taa<br/>the Taa<br/>even<br/>TAAr</li> </ol> | rite the<br>hETS0 bit<br>e value c<br>iting was<br>and then<br>TAAnEES<br>AAnCTL1<br>t count m<br>hCTL1.TA | TAAnE<br>s when<br>an be w<br>mistake<br>set the I<br>1 and TA<br>1.TAAnE<br>node (TA<br>AnMD0 | ES1, TAA<br>the TAAn(<br>ritten whe<br>enly perfor<br>bits again.<br>AnEES0 I<br>EE bit = 1<br>AnCTL1.T<br>bits = 001 | AnEES0,<br>CTL0.TAAr<br>en the TAA<br>med, clear<br>oits are val<br>or when the<br>GAnMD2 to<br>has been<br>oits are val | CE bit =<br>AnCE bit<br>the TAA<br>lid only the<br>extern<br>to<br>set. | = 0. (The<br>= 1.) If<br>AnCE bit<br>when<br>nal |

### (11) TAAn counter read buffer register (TAAnCNT)

The TAAnCNT register is a read buffer register that can read the count value of the 16-bit counter. If this register is read when the TAAnCTL0.TAAnCE bit = 1, the count value of the 16-bit timer can be read. This register is read-only, in 16-bit units.

The value of the TAAnCNT register is cleared to 0000H when the TAAnCE bit = 0. If the TAAnCNT register is read at this time, the value of the 16-bit counter (FFFFH) is not read, but 0000H is read.

Reset clears the TAAnCE bit to 0. Therefore, the value of the TAAnCNT register is cleared to 0000H.

### Caution Accessing the TAAnCNT register is prohibited in the following statuses. For details, see 3.4.9 (2) Accessing specific on-chip peripheral I/O registers.

- When the CPU operates with the subclock and the main clock oscillation is stopped

- When the CPU operates with the internal oscillation clock

| 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0         TAAnCNT | After res | set: 0 | 000H | F  | 8  | Addre | ess: |   | AOCN<br>A2CN |   |   |   |   |   |   |   |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|------|----|----|-------|------|---|--------------|---|---|---|---|---|---|---|---|

| (n = 0 to 2, 4)                                                                                                                                 | -         | 15     | 14   | 13 | 12 | 11    | 10   | 9 | 8            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

### (8) TMT0 option register 0 (TT0OPT0)

The TT0OPT0 register is an 8-bit register that sets the capture/compare operation and detects overflows. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

| After re | oot: 0011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                               |                                                                  |                              |                    |                     |                          |              |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------|--------------------|---------------------|--------------------------|--------------|--|--|--|--|

| After re | set: 00H<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W /                                                                                                                                                         | Address: FFF<br>5                                                | 4                            | 3                  | 2                   | 1                        | <0>          |  |  |  |  |

| TT0OPT0  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                             | TT0CCS1                                                          | TTOCCSO                      | 0                  | 0                   | 0                        | TT00VF       |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                               |                                                                  |                              |                    |                     |                          |              |  |  |  |  |

|          | TT0CCS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               | TT0CC                                                            | CR1 register                 | capture/c          | ompare se           | election                 |              |  |  |  |  |

|          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Selecte                                                                                                                                                       | d as compare                                                     | e register                   |                    |                     |                          |              |  |  |  |  |

|          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                             | d as capture                                                     | • •                          | -                  |                     |                          | bit = 0)     |  |  |  |  |

|          | The TT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The TT0CCS1 bit setting is valid only in the free-running timer mode.                                                                                         |                                                                  |                              |                    |                     |                          |              |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                               |                                                                  |                              | . ,                |                     | :                        |              |  |  |  |  |

|          | TTOCCS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |                                                                  | CR0 register                 | capture/c          | ompare se           | election                 |              |  |  |  |  |

|          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                               | d as compare                                                     |                              | ared by th         |                     |                          | hit = 0      |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1         Selected as capture register (cleared by the TT0CTL0.TT0CE bit = 0)           The TT0CCS0 bit setting is valid only in the free-running timer mode. |                                                                  |                              |                    |                     |                          |              |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | The Troccoo bit setting is valid only in the free-running timer mode.                                                                                         |                                                                  |                              |                    |                     |                          |              |  |  |  |  |

|          | тто                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OVF                                                                                                                                                           |                                                                  | TMT0 overflow detection flag |                    |                     |                          |              |  |  |  |  |

|          | Set (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               | Overflow                                                         | Overflow occurred            |                    |                     |                          |              |  |  |  |  |

|          | Reset (0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )                                                                                                                                                             | 0 written to TT0OVF bit or TT0CTL0.TT0CE bit = 0                 |                              |                    |                     |                          |              |  |  |  |  |

|          | <ul> <li>The TTOOVF bit is set to 1 when the 16-bit counter value overflows from FFFFH to 0000H in the free-running timer mode or the pulse width measurement mode.</li> <li>An overflow interrupt request signal (INTTTOOV) is generated when the TTOOVF bit is set to 1. The INTTTOOV signal is not generated in modes other than the free-running timer mode and the pulse width measurement mode.</li> <li>The TTOOVF bit is not cleared to 0 even when the TTOOVF bit or the TTOOPTO register are read when the TTOOVF bit = 1.</li> <li>Before clearing the TTOOVF bit to 0 after generation of the INTTTOOV signal, be sure to confirm (by reading) that the TTOOVF bit is set to 1.</li> <li>The TTOOVF bit can be both read and written, but the TTOOVF bit cannot be set to 1 by software. Writing 1 has no effect on the operation of TMTO.</li> </ul> |                                                                                                                                                               |                                                                  |                              |                    |                     |                          |              |  |  |  |  |

|          | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | san<br>mis<br>aga                                                                                                                                             | write the T<br>ne value ca<br>stakenly pe<br>sin.<br>sure to set | an be writt<br>rformed, c    | en whe<br>lear the | n the TT<br>TT0CE b | 0CE bit =<br>bit to 0 ar | = 1.) If rev |  |  |  |  |

### (1) Basic counter operation

This section explains the basic operation of the 16-bit counter. For details, refer to the description of the operation in each mode.

### (a) Count start operation

### • Encoder compare mode

A count operation is controlled by TENC00 and TENC01 phases. The 16-bit counter initial setting is performed by transferring the set value of the TT0TCW register to the 16-

bit counter and the count operation is started. (When the TT0CTL2.TT0ECC bit = 0, the TT0TCW register set value is transferred to the 16-bit counter at the timing when the TT0CTL0.TT0CE bit changes from 0 to 1.)

### Triangular-wave PWM mode

The 16-bit counter starts counting from the initial value FFFFH.

It counts up FFFFH, 0000H, 0001H, 0002H, 0003H, and so on.

Following the count-up operation, the counter counts down upon a match between the 16-bit count value and the CCR0 buffer register.

### • Mode other than above

The 16-bit counter starts counting from the initial value FFFFH. It counts up FFFFH, 0000H, 0001H, 0002H, 0003H, and so on.

### (b) Clear operation

The 16-bit counter is cleared to 0000H when its value matches the value of the compare register, when its value is captured, when the edge of the encoder clear signal is detected, and when the clear level condition of the TENC00, TENC01, and TECR0 pins is detected. The count operation from FFFFH to 0000H that takes place immediately after the counter has started counting or when the counter overflows is not a clear operation. Therefore, the INTTTOCC0 and INTTTOCC1 interrupt signals are not generated.

### (c) Overflow operation

The 16-bit counter overflows when it counts up from FFFFH to 0000H in the free-running mode, pulse width measurement mode, and encoder compare mode. If the counter overflows in the free-running mode and pulse width measurement mode, the TT0OPT0.TT0OVF bit is set to 1 and an interrupt request signal (INTTT0OV) is generated.

If the counter overflows in the encoder compare mode, the TT0OPT1.TT0EOF bit is set to 1 and an interrupt request signal (INTTT0OV) is generated.

Note that the INTTTOOV signal is not generated under the following conditions.

- Immediately after a count operation has been started

- If the counter value matches the compare value FFFFH and is cleared

- When FFFFH is captured and cleared to 0000H in the pulse width measurement mode

## Caution After the overflow interrupt request signal (INTTT0OV) has been generated, be sure to check that the overflow flag (TT0OVF, TT0EOF bits) is set to 1.

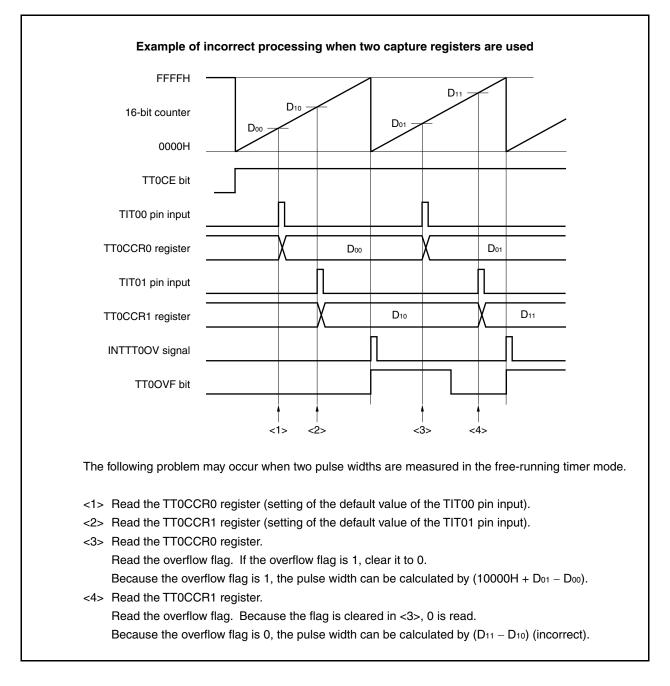

### (c) Processing of overflow when two capture registers are used

Care must be exercised in processing the overflow flag when two capture registers are used. First, an example of incorrect processing is shown below.

When two capture registers are used, and if the overflow flag is cleared to 0 by one capture register, the other capture register may not obtain the correct pulse width.

Use software when using two capture registers. An example of how to use software is shown below.

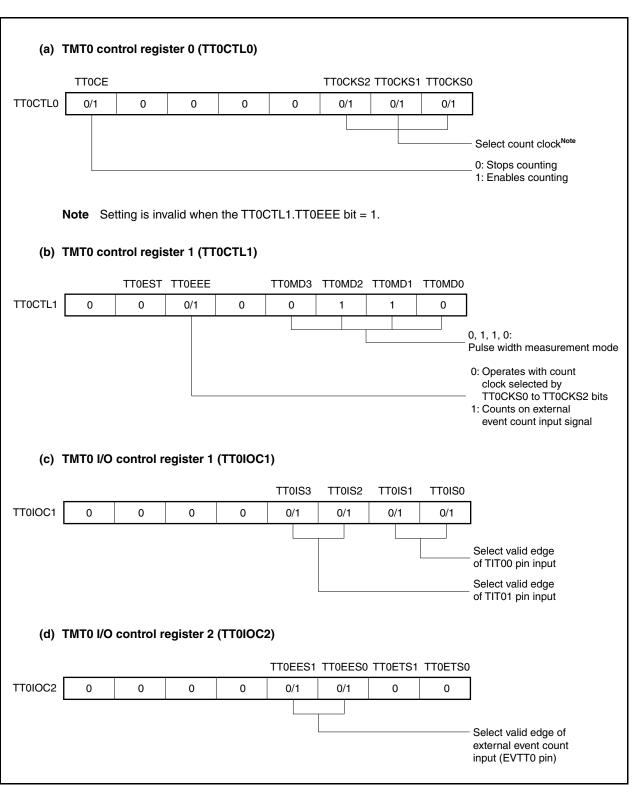

Figure 8-41. Register Setting in Pulse Width Measurement Mode (1/2)

| F6 | F5 to F0 | RC1SUBC Correction Value                                    | Frequency of Connected Clock<br>(Including Steady-State Deviation) |

|----|----------|-------------------------------------------------------------|--------------------------------------------------------------------|

| 0  | 000000   | No correction                                               | _                                                                  |

| 0  | 000001   | No correction                                               | _                                                                  |

| 0  | 000010   | Increments RC1SUBC count value by 2 once every 20 seconds   | 32.76810000 kHz                                                    |

| 0  | 000011   | Increments RC1SUBC count value by 4 once every 20 seconds   | 32.76820000 kHz                                                    |

| 0  | 000100   | Increments RC1SUBC count value by 6 once every 20 seconds   | 32.76830000 kHz                                                    |

|    |          |                                                             |                                                                    |

| 0  | 111011   | Increments RC1SUBC count value by 120 once every 20 seconds | 32.77400000 kHz                                                    |

| 0  | 111110   | Increments RC1SUBC count value by 122 once every 20 seconds | 32.77410000 kHz                                                    |

| 0  | 111111   | Increments RC1SUBC count value by 124 once every 20 seconds | 32.77420000 kHz (upper limit)                                      |

| 1  | 000000   | No correction                                               | _                                                                  |

| 1  | 000001   | No correction                                               | _                                                                  |

| 1  | 000010   | Decrements RC1SUBC count value by 124 once every 20 seconds | 32.76180000 kHz (lower limit)                                      |

| 1  | 000011   | Decrements RC1SUBC count value by 122 once every 20 seconds | 32.76190000 kHz                                                    |

| 1  | 000100   | Decrements RC1SUBC count value by 120 once every 20 seconds | 32.76200000 kHz                                                    |

|    |          |                                                             |                                                                    |

| 1  | 11011    | Decrements RC1SUBC count value by 6 once every 20 seconds   | 32.76770000 kHz                                                    |

| 1  | 11110    | Decrements RC1SUBC count value by 4 once every 20 seconds   | 32.76780000 kHz                                                    |

| 1  | 11111    | Decrements RC1SUBC count value by 2 once every 20 seconds   | 32.76790000 kHz                                                    |

Table 11-7. Range of Frequencies That Can Be Corrected When DEV Bit = 0

### Table 11-8. Range of Frequencies That Can Be Corrected When DEV Bit = 1

| F6 | F5 to F0 | RC1SUBC Correction Value                                    | Frequency of Connected Clock<br>(Including Steady-State Deviation) |

|----|----------|-------------------------------------------------------------|--------------------------------------------------------------------|

| 0  | 000000   | No correction                                               | _                                                                  |

| 0  | 000001   | No correction                                               | _                                                                  |

| 0  | 000010   | Increments RC1SUBC count value by 2 once every 60 seconds   | 32.76803333 kHz                                                    |

| 0  | 000011   | Increments RC1SUBC count value by 4 once every 60 seconds   | 32.76806667 kHz                                                    |

| 0  | 000100   | Increments RC1SUBC count value by 6 once every 60 seconds   | 32.76810000 kHz                                                    |

|    |          |                                                             |                                                                    |

| 0  | 111011   | Increments RC1SUBC count value by 120 once every 60 seconds | 32.77000000 kHz                                                    |

| 0  | 111110   | Increments RC1SUBC count value by 122 once every 60 seconds | 32.77003333 kHz                                                    |

| 0  | 111111   | Increments RC1SUBC count value by 124 once every 60 seconds | 32.77006667 kHz (upper limit)                                      |

| 1  | 000000   | No correction                                               | _                                                                  |

| 1  | 000001   | No correction                                               | _                                                                  |

| 1  | 000010   | Decrements RC1SUBC count value by 124 once every 60 seconds | 32.76593333 kHz (lower limit)                                      |

| 1  | 000011   | Decrements RC1SUBC count value by 122 once every 60 seconds | 32.76596667 kHz                                                    |

| 1  | 000100   | Decrements RC1SUBC count value by 120 once every 60 seconds | 32.76600000 kHz                                                    |

|    |          |                                                             |                                                                    |

| 1  | 11011    | Decrements RC1SUBC count value by 6 once every 60 seconds   | 32.76790000 kHz                                                    |

| 1  | 11110    | Decrements RC1SUBC count value by 4 once every 60 seconds   | 32.76793333 kHz                                                    |

| 1  | 11111    | Decrements RC1SUBC count value by 2 once every 60 seconds   | 32.76796667 kHz                                                    |

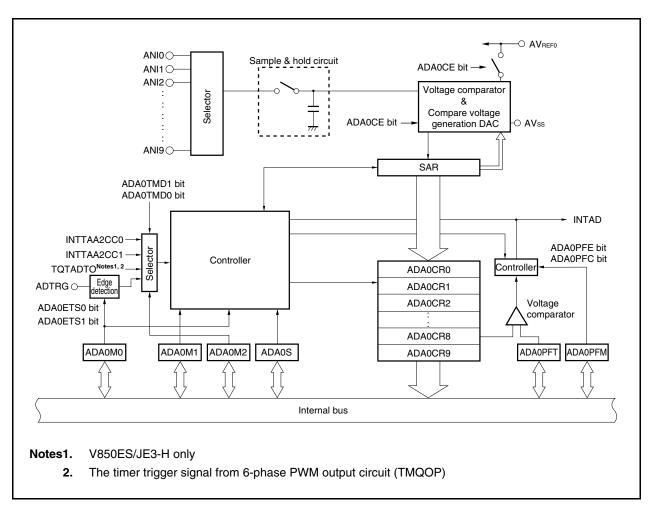

### 14.3 Configuration

The block diagram of the A/D converter is shown below.

The A/D converter includes the following hardware.

| Table 14-1. | Configuration of | A/D Converter |

|-------------|------------------|---------------|

|-------------|------------------|---------------|

| Item              | Configuration                                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog inputs     | 10 channels (ANI0 to ANI9 pins)                                                                                                                                                                                         |

| Registers         | Successive approximation register (SAR)<br>A/D conversion result registers 0 to 9 (ADA0CR0 to ADA0CR9)<br>A/D conversion result registers 0H to 9H (ADCR0H to ADCR9H): Only higher 8 bits can<br>be read                |

| Control registers | A/D converter mode registers 0 to 2 (ADA0M0 to ADA0M9)<br>A/D converter channel specification register 0 (ADA0S)<br>Power fail compare mode register (ADA0PFM)<br>Power fail compare threshold value register (ADA0PFT) |

### (12) Compare voltage generation DAC

This compare voltage generation DAC is connected between AV<sub>REF0</sub> and AV<sub>SS</sub> and generates a voltage for comparison with the analog input signal.

### (13) ANI0 to ANI9 pins

These are analog input pins for the 10 A/D converter channels and are used to input analog signals to be converted into digital signals. Pins other than the one selected as the analog input by the ADA0S register can be used as input port pins.

# Caution Make sure that the voltages input to the ANI0 to ANI9 pins do not exceed the rated values. In particular if a voltage of AV<sub>REF0</sub> or higher is input to a channel, the conversion value of that channel becomes undefined, and the conversion values of the other channels may also be affected.

### (14) AVREFO pin

This is the pin used to input the reference voltage of the A/D converter. Always make the potential at this pin the same as that at the V<sub>DD</sub> pin even when the A/D converter is not used.

The signals input to the ANI0 to ANI9 pins are converted to digital signals based on the voltage applied between the AV<sub>REF0</sub> and AV<sub>SS</sub> pins.

### (15) AVss pin

This is the ground potential pin of the A/D converter. Always make the potential at this pin the same as that at the Vss pin even when the A/D converter is not used.

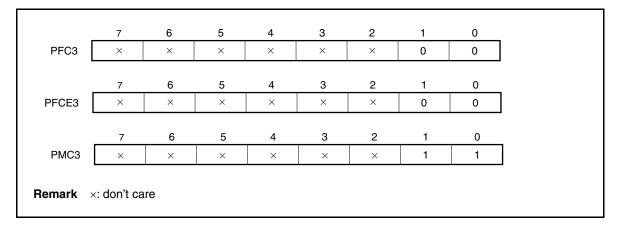

### 16.3.4 Mode switching between UARTC4, CSIF0, and I<sup>2</sup>C01

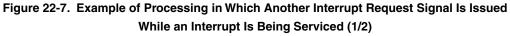

In the V850ES/JC3-H and V850ES/JE3-H, UARTC4, CSIF0, and I<sup>2</sup>C01 share the same pin and therefore cannot be used simultaneously. Set UARTC4 in advance, using the PMC4, PFC4, and PMCE4 registers, before use.

## Caution The transmit/receive operation of UARTC4, CSIF0, and I<sup>2</sup>C01 is not guaranteed if these functions are switched during transmission or reception. Be sure to disable the one that is not used.

| After re  | set: 00H                                                                             | R/W                     | Address: I              | FFFF446               | 4                       |            |        |        |

|-----------|--------------------------------------------------------------------------------------|-------------------------|-------------------------|-----------------------|-------------------------|------------|--------|--------|

|           | 7                                                                                    | 6                       | 5                       | 4                     | 3                       | 2          | 1      | 0      |

| PMC3      | PMC37                                                                                | PMC36                   | PMC35                   | PMC34                 | PMC33                   | PMC32      | PMC31  | PMC30  |

|           |                                                                                      |                         |                         |                       |                         |            |        |        |

| A ()      |                                                                                      | 544                     |                         |                       |                         |            |        |        |

| After res | set: 00H                                                                             | R/W                     | Address: F              | ·FFFF466F             | 1                       |            |        |        |

|           | 7                                                                                    | 6                       | 5                       | 4                     | 3                       | 2          | 1      | 0      |

| PFC3      | PFC37 <sup>Note1</sup>                                                               | PFC36 <sup>Note1</sup>  | PFC35 <sup>Note2</sup>  | PFC34                 | PFC33 <sup>Note2</sup>  | PFC32      | PFC31  | PFC30  |

|           |                                                                                      |                         |                         |                       |                         |            |        |        |

|           |                                                                                      |                         |                         |                       |                         |            |        |        |

| After res | set: 00H                                                                             | R/W                     | Address: F              | FFFF706H              | 4                       |            |        |        |

|           | 7                                                                                    | 6                       | 5                       | 4                     | 3                       | 2          | 1      | 0      |

| PFCE3     | PFCE37 <sup>Note1</sup>                                                              | PFCE36 <sup>Note1</sup> | PFCE35 <sup>Note2</sup> | PFCE34                | PFCE33 <sup>Note2</sup> | PFCE32     | PFCE31 | PFCE30 |

|           |                                                                                      |                         |                         |                       |                         |            |        |        |

|           | PMC37 <sup>Note1</sup> PFCE37 <sup>Note1</sup> PFC37 <sup>Note1</sup> Operation mode |                         |                         |                       |                         |            |        |        |

|           | 0                                                                                    | ×                       | ×                       | Port I/O m            | node                    |            |        |        |

|           | 1                                                                                    | 0                       | 0                       | RXDC3 (l              | JARTC3)                 |            |        |        |

|           | 1                                                                                    | 0                       | 1                       | SDA00 (I <sup>2</sup> |                         |            |        |        |

|           | 1                                                                                    | 1                       | 0                       | CRXD0 (0              | CAN0) <sup>Note3</sup>  |            |        |        |

|           | DMC2cNote1                                                                           | PFCE36 <sup>Note1</sup> | DECocNote1              |                       |                         | peration m | ada    |        |

|           | PMC36                                                                                | ×                       | ×                       | Port I/O m            |                         |            | JUE    |        |

|           | 1                                                                                    | 0                       | 0                       | TXDC3 (L              |                         |            |        |        |

|           | 1                                                                                    | 0                       | 1                       | SCL00 (I <sup>2</sup> |                         |            |        |        |

|           | 1                                                                                    | 1                       | 0                       | CTXD0 (0              | ,                       |            |        |        |

|           |                                                                                      |                         |                         | 0.7.20 (0             |                         |            |        |        |

|           | Notes1.                                                                              | V850ES                  | /JC3-H (4               | 8 pin) V8             | 50ES/JE3                | -H only    |        |        |

|           | 2.                                                                                   |                         | /JE3-H on               |                       | 2020/020                |            |        |        |

|           | 3.                                                                                   |                         | -3819, 70               | •                     | ly                      |            |        |        |

|           |                                                                                      |                         |                         |                       |                         |            |        |        |

|           | Remark                                                                               | × = don'                | t care                  |                       |                         |            |        |        |

|           |                                                                                      |                         |                         |                       |                         |            |        |        |

Figure 16-5. UARTC4, CSIF0 and I<sup>2</sup>C01 Mode Switch Settings

### 19.5.2 Register access type

| Address   | Register Name                                           | Symbol   | R/W | Bit Ma | anipulatior  | n Units      | After Reset |

|-----------|---------------------------------------------------------|----------|-----|--------|--------------|--------------|-------------|

|           |                                                         |          |     | 1 Bit  | 8 Bits       | 16 Bits      |             |

| 03FEC000H | CAN0 global control register                            | COGMCTRL | R/W |        |              | $\checkmark$ | 0000H       |

| 03FEC002H | CAN0 global clock selection register                    | COGMCS   |     |        | $\checkmark$ |              | 0FH         |

| 03FEC006H | CAN0 global automatic block transmission register       | COGMABT  |     |        |              | $\checkmark$ | 0000H       |

| 03FEC008H | CAN0 global automatic block transmission delay register | COGMABTD |     |        | $\checkmark$ |              | 00H         |

| 03FEC040H | CAN0 module mask 1 register                             | C0MASK1L |     |        |              | $\checkmark$ | Undefined   |

| 03FEC042H |                                                         | C0MASK1H |     |        |              | $\checkmark$ | Undefined   |

| 03FEC044H | CAN0 module mask 2 register                             | C0MASK2L |     |        |              | $\checkmark$ | Undefined   |

| 03FEC046H |                                                         | C0MASK2H |     |        |              | $\checkmark$ | Undefined   |

| 03FEC048H | CAN0 module mask 3 register                             | C0MASK3L |     |        |              | $\checkmark$ | Undefined   |

| 03FEC04AH |                                                         | C0MASK3H |     |        |              | $\checkmark$ | Undefined   |

| 03FEC04CH | CAN0 module mask 4 register                             | C0MASK4L |     |        |              | $\checkmark$ | Undefined   |

| 03FEC04EH |                                                         | C0MASK4H |     |        |              | $\checkmark$ | Undefined   |

| 03FEC050H | CAN0 module control register                            | COCTRL   |     |        |              | $\checkmark$ | 0000H       |

| 03FEC052H | CAN0 module last error code register                    | COLEC    |     |        | $\checkmark$ |              | 00H         |

| 03FEC053H | CAN0 module information register                        | COINFO   | R   |        | $\checkmark$ |              | 00H         |

| 03FEC054H | CAN0 module error counter register                      | C0ERC    |     |        |              | $\checkmark$ | 0000H       |

| 03FEC056H | CAN0 module interrupt enable register                   | COIE     | R/W |        |              | $\checkmark$ | 0000H       |

| 03FEC058H | CAN0 module interrupt status register                   | COINTS   |     |        |              | $\checkmark$ | 0000H       |

| 03FEC05AH | CAN0 module bit-rate prescaler register                 | COBRP    |     |        | $\checkmark$ |              | FFH         |

| 03FEC05CH | CAN0 module bit-rate register                           | COBTR    |     |        |              | $\checkmark$ | 370FH       |

| 03FEC05EH | CAN0 module last in-pointer register                    | COLIPT   | R   |        | $\checkmark$ |              | Undefined   |

| 03FEC060H | CAN0 module receive history list register               | CORGPT   | R/W |        |              | $\checkmark$ | xx02H       |

| 03FEC062H | CAN0 module last out-pointer register                   | COLOPT   | R   |        | $\checkmark$ |              | Undefined   |

| 03FEC064H | CAN0 module transmit history list register              | COTGPT   | R/W |        |              | $\checkmark$ | xx02H       |

| 03FEC066H | CAN0 module time stamp register                         | COTS     |     |        |              | $\checkmark$ | 0000H       |

### Table 19-16. Register Access Types (1/17)

(2/2)

| o) Write   |                           |

|------------|---------------------------|

| •          |                           |

| Clear TOVF | Setting of TOVF bit       |

| 0          | TOVF bit is not changed.  |

| 1          | TOVF bit is cleared to 0. |

### (18) CAN0 module time stamp register (C0TS)

The COTS register is used to control the time stamp function.

| (a) Read  | 15      | 14      | 10      | 10      | 4.4     | 10              | 0              | 0             |

|-----------|---------|---------|---------|---------|---------|-----------------|----------------|---------------|

|           | 15      | 14      | 13      | 12      | 11      | 10              | 9              | 8             |

| COTS      | 0       | 0       | 0       | 0       | 0       | 0               | 0              | 0             |

|           | 7       | 6       | 5       | 4       | 3       | 2               | 1              | 0             |

|           | 0       | 0       | 0       | 0       | 0       | TSLOCK          | TSSEL          | TSEN          |

| (b) Write | 15<br>0 | 14<br>0 | 13<br>0 | 12<br>0 | 11<br>0 | 10<br>Set       | 9<br>Set       | 8<br>Set      |

|           |         |         |         |         |         | TSLOCK          | TSSEL          | TSEN          |

|           | 7       | 6       | 5       | 4       | 3       | 2               | 1              | 0             |

|           | 0       | 0       | 0       | 0       | 0       | Clear<br>TSLOCK | Clear<br>TSSEL | Clear<br>TSEN |

| Address   | Function Register Name                                       | Symbol    | R/W | Manipulatable Bits |              |           | Default Value |

|-----------|--------------------------------------------------------------|-----------|-----|--------------------|--------------|-----------|---------------|

|           |                                                              |           |     | 1                  | 8            | 16        |               |

| 00200302H | UF0 configuration/interface/endpoint descriptor register 158 | UF0CIE158 | R/W |                    | V            |           | Undefined     |

| 00200304H | UF0 configuration/interface/endpoint descriptor register 159 | UF0CIE159 | R/W |                    | V            |           | Undefined     |

| 00200306H | UF0 configuration/interface/endpoint descriptor register 160 | UF0CIE160 | R/W |                    | V            |           | Undefined     |

| 00200308H | UF0 configuration/interface/endpoint descriptor register 161 | UF0CIE161 | R/W |                    | V            |           | Undefined     |

| 0020030AH | UF0 configuration/interface/endpoint descriptor register 162 | UF0CIE162 | R/W |                    | $\checkmark$ |           | Undefined     |

| 0020030CH | UF0 configuration/interface/endpoint descriptor register 163 | UF0CIE163 | R/W |                    | $\checkmark$ |           | Undefined     |

| 0020030EH | UF0 configuration/interface/endpoint descriptor register 164 | UF0CIE164 | R/W |                    | V            |           | Undefined     |

| 00200310H | UF0 configuration/interface/endpoint descriptor register 165 | UF0CIE165 | R/W | √                  |              |           | Undefined     |

| 00200312H | UF0 configuration/interface/endpoint descriptor register 166 | UF0CIE166 | R/W |                    | $\checkmark$ |           | Undefined     |

| 00200314H | UF0 configuration/interface/endpoint descriptor register 167 | UF0CIE167 | R/W |                    | $\checkmark$ |           | Undefined     |

| 00200316H | UF0 configuration/interface/endpoint descriptor register 168 | UF0CIE168 | R/W |                    | V            |           | Undefined     |

| 00200318H | UF0 configuration/interface/endpoint descriptor register 169 | UF0CIE169 | R/W |                    | $\checkmark$ |           | Undefined     |

| 0020031AH | UF0 configuration/interface/endpoint descriptor register 170 | UF0CIE170 | R/W |                    | V            |           | Undefined     |

| 0020031CH | UF0 configuration/interface/endpoint descriptor register 171 | UF0CIE171 | R/W |                    | $\checkmark$ |           | Undefined     |

| 0020031EH | UF0 configuration/interface/endpoint descriptor register 172 | UF0CIE172 | R/W | √                  |              | Undefined |               |

| 00200320H | UF0 configuration/interface/endpoint descriptor register 173 | UF0CIE173 | R/W |                    | V            |           | Undefined     |

| 00200322H | UF0 configuration/interface/endpoint descriptor register 174 | UF0CIE174 | R/W |                    | V            |           | Undefined     |

| 00200324H | UF0 configuration/interface/endpoint descriptor register 175 | UF0CIE175 | R/W |                    | V            |           | Undefined     |

| 00200326H | UF0 configuration/interface/endpoint descriptor register 176 | UF0CIE176 | R/W |                    | V            |           | Undefined     |

| 0200328H  | UF0 configuration/interface/endpoint descriptor register 177 | UF0CIE177 | R/W |                    | V            |           | Undefined     |

| 020032AH  | UF0 configuration/interface/endpoint descriptor register 178 | UF0CIE178 | R/W |                    | V            |           | Undefined     |

| 020032CH  | UF0 configuration/interface/endpoint descriptor register 179 | UF0CIE179 | R/W |                    | $\checkmark$ |           | Undefined     |

(3/4)

| Bit position | Bit name | Function                                                                                             |

|--------------|----------|------------------------------------------------------------------------------------------------------|

| 1            | BKI2NK   | This bit controls NAK to Endpoint3 (bulk 2 transfer (IN)).                                           |

|              |          | 1: Do not transmit NAK.                                                                              |

|              |          | 0: Transmit NAK (default value).                                                                     |

|              |          | This bit is cleared to 0 only when the FIFO connected to the SIE side of the UF0BI2                  |

|              |          | register (64-byte FIFO of bank configuration) cannot receive data. It is set to 1 when a             |

|              |          | toggle operation is performed (the data of the UF0BI2 register is retained until                     |

|              |          | transmission has been correctly completed). The bank is changed (toggle operation)                   |

|              |          | when the following conditions are satisfied.                                                         |

|              |          | <ul> <li>Data is correctly written to the FIFO connected to the CPU bus side (writing has</li> </ul> |

|              |          | been completed and the FIFO is full or the UF0DEND register is set).                                 |

|              |          | <ul> <li>The value of the FIFO counter connected to the SIE side is 0.</li> </ul>                    |

|              |          | This bit is automatically set to 1 and data transmission is started when the FIFO on the             |

|              |          | CPU side becomes full and a FIFO toggle operation is performed as a result of writing                |

|              |          | data to the FIFO. However, if the FIFO on the CPU side becomes full as a result of writin            |

|              |          | data to it by DMA while the BKI2T bit of the UF0DEND register is cleared to 0, the toggle            |

|              |          | operation is not performed because the condition of the toggle operation is not satisfied            |

|              |          | until the BKI2DED bit of the UF0DEND register is set to 1. To send a short packet that               |

|              |          | does not make the FIFO on the CPU side full, set the BKI2DED bit to 1 after completing               |

|              |          | writing data. When the BKI2DED bit is set to 1, a toggle operation is performed and at the           |

|              |          | same time, this bit is automatically set to 1. This bit is also cleared to 0 as soon as the          |

|              |          | UF0BI2 register has been cleared.                                                                    |

Cautions 1. If DMA is enabled while data is being written to the UF0Bl2 register in the PIO mode, a DMA request is immediately issued.

- 2. If 64-byte data is written in the DMA transfer mode, the DMA request signal becomes inactive. If the BKI2NK bit is then set to 1, data is transmitted in synchronization with an IN token. The DMA request signal becomes active again as long as the DMA request is not masked as soon as the FIFO is toggled. If the BKI2NK bit is not set, data is not transmitted even if an IN token has been received. In this case, set the BKI2DED bit of the UF0DEND register to 1.

- 3. If the TC signal is received in the DMA transfer mode, the DMA request signal becomes inactive. At the same time, the DMA request is masked. If the BKI2NK bit is not set to 1, data is not transmitted even if an IN token is received. When the BKI2DED bit of the UF0DEND register is set to 1 by FW, data is transmitted in synchronization with the IN token. To execute DMA transfer again, unmask the DMA request.

### (6) UF0 EP4 status register L (UF0E4SL)

This register stores the value that is to be returned in response to the GET\_STATUS Endpoint4 request.

This register can be read or written in 8-bit units. Note, however, that data can be written to this register only when the EP0NKA bit is set to 1.

If an error occurs in Endpoint4, the E4HALT bit is set to 1. A write access to this register is ignored while a USBside access to Endpoint4 is being received.

The hardware automatically transmits the contents of this register to the host when it has received the GET\_STATUS Endpoint4 request. If Endpoint4 has stalled, the UF0BO2 register is cleared and the BKO2NK bit is cleared to 0.

Because writing this register is always masked when transfer to Endpoint4, rather than control transfer, is executed, be sure to check this register to see if data has been correctly written to it.

## Caution To rewrite this register, set the EP0NKA bit to 1 before reading the register contents, and rewrite the register contents after confirming that the bit has been set, in order to prevent conflict between a read access and a write access.

|              | 7    | 6        | 5 | 4 | 3 | 2 | 1        | 0      | Address                 | After reset |  |

|--------------|------|----------|---|---|---|---|----------|--------|-------------------------|-------------|--|

| UF0E4SL      | 0    | 0        | 0 | 0 | 0 | 0 | 0        | E4HALT | 0020015CH               | 00H         |  |

|              | 1    |          |   |   |   |   |          |        |                         |             |  |

| Bit position | В    | lit name |   |   |   |   | Function |        |                         |             |  |

| 0            | E4H. |          |   |   |   |   |          |        | t4 request,<br>rface to |             |  |

### • Port registers when UARTC0 is used

When UARTC0 is used, port registers are set to make the TXDC0 and RXDC0 pins valid by the debug monitor program. Do not change the following register settings with the user program during debugging. (The same value can be overwritten.)

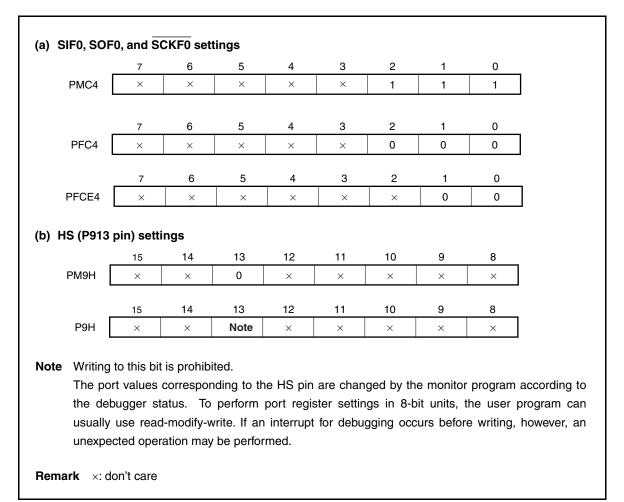

### • Port registers when CSIF0 is used

When CSIF0 is used, port registers are set to make the SIF0, SOF0, SCKF0, and HS (P913) pins valid by the debug monitor program. Do not change the following register settings with the user program during debugging. (The same value can be overwritten.)

### 32.5.2 Supply current

| Parameter                            | Symbol |                                     | Conditions                                                              | MIN. | TYP. | MAX. | Unit |

|--------------------------------------|--------|-------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| Supply current <sup>Notes 1, 2</sup> | Idd1   | Normal operation                    | fxx = 48 MHz (fx = 6 MHz)<br>Peripheral function operating              |      |      | 60   | mA   |

|                                      |        |                                     | fxx = 48 MHz (fx = 6 MHz)<br>USBF operating                             |      | 42   |      | mA   |

|                                      | Idd2   | HALT mode                           | fxx = 48 MHz (fx = 6 MHz)<br>Peripheral function operating              |      | 33   | 42   | mA   |

|                                      | Idd3   | IDLE1<br>mode                       | fxx = 48 MHz (fx = 6 MHz),<br>PLL on                                    |      | 4    | 7    | mA   |

|                                      | Idd4   | IDLE2<br>mode                       | fxx = 6 MHz (fx = 6 MHz),<br>PLL off                                    |      | 0.5  | 0.8  | mA   |

|                                      | Idd5   | Subclock<br>operation<br>mode       | fxr = 32.768 kHz,<br>main clock stopped,<br>internal oscillator stopped |      | 120  | 600  | μA   |

|                                      | Idde   | Sub-IDLE<br>mode                    | fxr = 32.768 kHz,<br>main clock stopped,<br>internal oscillator stopped |      | 13   | 95   | μA   |

|                                      | Idd7   | STOP<br>mode                        | Subclock stopped,<br>internal oscillator stopped                        |      | 10   | 90   | μA   |

|                                      |        |                                     | Subclock operating,<br>internal oscillator stopped                      |      | 13   | 95   | μA   |