# E. Renesas Electronics America Inc - UPD70F3822GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                             |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 48MHz                                                                                |

| Connectivity               | CANbus, CSI, EBI/EMI, I <sup>2</sup> C, UART/USART, USB                              |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 45                                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 24K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 10x10b; D/A 1x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

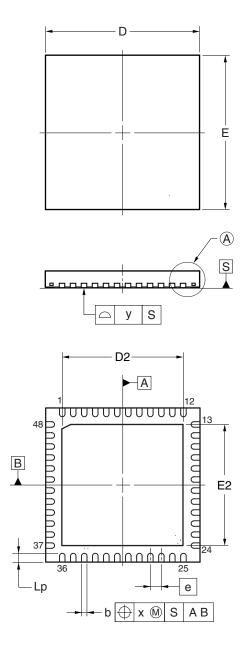

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3822gb-gah-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### (9) Real-time counter (for watch)

The real-time counter counts the reference time (one second) for watch counting based on the subclock (32.768 kHz) or main clock. This can simultaneously be used as the interval timer based on the main clock. Hardware counters dedicated to year, month, day of week, day, hour, minute, and second are provided, and can count up to 99 years.

#### (10) Watchdog timer 2

A watchdog timer is provided on chip to detect inadvertent program loops, system abnormalities, etc. The internal oscillation clock, the main clock, or the subclock can be selected as the source clock. Watchdog timer 2 generates a non-maskable interrupt request signal (INTWDT2) or a system reset signal (WDT2RES) after an overflow occurs.

#### (11) Serial interface

The V850ES/JC3-H and V850ES/JE3-H include three kinds of serial interfaces (asynchronous serial interface C (UARTC), 3-wire variable-length serial interface F (CSIF), and an  $l^2$ C bus interface ( $l^2$ C)), a CAN controller (CAN)<sup>Note1</sup>, and a USB function controller (USBF).

UARTC transfers data via the TXDC0, TXDC2 to TXDC4 pins and RXDC0, RXDC2 to RXDC4 pins.

CSIF transfers data via the SOF0, SOF2 to SOF4 pins, SIF0, SIF2 to SIF4 pins, and SCKF0, SCKF2 to SCKF4 pins.

In the case of I<sup>2</sup>C, data is transferred via the (SDA00)<sup>Note2</sup>, SDA01 and (SCL00)<sup>Note2</sup>, SCL01 pins. CAN<sup>Note1</sup> transfers data via the CRXD<sup>Note1</sup> and CTXD0<sup>Note1</sup> pins.

USBF transfers data via the UDMF and UDPF pins.

#### **Notes1.** *μ* PD70F3819, 70F3825 only

**2.** V850ES/JC3-H (48 pin), V850ES/JE3-H only

#### (12) A/D converter

This 10-bit A/D converter includes 10/6/5 analog input pins. Conversion is performed using the successive approximation method.

#### (13) D/A converter (V850ES/JC3-H (48 pin), JE3-H only)

A one-channel, 8-bit-resolution D/A converter that uses the R-2R ladder method is provided on chip.

#### (14) DMA controller

A 4-channel DMA controller is provided on chip. This controller transfers data between the internal RAM, on-chip peripheral I/O devices, and external memory in response to interrupt requests sent by on-chip peripheral I/O devices.

#### (15) Key interrupt function

A key interrupt request signal (INTKR) can be generated by inputting a falling edge to the key input pins (4 channels).

#### (16) Real-time output function

The real-time output function transfers preset 4-bit data to output latches upon the occurrence of a timer compare register match signal.

#### (b) Batch write

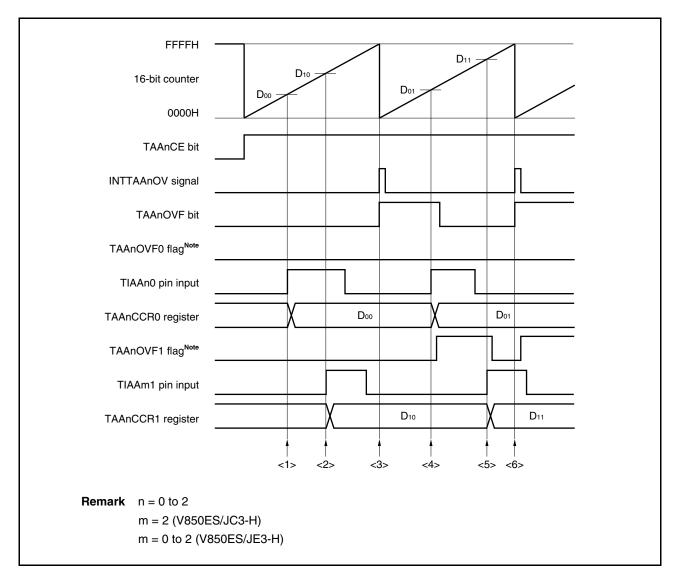

In this mode, data is transferred all at once from the TAAnCCR0 and TAAnCCR1 registers to the CCR0 and CCR1 buffer registers during timer operation. This data is transferred upon a match between the value of the CCR0 buffer register and the value of the 16-bit counter. Transfer is enabled by writing to the TAAnCCR1 register. Whether to enable or disable the next transfer timing is controlled by writing or not writing to the TAAnCCR1 register.

In order for the set value when the TAAnCCR0 and TAAnCCR1 registers are rewritten to become the 16-bit counter comparison value (in other words, in order for this value to be transferred to the CCR0 and CCR1 buffer registers), it is necessary to rewrite the TAAnCCR0 register and then write to the TAAnCCR1 register before the 16-bit counter value and the CCR0 buffer register value match. Therefore, the values of the TAAnCCR0 and TAAnCCR1 registers are transferred to the CCR0 and CCR1 buffer registers upon a match between the count value of the 16-bit counter and the value of the CCR0 buffer register. Thus even when wishing only to rewrite the value of the TAAnCCR0 register, also write the same value (same as preset value of the TAAnCCR1 register) to the TAAnCCR1 register.

#### (b) When using capture/compare register as capture register

#### Figure 6-38. Software Processing Flow in Free-Running Timer Mode (Capture Function) (1/2)

Figure 6-46. Example of Timing in Free-Running Mode (Capture/Compare Used Together)

| -        |           | T404050    | TARAOLO    |            |          | TADAOCA   |                                  | TADAOE              |                                                                                                       |

|----------|-----------|------------|------------|------------|----------|-----------|----------------------------------|---------------------|-------------------------------------------------------------------------------------------------------|

|          | 0/1       | 0/1        | 0/1        | 0/1        | 0/1      | 0/1       | 1 TAB1OL0<br>0/1 <sup>Note</sup> | 0/1 <sup>Note</sup> | ]                                                                                                     |

| L        |           |            |            |            |          |           |                                  |                     | O: Disable TOAB10 pin output T: Enable TOAB10 pin output                                              |

|          |           |            |            |            |          |           |                                  |                     | Setting of output level while<br>operation of TOAB10 pin is disabled<br>0: Low level<br>1: High level |

|          |           |            |            |            |          |           |                                  |                     | 0: Disable TOAB11 pin output<br>1: Enable TOAB11 pin output                                           |

|          |           |            |            |            |          |           |                                  |                     | Specification of active level of<br>TOAB11 pin output<br>0: Active-high<br>1: Active-low              |

|          |           |            |            |            |          |           |                                  |                     | 0: Disable TOAB12 pin output<br>1: Enable TOAB12 pin output                                           |

|          |           |            |            |            |          |           |                                  |                     | Specification of active level<br>of TOAB12 pin output<br>0: Active-high<br>1: Active-low              |

|          |           |            |            |            |          |           |                                  |                     | 0: Disable TOAB13 pin output<br>1: Enable TOAB13 pin output                                           |

|          |           |            |            |            |          |           |                                  |                     | Specification of active level<br>of TOAB13 pin output<br>0: Active-high<br>1: Active-low              |

| When     | TAB1OLI   | k bit = 0  |            |            |          | When      | TAB1OLk b                        | it = 1              |                                                                                                       |

|          | 16-bit cc | ounter     | $\wedge$   |            | 1        |           | 16-bit cour                      | nter                |                                                                                                       |

| TOA      | B1k pin o | output     |            |            |          | TOA       | B1k pin out                      | out 🗌               |                                                                                                       |

| (d) TA   | B1 I/O c  | ontrol reg | gister 2 ( | TAB1IOC    | 2)       |           |                                  |                     |                                                                                                       |

|          |           |            |            |            | TAB1EES1 | TAB1EES   | TAB1ETS1                         | TAB1ETS             | )                                                                                                     |

| TAB1IOC2 | 0         | 0          | 0          | 0          | 0/1      | 0/1       | 0                                | 0                   | ]                                                                                                     |

|          |           |            |            |            |          |           |                                  |                     |                                                                                                       |

|          |           |            |            |            |          |           |                                  |                     | Select valid edge<br>of external event<br>count input.                                                |

| (e) TA   | B1 cour   | nter read  | buffer re  | qister (TA | AB1CNT)  |           |                                  |                     |                                                                                                       |

|          |           |            |            |            |          | nding the | TAB1CNT                          | register            |                                                                                                       |

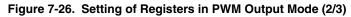

In order to transfer data from the TT0CCRn register to the CCRn buffer register, the TT0CCR1 register must be written.

To change both the cycle and active level width of the PWM waveform at this time, first set the cycle to the TT0CCR0 register and then set the active level width to the TT0CCR1 register.

To change only the cycle of the PWM waveform, first set the cycle to the TT0CCR0 register, and then write the same value (same as preset value of the TT0CCR1 register) to the TT0CCR1 register.

To change only the active level width (duty factor) of the PWM waveform, only the TT0CCR1 register has to be set.

After data is written to the TT0CCR1 register, the value written to the TT0CCRn register is transferred to the CCRn buffer register in synchronization with clearing of the 16-bit counter, and is used as the value compared with the 16-bit counter.

To write the TT0CCR0 or TT0CCR1 register again after writing the TT0CCR1 register once, do so after the INTTT0CC0 signal is generated. Otherwise, the value of the CCRn buffer register may become undefined because the timing of transferring data from the TT0CCRn register to the CCRn buffer register conflicts with writing the TT0CCRn register.

**Remark** n = 0, 1

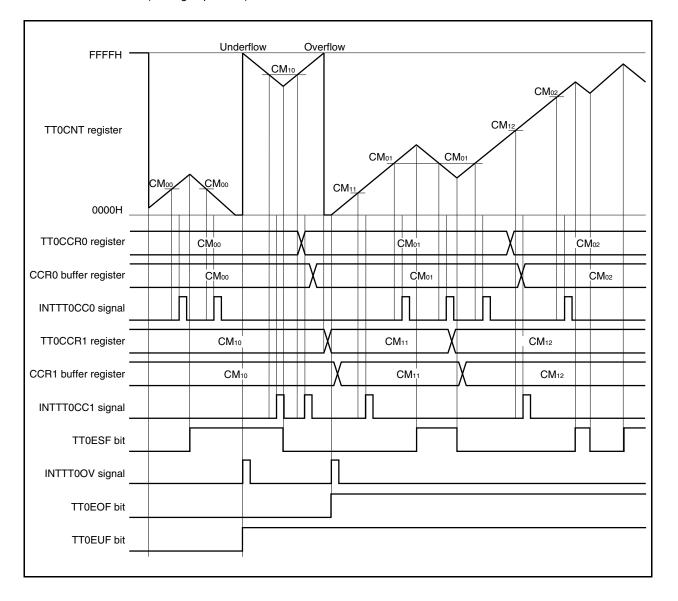

#### (b) Basic timing 2

#### [Register setting condition]

- TT0CTL2.TT0ECM1 and TT0CTL2.TT0ECM0 bits = 00 The 16-bit counter is not cleared even when its count value matches the value of the CCRn buffer register (a = 0, 1).

- TT0CTL2.TT0LDE bit = 0

The set value of the TT0CCR0 register is not transferred to the 16-bit counter after the counter underflows.

TT0IOC3.TT0SCE bit = 0, and TT0IOC3.TT0ECS1 and TT0IOC3.TT0ECS0 bits = 00 Specification of clearing the 16-bit counter when the edge of the encoder clear input signal (TECR0 pin) is detected (no edge specified)

#### 10.4.3 Interrupt culling function

- The interrupts to be culled are INTTAB1CC0 (crest interrupt) and INTTAB1OV (valley interrupt).

- The TAB1OPT1.TAB1ICE bit is used to enable output of the INTTAB1CC0 interrupt and the number of times the interrupt is to be culled.

- The TAB1OPT1.TAB1IOE bit is used to enable output of the INTTAB1OV interrupt and the number of times the interrupt is to be culled.

- The TAB1OPT1.TAB1ID4 to TAB1OPT1.TAB1ID0 bits are used to specify the number of counts by which a specified interrupt is to be culled. The interrupt is masked for the duration of the specified number of counts and is generated at the next interrupt timing.

- The TAB1OPT2.TAB1RDE bit is used to specify whether transfer is to be culled or not. If it is specified that transfer is to be culled, transfer is executed at the same timing as the interrupt output after culling. If it is specified that transfer is not to be culled, transfer is executed at the transfer timing after the TAB1CCR1 register has been written.

- The TAB1OPT0.TAB1CMS bit is used to specify whether the registers with a transfer function are batch rewritten or anytime rewritten.

The values of the registers are updated in synchronization with transfer when the TAB1CMS bit is 0. When the TAB1CMS bit is 1, the values of the registers are immediately updated when a new value is written to the registers.

Transfer is performed from the TAB1CCRm register to the CCRm buffer register in synchronization with the interrupt culling timing.

## Cautions 1. When using the interrupt culling function in the batch rewrite mode (transfer mode), execute the function in the intermittent batch rewrite mode (transfer culling mode).

2. The interrupt is generated at the timing after culling.

Remark m = 1 to 3

CSIFn includes the following hardware.

| Table 17-1. | Configuration | of CSIFn |

|-------------|---------------|----------|

|-------------|---------------|----------|

| Item      | Configuration                                                                                                                                                                                                                   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers | CSIFn receive data register (CFnRX)<br>CSIFn transmit data register (CFnTX)<br>CSIFn control register 0 (CFnCTL0)<br>CSIFn control register 1 (CFnCTL1)<br>CSIFn control register 2 (CFnCTL2)<br>CSIFn status register (CFnSTR) |

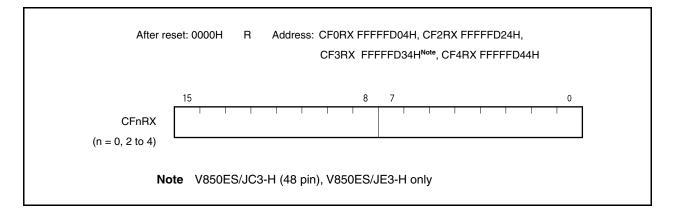

#### (1) CSIFn receive data register (CFnRX)

The CFnRX register is a 16-bit buffer register that holds receive data.

This register is read-only, in 16-bit units.

The receive operation is started by reading the CFnRX register in the reception enabled status.

If the transfer data length is 8 bits, the lower 8 bits of this register are read-only in 8-bit units as the CFnRXL register.

Reset sets this register to 0000H.

In addition to reset input, the CFnRX register can be initialized by clearing (to 0) the CFnPWR bit of the CFnCTL0 register.

#### (3) Start ~ Code ~ Data ~ Data ~ Stop (extension code transmission)

|                            |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |                          |           |          | SPTn        | bit = 1            |         |

|----------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|-----------|----------|-------------|--------------------|---------|

| ST                         | AD6 to AI                                                                                          | 0 R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ĀCK                                                                | D7 to D0                 | ĀCK       | D7 to D0 | ACK         | ↓<br>SP            | ٦       |

|                            | 1                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    | ▲1 ·                     | ▲2        |          | <b>▲</b> 3  | ▲4                 | Δ5      |

| ▲1                         | : IICSn regi                                                                                       | ter = 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X110B                                                              |                          |           |          |             |                    |         |

| ▲2                         | : IICSn regi                                                                                       | ter = 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X000B                                                              |                          |           |          |             |                    |         |

| <b>▲</b> 3                 | : IICSn regi                                                                                       | ter = 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X000B (                                                            | WTIMn bit = 1            | )         |          |             |                    |         |

| ▲4                         | : IICSn regi                                                                                       | ter = 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XX00B                                                              |                          |           |          |             |                    |         |

| Δ 5                        | : IICSn regis                                                                                      | er = 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0001B                                                              |                          |           |          |             |                    |         |

| W/b                        | 2                                                                                                  | : don't                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    | rated<br>nly when SPI    | IEn bit = | 1        |             |                    |         |

| • Wh                       |                                                                                                    | : don't                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |                          | IEn bit = | 1        | SPTn        | bit = 1            |         |

| • Wh                       | 2                                                                                                  | : don't<br>bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |                          | En bit =  | D7 to D0 | SPTn<br>ACK | bit = 1<br>↓<br>SP | 7       |

|                            | en WTIMn                                                                                           | : don't<br>bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | care<br>ĀCK                                                        | nly when SPI             | ĀĊĸ       |          | ĀCK         | ↓<br>SP            |         |

| ST                         | en WTIMn                                                                                           | : don't<br>bit = 1<br>0 R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | care                                                               | nly when SPI<br>D7 to D0 | ĀĊĸ       | D7 to D0 | ĀCK         | ↓<br>SP            | ∆4      |

| ST<br>▲1                   | en WTIMn                                                                                           | : don't<br><b>bit = 1</b><br>0 R/W<br>ter = 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ACK<br>ACK<br>X110B                                                | nly when SPI<br>D7 to D0 | ĀĊĸ       | D7 to D0 | ĀCK         | ↓<br>SP            |         |

| ST<br>▲1<br>▲2             | en WTIMn<br>AD6 to AI<br>: IICSn regi                                                              | : don't<br><b>bit = 1</b><br>0 R/W<br>ter = 1010<br>ter = 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Care<br>ACK<br>0X110B<br>0X100B                                    | nly when SPI<br>D7 to D0 | ĀĊĸ       | D7 to D0 | ĀCK         | ↓<br>SP            | Δ4      |

| ST<br>▲1<br>▲2<br>▲3       | en WTIMn<br>AD6 to AI<br>: IICSn regi<br>: IICSn regi                                              | : don't<br><b>bit = 1</b><br>0 R/W<br>ter = 1010<br>ter = 1010<br>ter = 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ACK<br>ACK<br>0X110B<br>0X100B<br>0XX00B                           | nly when SPI<br>D7 to D0 | ĀĊĸ       | D7 to D0 | ĀCK         | ↓<br>SP            | ∆4      |

| ST<br>▲1<br>▲2<br>▲3<br>△4 | en WTIMn<br>AD6 to AI<br>: IICSn regi<br>: IICSn regi<br>: IICSn regi<br>: IICSn regi              | $\frac{1}{2}  \text{don't}$ $\frac{1}{1}  \text{bit} = 1$ $\frac{1}{1}  \text{don't}$ $\frac{1}  \text{don't}$ $\frac{1}{1} $ | ACK<br>0X110B<br>0X100B<br>0XX00B<br>00001B                        | D7 to D0<br>▲1           | ĀĊĸ       | D7 to D0 | ĀCK         | ↓<br>SP            | ]<br>∆4 |

| ST<br>▲1<br>▲2<br>▲3<br>△4 | en WTIMn<br>AD6 to AI<br>: IICSn regis<br>: IICSn regis<br>: IICSn regis<br>: IICSn regis<br>emark | <ul> <li>don't</li> <li>bit = 1</li> <li>0 R/W</li> <li>ter = 1010</li> <li>ter = 1010</li> <li>ter = 1010</li> <li>ter = 0000</li> <li>: Alway</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ACK<br>ACK<br>ACK<br>ACK<br>ACK<br>ACK<br>ACK<br>ACK<br>ACK<br>ACK | D7 to D0<br>▲1           | ACK       | D7 to D0 | ĀCK         | ↓<br>SP            |         |

#### (4) Start ~ Code ~ Data ~ Start ~ Address ~ Data ~ Stop

|    | <1> When W          | TIMn b    | oit = 0 (     | after restart | , addre | ess mis  | match (= no | t exten | sion co | ode))    |     |    |    |

|----|---------------------|-----------|---------------|---------------|---------|----------|-------------|---------|---------|----------|-----|----|----|

| ST | AD6 to AD0          | R/W       | ĀCK           | D7 to D0      | ACK     | ST       | AD6 to AD0  | R/W     | ACK     | D7 to D0 | ĀCK | SP | 1  |

|    |                     |           | 1             |               | 2       |          |             | •       |         | 3        |     |    | Δ4 |

|    | ▲1: IICS            | n registe | er = 001      | 0X010B        |         |          |             |         |         |          |     |    |    |

|    | ▲2: IICS            | n registe | er = 001      | 0X000B        |         |          |             |         |         |          |     |    |    |

|    | ▲3: IICS            | n registe | er = 000      | 00X10B        |         |          |             |         |         |          |     |    |    |

|    | ∆ 4: IICS           | n registe | er = 0000     | 00001B        |         |          |             |         |         |          |     |    |    |

|    | Remar<br><2> When W | Δ:<br>X:  | Gene<br>don't |               | hen SF  |          |             | t exten | sion co | ode))    |     |    |    |

| ST | AD6 to AD0          | R/W       | ĀCK           | D7 to D0      | ACK     | ST       | AD6 to AD0  | R/W     | ĀĊK     | D7 to D0 | ĀCK | SP |    |

|    |                     |           | 1             | 2             |         | ▲3       | •           |         |         | 4        |     |    | Δ5 |

|    | ▲1: IICS            | n registe | er = 001      | 0X010B        |         |          |             |         |         |          |     |    |    |

|    | ▲2: IICS            | n registe | er = 001      | 0X110B        |         |          |             |         |         |          |     |    |    |

|    | ▲3: IICS            | n registe | er = 001      | 0XX00B        |         |          |             |         |         |          |     |    |    |

|    | ▲4: IICS            | n registe | er = 000      | 00X10B        |         |          |             |         |         |          |     |    |    |

|    | $\Delta$ 5: IICS    | n registe | er = 0000     | 00001B        |         |          |             |         |         |          |     |    |    |

|    | Remar               | k ▲:      |               | ys generated  |         |          |             |         |         |          |     |    |    |

|    |                     | Δ:        |               | erated only w | hen SF  | PIEn bit | := 1        |         |         |          |     |    |    |

|    |                     | X:        | don't         | care          |         |          |             |         |         |          |     |    |    |

#### 19.9.2 Reading reception data

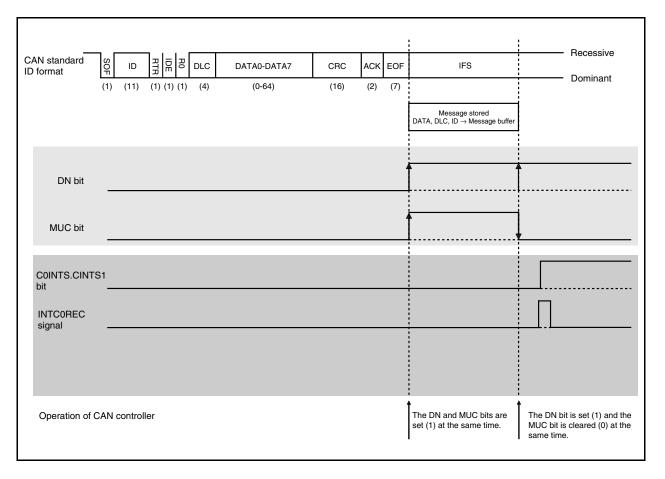

If it is necessary to consistently read data from the CAN message buffer by software, follow the recommended procedures shown in Figures 19-49 and 19-50.

While receiving a message, the CAN module sets the COMCTRLm.DN bit two times, at the beginning of the processing to store data in the message buffer and at the end of this storing processing. During this storing processing, the COMCTRLm.MUC bit of the message buffer is set (1) (refer to **Figure 19-29**).

Before the data is completely stored, the receive history list is written. During this data storing period (MUC bit = 1), the CPU is prohibited from rewriting the COMCTRLm.RDY bit of the message buffer in which the data is to be stored. Completion of this data storing processing may be delayed by a CPU's access to any message buffer.

Remark m = 0 to 31

#### Figure 19-29. DN and MUC Bit Setting Period (in Standard ID Format)

|                   | Va              | lid Bit Rate Setti | ing               |                   | C0BTR Registe       | er Setting Value    | Sampling Point |

|-------------------|-----------------|--------------------|-------------------|-------------------|---------------------|---------------------|----------------|

| DBT Length        | SYNC<br>SEGMENT | PROP<br>SEGMENT    | PHASE<br>SEGMENT1 | PHASE<br>SEGMENT2 | TSEG13 to<br>TSEG10 | TSEG22 to<br>TSEG20 | (Unit: %)      |

| 11                | 1               | 2                  | 4                 | 4                 | 0101                | 011                 | 63.6           |

| 11                | 1               | 4                  | 3                 | 3                 | 0110                | 010                 | 72.7           |

| 11                | 1               | 6                  | 2                 | 2                 | 0111                | 001                 | 81.8           |

| 11                | 1               | 8                  | 1                 | 1                 | 1000                | 000                 | 90.9           |

| 10                | 1               | 1                  | 4                 | 4                 | 0100                | 011                 | 60.0           |

| 10                | 1               | 3                  | 3                 | 3                 | 0101                | 010                 | 70.0           |

| 10                | 1               | 5                  | 2                 | 2                 | 0110                | 001                 | 80.0           |

| 10                | 1               | 7                  | 1                 | 1                 | 0111                | 000                 | 90.0           |

| 9                 | 1               | 2                  | 3                 | 3                 | 0100                | 010                 | 66.7           |

| 9                 | 1               | 4                  | 2                 | 2                 | 0101                | 001                 | 77.8           |

| 9                 | 1               | 6                  | 1                 | 1                 | 0110                | 000                 | 88.9           |

| 8                 | 1               | 1                  | 3                 | 3                 | 0011                | 010                 | 62.5           |