# E. Kenesas Electronics America Inc - UPD70F3824GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 48MHz                                                                                |

| Connectivity               | CANbus, CSI, EBI/EMI, I <sup>2</sup> C, UART/USART, USB                              |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 45                                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 24K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 10x10b; D/A 1x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3824gb-gah-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.3 Pin I/O Circuit Types, I/O Buffer Power Supplies and Connection of Unused Pins

#### Table 2-3. Pin I/O Circuit Types, I/O Buffer Power Supplies and Connection of Unused Pins (1/3)

| Pin           | Alternate Function                | I/O Circuit |                   | Recommended Connection                                                    |              | Pin No       |              |

|---------------|-----------------------------------|-------------|-------------------|---------------------------------------------------------------------------|--------------|--------------|--------------|

| Name          |                                   | Туре        |                   |                                                                           | JC3-H        |              | JE3-H        |

|               |                                   |             |                   |                                                                           | 40 pin       | 48 pin       |              |

| P02           | NMI                               | 10-D        | Input:            | Independently connect to EVDD or                                          | -            | -            | $\checkmark$ |

| P03           | INTP02/ADTRG/UCLK                 | 10-D        | Output:           | Vss via a resistor.<br>Leave open.                                        |              |              | $\checkmark$ |

| P10           | ANO0                              | 12-D        | Input:<br>Output: | Independently connect to AVREF1<br>or AVss via a resistor.<br>Leave open. | -            | V            | V            |

| P30           | TXDC0/SOF4/INTP07                 | 10-D        | Input:            | Independently connect to EVDD or                                          | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P31           | RXDC0/SIF4/INTP08                 |             |                   | Vss via a resistor.                                                       | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P32           | ASCKC0/SCKF4/TIAA00/TOAA00        |             | Output:           | Leave open.                                                               | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P33           | TIAA01/TOAA01/RTCDIV/RTCCL        |             |                   |                                                                           | _            | _            | $\checkmark$ |

| P34           | TIAA10/TOAA10/TOAA10FF/INTP09     |             |                   |                                                                           | _            | _            | $\checkmark$ |

|               | TIAA10/TOAA10/ INTP09             |             |                   |                                                                           |              | $\checkmark$ | _            |

| P35           | TIAA11/TOAA11/RTC1HZ              |             |                   |                                                                           | _            | _            | $\checkmark$ |

| P36           | TXDC3/SCL00/CTXD0 <sup>Note</sup> |             |                   |                                                                           |              | $\checkmark$ | $\checkmark$ |

| P37           | RXDC3/SDA00/CRXD0 <sup>Note</sup> |             |                   |                                                                           |              | $\checkmark$ | $\checkmark$ |

| P40           | SIF0/TXDC4/SDA01                  | 10-D        | Input:            | Independently connect to EVDD or                                          | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P41           | SOF0/RXDC4/SCL01                  |             | _                 | Vss via a resistor.                                                       | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P42           | SCKF0/INTP10                      |             | Output:           | Leave open.                                                               |              | $\checkmark$ | $\checkmark$ |

| P52           | KR2/RTP02/DDI                     | 10-D        | Input:            | Independently connect to EVDD or                                          |              | $\checkmark$ | $\checkmark$ |

| P53           | SIF2/KR3/RTP03/DDO                |             |                   | Vss via a resistor.                                                       | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P54           | SOF2/KR4/RTP04/DCK                |             | Output:           | Leave open.                                                               | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P55           | SCKF2/KR5/RTP05/DMS               |             |                   |                                                                           |              | $\checkmark$ | $\checkmark$ |

| P56           | INTP05/DRST                       |             |                   |                                                                           | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P60           | TOAB1T1/TIAB11/TOAB11             | 5           | Input:            | Independently connect to EVDD or                                          | -            | -            | $\checkmark$ |

| P61           | TOAB1B1/TIAB10/TOAB10             |             | Outout            | Vss via a resistor.                                                       | _            | -            | $\checkmark$ |

| P62           | TOAB1T2/TIAB12/TOAB12             |             | Output:           | Leave open.                                                               | -            | -            | $\checkmark$ |

| P63           | TOAB1B2/TRGAB1                    |             |                   |                                                                           | -            | -            | $\checkmark$ |

| P64           | TOAB1T3/TIAB13/TOAB13             |             |                   |                                                                           | _            | -            | $\checkmark$ |

| P70 to<br>P74 | ANI0 to ANI4                      | 11-G        | Input:            | Independently connect to AVREF1<br>or AVss via a resistor.                | V            | V            | $\checkmark$ |

| P75           | ANI5                              | ]           | Output:           | Leave open.                                                               | _            | $\checkmark$ | $\checkmark$ |

| P76 to<br>P79 | ANI6 to ANI9                      |             |                   |                                                                           | _            | -            | $\checkmark$ |

**Note** *μ* PD70F3819, 70F3825 only

Remark JC3-H: V850ES/JC3-H, JE3-H: V850ES/JE3-H

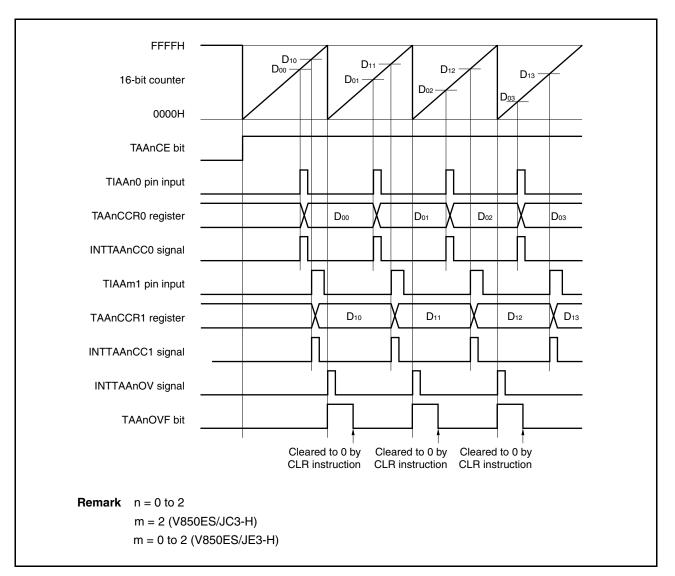

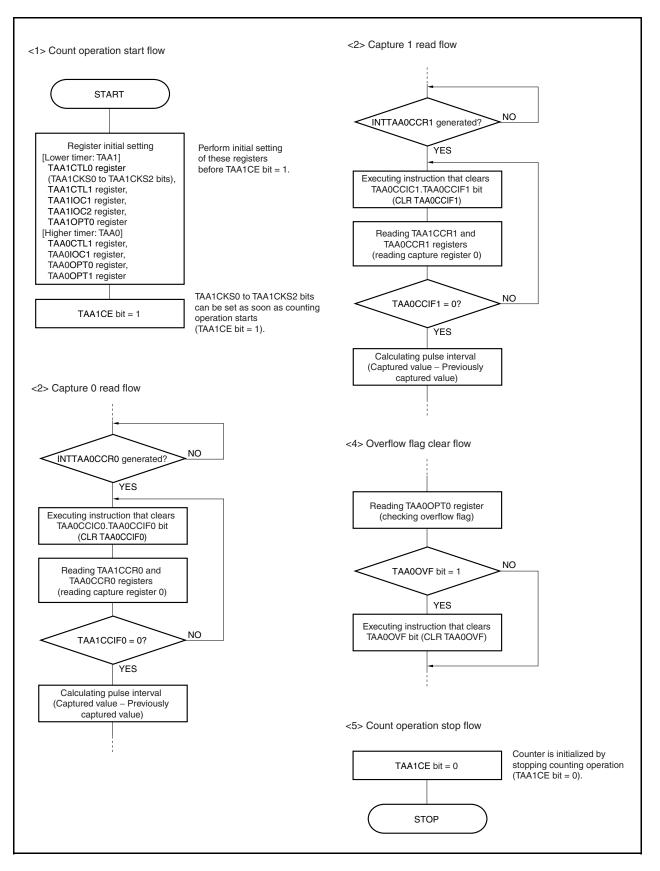

When the TAAnCE bit is set to 1, the 16-bit counter starts counting. When the valid edge input to the TIAAnm pin is detected, the count value of the 16-bit counter is stored in the TAAnCCRm register, and a capture interrupt request signal (INTTAAnCCm) is generated.

The 16-bit counter continues counting in synchronization with the count clock. When it counts up to FFFFH, it generates an overflow interrupt request signal (INTTAAnOV) at the next clock, is cleared to 0000H, and continues counting. At this time, the overflow flag (TAAnOPT0.TAAnOVF bit) is also set to 1. Clear the overflow flag to 0 by executing the CLR instruction by software.

Figure 6-51. Operation Flow in Cascade Connection of TAA1 and TAA0 (2/2)

# Figure 8-27. Setting of Registers in One-Shot Pulse Output Mode (2/2)

| (d)     | (d) TMT0 I/O control register 2 (TT0IOC2)                                                                |            |            |            |             |             |                         |          |                                                                                       |

|---------|----------------------------------------------------------------------------------------------------------|------------|------------|------------|-------------|-------------|-------------------------|----------|---------------------------------------------------------------------------------------|

|         |                                                                                                          |            |            |            | TT0EES1     | TT0EES0     | TT0ETS1                 | TT0ETS0  |                                                                                       |

| TT0IOC2 | 0                                                                                                        | 0          | 0          | 0          | 0           | 0           | 0/1                     | 0/1      |                                                                                       |

|         |                                                                                                          |            |            |            |             |             |                         |          | Select valid edge of external<br>trigger input (EVTT0 pin) <sup>Note</sup>            |

|         | Note Set the valid edge selection of the unused alternate external input signals to "No edge detection". |            |            |            |             |             | put signals to "No edge |          |                                                                                       |

| (e)     | TMT0 cou                                                                                                 | inter read | l buffer r | egister (T | TOCNT)      |             |                         |          |                                                                                       |

|         | The value of the 16-bit counter can be read by reading the TT0CNT register.                              |            |            |            |             |             |                         |          |                                                                                       |

| (f)     | TMT0 capture/compare registers 0 and 1 (TT0CCR0 and TT0CCR1)                                             |            |            |            |             |             |                         |          |                                                                                       |

|         | If Do is set to the TTOCCR0 register and D1 to the TTOCCR1 register, the active level width and output   |            |            |            |             |             |                         |          |                                                                                       |

|         | delay period of the one-shot pulse are as follows.                                                       |            |            |            |             |             |                         |          |                                                                                       |

|         | Active leve                                                                                              | el width = | (D0 – D1 - | + 1) × Cou | int clock c | ycle        |                         |          |                                                                                       |

|         | Output delay period = D1 × Count clock cycle                                                             |            |            |            |             |             |                         |          |                                                                                       |

|         | Remark                                                                                                   | register 3 |            | 3), TMT0   | option re   | gister 0 (T | T0OPT0)                 | , TMT0 o | T0IOC1), TMT0 I/O control<br>ption register 1 (TT0OPT1),<br>e-shot pulse output mode. |

# CHAPTER 16 ASYNCHRONOUS SERIAL INTERFACE C (UARTC)

The V850ES/JC3-H (40 pin) have a 3 channels UARTC. The V850ES/JC3-H (48 pin) and V850ES/JE3-H have a 4channels UARTC.

### 16.1 Features

- O Transfer rate: 300 bps to 3 Mbps (using internal system clock of 24 MHz and dedicated baud rate generator)

- O Full-duplex communication: Internal UARTCn receive data register (UCnRX)

Internal UARTCn transmit data register (UCnTX)

O 2-pin configuration: TXDCn: Transmit data output pin

RXDCn: Receive data input pin

- O Reception error detection function

- Parity error

- Framing error

- Overrun error

- LIN communication data consistency error detect function

- SBF reception success detect function

- O Interrupt sources: 2 types

- Reception completion interrupt (INTUCnR):

This interrupt occurs upon transfer of receive data from the receive shift register to the receive data register after serial transfer is complete, in the reception enabled status.

• Transmission enable interrupt (INTUCnT):

This interrupt occurs upon transfer of transmit data from the transmit data register to the transmit shift register in the transmission enabled status.

- O Character length: 7 to 9 bits

- O Parity function: Odd, even, 0, none

- O Transmission stop bit: 1, 2 bits

- O On-chip dedicated baud rate generator

- O MSB-/LSB-first transfer selectable

- O Transmit/receive data inverted input/output possible

- O SBF (Sync Break Field) transmission in the LIN (Local Interconnect Network) communication format

- 13 to 20 bits selectable for the SBF transmission

- Recognition of 11 bits or more possible for SBF reception

- SBF reception flag provided

**Remark** n = 0, 2, 4 (V850ES/JC3-H (40 pin)) n = 0, 2 to 4 (V850ES/JC3-H (48 pin), V850ES/JE3-H)

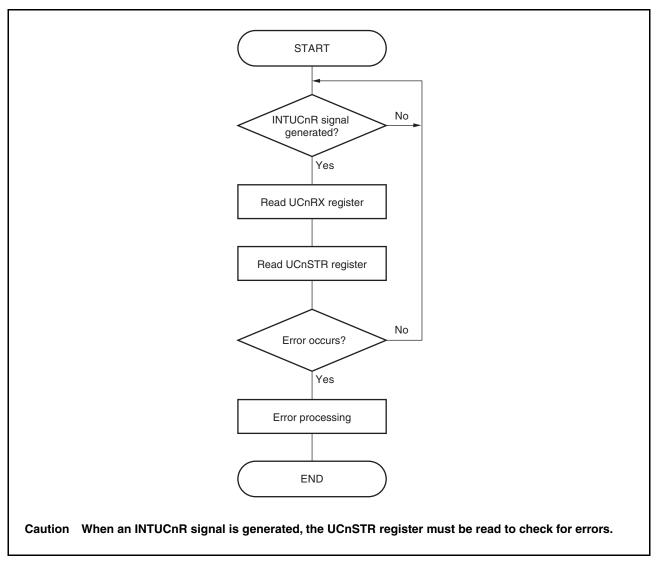

#### 16.6.8 Reception errors

Errors during a receive operation are of three types: parity errors, framing errors, and overrun errors. Data reception result error flags are set in the UCnSTR register and a reception completion interrupt request signal (INTUCnR) is output when an error occurs.

It is possible to ascertain which error occurred during reception by reading the contents of the UCnSTR register. Clear the reception error flag by writing 0 to it after reading it.

Figure 16-15. Receive Data Read Flow

Remark fxx: Main clock frequency ERR: Baud rate error (%)

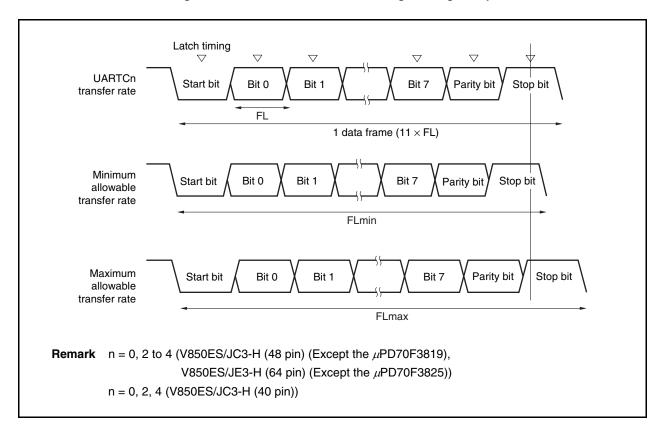

#### (5) Allowable baud rate range during reception

The baud rate error range at the destination that is allowable during reception is shown below.

# Caution The baud rate error during reception must be set within the allowable error range using the following equation.

Figure 16-19. Allowable Baud Rate Range During Reception

As shown in Figure 16-20, the receive data latch timing is determined by the counter set using the UCnCTL2 register following start bit detection. The transmit data can be normally received if up to the last data (stop bit) can be received in time for this latch timing.

When this is applied to 11-bit reception, the following is the theoretical result.

$FL = (Brate)^{-1}$

Brate: UARTCn baud rate (n = 0 to 2, 4)

- k: Set value of UCnCTL2.UCnBRS7 to UCnCTL2.UCnBRS0 bits (n = 0 to 2, 4)

- FL: 1-bit data length

Latch timing margin: 2 clocks

Minimum allowable transfer rate: FLmin =  $11 \times FL - \frac{k-2}{2k} \times FL = \frac{21k+2}{2k}$  FL

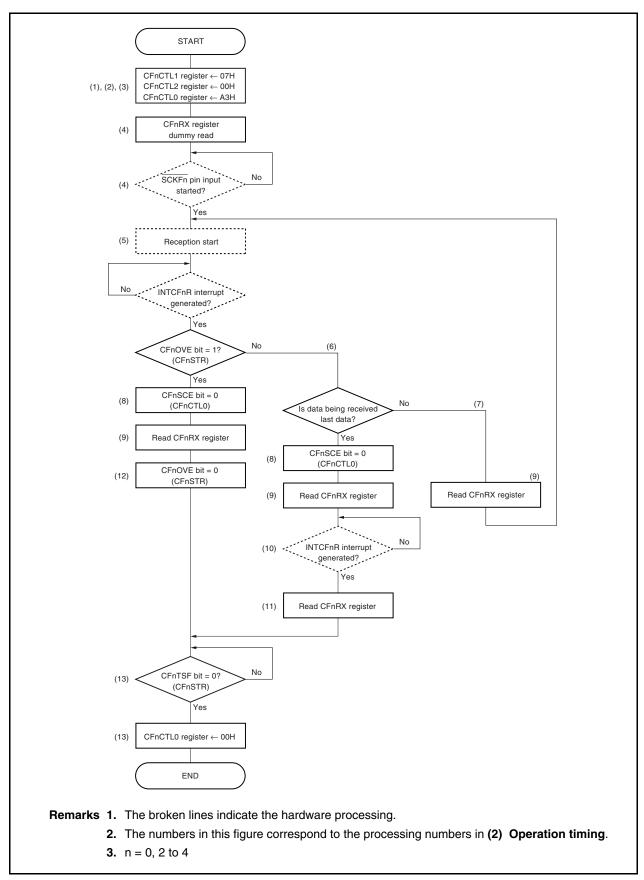

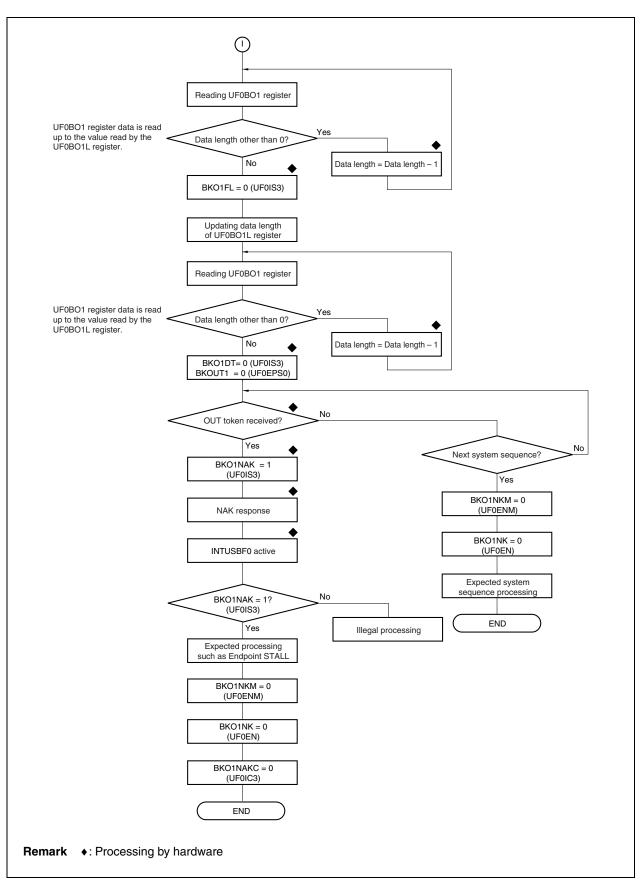

# (1) Operation flow

#### (5) When arbitration loss occurs due to stop condition during data transfer

| Address   | Register Name                          | Symbol      | R/W | Bit Manipulation Units |              | n Units      | After Reset           |

|-----------|----------------------------------------|-------------|-----|------------------------|--------------|--------------|-----------------------|

|           |                                        |             |     | 1 Bit                  | 8 Bits       | 16 Bits      |                       |

| 03FEC4C0H | CAN0 message data byte 01 register 30  | C0MDATA0130 | R/W |                        |              | $\checkmark$ | Undefined             |

| 03FEC4C0H | CAN0 message data byte 0 register 30   | COMDATA030  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4C1H | CAN0 message data byte 1 register 30   | C0MDATA130  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4C2H | CAN0 message data byte 23 register 30  | C0MDATA2330 |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4C2H | CAN0 message data byte 2 register 30   | C0MDATA230  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4C3H | CAN0 message data byte 3 register 30   | C0MDATA330  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4C4H | CAN0 message data byte 45 register 30  | C0MDATA4530 |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4C4H | CAN0 message data byte 4 register 30   | C0MDATA430  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4C5H | CAN0 message data byte 5 register 30   | C0MDATA530  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4C6H | CAN0 message data byte 67 register 30  | COMDATA6730 |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4C6H | CAN0 message data byte 6 register 30   | COMDATA630  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4C7H | CAN0 message data byte 7 register 30   | COMDATA730  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4C8H | CAN0 message data length register 30   | C0MDLC30    |     |                        | $\checkmark$ |              | 0000xxxxB             |

| 03FEC4C9H | CAN0 message configuration register 30 | C0MCONF30   |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4CAH | CAN0 message identifier register 30    | C0MIDL30    |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4CCH |                                        | C0MIDH30    |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4CEH | CAN0 message control register 30       | COMCTRL30   |     |                        |              | V            | 00x00000<br>000xx000B |

| 03FEC4E0H | CAN0 message data byte 01 register 31  | C0MDATA0131 |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4E0H | CAN0 message data byte 0 register 31   | C0MDATA031  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4E1H | CAN0 message data byte 1 register 31   | C0MDATA131  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4E2H | CAN0 message data byte 23 register 31  | C0MDATA2331 |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4E2H | CAN0 message data byte 2 register 31   | C0MDATA231  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4E3H | CAN0 message data byte 3 register 31   | C0MDATA331  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4E4H | CAN0 message data byte 45 register 31  | C0MDATA4531 |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4E4H | CAN0 message data byte 4 register 31   | C0MDATA431  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4E5H | CAN0 message data byte 5 register 31   | C0MDATA531  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4E6H | CAN0 message data byte 67 register 31  | C0MDATA6731 |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4E6H | CAN0 message data byte 6 register 31   | C0MDATA631  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4E7H | CAN0 message data byte 7 register 31   | C0MDATA731  |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4E8H | CAN0 message data length register 31   | C0MDLC31    |     |                        | $\checkmark$ |              | 0000xxxxB             |

| 03FEC4E9H | CAN0 message configuration register 31 | C0MCONF31   |     |                        | $\checkmark$ |              | Undefined             |

| 03FEC4EAH | CAN0 message identifier register 31    | C0MIDL31    |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4ECH | ]                                      | C0MIDH31    |     |                        |              | $\checkmark$ | Undefined             |

| 03FEC4EEH | CAN0 message control register 31       | COMCTRL31   |     |                        |              | V            | 00x00000<br>000xx000B |

# (7) CAN0 module last error information register (C0LEC)

The COLEC register provides the error information of the CAN protocol.

|       | 7                                                  | 7<br> | 6      | 5                                                                                                                                                                                                 | 4            | 3          | 2          | 1          | 0              |  |

|-------|----------------------------------------------------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|------------|------------|----------------|--|

| C0LEC | 0                                                  | )     | 0      | 0                                                                                                                                                                                                 | 0            | 0          | LEC2       | LEC1       | LEC0           |  |

| LEC2  | LEC2 LEC1 LEC0 Last CAN protocol error information |       |        |                                                                                                                                                                                                   |              |            |            |            |                |  |

| 0     | 0                                                  | 0     | No er  | ror                                                                                                                                                                                               |              |            |            |            |                |  |

| 0     | 0                                                  | 1     | Stuff  | error                                                                                                                                                                                             |              |            |            |            |                |  |

| 0     | 1                                                  | 0     | Form   | error                                                                                                                                                                                             |              |            |            |            |                |  |

| 0     | 1                                                  | 1     | ACK    | error                                                                                                                                                                                             |              |            |            |            |                |  |

| 1     | 0                                                  | 0     | transr | Bit error. (The CAN module tried to transmit a recessive-level bit as part of a transmit message (except the arbitration field), but the value on the CAN bus is a dominant-level bit.)           |              |            |            |            |                |  |

| 1     | 0                                                  | 1     | transr | Bit error. (The CAN module tried to transmit a dominant-level bit as part of a transmit message, ACK bit, error frame, or overload frame, but the value on the CAN bus is a recessive-level bit.) |              |            |            |            |                |  |

| 1     | 1                                                  | 0     | CRC    | CRC error                                                                                                                                                                                         |              |            |            |            |                |  |

| 1     | 1                                                  | 1     | Unde   | Undefined                                                                                                                                                                                         |              |            |            |            |                |  |

|       | Be sure to<br>1. The o                             |       |        |                                                                                                                                                                                                   | ister are no | ot cleared | when the C | CAN module | e changes fror |  |

is ignored.

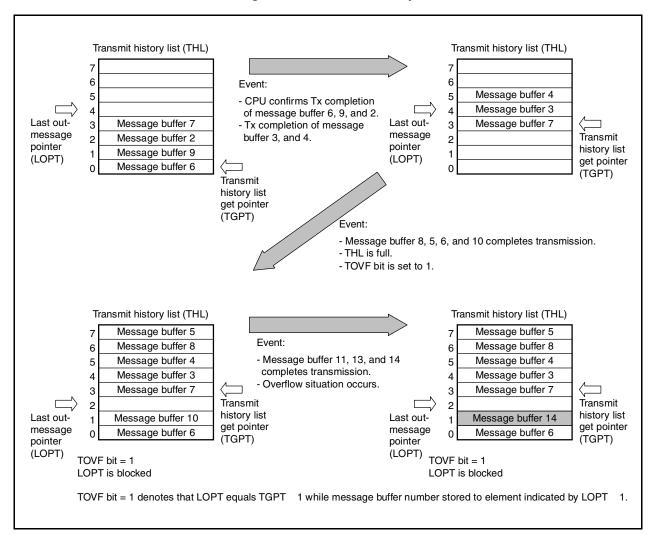

Figure 19-32. Transmit History List

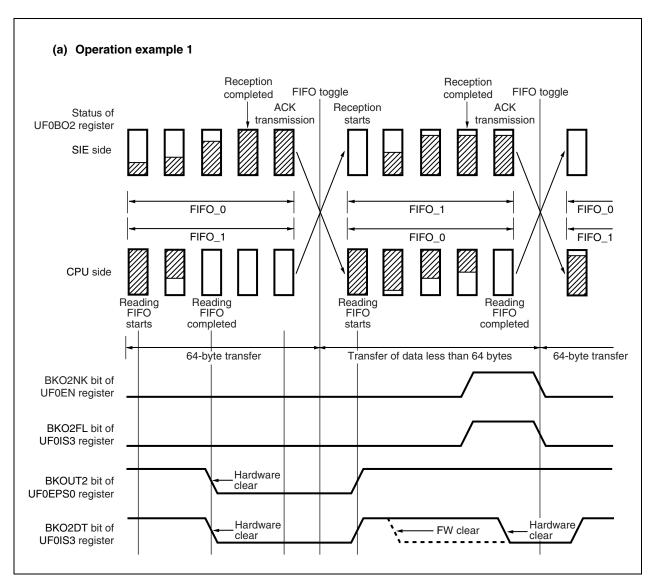

Figure 20-8. Operation of UF0BO2 Register (1/2)

| Request        | Reception<br>Side | Processing/<br>Frequency    | Explanation                                                                                                                                                                                                                                                                                                                                       |

|----------------|-------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLEAR_FEATURE  | Interface         | Automatic STALL<br>response | It is considered that this request does not come to Interface<br>because there is no function selector value, though it is reserved<br>for bmRequestType.<br>When this request is received, the hardware makes an automatic<br>STALL response.                                                                                                    |

| SET_FEATURE    | Interface         | Automatic STALL<br>response | It is considered that this request does not come to Interface<br>because there is no function selector value, though it is reserved<br>for bmRequestType.<br>When this request is received, the hardware makes an automatic<br>STALL response.                                                                                                    |

| GET_DESCRIPTOR | String            | FW                          | Returns the string descriptor.<br>When this request is received by the SETUP token, the hardware<br>generates the CPUDEC interrupt request for FW. FW decodes the<br>contents of the request from the CPUDEC interrupt request, and<br>writes the data to be returned to the host, to the UF0E0W register.                                        |

| SET_DESCRIPTOR | Device            | FW                          | Rewrites the device descriptor.<br>When this request is received by the SETUP token, the hardware<br>generates the CPUDEC interrupt request for FW. FW decodes the<br>contents of the request from the CPUDEC interrupt request, and<br>the writes the data for the next control transfer (OUT) to the<br>UF0DDn register (n = 0 to 17).          |

| SET_DESCRIPTOR | Configuration     | FW                          | Rewrites the configuration descriptor.<br>When this request is received by the SETUP token, the hardware<br>generates the CPUDEC interrupt request for FW. FW decodes the<br>contents of the request from the CPUDEC interrupt request, and<br>the writes the data for the next control transfer (OUT) to the<br>UF0CIEn register (n = 0 to 255). |

| SET_DESCRIPTOR | String            | FW                          | Rewrites the string descriptor.<br>When this request is received by the SETUP token, the hardware<br>generates the CPUDEC interrupt request for FW. FW decodes the<br>contents of the request from the CPUDEC interrupt request, and<br>loads the data for the next control transfer (OUT).                                                       |

| Other          | NA                | FW                          | When this request is received by the SETUP token, the hardware generates the CPUDEC interrupt request for FW. FW decodes the contents of the request from the CPUDEC interrupt request, and performs the necessary processing.                                                                                                                    |

Table 20-9.

FW-Supported Standard Requests

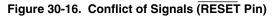

# (4) RESET pin

When the reset signals of the dedicated flash programmer are connected to the  $\overrightarrow{\mathsf{RESET}}$  pin that is connected to the reset signal generator on-board, a conflict of signals occurs. To avoid the conflict of signals, isolate the connection to the reset signal generator.

When a reset signal is input from the user system in the flash memory programming mode, the programming operation will not be performed correctly. Therefore, do not input signals other than the reset signals from the dedicated flash programmer.

#### (5) Port pins (including NMI)

When the system shifts to the flash memory programming mode, all the pins that are not used for flash memory programming are in the same status as that immediately after reset. If the external device connected to each port does not recognize the status of the port immediately after reset, pins require appropriate processing, such as connecting to V<sub>DD</sub> via a resistor or connecting to V<sub>SS</sub> via a resistor.

#### (6) Other signal pins

Connect X1, X2, XT1, XT2, and REGC in the same status as that in the normal operation mode. During flash memory programming, input a low level to the  $\overrightarrow{\text{DRST}}$  pin or leave it open. Do not input a high level.

#### (7) Power supply

Supply the same power (VDD, VSS, EVDD, UVDD, AVREF0, AVREF1, AVSS) as in normal operation mode.

|          |                                    |       | (24/34 |

|----------|------------------------------------|-------|--------|

| Symbol   | Name                               | Unit  | Page   |

| TM0CMP0  | TMM0 compare register 0            | Timer | 520    |

| TM0CTL0  | TMM0 control register 0            | Timer | 521    |

| TM0EQIC0 | Interrupt control register         | INTC  | 1222   |

| TM1CMP0  | TMM1 compare register 0            | Timer | 520    |

| TM1CTL0  | TMM1 control register 0            | Timer | 521    |

| TM1EQIC0 | Interrupt control register         | INTC  | 1222   |

| TM2CMP0  | TMM2 compare register 0            | Timer | 520    |

| TM2CTL0  | TMM2 control register 0            | Timer | 521    |

| TM2EQIC0 | Interrupt control register         | INTC  | 1222   |

| TM3CMP0  | TMM3 compare register 0            | Timer | 520    |

| TM3CTL0  | TMM3 control register 0            | Timer | 521    |

| TM3EQIC0 | Interrupt control register         | INTC  | 1222   |

| TTNFC    | Noise elimination control register | Timer | 410    |

| TRXIC0   | Interrupt control register         | INTC  | 1222   |

| TT0CCIC0 | Interrupt control register         | INTC  | 1222   |

| TT0CCIC1 | Interrupt control register         | INTC  | 1222   |

| TT0CCR0  | TMT0 capture/compare register 0    | Timer | 405    |

| TT0CCR1  | TMT0 capture/compare register 1    | Timer | 407    |

| TTOCNT   | TMT0 counter read buffer register  | Timer | 409    |

| TT0CTL0  | TMT0 control register 0            | Timer | 391    |

| TT0CTL1  | TMT0 control register 1            | Timer | 392    |

| TT0CTL2  | TMT0 control register 2            | Timer | 394    |

| TTOIECIC | Interrupt control register         | INTC  | 1222   |

| TT0IOC0  | TMT0 I/O control register 0        | Timer | 396    |

| TT0IOC1  | TMT0 I/O control register 1        | Timer | 398    |

| TT0IOC2  | TMT0 I/O control register 2        | Timer | 399    |

| TT0IOC3  | TMT0 I/O control register 3        | Timer | 400    |

| TT0OPT0  | TMT0 option register 0             | Timer | 402    |

| TT0OPT1  | TMT0 option register 1             | Timer | 403    |

| TT0OVIC  | Interrupt control register         | INTC  | 1222   |

| TTOTCW   | TMT0 count write register          | Timer | 409    |

| UC0CTL0  | UARTC0 control register 0          | UARTC | 679    |

| UC0CTL1  | UARTC0 control register 1          | UARTC | 707    |

| UC0CTL2  | UARTC0 control register 2          | UARTC | 708    |

| UC0OPT0  | UARTC0 option control register 0   | UARTC | 681    |

| UC0OPT1  | UARTC0 option control register 1   | UARTC | 683    |

| UCORIC   | Interrupt control register         | INTC  | 1222   |

| UC0RX    | UARTC0 receive data register       | UARTC | 687    |

| UCORXL   | UARTC0 receive data register L     | UARTC | 687    |

| UC0STR   | UARTC0 status register             | UARTC | 685    |

| UCOTIC   | Interrupt control register         | INTC  | 1222   |

| UCOTX    | UARTC0 transmit data register      | UARTC | 688    |

| UCOTX    | UARTC0 transmit data register L    | UARTC | 688    |

V850ES/JC3-H, V850ES/JE3-H User's Manual: Hardware

| Publication Date: |           | Sep 20, 2011<br>Mar 25, 2014 |

|-------------------|-----------|------------------------------|

| Published by:     | Renesas E | electronics Corporation      |