# E. Renesas Electronics America Inc - UPD70F3825GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 48MHz                                                                                |

| Connectivity               | CANbus, CSI, EBI/EMI, I <sup>2</sup> C, UART/USART, USB                              |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 45                                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 24K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 10x10b; D/A 1x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3825gb-gah-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (1) TAAn control register 0 (TAAnCTL0)

The TAAnCTL0 register is an 8-bit register that controls the operation of TAAn.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

The same value can always be written to the TAAnCTL0 register by software.

| TAAnCTL0       TAAnCE       0       0       0       TAAnCKS2       TAAnCKS1       TAAnCKS1         (n = 0 to 2, 4)       TAAnCE       TAAnCE       TAAn operation control       Image: Control operation control control operation control operation control control operation control control operation control control operation control c |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAAnCE     TAAn operation control       0     TAAn operation disabled (TAAn reset asynchronously <sup>Note</sup> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0 TAAn operation disabled (TAAn reset asynchronously <sup>Note</sup> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 TAAn operation enabled. TAAn operation started.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TAAnCKS2 TAAnCKS1 TAAnCKS0 Internal count clock selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| n = 0, 1, 4 n = 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0 0 0 fxx (20.8 ns) fxx/2 (41.7 ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0 0 1 fxx/2 (41.7 ns) fxx/4 (83.3 ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0 1 0 fxx/4 (83.3 ns) fxx/8 (166.7 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0 1 1 fxx/8 (166.7 ns) fxx/16 (333.3 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1 0 0 fxx/16 (333.3 ns) fxx/64 (1.3333 µ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1 0 1 fxx/32 (666.7 ns) fxx/256 (5.3333 µ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 1 0 fxx/64 (1.3333 µs) fxx/512 (10.6667                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 1 1 fxx/128 (2.6667 µs) fxx/1024 (21.3333                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

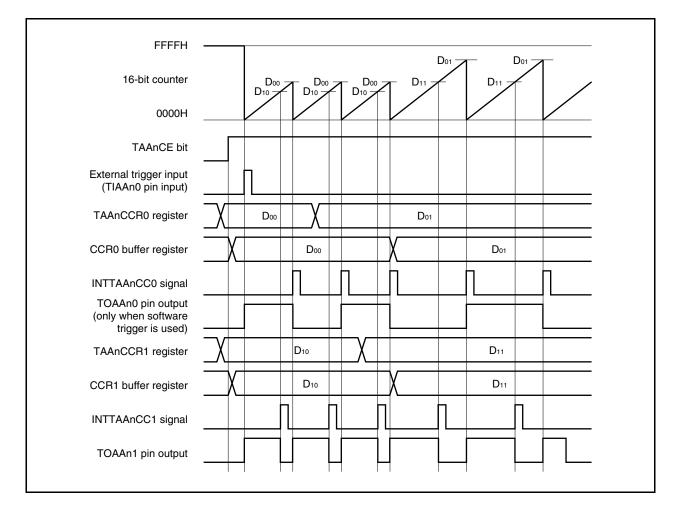

# (2) External trigger pulse output mode operation timing

#### (a) Note on changing pulse width during operation

To change the PWM waveform while the counter is operating, write the TAAnCCR1 register last. Rewrite the TAAnCCRm register after writing the TAAnCCR1 register after the INTTAAnCC0 signal is detected.

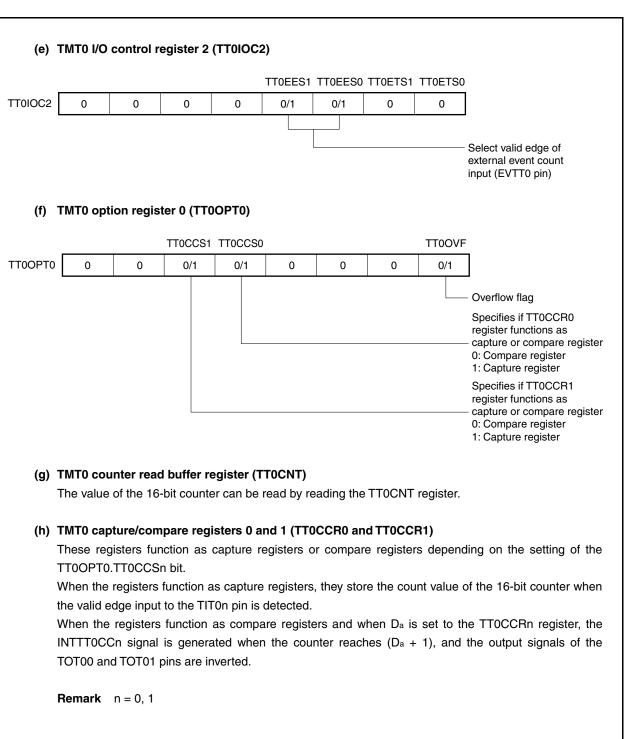

To output a 100% waveform, set a value of (set value of TT0CCR0 register + 1) to the TT0CCR1 register. If the set value of the TT0CCR0 register is FFFFH, 100% output cannot be produced.

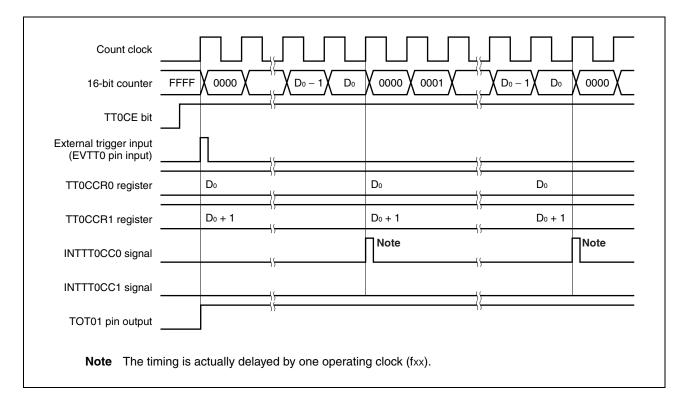

#### Figure 8-36. Register Setting in Free-Running Timer Mode (2/2)

# (2) Operation timing in pulse width measurement mode

# (a) Clearing overflow flag

The overflow flag can be cleared to 0 by clearing the TT0OVF bit to 0 with the CLR instruction after reading the TT0OVF bit when it is 1 and by writing 8-bit data (bit 0 is 0) to the TT0OPT0 register after reading the TT0OVF bit when it is 1.

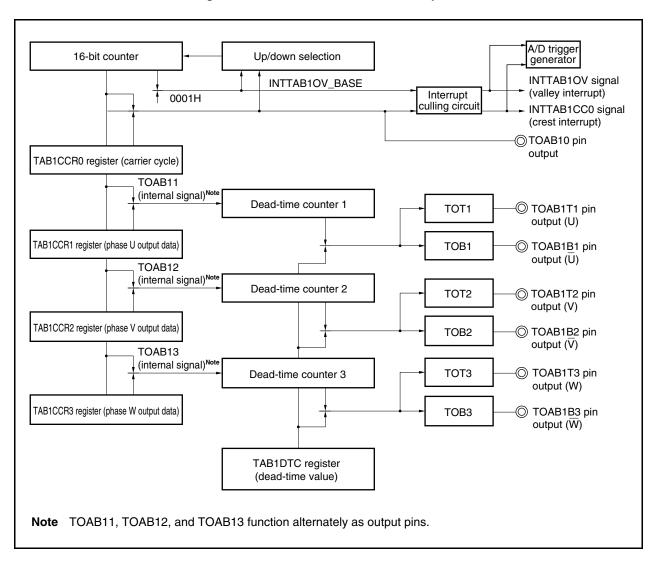

Figure 10-5. Outline of 6-Phase PWM Output Mode

- Cautions 1. The A/D conversion start trigger signal output that is set by the TAB1AT2 and TAB1AT3 bits can be used only when TAA4 is performing a tuning operation as the slave timer of TAB1. If TAB1 and TAA4 are not performing a tuning operation, or if a mode other than the 6-phase PWM output mode is used, the output cannot be guaranteed.

- 2. The TAB1 signal output is internally used to identify whether the 16-bit counter is counting up or down. Therefore, enable TOAB10 pin output by clearing the TAB1IOC0.TAB1OL0 bit to 0 and setting the TAB1IOC0.TAB1OE0 bit to 1.

# 14.5 Operation

#### 14.5.1 Basic operation

- <1> Set the operation mode, trigger mode, and conversion time for executing A/D conversion by using the ADA0M0, ADA0M1, ADA0M2, and ADA0S registers. When the ADA0CE bit of the ADA0M0 register is set, conversion is started in the software trigger mode and the A/D converter waits for a trigger in the external or timer trigger mode.

- <2> When A/D conversion is started, the voltage input to the selected analog input channel is sampled by the sample & hold circuit.

- <3> When the sample & hold circuit samples the input channel for a specific time, it enters the hold status, and holds the input analog voltage until A/D conversion is complete.

- <4> Set bit 9 of the successive approximation register (SAR), and set the compare voltage generation DAC to (1/2) AV<sub>REF0</sub>.

- <5> The voltage difference between the voltage of the compare voltage generation DAC and the analog input voltage is compared by the voltage comparator. If the analog input voltage is higher than (1/2) AVREF0, the MSB of the SAR remains set. If it is lower than (1/2) AVREF0, the MSB is reset.

- <6> Next, bit 8 of the SAR is automatically set and the next comparison is started. Depending on the value of bit 9, to which a result has been already set, the compare voltage generation DAC is selected as follows.

• Bit 9 = 1: (3/4) AVREFO

• Bit 9 = 0: (1/4) AVREF0

This compare voltage and the analog input voltage are compared and, depending on the result, bit 8 is manipulated as follows.

Analog input voltage  $\geq$  Compare voltage: Bit 8 = 1 Analog input voltage  $\leq$  Compare voltage: Bit 8 = 0

- <7> This comparison is continued to bit 0 of the SAR.

- <8> When comparison of the 10 bits is complete, the valid digital result remains in the SAR, and is then transferred to and stored in the ADA0CRn register. After that, an A/D conversion end interrupt request signal (INTAD) is generated.

- <9> In one-shot select mode, conversion is stopped<sup>Note</sup>. In one-shot scan mode, conversion is stopped after scanning once<sup>Note</sup>. In continuous select mode, repeat steps <2> to <8> until the ADA0M0.ADA0CE bit is cleared to 0. In continuous scan mode, repeat steps <2> to <8> for each channel.

- **Note** In the external trigger mode, timer trigger mode 0, or timer trigger mode 1, the trigger standby status is entered.

- **Remark** The trigger standby status means the status after the stabilization time has elapsed.

(4/4)

|                                                                                                      | Stop con                                                                                                                                                                               | dition trigger                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                                                                                    | Stop condition is not generated.                                                                                                                                                       |                                                                                                                                                                                                                                                                                       |

| 1                                                                                                    | -                                                                                                                                                                                      | the SCL0n line to high level or wait until the SCL0n unt of time has elapsed, the SDA0n line is changed                                                                                                                                                                               |

| For master<br>For master<br>• Cannot t<br>• The SPT<br>• When th<br>eight clo<br>The WTI<br>SPTn bit | after the slave has been notified of                                                                                                                                                   | ted normally during the ACK reception period. Set<br>ws output of the ninth clock.<br>t to 1 during the wait period that follows output of<br>ring the high-level period of the ninth clock.<br>ait period following output of eight clocks, and the<br>vs output of the ninth clock. |

| Condition                                                                                            | for clearing (SPTn bit = 0) Co                                                                                                                                                         | ndition for setting (SPTn bit = 1)                                                                                                                                                                                                                                                    |

| <ul> <li>Automat</li> <li>Cleared save)</li> </ul>                                                   | <ul> <li>by loss in arbitration</li> <li>ically cleared after stop condition is detected when the LRELn bit = 1 (communication</li> <li>e IICEn bit = 0 (operation stop) et</li> </ul> | Set by instruction                                                                                                                                                                                                                                                                    |

Caution If the WRELn bit is set to 1 during the ninth clock and the wait state is canceled when the TRCn bit is 1, the TRCn bit is cleared to 0 and the SDA0n line is set to high impedance.

Remark The SPTn bit is 0 if it is read immediately after data setting.

# (2) Start ~ Address ~ Data ~ Start ~ Address ~ Data ~ Stop (restart)

|                                                                                                                                                             | <1> When W       |               | 01t = 0  |             |            |              |            |     |     |          |     |                |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|----------|-------------|------------|--------------|------------|-----|-----|----------|-----|----------------|----|

|                                                                                                                                                             |                  |               |          |             | STTn       | bit = 1<br>↓ |            |     |     |          | SPT | n bit = 1<br>↓ |    |

| ST                                                                                                                                                          | AD6 to AD0       | R/W           | ACK      | D7 to D0    | ACK        | ST           | AD6 to AD0 | R/W | ACK | D7 to D0 | ACK | SP             |    |

|                                                                                                                                                             |                  |               |          | <b>1</b>    | <b>▲</b> 2 | ▲3           |            |     | 4   | ▲4       | ▲5  | ▲6             | Δ7 |

|                                                                                                                                                             | ▲1: IICS         | n registe     | er = 100 | 0X110B      |            |              |            |     |     |          |     |                |    |

| ▲2: IICSn register = 1000X000B (WTIMn bit = 1)                                                                                                              |                  |               |          |             |            |              |            |     |     |          |     |                |    |

| ▲3: IICSn register = 1000XX00B (WTIMn bit = 0)                                                                                                              |                  |               |          |             |            |              |            |     |     |          |     |                |    |

|                                                                                                                                                             |                  | -             |          | 0X110B (WTI |            |              |            |     |     |          |     |                |    |

|                                                                                                                                                             |                  |               |          | 0X000B (WTI | Mn bit =   | 1)           |            |     |     |          |     |                |    |

|                                                                                                                                                             | ▲6: IICS         |               |          |             |            |              |            |     |     |          |     |                |    |

|                                                                                                                                                             | $\Delta$ 7: IICS | n registe     | er = 000 | 00001B      |            |              |            |     |     |          |     |                |    |

|                                                                                                                                                             | <2> When W       | X:<br>/TIMn k |          | t care      | STTn       | bit = 1      |            |     |     |          | SPT | n bit = 1      |    |

| ST                                                                                                                                                          | AD6 to AD0       | R/W           | ACK      | D7 to D0    | ACK        | ↓<br>ST      | AD6 to AD0 | R/W | ACK | D7 to D0 | ACK | ↓<br>SP        |    |

| 31                                                                                                                                                          | ADO IO ADO       |               |          | 1           | 1          | ▲2           | ADO IO ADO |     |     | ▲3       | ACK | <br>▲4         |    |

|                                                                                                                                                             | ▲1: IICS         | n reaiste     |          |             | -          | <b>_</b> _   |            |     | -   |          |     | -              | 40 |

|                                                                                                                                                             | ▲2: IICS         |               |          |             |            |              |            |     |     |          |     |                |    |

|                                                                                                                                                             | ▲3: IICS         |               |          |             |            |              |            |     |     |          |     |                |    |

|                                                                                                                                                             | ▲4: IICS         | n registe     | er = 100 | 0XX00B      |            |              |            |     |     |          |     |                |    |

|                                                                                                                                                             | $\Delta$ 5: IICS | n registe     | er = 000 | 00001B      |            |              |            |     |     |          |     |                |    |

| <ul> <li>∆ 5: IICSn register = 0000001B</li> <li>Remark ▲: Always generated</li> <li>∆: Generated only when SPIEn bit = 1</li> <li>X: don't care</li> </ul> |                  |               |          |             |            |              |            |     |     |          |     |                |    |

#### 18.7.4 Operation without communication

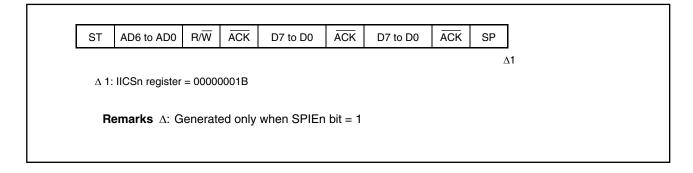

(1) Start ~ Code ~ Data ~ Data ~ Stop

# 18.7.5 Arbitration loss operation (operation as slave after arbitration loss)

(1) When arbitration loss occurs during transmission of slave address data

| ST                      | AD6 to AD0        | R/W                                                              | ĀCK                               | D7 to D0       | ĀCK       | D7 to D0       | ACK       | SP        |              |

|-------------------------|-------------------|------------------------------------------------------------------|-----------------------------------|----------------|-----------|----------------|-----------|-----------|--------------|

|                         |                   |                                                                  | 4                                 | ▲1             | ▲2        |                | ▲3        | Z         | \4           |

| ▲1:                     | IICSn registe     | = 01012                                                          | X110B (                           | Example: Whe   | en IICSn. | ALDn bit is re | ad during | g interru | pt servicing |

| ▲2:                     | IICSn registe     | r = 00012                                                        | X000B                             |                |           |                |           |           |              |

| ▲3:                     | IICSn registe     | r = 00012                                                        | X000B                             |                |           |                |           |           |              |

| Δ4:                     | IICSn register    | = 00000                                                          | 0001B                             |                |           |                |           |           |              |

|                         | Δ:                | Gener                                                            |                                   | nly when SP    | IEn bit = | : 1            |           |           |              |

| Whe                     | X:<br>en WTIMn bi | don't d<br>t = 1                                                 | care                              |                |           |                |           |           |              |

| Whe<br>ST               |                   |                                                                  | are<br>ACK                        | D7 to D0       | ĀCK       | D7 to D0       | ĀCK       | SP        |              |

|                         | en WTIMn bi       | t = 1                                                            | ĀCK                               | D7 to D0<br>▲1 | -         | D7 to D0       |           | _         | ]<br>\\4     |

| ST                      | AD6 to AD0        | t = 1<br>R/W                                                     | ĀĊĸ                               | ▲1             |           |                | <u>ا</u>  | 3 2       |              |

| ST<br>▲1:               | AD6 to AD0        | <b>t = 1</b><br>R/W                                              | <u>АСК</u><br>Х110В (             | ▲1             |           | 2              | <u>ا</u>  | 3 2       |              |

| ST<br>▲1:<br>▲2:        | AD6 to AD0        | t = 1<br>$R/\overline{W}$<br>r = 01012<br>r = 00012              | ACK<br>X110B (<br>X100B           | ▲1             |           | 2              | <u>ا</u>  | 3 2       |              |

| ST<br>▲1:<br>▲2:<br>▲3: | AD6 to AD0        | t = 1<br>$R/\overline{W}$<br>r = 01012<br>r = 00012<br>r = 00012 | ACK<br>X110B (I<br>X100B<br>XX00B | ▲1             |           | 2              | <u>ا</u>  | 3 2       |              |

# (2) When arbitration loss occurs during transmission of extension code

| ST                                     | AD6 to A                                                             | AD0                                                   | R/W                                                                  | ĀCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D7 to D0          | ĀCK       | D7 to D0             | ĀCK         | SP      |          |  |

|----------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|----------------------|-------------|---------|----------|--|

|                                        |                                                                      |                                                       |                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   | ▲2        |                      | ▲3          |         | <u>4</u> |  |

| <b>▲</b> 1:                            | : IICSn reg                                                          | gister                                                | = 0110                                                               | K010B (I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Example: Whe      | en ALDn   | bit is read du       | ring interi | upt ser | vicing)  |  |

| ▲2:                                    | : IICSn reg                                                          | gister                                                | = 00102                                                              | K000B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |           |                      |             |         |          |  |

| ▲3:                                    | ▲3: IICSn register = 0010X000B                                       |                                                       |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |           |                      |             |         |          |  |

| Δ4:                                    | : IICSn reg                                                          | gister                                                | = 00000                                                              | 001B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |           |                      |             |         |          |  |