Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 30/20MHz                                                                   |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIL                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at87c51rb2-3csul |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

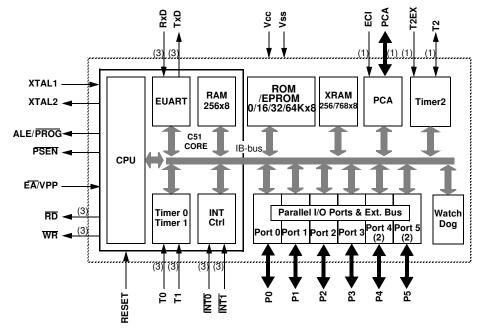

## 3. Block Diagram

(1): Alternate function of Port 1

(2): Only available on high pin count packages

(3): Alternate function of Port 3

## 4. SFR Mapping

The Special Function Registers (SFRs) of the TS80C51Rx2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3, P4, P5

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- HDW Watchdog Timer Reset: WDTRST, WDTPRG

- PCA registers: CL, CH, CCAPiL, CCAPiH, CCON, CMOD, CCAPMi

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

|     | Bit<br>addressable Non Bit addressable |                    |                     |                     |                      |                      |                      |                                     |     |  |  |

|-----|----------------------------------------|--------------------|---------------------|---------------------|----------------------|----------------------|----------------------|-------------------------------------|-----|--|--|

|     | 0/8                                    | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |  |

| F8h |                                        | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAPL2H<br>XXXX XXXX | CCAPL3H<br>XXXX XXXX | CCAPL4H<br>XXXX XXXX |                                     | FFh |  |  |

| F0h | B<br>0000 0000                         |                    |                     |                     |                      |                      |                      |                                     | F7h |  |  |

| E8h | P5 bit<br>addressable<br>1111 1111     | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                                     | EFh |  |  |

| E0h | ACC<br>0000 0000                       |                    |                     |                     |                      |                      |                      |                                     | E7h |  |  |

| D8h | CCON<br>00X0 0000                      | CMOD<br>00XX X000  | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                                     | DFh |  |  |

| D0h | PSW<br>0000 0000                       |                    |                     |                     |                      |                      |                      |                                     | D7h |  |  |

| C8h | T2CON<br>0000 0000                     | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                                     | CFh |  |  |

| C0h | P4 bit<br>addressable<br>1111 1111     |                    |                     |                     |                      |                      |                      | P5 byte<br>addressable<br>1111 1111 | C7h |  |  |

| B8h | IP<br>X000 000                         | SADEN<br>0000 0000 |                     |                     |                      |                      |                      |                                     | BFh |  |  |

| B0h | P3<br>1111 1111                        |                    |                     |                     |                      |                      |                      | IPH<br>X000 0000                    | B7h |  |  |

| A8h | IE<br>0000 0000                        | SADDR<br>0000 0000 |                     |                     |                      |                      |                      |                                     | AFh |  |  |

| A0h | P2<br>1111 1111                        |                    | AUXR1<br>XXXX0XX0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000                 | A7h |  |  |

| 98h | SCON<br>0000 0000                      | SBUF<br>XXXX XXXX  |                     |                     |                      |                      |                      |                                     | 9Fh |  |  |

| 90h | P1<br>1111 1111                        |                    |                     |                     |                      |                      |                      |                                     | 97h |  |  |

| 88h | TCON<br>0000 0000                      | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XXXXXX00     | CKCON<br>XXXX XXX0                  | 8Fh |  |  |

| 80h | P0<br>1111 1111                        | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000                   | 87h |  |  |

|     | 0/8                                    | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |  |

Table 4-1.

All SFRs with their address and their reset value

reserved

|                    |     | Pin Number |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|--------------------|-----|------------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mnemonic           | DIL | LCC        | VQFP 1.4 | Туре  | Name And Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                    | 12  | 14         | 8        | I     | INTO (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                    | 13  | 15         | 9        | I     | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                    | 14  | 16         | 10       | I     | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                    | 15  | 17         | 11       | I     | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                    | 16  | 18         | 12       | 0     | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                    | 17  | 19         | 13       | 0     | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Reset              | 9   | 10         | 4        | I     | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ . If the hardware watchdog reaches its time-out, the reset pin becomes an output during the time the internal reset is activated.                                                                                                                                                                                                                                                 |  |  |  |  |

| ALE/PROG           | 30  | 33         | 27       | O (I) | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during EPROM programming. ALE can be disabled by setting SFR's AUXR.0 bit. With this bit set, ALE will be inactive during internal fetches.                                           |  |  |  |  |

| PSEN               | 29  | 32         | 26       | 0     | <b>Program Store ENable:</b> The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                        |  |  |  |  |

| ĒĀ/V <sub>PP</sub> | 31  | 35         | 29       | I     | <b>External Access Enable/Programming Supply Voltage:</b> EA must be externally held low to enable the device to fetch code from external program memory locations 0000H and 3FFFH (RB) or 7FFFH (RC), or FFFFH (RD). If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than 3FFFH (RB) or 7FFFH (RC) EA must be held low for ROMless devices. This pin also receives the 12.75V programming supply voltage (V <sub>PP</sub> ) during EPROM programming. If security level 1 is programmed, EA will be internally latched on Reset. |  |  |  |  |

| XTAL1              | 19  | 21         | 15       | I     | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| XTAL2              | 18  | 20         | 14       | 0     | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

## 5.1 Pin Description for 64/68 pin Packages

Port 4 and Port 5 are 8-bit bidirectional I/O ports with internal pull-ups. Pins that have 1s written to them are pulled high by the internal pull ups and can be used as inputs.

As inputs, pins that are externally pulled low will source current because of the internal pull-ups.

Refer to the previous pin description for other pins.

**Table 5-1.**64/68 Pin Packages Configuration

| Pin | PLCC68 | SQUARE VQFP64 1.4 |

|-----|--------|-------------------|

| VSS | 51     | 9/40              |

| VCC | 17     | 8                 |

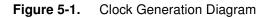

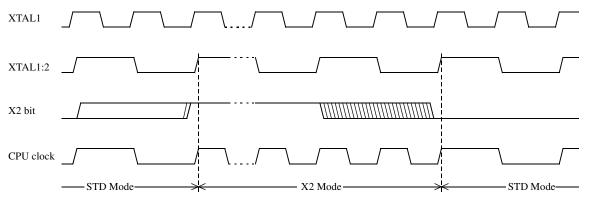

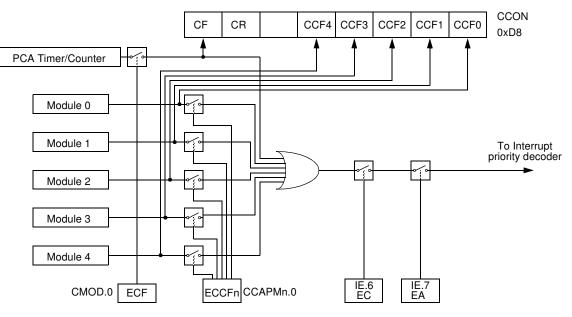

The X2 bit in the CKCON register (Table 5-2) allows to switch from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

Note: In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (UART, timers, PCA...) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. UART with 4800 baud rate will have 9600 baud rate.

| 7          | 6               | 5                               | 4                                                                               | 3               | 2                 | 1        | 0 |  |  |  |  |

|------------|-----------------|---------------------------------|---------------------------------------------------------------------------------|-----------------|-------------------|----------|---|--|--|--|--|

| -          | -               | -                               | X2                                                                              |                 |                   |          |   |  |  |  |  |

| Bit Number | Bit<br>Mnemonic | Description                     | escription                                                                      |                 |                   |          |   |  |  |  |  |

| 7          | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |          |   |  |  |  |  |

| 6          | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |          |   |  |  |  |  |

| 5          | -               | <b>Reserved</b><br>The value re | ad from this bit                                                                | is indeterminat | te. Do not set th | nis bit. |   |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                          |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | TF2             | <b>Timer 2 overflow Flag</b><br>Must be cleared by software.<br>Set by hardware on timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                                       |

| 6             | EXF2            | Timer 2 External Flag<br>Set when a capture or a reload is caused by a negative transition on T2EX pin if<br>EXEN2=1.<br>When set, causes the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is<br>enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter mode<br>(DCEN = 1) |

| 5             | RCLK            | <b>Receive Clock bit</b><br>Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                                           |

| 4             | TCLK            | <b>Transmit Clock bit</b><br>Clear to use timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                                                                                                                        |

| 3             | EXEN2           | <b>Timer 2 External Enable bit</b><br>Clear to ignore events on T2EX pin for timer 2 operation.<br>Set to cause a capture or reload when a negative transition on T2EX pin is detected, if<br>timer 2 is not used to clock the serial port.                                                                                          |

| 2             | TR2             | Timer 2 Run control bit<br>Clear to turn off timer 2.<br>Set to turn on timer 2.                                                                                                                                                                                                                                                     |

| 1             | C/T2#           | <b>Timer/Counter 2 select bit</b><br>Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for clock<br>out mode.                                                                                                 |

| 0             | CP/RL2#         | <b>Timer 2 Capture/Reload bit</b><br>If RCLK=1 or TCLK=1, CP/RL2# is ignored and timer is forced to auto-reload on timer 2<br>overflow.<br>Clear to auto-reload on timer 2 overflows or negative transitions on T2EX pin if EXEN2=1.<br>Set to capture on negative transitions on T2EX pin if EXEN2=1.                               |

Reset Value = 0000 0000b

Bit addressable

#### Table 6-3.

T2MOD Register T2MOD - Timer 2 Mode Control Register (C9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|---|---|---|---|---|---|------|------|

| - | - | - | - | - | - | T2OE | DCEN |

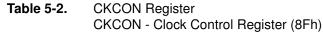

### Figure 6-4. PCA Timer/Counter

Table 6-4. CMOD: PCA Counter Mode Register

| C<br>Addr | CIDL               | WDTE       | -                                                                | -                        | -                          | CPS1      | CPS0       | ECF         |             |           |

|-----------|--------------------|------------|------------------------------------------------------------------|--------------------------|----------------------------|-----------|------------|-------------|-------------|-----------|

|           | Re                 | eset value | 0                                                                | 0                        | Х                          | Х         | х          | 0           | 0           | 0         |

| Symbol    | Functio            | n          |                                                                  |                          |                            |           |            |             |             |           |

| CIDL      |                    |            | ol: CIDL = 0 p<br>s it to be gate                                | 0                        |                            | ounter to | continue f | functioning | g during id | le Mode.  |

| WDTE      | Watchdo<br>enables | •          | nable: WDTE                                                      | E = 0 disab              | les Watch                  | dog Timer | function ( | on PCA M    | odule 4. W  | /DTE = 1  |

| -         | Not impl           | emented,   | reserved for                                                     | future use               | . (1)                      |           |            |             |             |           |

| CPS1      | PCA Co             | unt Pulse  | Select bit 1.                                                    |                          |                            |           |            |             |             |           |

| CPS0      | PCA Co             | unt Pulse  | Select bit 0.                                                    |                          |                            |           |            |             |             |           |

|           | CPS1               | CPS0       | Selected PC                                                      | A input. <sup>(2)</sup>  |                            |           |            |             |             |           |

|           | 0                  | 0          | Internal cloc                                                    | k f <sub>osc</sub> /12(0 | Or f <sub>osc</sub> /6 in  | X2 Mode   | ).         |             |             |           |

|           | 0                  | 1          | Internal cloc                                                    | k f <sub>osc</sub> /4(O  | r f <sub>osc</sub> /2 in X | K2 Mode). |            |             |             |           |

|           | 1                  | 0          | Timer 0 Ove                                                      | rflow                    |                            |           |            |             |             |           |

|           | 1                  | 1          | External clock at ECI/P1.2 pin (max rate = f <sub>osc</sub> / 8) |                          |                            |           |            |             |             |           |

| ECF       |                    |            | ter Overflow that function                                       |                          | ECF = 1 e                  | nables CF | bit in CC  | ON to ger   | nerate an i | nterrupt. |

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

2.  $f_{osc} = oscillator frequency$

**The CMOD SFR** includes three additional bits associated with the PCA (See Figure 6-4 and Table 6-4).

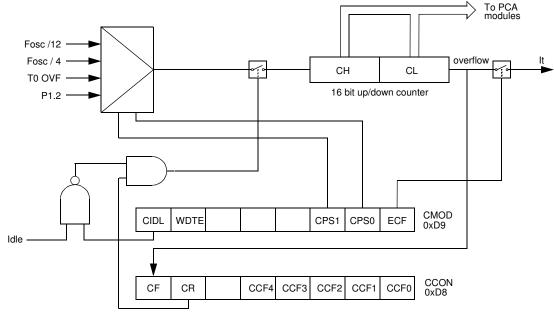

### Figure 6-5. PCA Interrupt System

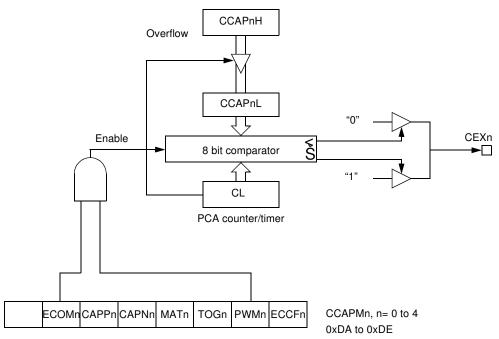

**PCA Modules:** each one of the five compare/capture modules has six possible functions. It can perform:

- 16-bit Capture, positive-edge triggered,

- 16-bit Capture, negative-edge triggered,

- 16-bit Capture, both positive and negative-edge triggered,

- 16-bit Software Timer,

- 16-bit High Speed Output,

- 8-bit Pulse Width Modulator.

In addition, module 4 can be used as a Watchdog Timer.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (See Table 6-6). The registers contain the bits that control the mode that each module will operate in.

- The ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module.

- PWM (CCAPMn.1) enables the pulse width modulation mode.

- The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register.

- The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

- The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

### Figure 6-9. PCA PWM Mode

### 6.3.5 PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 6-7 shows a diagram of how the watchdog works. The user preloads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. Periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. Disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

### 6.4 TS80C51Rx2 Serial I/O Port

The serial I/O port in the TS80C51Rx2 is compatible with the serial I/O port in the 80C52.

It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- · Automatic address recognition

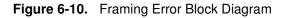

#### 6.4.1 Framing Error Detection

Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 6-10).

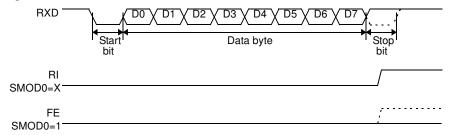

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 6-14.) bit is set.

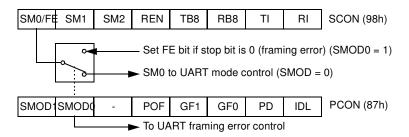

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 6-11 and Figure 6-12).

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | SMOD1           | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                                                                |

| 6             | SMOD0           | Serial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register.                                           |

| 5             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                     |

| 4             | POF             | <b>Power-Off Flag</b><br>Clear to recognize next reset type.<br>Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set by software. |

| 3             | GF1             | <b>General purpose Flag</b><br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                        |

| 2             | GF0             | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                               |

| 1             | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                             |

| 0             | IDL             | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                              |

Reset Value = 00X1 0000b

Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

| Table 6-19. | IPH Register |

|-------------|--------------|

|-------------|--------------|

IPH - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                            | 4                                                                            | 3                             | 2                | 1             | 0    |

|---------------|-----------------|----------------------------------------------|------------------------------------------------------------------------------|-------------------------------|------------------|---------------|------|

| -             | РРСН            | PT2H                                         | PSH                                                                          | PT1H                          | PX1H             | РТОН          | PX0H |

| Bit<br>Number | Bit<br>Mnemonic | Descrip                                      | otion                                                                        |                               |                  |               |      |

| 7             | -               | <b>Reserv</b><br>The val                     |                                                                              | nis bit is indeter            | ninate. Do not s | set this bit. |      |

| 6             | PPCH            | PCA int<br><u>PPCHP</u><br>0<br>1<br>1       | errupt priority t<br><u>PC Priori</u><br>0 Lowest<br>1<br>0<br>1 Highest     | ty Level                      |                  |               |      |

| 5             | PT2H            | Timer 2<br><u>PT2H P</u><br>0<br>0<br>1<br>1 |                                                                              | :                             | n bit            |               |      |

| 4             | PSH             | Serial p<br><u>PSH</u> 0<br>0<br>1<br>1      | ort Priority Hig<br>P <u>S Priority</u><br>0Lowest<br>1<br>0<br>1Highest     |                               |                  |               |      |

| 3             | PT1H            |                                              | overflow interr<br><u>T1Priority Leve</u><br>0Lowest<br>1<br>0<br>1Highest   | upt Priority Higl<br><u>위</u> | n bit            |               |      |

| 2             | PX1H            |                                              | l interrupt 1 Pri<br><u>X1Priority Leve</u><br>0Lowest<br>1<br>0<br>1Highest |                               |                  |               |      |

| 1             | РТОН            | Timer 0<br><u>PT0H P</u><br>0<br>0<br>1<br>1 | overflow interr<br><u>T0 Priority</u><br>0 Lowest<br>1<br>0<br>1 Highes      | 1                             | n bit            |               |      |

| 0             | РХОН            | Externa<br><u>PX0HP</u><br>0<br>0<br>1<br>1  | l interrupt 0 Pri<br><u>X0 Priority</u><br>0 Lowest<br>1<br>0<br>1 Highes    | Level                         |                  |               |      |

Reset Value = X000 0000b

Not bit addressable

## 6.9 ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS8xC51Rx2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C51Rx2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the TS80C51Rx2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

Table 6-23.

External Pin Status during ONCE Mode

WARNING: Security level 2 and 3 should only be programmed after EPROM and Core verification.

#### 9.2.3 Signature bytes

The TS87C51RB2/RC2/RD2 contains 4 factory programmed signatures bytes. To read these bytes, perform the process described in Section "Signature bytes".

#### 9.3 EPROM Programming

#### 9.3.1 Set-up Modes

In order to program and verify the EPROM or to read the signature bytes, the TS87C51RB2/RC2/RD2 is placed in specific set-up modes (See Figure 9-1.).

Control and program signals must be held at the levels indicated in Table 9-2.

#### 9.3.2 Definition of Terms

Address Lines: P1.0-P1.7, P2.0-P2.5, P3.4, P3.5 respectively for A0-A15 (P2.5 (A13) for RB, P3.4 (A14) for RC, P3.5 (A15) for RD)

Data Lines: P0.0-P0.7 for D0-D7

Control Signals:RST, PSEN, P2.6, P2.7, P3.3, P3.6, P3.7.

Program Signals: ALE/PROG, EA/VPP.

| Mode                                      | RST | PSEN | ALE/P<br>ROG | EA/VP<br>P | P2.6 | P2.7 | P3.3 | P3.6 | P3.7 |

|-------------------------------------------|-----|------|--------------|------------|------|------|------|------|------|

| Program Code data                         | 1   | 0    | 1.           | 12.75V     | 0    | 1    | 1    | 1    | 1    |

| Verify Code data                          | 1   | 0    | 1            | 1          | 0    |      | 0    | 1    | 1    |

| Program Encryption<br>Array Address 0-3Fh | 1   | 0    | Ŀ            | 12.75V     | 0    | 1    | 1    | 0    | 1    |

| Read Signature Bytes                      | 1   | 0    | 1            | 1          | 0    |      | 0    | 0    | 0    |

| Program Lock bit 1                        | 1   | 0    | 1.1          | 12.75V     | 1    | 1    | 1    | 1    | 1    |

| Program Lock bit 2                        | 1   | 0    | Ŀ            | 12.75V     | 1    | 1    | 1    | 0    | 0    |

| Program Lock bit 3                        | 1   | 0    | IJ           | 12.75V     | 1    | 0    | 1    | 1    | 0    |

#### Table 9-2.EPROM Set-Up Modes

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 11-9. AC Parameters for a Variable Clock: derating formula

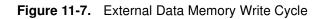

### 11.5.5 External Data Memory Write Cycle

11.5.6 External Data Memory Read Cycle

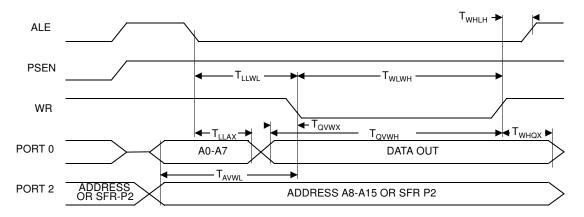

#### 11.5.15 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 signal must be changed to XTAL2 divided by two.

#### Figure 11-14. Clock Waveforms

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |  |  |  |  |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|--|--|--|--|

| TS87C51RC2-MCA   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MCB   | _             |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MCE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MIA   | _             |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MIB   | _             |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MIE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LCA   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LCB   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LCE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LIA   |               |                | OBSOLE             | IE                 |         |         |  |  |  |  |

| TS87C51RC2-LIB   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LIE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VCA   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VCB   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VCE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VIA   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VIB   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VIE   |               |                |                    |                    |         |         |  |  |  |  |

|                  |               |                |                    |                    |         |         |  |  |  |  |

| AT87C51RC2-3CSUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |  |  |  |  |

| AT87C51RC2-SLSUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |  |  |  |  |

| AT87C51RC2-RLTUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |  |  |  |  |

| AT87C51RC2-3CSUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |  |  |  |  |

| AT87C51RC2-SLSUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |  |  |  |  |

| AT87C51RC2-RLTUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |  |  |  |  |

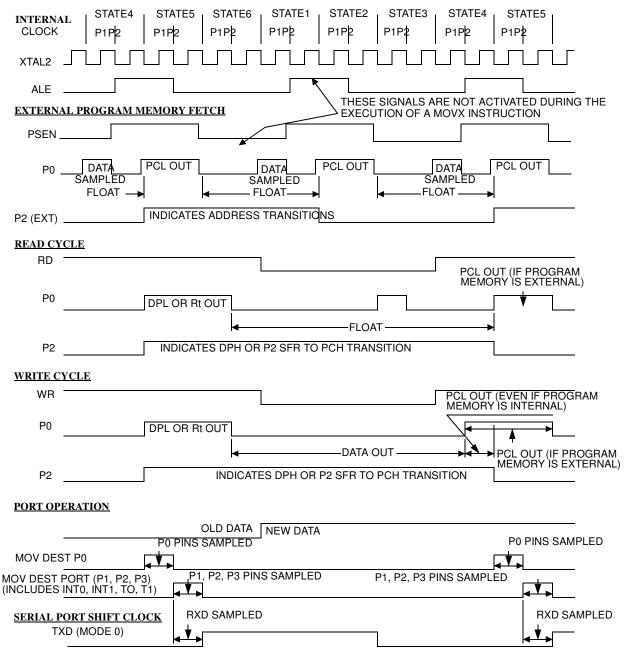

# 13. Package Drawings

## 13.1 PLCC44

|    | Ν      | 1M ·  | I NCH |       |  |

|----|--------|-------|-------|-------|--|

| A  | 4.20   | 4. 57 | . 165 | . 180 |  |

| A1 | 2, 29  | 3.04  | . 090 | . 120 |  |

| D  | 17.40  | 17.65 | . 685 | . 695 |  |

| D1 | 16.44  | 16.66 | . 647 | . 656 |  |

| D5 | 14.99  | 16.00 | . 590 | . 630 |  |

| E  | 17.40  | 17.65 | . 685 | . 695 |  |

| E1 | 16.44  | 16.66 | . 647 | . 656 |  |

| E5 | 14.99  | 16.00 | . 590 | . 630 |  |

| e  | 1.27   | BSC   | . 050 | BSC   |  |

| G  | 1.07   | 1.22  | . 042 | . 048 |  |

| н  | 1.07   | 1.42  | . 042 | .056  |  |

| J  | 0.51   | -     | . 020 | -     |  |

| К  | 0.33   | 0.53  | . 013 | . 021 |  |

| Nd | 1      | 1     | 1 1   |       |  |

| Ne | 1      | 1     | 1 1   |       |  |

| P  | KG STD | 00    |       |       |  |

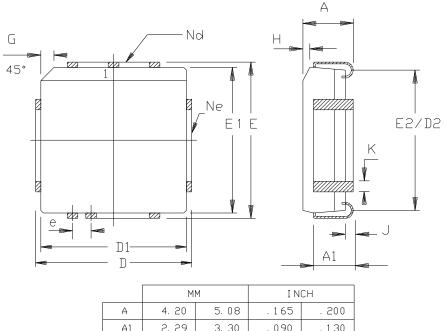

## 13.5 PLCC68

68 PINS PLCC

|    | IM     | M      | INCH  |        |  |

|----|--------|--------|-------|--------|--|

| A  | 4.20   | 5.08   | . 165 | . 200  |  |

| A1 | 2, 29  | 3.30   | . 090 | . 1 30 |  |

| D  | 25.02  | 25. 27 | . 985 | . 995  |  |

| D1 | 24.13  | 24.33  | . 950 | . 958  |  |

| D2 | 22. 61 | 23. 62 | . 890 | . 930  |  |

| E  | 25.02  | 25. 27 | . 985 | . 995  |  |

| E1 | 24.13  | 24.33  | . 950 | . 958  |  |

| E5 | 22. 61 | 23. 62 | . 890 | . 930  |  |

| e  | 1.27   | BSC    | . 050 | BSC    |  |

| G  | 1.07   | 1.22   | . 042 | . 048  |  |

| н  | 1.07   | 1.42   | . 042 | .056   |  |

| J  | 0.51   | -      | . 020 | -      |  |

| К  | 0.33   | 0.53   | . 013 | . 021  |  |

| Nd | 1      | 7      | 17    |        |  |

| Ne | 1      | 7      | 17    |        |  |

| P  | KG STD |        |       |        |  |

## 14. Datasheet Revision History

## 14.1 Changes from 4188E to 4188F

- 1. Removed TS80C51RD2 and AT80C51RD2 from "Ordering Information" on page 73.

- 2. Removed non-green part numbers from ordering information.

#### Headquarters

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com *Technical Support* Enter Product Line E-mail Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.