Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 30/20MHz                                                                   |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIL                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at87c51rc2-3csul |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

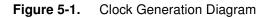

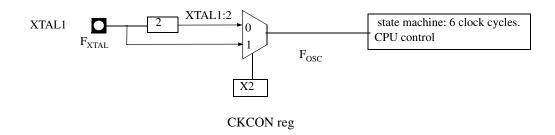

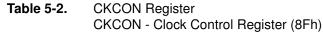

The X2 bit in the CKCON register (Table 5-2) allows to switch from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

Note: In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (UART, timers, PCA...) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. UART with 4800 baud rate will have 9600 baud rate.

| 7          | 6               | 5                               | 4                                                                               | 3               | 2                | 1        | 0 |  |  |  |  |  |

|------------|-----------------|---------------------------------|---------------------------------------------------------------------------------|-----------------|------------------|----------|---|--|--|--|--|--|

| -          | -               | -                               |                                                                                 |                 |                  |          |   |  |  |  |  |  |

| Bit Number | Bit<br>Mnemonic | Description                     | escription                                                                      |                 |                  |          |   |  |  |  |  |  |

| 7          | -               | <b>Reserved</b><br>The value re | ad from this bit                                                                | is indeterminat | e. Do not set th | nis bit. |   |  |  |  |  |  |

| 6          | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                  |          |   |  |  |  |  |  |

| 5          | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                  |          |   |  |  |  |  |  |

## 6.2 Timer 2

The timer 2 in the TS80C51RX2 is compatible with the timer 2 in the 80C52. It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2, connected in cascade. It is controlled by T2CON register (See Table 6-2) and T2MOD register (See Table 6-3). Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects  $F_{OSC}/12$  (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to be incremented by the selected input.

Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and  $CP/\overline{RL2}$  (T2CON), as described in the Atmel 8-bit Microcontroller Hardware description.

Refer to the Atmel 8-bit Microcontroller Hardware description for the description of Capture and Baud Rate Generator Modes.

In TS80C51RX2 Timer 2 includes the following enhancements:

- Auto-reload mode with up or down counter

- Programmable clock-output

### 6.2.1 Auto-reload Mode

The auto-reload mode configures timer 2 as a 16-bit timer or event counter with automatic reload. If DCEN bit in T2MOD is cleared, timer 2 behaves as in 80C52 (refer to the Atmel 8-bit Microcontroller Hardware description). If DCEN bit is set, timer 2 acts as an Up/down timer/counter as shown in Figure 6-2. In this mode the T2EX pin controls the direction of count.

When T2EX is high, timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.

When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.

The EXF2 bit toggles when timer 2 overflows or underflows according to the the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 6             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 5             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 4             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 3             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 2             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 1             | T2OE            | Timer 2 Output Enable bit<br>Clear to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |

| 0             | DCEN            | Down Counter Enable bit<br>Clear to disable timer 2 as up/down counter.<br>Set to enable timer 2 as up/down counter.         |

Reset Value = XXXX XX00b

Not bit addressable

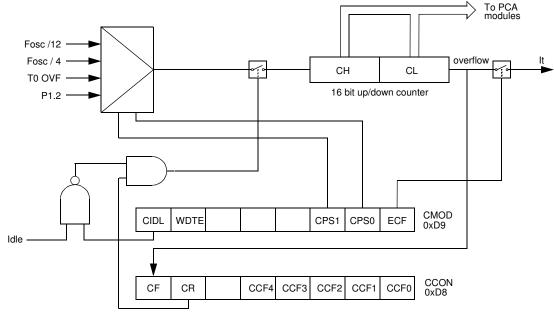

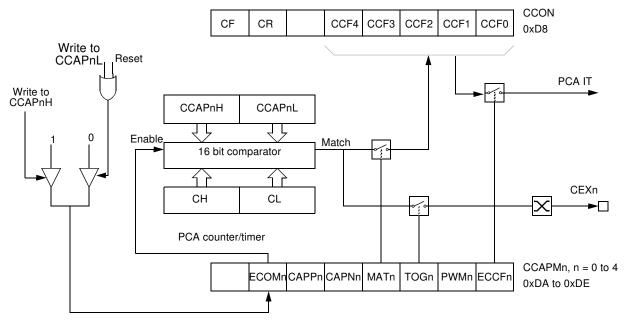

## Figure 6-4. PCA Timer/Counter

Table 6-4. CMOD: PCA Counter Mode Register

| C<br>Addr | CIDL               | WDTE       | -                                 | -                        | -                          | CPS1       | CPS0                  | ECF         |             |           |

|-----------|--------------------|------------|-----------------------------------|--------------------------|----------------------------|------------|-----------------------|-------------|-------------|-----------|

|           | Re                 | eset value | 0                                 | 0                        | Х                          | Х          | х                     | 0           | 0           | 0         |

| Symbol    | Functio            | n          |                                   |                          |                            |            |                       |             |             |           |

| CIDL      |                    |            | ol: CIDL = 0 p<br>s it to be gate | 0                        |                            | ounter to  | continue f            | functioning | g during id | le Mode.  |

| WDTE      | Watchdo<br>enables | •          | nable: WDTE                       | E = 0 disab              | les Watch                  | dog Timer  | function (            | on PCA M    | odule 4. W  | /DTE = 1  |

| -         | Not impl           | emented,   | reserved for                      | future use               | . (1)                      |            |                       |             |             |           |

| CPS1      | PCA Co             | unt Pulse  | Select bit 1.                     |                          |                            |            |                       |             |             |           |

| CPS0      | PCA Co             | unt Pulse  | Select bit 0.                     |                          |                            |            |                       |             |             |           |

|           | CPS1               | CPS0       | Selected PC                       | A input. <sup>(2)</sup>  |                            |            |                       |             |             |           |

|           | 0                  | 0          | Internal cloc                     | k f <sub>osc</sub> /12(0 | Or f <sub>osc</sub> /6 in  | X2 Mode    | ).                    |             |             |           |

|           | 0                  | 1          | Internal cloc                     | k f <sub>osc</sub> /4(O  | r f <sub>osc</sub> /2 in X | K2 Mode).  |                       |             |             |           |

|           | 1                  | 0          | Timer 0 Ove                       | rflow                    |                            |            |                       |             |             |           |

|           | 1                  | 1          | External cloc                     | k at ECI/P               | 91.2 pin (m                | nax rate = | f <sub>osc</sub> / 8) |             |             |           |

| ECF       |                    |            | ter Overflow that function        |                          | ECF = 1 e                  | nables CF  | bit in CC             | ON to ger   | nerate an i | nterrupt. |

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

2.  $f_{osc} = oscillator frequency$

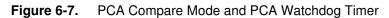

**The CMOD SFR** includes three additional bits associated with the PCA (See Figure 6-4 and Table 6-4).

\* Only for Module 4

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

## 6.3.3 High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (See Figure 6-8).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

Figure 6-8. PCA High Speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

### 6.3.4 Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 6-9 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

```

Slave C:SADDR1111 0010b

<u>SADEN1111 1101b</u>

Given1111 00X1b

```

The SADEN byte is selected so that each slave may be addressed separately.

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g. 1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

#### 6.4.4 Broadcast Address

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR0101 0110b SADEN1111 1100b Broadcast =SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

```

Slave A:SADDR1111 0001b

SADEN1111 1010b

Broadcast1111 1X11b,

Slave B:SADDR1111 0011b

SADEN1111 1001b

Broadcast1111 1X11B,

Slave C:SADDR=1111 0010b

SADEN1111 1101b

Broadcast1111 1111b

```

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

### 6.4.5 Reset Addresses

On reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

## 6.6 Idle Mode

An instruction that sets PCON.0 causes that to be the last instruction executed before going into the Idle mode. In the Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during Idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high levels.

There are two ways to terminate the Idle. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.

The flag bits GF0 and GF1 can be used to give an indication if an interrupt occured during normal operation or during an Idle. For example, an instruction that activates Idle can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt service routine can examine the flag bits.

The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.

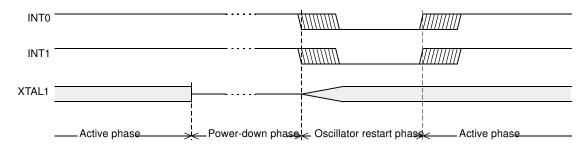

## 6.7 Power-down Mode

To save maximum power, a power-down mode can be invoked by software (Refer to Table 6-15, PCON register).

In power-down mode, the oscillator is stopped and the instruction that invoked power-down mode is the last instruction executed. The internal RAM and SFRs retain their value until the power-down mode is terminated.  $V_{CC}$  can be lowered to save further power. Either a hardware reset or an external interrupt can cause an exit from power-down. To properly terminate power-down, the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize.

Only external interrupts INT0 and INT1 are useful to exit from power-down. For that, interrupt must be enabled and configured as level or edge sensitive interrupt input.

Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 6-14. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power down exit will be completed when the first input will be released. In this case the higher priority interrupt service routine is executed.

Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put TS80C51Rx2 into power-down mode.

Figure 6-14. Power-Down Exit Waveform

Exit from power-down by reset redefines all the SFRs, exit from power-down by external interrupt does no affect the SFRs.

Exit from power-down by either reset or external interrupt does not affect the internal RAM content.

Note: If idle mode is activated with power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

**Table 6-20.** The state of ports during idle and power-down mode

| Mode       | Program<br>Memory | ALE | PSEN | PORT0      | PORT1     | PORT2     | PORT3     |

|------------|-------------------|-----|------|------------|-----------|-----------|-----------|

| Idle       | Internal          | 1   | 1    | Port Data* | Port Data | Port Data | Port Data |

| Idle       | External          | 1   | 1    | Floating   | Port Data | Address   | Port Data |

| Power-down | Internal          | 0   | 0    | Port Data* | Port Data | Port Data | Port Data |

| Power-down | External          | 0   | 0    | Floating   | Port Data | Port Data | Port Data |

\* Port 0 can force a "zero" level. A "one" will leave port floating.

# 8. TS83C51RB2/RC2/RD2 ROM

# 8.1 ROM Structure

The TS83C51RB2/RC2/RD2 ROM memory is divided in three different arrays:

- the code array:16/32/64 Kbytes.

- the encryption array:64 bytes.

- the signature array:4 bytes.

# 8.2 ROM Lock System

The program Lock system, when programmed, protects the on-chip program against software piracy.

# 8.2.1 8.2.1 Encryption Array

Within the ROM array are 64 bytes of encryption array that are initially unprogrammed (all FF's). Every time a byte is addressed during program verify, 6 address lines are used to select a byte of the encryption array. This byte is then exclusive-NOR'ed (XNOR) with the code byte, creating an encrypted verify byte. The algorithm, with the encryption array in the unprogrammed state, will return the code in its original, unmodified form.

When using the encryption array, one important factor needs to be considered. If a byte has the value FFh, verifying the byte will produce the encryption byte value. If a large block (>64 bytes) of code is left unprogrammed, a verification routine will display the content of the encryption array. For this reason all the unused code bytes should be programmed with random values. This will ensure program protection.

# 8.2.2 Program Lock Bits

The lock bits when programmed according to Table 8-1. will provide different level of protection for the on-chip code and data.

|                   | Program L | ock Bits |     |                                                                                                                                                                                                       |  |  |  |  |

|-------------------|-----------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Security<br>level | LB1       | LB2      | LB3 | Protection Description                                                                                                                                                                                |  |  |  |  |

| 1                 | U         | U        | U   | No program lock features enabled. Code verify will still be encrypted<br>by the encryption array if programmed. MOVC instruction executed<br>from external program memory returns non encrypted data. |  |  |  |  |

| 2                 | Р         | U        | U   | MOVC instruction executed from external program memory are disabled from fetching code bytes from internal memory, EA is sampled and latched on reset.                                                |  |  |  |  |

| 3                 | U         | Р        | U   | Same as level 1+ Verify disable.<br>This security level is only available for 51RDX2 devices.                                                                                                         |  |  |  |  |

| Table 8-1. | Program Lock bits |

|------------|-------------------|

|            |                   |

U: unprogrammed P: programmed

## 8.2.3 Signature bytes

The TS83C51RB2/RC2/RD2 contains 4 factory programmed signatures bytes. To read these bytes, perform the process described in section 8.3.

## 11.4 DC Parameters for Low Voltage

TA = 0°C to +70°C; V<sub>SS</sub> = 0 V; V<sub>CC</sub> = 2.7 V to 5.5 V  $\pm$  10%; F = 0 to 30 MHz. TA = -40°C to +85°C; V<sub>SS</sub> = 0 V; V<sub>CC</sub> = 2.7 V to 5.5 V  $\pm$  10%; F = 0 to 30 MHz.

Table 11-2.

DC Parameters for Low Voltage

| Symbol                            | Parameter                                                           | Min                       | Тур                                    | Мах                                                | Unit | Test Conditions                                                                                      |

|-----------------------------------|---------------------------------------------------------------------|---------------------------|----------------------------------------|----------------------------------------------------|------|------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                                   | -0.5                      |                                        | 0.2 V <sub>CC</sub> - 0.1                          | V    |                                                                                                      |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                                | 0.2 V <sub>CC</sub> + 0.9 |                                        | V <sub>CC</sub> + 0.5                              | V    |                                                                                                      |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                                      | 0.7 V <sub>CC</sub>       |                                        | V <sub>CC</sub> + 0.5                              | V    |                                                                                                      |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3, 4, 5 <sup>(6)</sup>              |                           |                                        | 0.45                                               | V    | I <sub>OL</sub> = 0.8 mA <sup>(4)</sup>                                                              |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0, ALE, PSEN (6)                           |                           |                                        | 0.45                                               | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup>                                                              |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3, 4, 5                            | 0.9 V <sub>CC</sub>       |                                        |                                                    | V    | I <sub>OH</sub> = -10 μA                                                                             |

| V <sub>OH1</sub>                  | Output High Voltage, port 0, ALE, PSEN                              | 0.9 V <sub>CC</sub>       |                                        |                                                    | V    | I <sub>OH</sub> = -40 μA                                                                             |

| I                                 | Logical 0 Input Current ports 1, 2, 3, 4, 5                         |                           |                                        | -50                                                | μA   | Vin = 0.45 V                                                                                         |

| ILI                               | Input Leakage Current                                               |                           |                                        | ±10                                                | μA   | 0.45 V < Vin < V <sub>CC</sub>                                                                       |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3, 4, 5              |                           |                                        | -650                                               | μA   | Vin = 2.0 V                                                                                          |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                               | 50                        | 90 <sup>(5)</sup>                      | 200                                                | kΩ   |                                                                                                      |

| CIO                               | Capacitance of I/O Buffer                                           |                           |                                        | 10                                                 | pF   | Fc = 1 MHz<br>TA = 25°C                                                                              |

| I <sub>PD</sub>                   | Power-down Current                                                  |                           | 20 <sup>(5)</sup><br>10 <sup>(5)</sup> | 50<br>30                                           | μΑ   | $V_{CC} = 2.0 \text{ V to } 5.5 \text{ V}^{(3)}$<br>$V_{CC} = 2.0 \text{ V to } 3.3 \text{ V}^{(3)}$ |

| I <sub>PD</sub>                   | Power-down Current (Only for TS87C51RD2<br>S287-xxx Very Low power) |                           | 2 <sup>(5)</sup>                       | 15                                                 | μΑ   | $2.0 \text{ V} < \text{V}_{\text{CC}} < 3.6 \text{ V}^{(3)}$                                         |

| I <sub>cc</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: (7)                   |                           |                                        | 1 + 0.2 Freq<br>(MHz)<br>@12MHz 3.4<br>@16MHz 4.2  | mA   | $V_{CC} = 3.3 V^{(1)}$                                                                               |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: (7)                   |                           |                                        | 1 + 0.3 Freq<br>(MHz)<br>@12MHz 4.6<br>@16MHz 5.8  | mA   | $V_{CC} = 3.3 V^{(8)}$                                                                               |

| I <sub>CC</sub><br>idle           | Power Supply Current Maximum values, X1 mode: (7)                   |                           |                                        | 0.15 Freq<br>(MHz) + 0.2<br>@12MHz 2<br>@16MHz 2.6 | mA   | $V_{CC} = 3.3 V^{(2)}$                                                                               |

Notes: 1.  $I_{CC}$  under reset is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 11-5.),  $V_{IL} = V_{SS} + 0.5$  V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used...

2. Idle I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V, V<sub>IH</sub> = V<sub>CC</sub> - 0.5 V; XTAL2 N.C; Port 0 = V<sub>CC</sub>;  $\overline{EA}$  = RST = V<sub>SS</sub> (see Figure 11-3.).

Power-down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 11-4.).

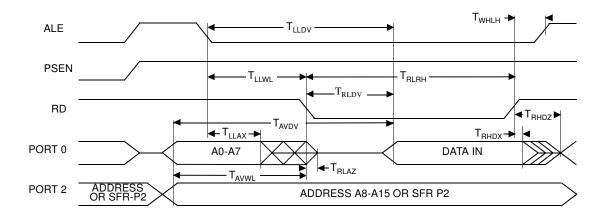

#### **External Data Memory Characteristics** 11.5.4

| Symbol            | Parameter                   |

|-------------------|-----------------------------|

| T <sub>RLRH</sub> | RD Pulse Width              |

| T <sub>WLWH</sub> | WR Pulse Width              |

| T <sub>RLDV</sub> | RD to Valid Data In         |

| T <sub>RHDX</sub> | Data Hold After RD          |

| T <sub>RHDZ</sub> | Data Float After RD         |

| T <sub>LLDV</sub> | ALE to Valid Data In        |

| T <sub>AVDV</sub> | Address to Valid Data In    |

| T <sub>LLWL</sub> | ALE to WR or RD             |

| T <sub>AVWL</sub> | Address to WR or RD         |

| T <sub>QVWX</sub> | Data Valid to WR Transition |

| T <sub>QVWH</sub> | Data set-up to WR High      |

| T <sub>WHQX</sub> | Data Hold After WR          |

| T <sub>RLAZ</sub> | RD Low to Address Float     |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |

Table 11-8.

AC Parameters for a Fix Clock

| Speed             | Speed -M<br>40 MHz |     | -V<br>X2 mode<br>30 MHz<br>60 MHz equiv. |     | -V<br>standard mode 40<br>MHz |     | -L<br>X2 mode<br>20 MHz<br>40 MHz equiv. |     | -L<br>standard mode<br>30 MHz |     | Units |

|-------------------|--------------------|-----|------------------------------------------|-----|-------------------------------|-----|------------------------------------------|-----|-------------------------------|-----|-------|

| Symbol            | Min                | Max | Min                                      | Max | Min                           | Max | Min                                      | Max | Min                           | Max |       |

| T <sub>RLRH</sub> | 130                |     | 85                                       |     | 135                           |     | 125                                      |     | 175                           |     | ns    |

| T <sub>WLWH</sub> | 130                |     | 85                                       |     | 135                           |     | 125                                      |     | 175                           |     | ns    |

| T <sub>RLDV</sub> |                    | 100 |                                          | 60  |                               | 102 |                                          | 95  |                               | 137 | ns    |

| T <sub>RHDX</sub> | 0                  |     | 0                                        |     | 0                             |     | 0                                        |     | 0                             |     | ns    |

| T <sub>RHDZ</sub> |                    | 30  |                                          | 18  |                               | 35  |                                          | 25  |                               | 42  | ns    |

| T <sub>LLDV</sub> |                    | 160 |                                          | 98  |                               | 165 |                                          | 155 |                               | 222 | ns    |

| T <sub>AVDV</sub> |                    | 165 |                                          | 100 |                               | 175 |                                          | 160 |                               | 235 | ns    |

| T <sub>LLWL</sub> | 50                 | 100 | 30                                       | 70  | 55                            | 95  | 45                                       | 105 | 70                            | 130 | ns    |

| T <sub>AVWL</sub> | 75                 |     | 47                                       |     | 80                            |     | 70                                       |     | 103                           |     | ns    |

| T <sub>QVWX</sub> | 10                 |     | 7                                        |     | 15                            |     | 5                                        |     | 13                            |     | ns    |

| Τ <sub>QVWH</sub> | 160                |     | 107                                      |     | 165                           |     | 155                                      |     | 213                           |     | ns    |

| T <sub>WHQX</sub> | 15                 |     | 9                                        |     | 17                            |     | 10                                       |     | 18                            |     | ns    |

| T <sub>RLAZ</sub> |                    | 0   |                                          | 0   |                               | 0   |                                          | 0   |                               | 0   | ns    |

| T <sub>WHLH</sub> | 10                 | 40  | 7                                        | 27  | 15                            | 35  | 5                                        | 45  | 13                            | 53  | ns    |

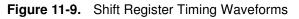

## 11.5.7 Serial Port Timing - Shift Register Mode

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

Table 11-10.

AC Parameters for a Fix Clock

| Speed             |     | M<br>MHz | X2 n | MHz | -V<br>standard mode 4<br>MHz |     | X2 n<br>20 l | -L<br>X2 mode<br>20 MHz<br>40 MHz equiv. |     | L<br>d mode<br>MHz | Units |

|-------------------|-----|----------|------|-----|------------------------------|-----|--------------|------------------------------------------|-----|--------------------|-------|

| Symbol            | Min | Max      | Min  | Max | Min                          | Max | Min          | Max                                      | Min | Max                |       |

| T <sub>XLXL</sub> | 300 |          | 200  |     | 300                          |     | 300          |                                          | 400 |                    | ns    |

| T <sub>QVHX</sub> | 200 |          | 117  |     | 200                          |     | 200          |                                          | 283 |                    | ns    |

| T <sub>XHQX</sub> | 30  |          | 13   |     | 30                           |     | 30           |                                          | 47  |                    | ns    |

| T <sub>XHDX</sub> | 0   |          | 0    |     | 0                            |     | 0            |                                          | 0   |                    | ns    |

| T <sub>XHDV</sub> |     | 117      |      | 34  |                              | 117 |              | 117                                      |     | 200                | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock | -M  | -V  | -L  | Units |

|-------------------|------|-------------------|----------|-----|-----|-----|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |     |     |     | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50  | 50  | 50  | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20  | 20  | 20  | ns    |

| T <sub>XHDX</sub> | Min  | x                 | х        | 0   | 0   | 0   | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133 | 133 | 133 | ns    |

Table 11-11. AC Parameters for a Variable Clock: derating formula

# 11.5.8 Shift Register Timing Waveforms

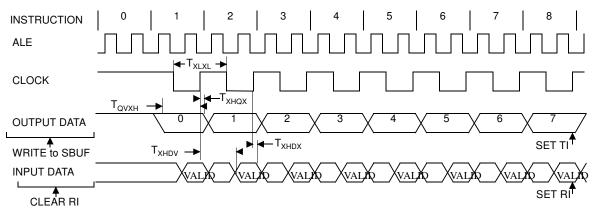

## 11.5.9 EPROM Programming and Verification Characteristics

TA = 21°C to 27°C; V<sub>SS</sub> = 0V; V<sub>CC</sub> = 5V  $\pm$  10% while programming. V<sub>CC</sub> = operating range while

| Symbol              | Parameter                         | Min                  | Max                  | Units |

|---------------------|-----------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage        | 12.5                 | 13                   | V     |

| I <sub>PP</sub>     | Programming Supply Current        |                      | 75                   | mA    |

| 1/T <sub>CLCL</sub> | Oscillator Frquency               | 4                    | 6                    | MHz   |

| T <sub>AVGL</sub>   | Address Setup to PROG Low         | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHAX</sub>   | Adress Hold after PROG            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>DVGL</sub>   | Data Setup to PROG Low            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHDX</sub>   | Data Hold after PROG              | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>EHSH</sub>   | (Enable) High to V <sub>PP</sub>  | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low | 10                   |                      | μs    |

| T <sub>GHSL</sub>   | V <sub>PP</sub> Hold after PROG   | 10                   |                      | μs    |

| T <sub>GLGH</sub>   | PROG Width                        | 90                   | 110                  | μs    |

| T <sub>AVQV</sub>   | Address to Valid Data             |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>ELQV</sub>   | ENABLE Low to Data Valid          |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>EHQZ</sub>   | Data Float after ENABLE           | 0                    | 48 T <sub>CLCL</sub> |       |

verifying

## 11.5.10 EPROM Programming and Verification Waveforms

Figure 11-10. EPROM Programming and Verification Waveforms

\* 8KB: up to P2.4, 16KB: up to P2.5, 32KB: up to P3.4, 64KB: up to P3.5

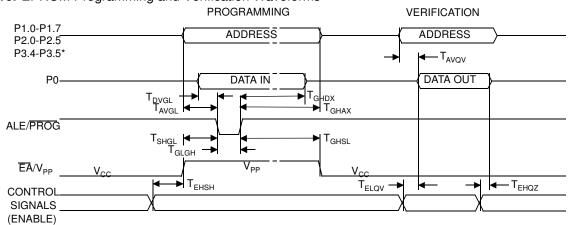

### 11.5.15 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 signal must be changed to XTAL2 divided by two.

### Figure 11-14. Clock Waveforms

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS87C51RC2-MCA   |               |                |                    |                    |         |         |

| TS87C51RC2-MCB   | _             |                |                    |                    |         |         |

| TS87C51RC2-MCE   |               |                |                    |                    |         |         |

| TS87C51RC2-MIA   | _             |                |                    |                    |         |         |

| TS87C51RC2-MIB   | _             |                |                    |                    |         |         |

| TS87C51RC2-MIE   |               |                |                    |                    |         |         |

| TS87C51RC2-LCA   |               |                |                    |                    |         |         |

| TS87C51RC2-LCB   |               |                |                    |                    |         |         |

| TS87C51RC2-LCE   |               |                |                    | <b>T</b> E         |         |         |

| TS87C51RC2-LIA   |               |                | OBSOLE             | IE                 |         |         |

| TS87C51RC2-LIB   |               |                |                    |                    |         |         |

| TS87C51RC2-LIE   |               |                |                    |                    |         |         |

| TS87C51RC2-VCA   |               |                |                    |                    |         |         |

| TS87C51RC2-VCB   |               |                |                    |                    |         |         |

| TS87C51RC2-VCE   |               |                |                    |                    |         |         |

| TS87C51RC2-VIA   |               |                |                    |                    |         |         |

| TS87C51RC2-VIB   |               |                |                    |                    |         |         |

| TS87C51RC2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT87C51RC2-3CSUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RC2-SLSUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RC2-RLTUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT87C51RC2-3CSUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RC2-SLSUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RC2-RLTUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS83C51RB2-MCA   |               |                |                    | •                  |         |         |

| TS83C51RB2-MCB   |               |                |                    |                    |         |         |

| TS83C51RB2-MCE   |               |                |                    |                    |         |         |

| TS83C51RB2-MIA   |               |                |                    |                    |         |         |

| TS83C51RB2-MIB   |               |                |                    |                    |         |         |

| TS83C51RB2-MIE   |               |                |                    |                    |         |         |

| TS83C51RB2-LCA   |               |                |                    |                    |         |         |

| TS83C51RB2-LCB   |               |                |                    |                    |         |         |

| TS83C51RB2-LCE   |               |                |                    | TE                 |         |         |

| TS83C51RB2-LIA   |               |                | OBSOLE             |                    |         |         |

| TS83C51RB2-LIB   |               |                |                    |                    |         |         |

| TS83C51RB2-LIE   |               |                |                    |                    |         |         |

| TS83C51RB2-VCA   |               |                |                    |                    |         |         |

| TS83C51RB2-VCB   |               |                |                    |                    |         |         |

| TS83C51RB2-VCE   |               |                |                    |                    |         |         |

| TS83C51RB2-VIA   |               |                |                    |                    |         |         |

| TS83C51RB2-VIB   |               |                |                    |                    |         |         |

| TS83C51RB2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT83C51RB2-3CSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RB2-SLSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RB2-RLTUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RB2-3CSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RB2-SLSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RB2-RLTUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS83C51RC2-MCA   |               |                |                    | L                  | 1       |         |

| TS83C51RC2-MCB   |               |                |                    |                    |         |         |

| TS83C51RC2-MCE   |               |                |                    |                    |         |         |

| TS83C51RC2-MIA   |               |                |                    |                    |         |         |

| TS83C51RC2-MIB   |               |                |                    |                    |         |         |

| TS83C51RC2-MIE   |               |                |                    |                    |         |         |

| TS83C51RC2-LCA   |               |                |                    |                    |         |         |

| TS83C51RC2-LCB   |               |                |                    |                    |         |         |

| TS83C51RC2-LCE   |               |                |                    | TE                 |         |         |

| TS83C51RC2-LIA   |               |                | OBSOLE             |                    |         |         |

| TS83C51RC2-LIB   |               |                |                    |                    |         |         |

| TS83C51RC2-LIE   |               |                |                    |                    |         |         |

| TS83C51RC2-VCA   |               |                |                    |                    |         |         |

| TS83C51RC2-VCB   |               |                |                    |                    |         |         |

| TS83C51RC2-VCE   |               |                |                    |                    |         |         |

| TS83C51RC2-VIA   |               |                |                    |                    |         |         |

| TS83C51RC2-VIB   |               |                |                    |                    |         |         |

| TS83C51RC2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT83C51RC2-3CSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RC2-SLSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RC2-RLTUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RC2-3CSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RC2-SLSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RC2-RLTUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS83C51RD2-MCA   |               | •              | 1                  | •                  | •       | •       |

| TS83C51RD2-MCB   |               |                |                    |                    |         |         |

| TS83C51RD2-MCE   |               |                |                    |                    |         |         |

| TS83C51RD2-MIA   |               |                |                    |                    |         |         |

| TS83C51RD2-MIB   |               |                |                    |                    |         |         |

| TS83C51RD2-MIE   |               |                |                    |                    |         |         |

| TS83C51RD2-LCB   |               |                |                    |                    |         |         |

| TS83C51RD2-LCE   |               |                |                    |                    |         |         |

| TS83C51RD2-LIA   |               |                | OBSOLE             | TE                 |         |         |

| TS83C51RD2-LIB   |               |                |                    |                    |         |         |

| TS83C51RD2-LIE   |               |                |                    |                    |         |         |

| TS83C51RD2-VCA   |               |                |                    |                    |         |         |

| TS83C51RD2-VCB   |               |                |                    |                    |         |         |

| TS83C51RD2-VCE   |               |                |                    |                    |         |         |

| TS83C51RD2-VIA   |               |                |                    |                    |         |         |

| TS83C51RD2-VIB   |               |                |                    |                    |         |         |

| TS83C51RD2-VIE   |               |                |                    |                    |         |         |

|                  | · ·           |                |                    |                    |         |         |

| AT83C51RD2-3CSUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RD2-SLSUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RD2-RLTUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RD2-3CSUL | ROM 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RD2-SLSUL | ROM 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RD2-RLTUL | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (30 MHz X2) | PDIL40  | Stick   |