Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Obsolete                                                    |

| Core Processor             | 80C51                                                       |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 30/20MHz                                                    |

| Connectivity               | UART/USART                                                  |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 32                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | OTP                                                         |

| EEPROM Size                | -                                                           |

| RAM Size                   | 512 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 44-LCC (J-Lead)                                             |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at87c51rc2-slsul |

facilitates multiprocessor communication (EUART) and an X2 speed improvement mechanism.

The fully static design of the TS80C51Rx2 allows to reduce system power consumption by bringing the clock frequency down to any value, even DC, without loss of data.

The TS80C51Rx2 has 2 software-selectable modes of reduced activity for further reduction in power consumption. In the idle mode the CPU is frozen while the timers, the serial port and the interrupt system are still operating. In the power-down mode the RAM is saved and all other functions are inoperative.

| PDIL40<br>PLCC44<br>VQFP44 1.4 | ROM (bytes) | EPROM (bytes) | XRAM (bytes) | TOTAL RAM<br>(bytes) | I/O |

|--------------------------------|-------------|---------------|--------------|----------------------|-----|

| TS80C51RA2                     | 0           | 0             | 256          | 512                  | 32  |

| TS80C51RD2                     | 0           | 0             | 768          | 1024                 | 32  |

| TS83C51RB2                     | 16k         | 0             | 256          | 512                  | 32  |

| TS83C51RC2                     | 32k         | 0             | 256          | 512                  | 32  |

| TS83C51RD2                     | 64k         | 0             | 768          | 1024                 | 32  |

| TS87C51RB2                     | 0           | 16k           | 256          | 512                  | 32  |

| TS87C51RC2                     | 0           | 32k           | 256          | 512                  | 32  |

| TS87C51RD2                     | 0           | 64k           | 768          | 1024                 | 32  |

| PLCC68<br>VQFP64 1.4 | ROM (bytes) | EPROM (bytes) | XRAM (bytes) | TOTAL RAM<br>(bytes) | I/O |

|----------------------|-------------|---------------|--------------|----------------------|-----|

| TS80C51RD2           | 0           | 0             | 768          | 1024                 | 48  |

| TS83C51RD2           | 64k         | 0             | 768          | 1024                 | 48  |

| TS87C51RD2           | 0           | 64k           | 768          | 1024                 | 48  |

### 5.2 TS80C51Rx2 Enhanced Features

In comparison to the original 80C52, the TS8xC51Rx2 implements some new features, which are:

- The X2 option.

- The Dual Data Pointer.

- The extended RAM.

- The Programmable Counter Array (PCA).

- · The Watchdog.

- The 4 level interrupt priority system.

- · The power-off flag.

- · The ONCE mode.

- The ALE disabling.

- Some enhanced features are also located in the UART and the timer 2.

### 5.3 X2 Feature

The TS80C51Rx2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divides frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Saves power consumption while keeping same CPU power (oscillator power saving).

- Saves power consumption by dividing dynamically operating frequency by 2 in operating and idle modes.

- Increases CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

### 5.3.1 Description

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 5-1 shows the clock generation block diagram. X2 bit is validated on XTAL1÷2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 5-2 shows the mode switching waveforms.

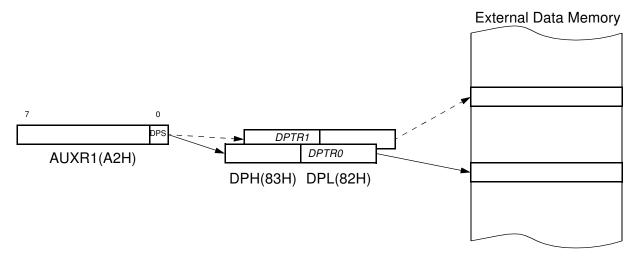

## 5.4 Dual Data Pointer Register

The additional data pointer can be used to speed up code execution and reduce code size in a number of ways.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1/bit0 (Table 5-3) that allows the program code to switch between them (Refer to Figure 5-3).

Figure 5-3. Use of Dual Pointer

Table 5-3. AUXR1: Auxiliary Register 1

ALIVDA

| Address 0A2 | Н           | - | - | - | - | GF3 | - | - | DPS |

|-------------|-------------|---|---|---|---|-----|---|---|-----|

|             | Reset value | Х | Х | Х | Х | 0   | Х | Х | 0   |

| Symbol      | Function    |   |   |   |   |     |   |   |     |

| Symbol | Function                                                 | Function                                     |  |  |  |  |  |

|--------|----------------------------------------------------------|----------------------------------------------|--|--|--|--|--|

| -      | Not implemente                                           | Not implemented, reserved for future use (1) |  |  |  |  |  |

| DPS    | Data Pointer Se                                          | Data Pointer Selection.                      |  |  |  |  |  |

|        | DPS                                                      | Operating Mode                               |  |  |  |  |  |

|        | 0                                                        | DPTR0 Selected                               |  |  |  |  |  |

|        | 1                                                        | DPTR1 Selected                               |  |  |  |  |  |

| GF3    | This bit is a general purpose user flag <sup>(2)</sup> . |                                              |  |  |  |  |  |

User software should not write 1s to reserved bits. These bits may be used in future 8051 family

products to invoke new feature. In that case, the reset value of the new bit will be 0, and its

active value will be 1. The value read from a reserved bit is indeterminate.

GF3 will not be available on first version of the RC devices.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                        |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | TF2             | Timer 2 overflow Flag  Must be cleared by software.  Set by hardware on timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                                |

| 6             | EXF2            | Timer 2 External Flag Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2=1. When set, causes the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is enabled. Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter mode (DCEN = 1) |

| 5             | RCLK            | Receive Clock bit Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3. Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                                      |

| 4             | TCLK            | Transmit Clock bit Clear to use timer 1 overflow as transmit clock for serial port in mode 1 or 3. Set to use timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                                                                                                                   |

| 3             | EXEN2           | Timer 2 External Enable bit Clear to ignore events on T2EX pin for timer 2 operation. Set to cause a capture or reload when a negative transition on T2EX pin is detected, if timer 2 is not used to clock the serial port.                                                                                        |

| 2             | TR2             | Timer 2 Run control bit Clear to turn off timer 2. Set to turn on timer 2.                                                                                                                                                                                                                                         |

| 1             | C/T2#           | Timer/Counter 2 select bit Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ). Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for clock out mode.                                                                                               |

| 0             | CP/RL2#         | Timer 2 Capture/Reload bit  If RCLK=1 or TCLK=1, CP/RL2# is ignored and timer is forced to auto-reload on timer 2 overflow.  Clear to auto-reload on timer 2 overflows or negative transitions on T2EX pin if EXEN2=1.  Set to capture on negative transitions on T2EX pin if EXEN2=1.                             |

Reset Value = 0000 0000b

Bit addressable

| Table 6-3. | T2MOD Register |

|------------|----------------|

|------------|----------------|

T2MOD - Timer 2 Mode Control Register (C9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|---|---|---|---|---|---|------|------|

| - | - | - | - | - | - | T2OE | DCEN |

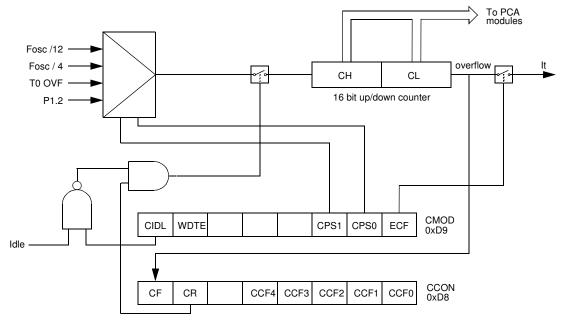

Figure 6-4. PCA Timer/Counter

Table 6-4. CMOD: PCA Counter Mode Register

| CMOD<br>Address 0D9H |             | CIDL | WDTE | - | - | - | CPS1 | CPS0 | ECF |  |

|----------------------|-------------|------|------|---|---|---|------|------|-----|--|

|                      | Reset value | 0    | 0    | Х | Х | Х | 0    | 0    | 0   |  |

| Symbol | Functio                                                                                                                               | Function                                                             |                                                                                                                     |  |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CIDL   |                                                                                                                                       |                                                                      | rol: CIDL = 0 programs the PCA Counter to continue functioning during idle Mode. ns it to be gated off during idle. |  |  |  |  |

| WDTE   | Watchdo<br>enables                                                                                                                    | •                                                                    | Enable: WDTE = 0 disables Watchdog Timer function on PCA Module 4. WDTE = 1                                         |  |  |  |  |

| -      | Not impl                                                                                                                              | emented                                                              | , reserved for future use. (1)                                                                                      |  |  |  |  |

| CPS1   | PCA Co                                                                                                                                | unt Pulse                                                            | Select bit 1.                                                                                                       |  |  |  |  |

| CPS0   | PCA Co                                                                                                                                | unt Pulse                                                            | Select bit 0.                                                                                                       |  |  |  |  |

|        | CPS1                                                                                                                                  | CPS0                                                                 | Selected PCA input. (2)                                                                                             |  |  |  |  |

|        | 0                                                                                                                                     | 0                                                                    | Internal clock f <sub>osc</sub> /12 ( Or f <sub>osc</sub> /6 in X2 Mode).                                           |  |  |  |  |

|        | 0                                                                                                                                     | 1                                                                    | Internal clock f <sub>osc</sub> /4 ( Or f <sub>osc</sub> /2 in X2 Mode).                                            |  |  |  |  |

|        | 1                                                                                                                                     | 0                                                                    | Timer 0 Overflow                                                                                                    |  |  |  |  |

|        | 1                                                                                                                                     | 1 1 External clock at ECI/P1.2 pin (max rate = f <sub>osc</sub> / 8) |                                                                                                                     |  |  |  |  |

| ECF    | PCA Enable Counter Overflow interrupt: ECF = 1 enables CF bit in CCON to generate an interrupt. ECF = 0 disables that function of CF. |                                                                      |                                                                                                                     |  |  |  |  |

- 1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

- 2.  $f_{osc} = oscillator frequency$

**The CMOD SFR** includes three additional bits associated with the PCA (See Figure 6-4 and Table 6-4).

- The CIDL bit which allows the PCA to stop during idle mode.

- The WDTE bit which enables or disables the watchdog function on module 4.

- The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

**The CCON SFR** contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 6-5).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

Table 6-5. CCON: PCA Counter Control Register

| CCON<br>Address 0D8H |             | CF | CR | - | CCF4 | CCF3 | CCF2 | CCF1 | CCF0 |

|----------------------|-------------|----|----|---|------|------|------|------|------|

|                      | Reset value | 0  | 0  | Х | 0    | 0    | 0    | 0    | 0    |

| Symbol | Function                                                                                                                                                                                                   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CF     | PCA Counter Overflow flag. Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is set. CF may be set by either hardware or software but can only be cleared by software. |

| CR     | PCA Counter Run control bit. Set by software to turn the PCA counter on. Must be cleared by software to turn the PCA counter off.                                                                          |

| -      | Not implemented, reserved for future use. (1)                                                                                                                                                              |

| CCF4   | PCA Module 4 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

| CCF3   | PCA Module 3 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

| CCF2   | PCA Module 2 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

| CCF1   | PCA Module 1 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

| CCF0   | PCA Module 0 interrupt flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

User software should not write 1s to reserved bits. These bits may be used in future 8051 family

products to invoke new features. In that case, the reset or inactive value of the new bit will be 0,

and its active value will be 1. The value read from a reserved bit is indeterminate.

The watchdog timer function is implemented in module 4 (See Figure 6-7).

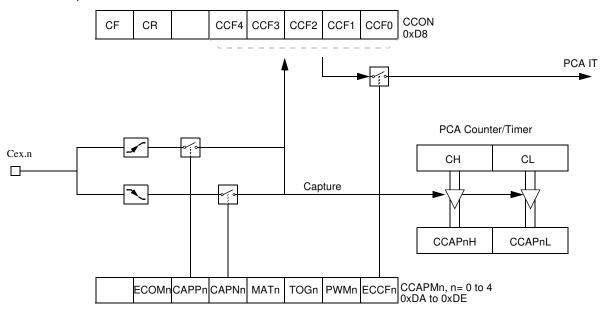

The PCA interrupt system is shown in Figure 6-5.

Figure 6-6. PCA Capture Mode

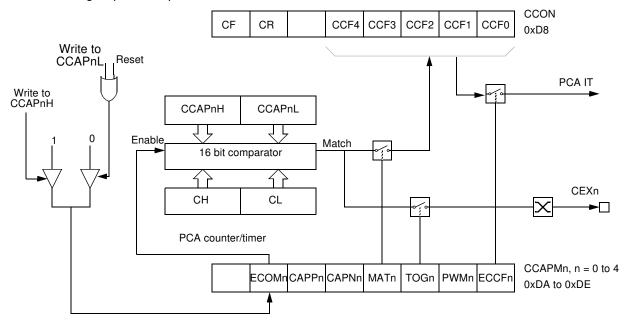

## 6.3.2 16-bit Software Timer/ Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (See Figure 6-7).

CCON CCF2 0xD8 CF CR CCF4 CCF3 CCF1 CCF0 Write to CCAPnL Reset PCA IT Write to **CCAPnH CCAPnH CCAPnL** Enable 0 Match 16 bit comparator RESET \* СН CL PCA counter/timer CCAPMn, n = 0 to 4 ECOMn CAPPn CAPNn MATn TOGn PWMn ECCFn 0xDA to 0xDE **CMOD** CIDL **WDTE** CPS1 CPS0 **ECF** 0xD9

Figure 6-7. PCA Compare Mode and PCA Watchdog Timer

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

### 6.3.3 High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (See Figure 6-8).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

<sup>\*</sup> Only for Module 4

Figure 6-8. PCA High Speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

#### 6.3.4 Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 6-9 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                   |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | SMOD1           | Serial port Mode bit 1 Set to select double baud rate in mode 1, 2 or 3.                                                                      |

| 6             | SMOD0           | Serial port Mode bit 0 Clear to select SM0 bit in SCON register. Set to to select FE bit in SCON register.                                    |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                  |

| 4             | POF             | Power-Off Flag Clear to recognize next reset type. Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set by software. |

| 3             | GF1             | General purpose Flag Cleared by user for general purpose usage. Set by user for general purpose usage.                                        |

| 2             | GF0             | General purpose Flag Cleared by user for general purpose usage. Set by user for general purpose usage.                                        |

| 1             | PD              | Power-Down mode bit Cleared by hardware when reset occurs. Set to enter power-down mode.                                                      |

| 0             | IDL             | Idle mode bit Clear by hardware when interrupt or reset occurs. Set to enter idle mode.                                                       |

Reset Value = 00X1 0000b

Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | T4              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6             | Т3              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5             | T2              | Reserved Do not try to set or clear this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4             | T1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3             | T0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2             | S2              | WDT Time-out select bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1             | S1              | WDT Time-out select bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0             | S0              | WDT Time-out select bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ļ             |                 | S2         S1         S0Selected Time-out           0         0         0(2 <sup>14</sup> - 1) machine cycles, 16.3 ms @ 12 MHz           0         0         1(2 <sup>15</sup> - 1) machine cycles, 32.7 ms @ 12 MHz           0         1         0(2 <sup>16</sup> - 1) machine cycles, 65.5 ms @ 12 MHz           0         1         1(2 <sup>17</sup> - 1) machine cycles, 131 ms @ 12 MHz           1         0         0(2 <sup>18</sup> - 1) machine cycles, 262 ms @ 12 MHz           1         0         1(2 <sup>19</sup> - 1) machine cycles, 542 ms @ 12 MHz           1         1         0(2 <sup>20</sup> - 1) machine cycles, 1.05 s @ 12 MHz           1         1         1(2 <sup>21</sup> - 1) machine cycles, 2.09 s @ 12 MHz |

Reset value XXXX X000

### 6.8.2 WDT during Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Power-down mode the user does not need to service the WDT. There are 2 methods of exiting Power-down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the TS80C51Rx2 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is best to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the TS80C51Rx2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

# 6.9 ONCE™ Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS8xC51Rx2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C51Rx2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- · Hold ALE low as RST is deactivated.

While the TS80C51Rx2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

**Table 6-23.** External Pin Status during ONCE Mode

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

Table 11-1.

DC Parameters in Standard Voltage

| Symbol                            | Parameter                                              | Min                                                                     | Тур               | Max                                                 | Unit        | Test Conditions                                                                                                                     |

|-----------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------|-------------------|-----------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3, 4, 5               | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                     | V<br>V<br>V | $\begin{split} I_{OH} &= -10 \; \mu A \\ I_{OH} &= -30 \; \mu A \\ I_{OH} &= -60 \; \mu A \\ V_{CC} &= 5 \; V \pm 10\% \end{split}$ |

| V <sub>OH1</sub>                  | Output High Voltage, port 0                            | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                     | V<br>V<br>V | $I_{OH} = -200 \ \mu A$ $I_{OH} = -3.2 \ mA$ $I_{OH} = -7.0 \ mA$ $V_{CC} = 5 \ V \pm 10\%$                                         |

| V <sub>OH2</sub>                  | Output High Voltage,ALE, PSEN                          | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                     | V<br>V<br>V | $I_{OH} = -100 \ \mu A$ $I_{OH} = -1.6 \ mA$ $I_{OH} = -3.5 \ mA$ $V_{CC} = 5 \ V \pm 10\%$                                         |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                  | 50                                                                      | 90 (5)            | 200                                                 | kΩ          |                                                                                                                                     |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2, 3, 4, 5            |                                                                         |                   | -50                                                 | μА          | Vin = 0.45 V                                                                                                                        |

| ILI                               | Input Leakage Current                                  |                                                                         |                   | ±10                                                 | μА          | 0.45 V < Vin < V <sub>CC</sub>                                                                                                      |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3, 4, 5 |                                                                         |                   | -650                                                | μА          | Vin = 2.0 V                                                                                                                         |

| C <sub>IO</sub>                   | Capacitance of I/O Buffer                              |                                                                         |                   | 10                                                  | pF          | Fc = 1 MHz<br>Ta = 25°C                                                                                                             |

| I <sub>PD</sub>                   | Power-down Current                                     |                                                                         | 20 <sup>(5)</sup> | 50                                                  | μΑ          | 2.0 V < V <sub>CC &lt;</sub> 5.5 V <sup>(3)</sup>                                                                                   |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: (7)      |                                                                         |                   | 1 + 0.4 Freq<br>(MHz)<br>@12MHz 5.8<br>@16MHz 7.4   | mA          | V <sub>CC</sub> = 5.5 V <sup>(1)</sup>                                                                                              |

| I <sub>CC</sub> operating         | Power Supply Current Maximum values, X1 mode: (7)      |                                                                         |                   | 3 + 0.6 Freq<br>(MHz)<br>@12MHz 10.2<br>@16MHz 12.6 | mA          | V <sub>CC</sub> = 5.5 V <sup>(8)</sup>                                                                                              |

| I <sub>CC</sub><br>idle           | Power Supply Current Maximum values, X1 mode: (7)      |                                                                         |                   | 0.25+0.3 Freq<br>(MHz)<br>@12MHz 3.9<br>@16MHz 5.1  | mA          | V <sub>CC</sub> = 5.5 V <sup>(2)</sup>                                                                                              |

# External Program Memory Characteristics Table 11-5. Symbol Description 11.5.2

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| $T_{PXIZ}$        | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

Table 11-6. AC Parameters for Fix Clock

| Speed             |     | M<br>MHz | X2 n<br>30 l | V<br>node<br>MHz<br>z equiv. | stan<br>mo | V<br>dard<br>ode<br>MHz | X2 n<br>20 I | L<br>node<br>MHz<br>z equiv. | stan<br>mo | L<br>dard<br>ode<br>MHz | Units |

|-------------------|-----|----------|--------------|------------------------------|------------|-------------------------|--------------|------------------------------|------------|-------------------------|-------|

| Symbol            | Min | Max      | Min          | Max                          | Min        | Max                     | Min          | Max                          | Min        | Max                     |       |

| Т                 | 25  |          | 33           |                              | 25         |                         | 50           |                              | 33         |                         | ns    |

| T <sub>LHLL</sub> | 40  |          | 25           |                              | 42         |                         | 35           |                              | 52         |                         | ns    |

| T <sub>AVLL</sub> | 10  |          | 4            |                              | 12         |                         | 5            |                              | 13         |                         | ns    |

| T <sub>LLAX</sub> | 10  |          | 4            |                              | 12         |                         | 5            |                              | 13         |                         | ns    |

| T <sub>LLIV</sub> |     | 70       |              | 45                           |            | 78                      |              | 65                           |            | 98                      | ns    |

| T <sub>LLPL</sub> | 15  |          | 9            |                              | 17         |                         | 10           |                              | 18         |                         | ns    |

| T <sub>PLPH</sub> | 55  |          | 35           |                              | 60         |                         | 50           |                              | 75         |                         | ns    |

| T <sub>PLIV</sub> |     | 35       |              | 25                           |            | 50                      |              | 30                           |            | 55                      | ns    |

| T <sub>PXIX</sub> | 0   |          | 0            |                              | 0          |                         | 0            |                              | 0          |                         | ns    |

| T <sub>PXIZ</sub> |     | 18       |              | 12                           |            | 20                      |              | 10                           |            | 18                      | ns    |

| T <sub>AVIV</sub> |     | 85       |              | 53                           |            | 95                      |              | 80                           |            | 122                     | ns    |

| T <sub>PLAZ</sub> |     | 10       |              | 10                           |            | 10                      |              | 10                           |            | 10                      | ns    |

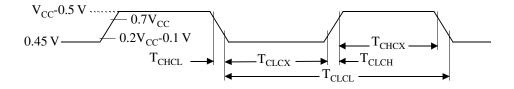

### 11.5.11 External Clock Drive Characteristics (XTAL1)

| Symbol                               | Parameter               | Min | Max | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

### 11.5.12 External Clock Drive Waveforms

Figure 11-11. External Clock Drive Waveforms

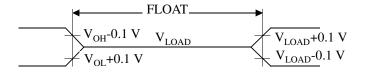

### 11.5.13 AC Testing Input/Output Waveforms

Figure 11-12. AC Testing Input/Output Waveforms

$$\begin{array}{c} V_{\text{CC}}\text{-}0.5\,\text{V} \\ \hline 0.2V_{\text{CC}}\text{+}0.9 \\ \hline 0.2V_{\text{CC}}\text{-}0.1 \\ \hline \end{array}$$

Input/output

AC inputs during testing are driven at  $V_{CC}$  - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at  $V_{IH}$  min for a logic "1" and  $V_{IL}$  max for a logic "0".

### 11.5.14 Float Waveforms

Figure 11-13. Float Waveforms

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20 \text{mA}$ .

| Part Number      | Memory size     | Supply Voltage   | Temperature Range | Max Frequency | Package | Packing  |  |  |  |  |  |

|------------------|-----------------|------------------|-------------------|---------------|---------|----------|--|--|--|--|--|

| AT80C51RA2-3CSCV |                 | 1                | 1                 |               | l .     | <b>'</b> |  |  |  |  |  |

| AT80C51RA2-SLSCV |                 |                  |                   |               |         |          |  |  |  |  |  |

| AT80C51RA2-RLTCV |                 |                  | 00001             |               |         |          |  |  |  |  |  |

| AT80C51RA2-3CSIV |                 | OBSOLETE         |                   |               |         |          |  |  |  |  |  |

| AT80C51RA2-SLSIV |                 |                  |                   |               |         |          |  |  |  |  |  |

| AT80C51RA2-RLSIV |                 |                  |                   |               |         |          |  |  |  |  |  |

|                  | •               |                  |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-MCA   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-MCB   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-MCE   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-MIA   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-MIB   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-MIE   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-LCA   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-LCB   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-LCE   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-LIA   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-LIB   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-LIE   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-VCA   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-VCB   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-VCE   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-VIA   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-VIB   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| TS80C51RD2-VIE   | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

|                  | •               |                  |                   |               |         |          |  |  |  |  |  |

| AT80C51RD2-3CSUM | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| AT80C51RD2-SLSUM | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| AT80C51RD2-RLTUM | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| AT80C51RD2-3CSUL | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| AT80C51RD2-SLSUL | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| AT80C51RD2-RLTUL | Not recommended | d use AT87C51RD2 |                   |               |         |          |  |  |  |  |  |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS83C51RB2-MCA   |               | •              |                    |                    | •       | •       |

| TS83C51RB2-MCB   | ]             |                |                    |                    |         |         |

| TS83C51RB2-MCE   | ]             |                |                    |                    |         |         |

| TS83C51RB2-MIA   | ]             |                |                    |                    |         |         |

| TS83C51RB2-MIB   |               |                |                    |                    |         |         |

| TS83C51RB2-MIE   | ]             |                |                    |                    |         |         |

| TS83C51RB2-LCA   | ]             |                |                    |                    |         |         |

| TS83C51RB2-LCB   | ]             |                |                    |                    |         |         |

| TS83C51RB2-LCE   |               |                | OBSOLE             | TE                 |         |         |

| TS83C51RB2-LIA   | ]             |                | OBSOLE             | IE                 |         |         |

| TS83C51RB2-LIB   | ]             |                |                    |                    |         |         |

| TS83C51RB2-LIE   | ]             |                |                    |                    |         |         |

| TS83C51RB2-VCA   | ]             |                |                    |                    |         |         |

| TS83C51RB2-VCB   | ]             |                |                    |                    |         |         |

| TS83C51RB2-VCE   | ]             |                |                    |                    |         |         |

| TS83C51RB2-VIA   | ]             |                |                    |                    |         |         |

| TS83C51RB2-VIB   | ]             |                |                    |                    |         |         |

| TS83C51RB2-VIE   | ]             |                |                    |                    |         |         |

|                  | •             |                |                    |                    |         |         |

| AT83C51RB2-3CSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RB2-SLSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RB2-RLTUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RB2-3CSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RB2-SLSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RB2-RLTUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS83C51RD2-MCA   |               | 1              | 1                  |                    |         | 1       |

| TS83C51RD2-MCB   |               |                |                    |                    |         |         |

| TS83C51RD2-MCE   |               |                |                    |                    |         |         |

| TS83C51RD2-MIA   |               |                |                    |                    |         |         |

| TS83C51RD2-MIB   |               |                |                    |                    |         |         |

| TS83C51RD2-MIE   |               |                |                    |                    |         |         |

| TS83C51RD2-LCB   |               |                |                    |                    |         |         |

| TS83C51RD2-LCE   |               |                |                    |                    |         |         |

| TS83C51RD2-LIA   |               |                | OBSOLE             | TE                 |         |         |

| TS83C51RD2-LIB   |               |                |                    |                    |         |         |

| TS83C51RD2-LIE   |               |                |                    |                    |         |         |

| TS83C51RD2-VCA   |               |                |                    |                    |         |         |

| TS83C51RD2-VCB   |               |                |                    |                    |         |         |

| TS83C51RD2-VCE   |               |                |                    |                    |         |         |

| TS83C51RD2-VIA   |               |                |                    |                    |         |         |

| TS83C51RD2-VIB   |               |                |                    |                    |         |         |

| TS83C51RD2-VIE   |               |                |                    |                    |         |         |

|                  | •             |                |                    |                    |         |         |

| AT83C51RD2-3CSUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RD2-SLSUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RD2-RLTUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RD2-3CSUL | ROM 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RD2-SLSUL | ROM 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RD2-RLTUL | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (30 MHz X2) | PDIL40  | Stick   |

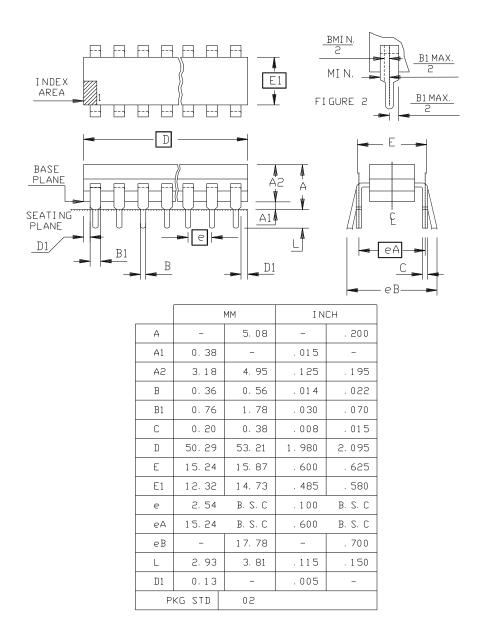

## 13.2 PDIL40

### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### International

Atmel Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex

France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11 Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com

Technical Support

Enter Product Line E-mail

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.