Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Obsolete                                                    |

| Core Processor             | 80C51                                                       |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40/20MHz                                                    |

| Connectivity               | UART/USART                                                  |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 32                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | OTP                                                         |

| EEPROM Size                | ·                                                           |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Through Hole                                                |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                    |

| Supplier Device Package    | 40-PDIL                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at87c51rd2-3csum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

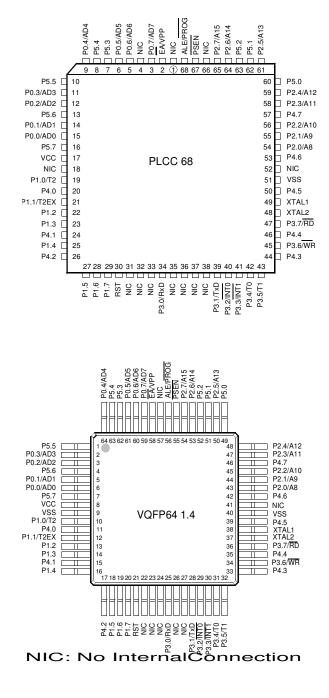

| PSEN   | 67 | 55 |

|--------|----|----|

| EA/VPP | 2  | 58 |

| XTAL1  | 49 | 38 |

| XTAL2  | 48 | 37 |

| P4.0   | 20 | 11 |

| P4.1   | 24 | 15 |

| P4.2   | 26 | 17 |

| P4.3   | 44 | 33 |

| P4.4   | 46 | 35 |

| P4.5   | 50 | 39 |

| P4.6   | 53 | 42 |

| P4.7   | 57 | 46 |

| P5.0   | 60 | 49 |

| P5.1   | 62 | 51 |

| P5.2   | 63 | 52 |

| P5.3   | 7  | 62 |

| P5.4   | 8  | 63 |

| P5.5   | 10 | 1  |

| P5.6   | 13 | 4  |

| P5.7   | 16 | 7  |

### 6.2 Timer 2

The timer 2 in the TS80C51RX2 is compatible with the timer 2 in the 80C52. It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2, connected in cascade. It is controlled by T2CON register (See Table 6-2) and T2MOD register (See Table 6-3). Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects  $F_{OSC}/12$  (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to be incremented by the selected input.

Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and  $CP/\overline{RL2}$  (T2CON), as described in the Atmel 8-bit Microcontroller Hardware description.

Refer to the Atmel 8-bit Microcontroller Hardware description for the description of Capture and Baud Rate Generator Modes.

In TS80C51RX2 Timer 2 includes the following enhancements:

- Auto-reload mode with up or down counter

- Programmable clock-output

#### 6.2.1 Auto-reload Mode

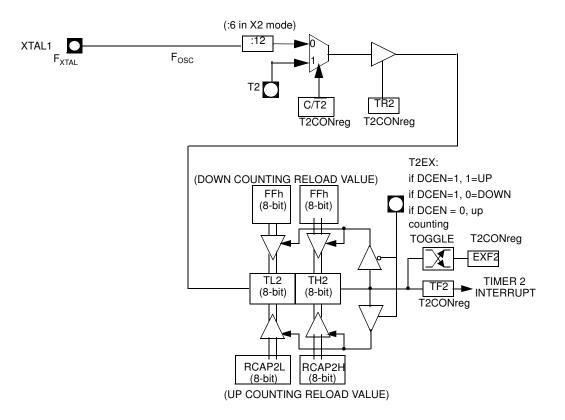

The auto-reload mode configures timer 2 as a 16-bit timer or event counter with automatic reload. If DCEN bit in T2MOD is cleared, timer 2 behaves as in 80C52 (refer to the Atmel 8-bit Microcontroller Hardware description). If DCEN bit is set, timer 2 acts as an Up/down timer/counter as shown in Figure 6-2. In this mode the T2EX pin controls the direction of count.

When T2EX is high, timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.

When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.

The EXF2 bit toggles when timer 2 overflows or underflows according to the the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.

#### Figure 6-2. Auto-reload Mode Up/Down Counter (DCEN = 1)

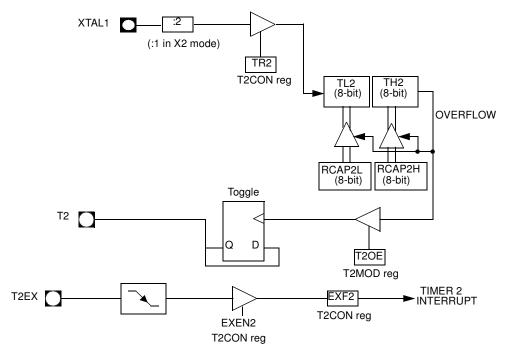

#### 6.2.2 Programmable Clock-Output

In the clock-out mode, timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 6-3) . The input clock increments TL2 at frequency  $F_{OSC}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$$Clock - OutFrequency = \frac{F_{osc}}{4 \times (65536 - RCAP2H/RCAP2L)}$$

For a 16 MHz system clock, timer 2 has a programmable frequency range of 61 Hz  $(F_{OSC}/2^{16})$  to 4 MHz  $(F_{OSC}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

### **Figure 6-3.** Clock-Out Mode $C/\overline{T2} = 0$

| Table 6-2. | T2CON F<br>T2CON - | 0    | ontrol Regist | er (C8h) |     |       |         |

|------------|--------------------|------|---------------|----------|-----|-------|---------|

| 7          | 6                  | 5    | 4             | 3        | 2   | 1     | 0       |

| TF2        | EXF2               | RCLK | TCLK          | EXEN2    | TR2 | C/T2# | CP/RL2# |

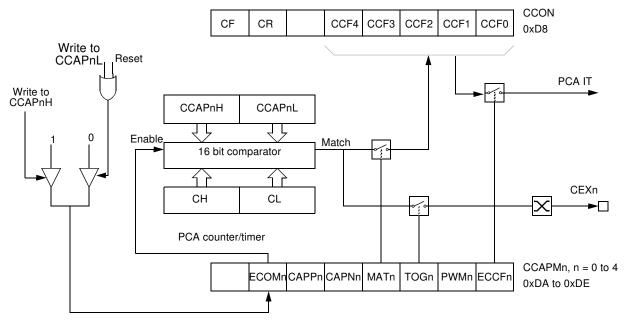

## 6.3 Programmable Counter Array PCA

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture modules. Its clock input can be programmed to count any one of the following signals:

- Oscillator frequency  $\div$  12 ( $\div$  6 in X2 mode)

- Oscillator frequency  $\div$  4 ( $\div$  2 in X2 mode)

- Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture modules can be programmed in any one of the following modes:

- rising and/or falling edge capture,

- · software timer,

- · high-speed output, or

- pulse width modulator.

Module 4 can also be programmed as a watchdog timer (See Section "PCA Watchdog Timer", page 33).

When the compare/capture modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the module executes its function. All five modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If the port is not used for the PCA, it can still be used for standard I/O.

| PCA component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2 / ECI       |

| 16-bit Module 0 | P1.3 / CEX0      |

| 16-bit Module 1 | P1.4 / CEX1      |

| 16-bit Module 2 | P1.5 / CEX2      |

| 16-bit Module 3 | P1.6 / CEX3      |

| 16-bit Module 4 | P1.7 / CEX4      |

**The PCA timer** is a common time base for all five modules (See Figure 6-4). The timer count source is determined from the CPS1 and CPS0 bits in the **CMOD SFR** (See Table 6-4) and can be programmed to run at:

- 1/12 the oscillator frequency. (Or 1/6 in X2 Mode)

- 1/4 the oscillator frequency. (Or 1/2 in X2 Mode)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

• The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function. Table 6-7 shows the CCAPMn settings for the various PCA functions.

#### Table 6-6. CCAPMn: PCA Modules Compare/Capture Control Registers

CCAPMn Address n = 0 - 4 CCAPM0=0DAH CCAPM1=0DBH CCAPM2=0DCH CCAPM3=0DDH CCAPM4=0DEH

| Reset value         X         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< th=""><th></th><th>-</th><th>ECOMn</th><th>CAPPn</th><th>CAPNn</th><th>MATn</th><th>TOGn</th><th>PWMm</th><th>ECCFn</th></th<> |             | - | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---|-------|-------|-------|------|------|------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Reset value | Х | 0     | 0     | 0     | 0    | 0    | 0    | 0     |

| Symbol | Function                                                                                                                                                   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -      | Not implemented, reserved for future use. (1)                                                                                                              |

| ECOMn  | Enable Comparator. ECOMn = 1 enables the comparator function.                                                                                              |

| CAPPn  | Capture Positive, CAPPn = 1 enables positive edge capture.                                                                                                 |

| CAPNn  | Capture Negative, CAPNn = 1 enables negative edge capture.                                                                                                 |

| MATn   | Match. When MATn = 1, a match of the PCA counter with this module's compare/capture register causes the CCFn bit in CCON to be set, flagging an interrupt. |

| TOGn   | Toggle. When TOGn = 1, a match of the PCA counter with this module's compare/capture register causes the CEXn pin to toggle.                               |

| PWMn   | Pulse Width Modulation Mode. PWMn = 1 enables the CEXn pin to be used as a pulse width modulated output.                                                   |

| ECCFn  | Enable CCF interrupt. Enables compare/capture flag CCFn in the CCON register to generate an interrupt.                                                     |

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

| Table 6-7. | PCA Module Modes | (CCAPMn Registers) |

|------------|------------------|--------------------|

|------------|------------------|--------------------|

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn | Module Function                                  |  |

|-------|-------|-------|------|------|------|-------|--------------------------------------------------|--|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | No Operation                                     |  |

| х     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigge on CEXn |  |

| х     | 0     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a negative trigger on CEXn     |  |

| Х     | 1     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a transition on CEXn           |  |

| 1     | 0     | 0     | 1    | 0    | 0    | Х     | 16-bit Software Timer / Compare mode.            |  |

| 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                         |  |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                        |  |

| 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer (module 4 only)                   |  |

Figure 6-8. PCA High Speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

#### 6.3.4 Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 6-9 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

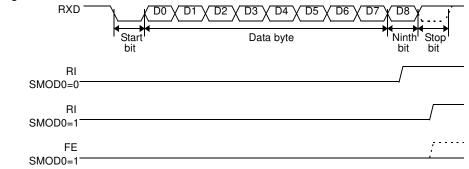

Figure 6-12. UART Timings in Modes 2 and 3

#### 6.4.2 Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit.

To support automatic address recognition, a device is identified by a given address and a broadcast address.

Note: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

#### 6.4.3 Given Address

Each device has an individual address that is specified in SADDR register; the SADEN register is a mask byte that contains don't-care bits (defined by zeros) to form the device's given address. The don't-care bits provide the flexibility to address one or more slaves at a time. The following example illustrates how a given address is formed.

To address a device by its individual address, the SADEN mask byte must be 1111 1111b.

For example:

```

SADDR0101 0110b

SADEN1111 1100b

Given0101 01XXb

```

The following is an example of how to use given addresses to address different slaves:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Given1111 0X0Xb

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Given1111 0XX1b

```

#### Table 6-12. SADEN - Slave Address Mask Register (B9h)

| 7                        | 6       | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|--------------------------|---------|---|---|---|---|---|---|--|--|--|--|

|                          |         |   |   |   |   |   |   |  |  |  |  |

| Reset Value = 0000 0000b |         |   |   |   |   |   |   |  |  |  |  |

| Not bit addr             | essable |   |   |   |   |   |   |  |  |  |  |

### Table 6-13. SADDR - Slave Address Register (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   | • | • | • | • | · |

Reset Value = 0000 0000b

Not bit addressable

# Table 6-14. SCON Register

SCON - Serial Control Register (98h)

| 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|--------|-----|-----|-----|-----|-----|----|----|

| FE/SM0 | SM1 | SM2 | REN | TB8 | RB8 | ТІ | RI |

# Table 6-18.IP RegisterIP - Interrupt Priority Register (B8h)

| 7          | 6         | 5          | 4                                                                                      | 3   | 2   | 1   | 0   |  |  |

|------------|-----------|------------|----------------------------------------------------------------------------------------|-----|-----|-----|-----|--|--|

| -          | PPC       | PT2        | PS                                                                                     | PT1 | PX1 | PT0 | PX0 |  |  |

| Bit Number | Bit Mnemo | nic Descri | otion                                                                                  |     |     |     |     |  |  |

| 7          | -         |            | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |     |     |     |     |  |  |

| 6          | PPC       |            | PCA interrupt priority bit<br>Refer to PPCH for priority level.                        |     |     |     |     |  |  |

| 5          | PT2       |            | Timer 2 overflow interrupt Priority bit<br>Refer to PT2H for priority level.           |     |     |     |     |  |  |

| 4          | PS        |            | o <b>ort Priority bi</b><br>PSH for priori                                             |     |     |     |     |  |  |

| 3          | PT1       |            | Timer 1 overflow interrupt Priority bit<br>Refer to PT1H for priority level.           |     |     |     |     |  |  |

| 2          | PX1       |            | External interrupt 1 Priority bit<br>Refer to PX1H for priority level.                 |     |     |     |     |  |  |

| 1          | PT0       |            | Timer 0 overflow interrupt Priority bit<br>Refer to PT0H for priority level.           |     |     |     |     |  |  |

| 0          | PX0       |            | External interrupt 0 Priority bit<br>Refer to PX0H for priority level.                 |     |     |     |     |  |  |

Reset Value = X000 0000b

Bit addressable

| Table 6-19. | IPH Register |

|-------------|--------------|

|-------------|--------------|

IPH - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                            | 4                                                                               | 3                             | 2     | 1    | 0    |  |  |

|---------------|-----------------|----------------------------------------------|---------------------------------------------------------------------------------|-------------------------------|-------|------|------|--|--|

| -             | РРСН            | PT2H                                         | PSH                                                                             | PT1H                          | PX1H  | РТОН | PX0H |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descrip                                      | otion                                                                           |                               |       |      |      |  |  |

| 7             | -               |                                              | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                               |       |      |      |  |  |

| 6             | PPCH            | PCA int<br><u>PPCHP</u><br>0<br>1<br>1       | errupt priority t<br><u>PC Priori</u><br>0 Lowest<br>1<br>0<br>1 Highest        | ty Level                      |       |      |      |  |  |

| 5             | PT2H            | Timer 2<br><u>PT2H P</u><br>0<br>0<br>1<br>1 |                                                                                 | :                             | n bit |      |      |  |  |

| 4             | PSH             | Serial p<br><u>PSH</u> 0<br>0<br>1<br>1      | ort Priority Hig<br>P <u>S Priority</u><br>0Lowest<br>1<br>0<br>1Highest        |                               |       |      |      |  |  |

| 3             | PT1H            |                                              | overflow interr<br><u>T1Priority Leve</u><br>0Lowest<br>1<br>0<br>1Highest      | upt Priority Higl<br><u>위</u> | n bit |      |      |  |  |

| 2             | PX1H            |                                              | l interrupt 1 Pri<br><u>X1Priority Leve</u><br>0Lowest<br>1<br>0<br>1Highest    |                               |       |      |      |  |  |

| 1             | РТОН            | Timer 0<br><u>PT0H P</u><br>0<br>0<br>1<br>1 | overflow interr<br><u>T0 Priority</u><br>0 Lowest<br>1<br>0<br>1 Highes         | 1                             | n bit |      |      |  |  |

| 0             | PX0H            | Externa<br><u>PX0HP</u><br>0<br>0<br>1<br>1  | l interrupt 0 Pri<br><u>X0 Priority</u><br>0 Lowest<br>1<br>0<br>1 Highes       | Level                         |       |      |      |  |  |

Reset Value = X000 0000b

Not bit addressable

### 6.6 Idle Mode

An instruction that sets PCON.0 causes that to be the last instruction executed before going into the Idle mode. In the Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during Idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high levels.

There are two ways to terminate the Idle. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.

The flag bits GF0 and GF1 can be used to give an indication if an interrupt occured during normal operation or during an Idle. For example, an instruction that activates Idle can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt service routine can examine the flag bits.

The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.

### 6.7 Power-down Mode

To save maximum power, a power-down mode can be invoked by software (Refer to Table 6-15, PCON register).

In power-down mode, the oscillator is stopped and the instruction that invoked power-down mode is the last instruction executed. The internal RAM and SFRs retain their value until the power-down mode is terminated.  $V_{CC}$  can be lowered to save further power. Either a hardware reset or an external interrupt can cause an exit from power-down. To properly terminate power-down, the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize.

Only external interrupts INT0 and INT1 are useful to exit from power-down. For that, interrupt must be enabled and configured as level or edge sensitive interrupt input.

Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 6-14. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power down exit will be completed when the first input will be released. In this case the higher priority interrupt service routine is executed.

Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put TS80C51Rx2 into power-down mode.

## 8.2.4 Verify Algorithm

Refer to Section "Verify algorithm".

- 4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

- 5. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

- 6. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Port 0: 26 mA Ports 1, 2, 3 and 4 and 5 when available: 15 mA Maximum total I<sub>OL</sub> for all output pins: 71 mA If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

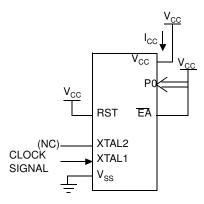

- Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (see Figure 11-5.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ . The internal ROM runs the code 80 FE (label: SJMP label). I<sub>CC</sub> would be slightly higher if a crystal oscillator is used. Measurements are made with OTP products when possible, which is the worst case.

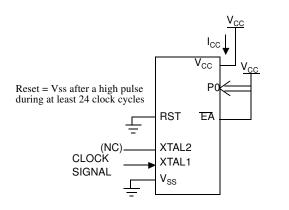

Figure 11-1. I<sub>CC</sub> Test Condition, under reset

All other pins are disconnected.

All other pins are disconnected.

### External Program Memory Characteristics Table 11-5. Symbol Description 11.5.2

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| T <sub>PXIZ</sub> | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

Table 11-6.

AC Parameters for Fix Clock

| Speed             |     | M<br>MHz | X2 n<br>30 l | V<br>node<br>MHz<br>z equiv. | stan<br>mo | V<br>dard<br>ode<br>MHz | 20 1 | L<br>node<br>MHz<br>z equiv. | stan<br>mo | L<br>dard<br>ode<br>MHz | Units |

|-------------------|-----|----------|--------------|------------------------------|------------|-------------------------|------|------------------------------|------------|-------------------------|-------|

| Symbol            | Min | Max      | Min          | Max                          | Min        | Max                     | Min  | Max                          | Min        | Max                     |       |

| Т                 | 25  |          | 33           |                              | 25         |                         | 50   |                              | 33         |                         | ns    |

| T <sub>LHLL</sub> | 40  |          | 25           |                              | 42         |                         | 35   |                              | 52         |                         | ns    |

| T <sub>AVLL</sub> | 10  |          | 4            |                              | 12         |                         | 5    |                              | 13         |                         | ns    |

| T <sub>LLAX</sub> | 10  |          | 4            |                              | 12         |                         | 5    |                              | 13         |                         | ns    |

| T <sub>LLIV</sub> |     | 70       |              | 45                           |            | 78                      |      | 65                           |            | 98                      | ns    |

| T <sub>LLPL</sub> | 15  |          | 9            |                              | 17         |                         | 10   |                              | 18         |                         | ns    |

| T <sub>PLPH</sub> | 55  |          | 35           |                              | 60         |                         | 50   |                              | 75         |                         | ns    |

| T <sub>PLIV</sub> |     | 35       |              | 25                           |            | 50                      |      | 30                           |            | 55                      | ns    |

| T <sub>PXIX</sub> | 0   |          | 0            |                              | 0          |                         | 0    |                              | 0          |                         | ns    |

| T <sub>PXIZ</sub> |     | 18       |              | 12                           |            | 20                      |      | 10                           |            | 18                      | ns    |

| T <sub>AVIV</sub> |     | 85       |              | 53                           |            | 95                      |      | 80                           |            | 122                     | ns    |

| T <sub>PLAZ</sub> |     | 10       |              | 10                           |            | 10                      |      | 10                           |            | 10                      | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 11-9. AC Parameters for a Variable Clock: derating formula

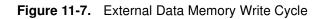

### 11.5.5 External Data Memory Write Cycle

11.5.6 External Data Memory Read Cycle

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS83C51RC2-MCA   |               |                |                    | L                  | 1       | I       |

| TS83C51RC2-MCB   |               |                |                    |                    |         |         |

| TS83C51RC2-MCE   |               |                |                    |                    |         |         |

| TS83C51RC2-MIA   |               |                |                    |                    |         |         |

| TS83C51RC2-MIB   |               |                |                    |                    |         |         |

| TS83C51RC2-MIE   |               |                |                    |                    |         |         |

| TS83C51RC2-LCA   |               |                |                    |                    |         |         |

| TS83C51RC2-LCB   |               |                |                    |                    |         |         |

| TS83C51RC2-LCE   |               |                |                    | TE                 |         |         |

| TS83C51RC2-LIA   |               |                | OBSOLE             |                    |         |         |

| TS83C51RC2-LIB   |               |                |                    |                    |         |         |

| TS83C51RC2-LIE   |               |                |                    |                    |         |         |

| TS83C51RC2-VCA   |               |                |                    |                    |         |         |

| TS83C51RC2-VCB   |               |                |                    |                    |         |         |

| TS83C51RC2-VCE   |               |                |                    |                    |         |         |

| TS83C51RC2-VIA   |               |                |                    |                    |         |         |

| TS83C51RC2-VIB   |               |                |                    |                    |         |         |

| TS83C51RC2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT83C51RC2-3CSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RC2-SLSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RC2-RLTUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RC2-3CSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RC2-SLSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RC2-RLTUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

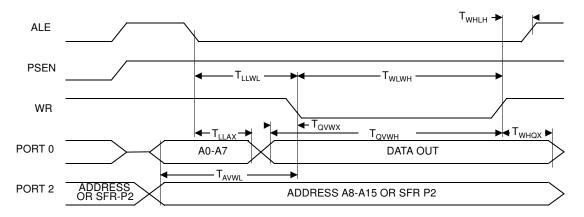

13.2 PDIL40

|    |        | MM      | ΙN    | СН      |  |  |  |  |

|----|--------|---------|-------|---------|--|--|--|--|

| А  | -      | 5.08    | -     | . 200   |  |  |  |  |

| A1 | 0.38   | -       | . 015 | -       |  |  |  |  |

| A2 | 3.18   | 4. 95   | . 125 | . 195   |  |  |  |  |

| В  | 0.36   | 0.56    | . 014 | . 022   |  |  |  |  |

| B1 | 0.76   | 1.78    | . 030 | . 070   |  |  |  |  |

| С  | 0.20   | 0.38    | . 008 | . 015   |  |  |  |  |

| D  | 50.29  | 53. 21  | 1.980 | 2.095   |  |  |  |  |

| E  | 15.24  | 15.87   | . 600 | . 625   |  |  |  |  |

| E1 | 12.32  | 14.73   | . 485 | . 580   |  |  |  |  |

| e  | 2. 54  | B. S. C | . 100 | B. S. C |  |  |  |  |

| eA | 15.24  | B. S. C | . 600 | B. S. C |  |  |  |  |

| еB | -      | 17.78   | -     | . 700   |  |  |  |  |

| L  | 2. 93  | 3. 81   | . 115 | . 150   |  |  |  |  |

| D1 | 0.13   | -       | . 005 | -       |  |  |  |  |

| P  | KG STD | 02      |       |         |  |  |  |  |

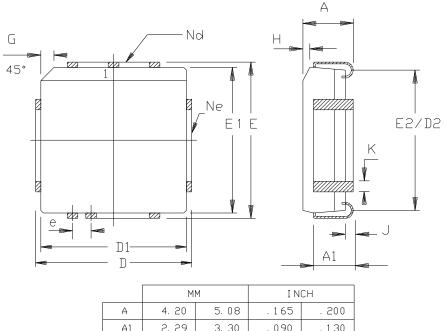

## 13.5 PLCC68

68 PINS PLCC

|    | IM     | M      | INCH  |        |  |

|----|--------|--------|-------|--------|--|

| A  | 4.20   | 5.08   | . 165 | . 200  |  |

| A1 | 2, 29  | 3.30   | . 090 | . 1 30 |  |

| D  | 25.02  | 25. 27 | . 985 | . 995  |  |

| D1 | 24.13  | 24.33  | . 950 | . 958  |  |

| D2 | 22. 61 | 23. 62 | . 890 | . 930  |  |

| E  | 25.02  | 25. 27 | . 985 | . 995  |  |

| E1 | 24.13  | 24.33  | . 950 | . 958  |  |

| E5 | 22. 61 | 23. 62 | . 890 | . 930  |  |

| e  | 1.27   | BSC    | . 050 | BSC    |  |

| G  | 1.07   | 1.22   | . 042 | . 048  |  |

| н  | 1.07   | 1.42   | . 042 | .056   |  |

| J  | 0.51   | -      | . 020 | -      |  |

| К  | 0.33   | 0.53   | . 013 | . 021  |  |

| Nd | 1      | 7      | 1     | 7      |  |

| Ne | 1      | 7      | 1     | 7      |  |

| P  | KG STD | 00     |       |        |  |

# 14. Datasheet Revision History

# 14.1 Changes from 4188E to 4188F

- 1. Removed TS80C51RD2 and AT80C51RD2 from "Ordering Information" on page 73.

- 2. Removed non-green part numbers from ordering information.