Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 30/20MHz                                                                 |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-QFP                                                                   |

| Supplier Device Package    | 44-VQFP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts80c51ra2-lce |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

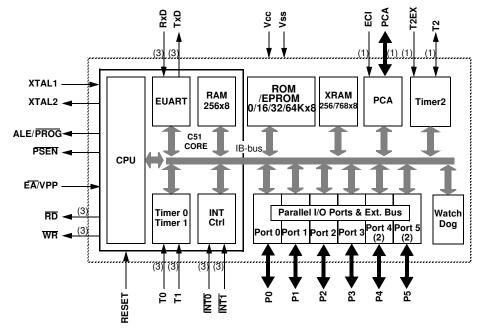

# 3. Block Diagram

(1): Alternate function of Port 1

(2): Only available on high pin count packages

(3): Alternate function of Port 3

# 4. SFR Mapping

The Special Function Registers (SFRs) of the TS80C51Rx2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3, P4, P5

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- HDW Watchdog Timer Reset: WDTRST, WDTPRG

- PCA registers: CL, CH, CCAPiL, CCAPiH, CCON, CMOD, CCAPMi

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

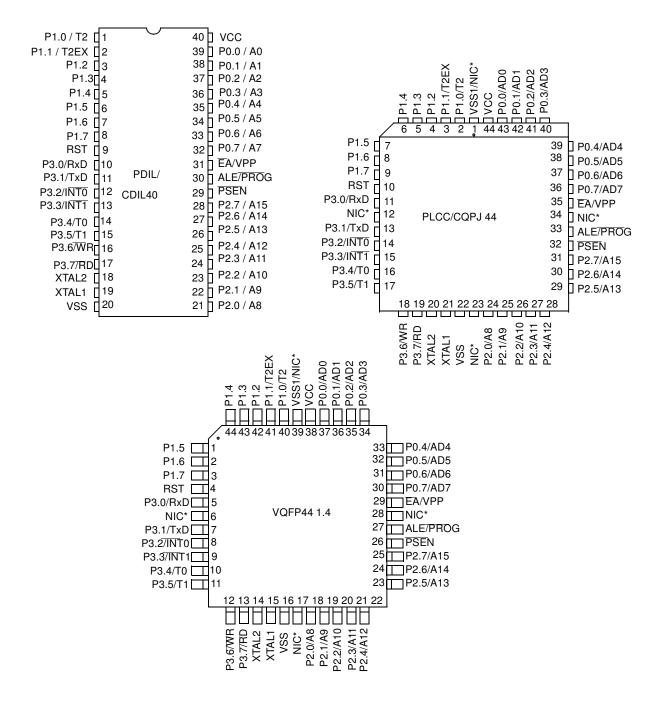

# 5. Pin Configuration

\*NIC: No Internal Connection

|                 | Pin Number |              |              |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----------------|------------|--------------|--------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mnemonic        | DIL        | LCC          | VQFP 1.4     | Туре | Name And Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| V <sub>SS</sub> | 20         | 22           | 16           | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Vss1            |            | 1            | 39           | I    | Optional Ground: Contact the Sales Office for ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| V <sub>cc</sub> | 40         | 44           | 38           | I    | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| P0.0-P0.7       | 39-32      | 43-36        | 37-30        | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. Port 0 pins must be polarized to Vcc or Vss in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port 0 also inputs the code bytes during EPROM programming. External pull-ups are required during program verification during which P0 outputs the code bytes.                                                                                                                                                                        |  |  |  |

| P1.0-P1.7       | 1-8        | 2-9          | 40-44<br>1-3 | I/O  | <b>Port 1</b> : Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. Port 1 also receives the low-order address byte during memory programming and verification.<br>Alternate functions for Port 1 include:                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                 | 1          | 2            | 40           | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                 | 2          | 3            | 41           | I    | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                 | 3          | 4            | 42           | I    | ECI (P1.2): External Clock for the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                 | 4          | 5            | 43           | I/O  | CEX0 (P1.3): Capture/Compare External I/O for PCA module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                 | 5          | 6            | 44           | I/O  | CEX1 (P1.4): Capture/Compare External I/O for PCA module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                 | 6          | 7            | 45           | I/O  | CEX0 (P1.5): Capture/Compare External I/O for PCA module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                 | 7          | 8            | 46           | I/O  | CEX0 (P1.6): Capture/Compare External I/O for PCA module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                 | 8          | 9            | 47           | I/O  | CEX0 (P1.7): Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| P2.0-P2.7       | 21-28      | 24-31        | 18-25        | I/O  | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. Some Port 2 pins (P2.0 to P2.5) receive the high order address bits during EPROM programming and verification: |  |  |  |

| P3.0-P3.7       | 10-17      | 11,<br>13-19 | 5,<br>7-13   | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Some Port 3 pins (P3.4 to P3.5) receive the high order address bits during EPROM programming and verification. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                     |  |  |  |

|                 | 10         | 11           | 5            |      | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                 |            |              | 5            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

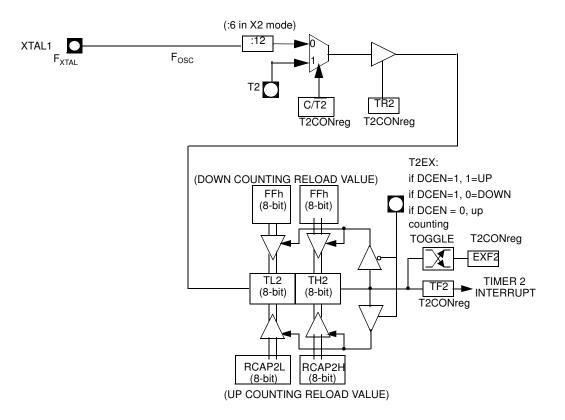

## Figure 6-2. Auto-reload Mode Up/Down Counter (DCEN = 1)

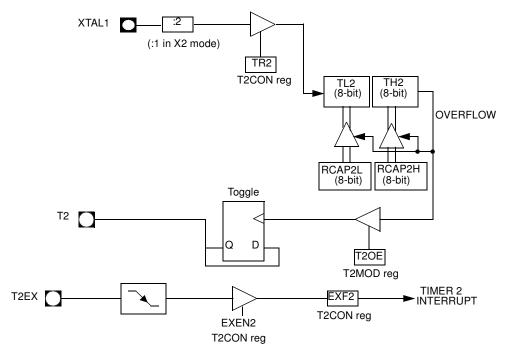

#### 6.2.2 Programmable Clock-Output

In the clock-out mode, timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 6-3) . The input clock increments TL2 at frequency  $F_{OSC}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$$Clock - OutFrequency = \frac{F_{osc}}{4 \times (65536 - RCAP2H/RCAP2L)}$$

For a 16 MHz system clock, timer 2 has a programmable frequency range of 61 Hz  $(F_{OSC}/2^{16})$  to 4 MHz  $(F_{OSC}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

AT/TS8xC51Rx2

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

## **Figure 6-3.** Clock-Out Mode $C/\overline{T2} = 0$

| Table 6-2. | T2CON F<br>T2CON - | 0    | ontrol Regist | er (C8h) |     |       |         |

|------------|--------------------|------|---------------|----------|-----|-------|---------|

| 7          | 6                  | 5    | 4             | 3        | 2   | 1     | 0       |

| TF2        | EXF2               | RCLK | TCLK          | EXEN2    | TR2 | C/T2# | CP/RL2# |

# 6.3 Programmable Counter Array PCA

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture modules. Its clock input can be programmed to count any one of the following signals:

- Oscillator frequency  $\div$  12 ( $\div$  6 in X2 mode)

- Oscillator frequency  $\div$  4 ( $\div$  2 in X2 mode)

- Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture modules can be programmed in any one of the following modes:

- rising and/or falling edge capture,

- · software timer,

- · high-speed output, or

- pulse width modulator.

Module 4 can also be programmed as a watchdog timer (See Section "PCA Watchdog Timer", page 33).

When the compare/capture modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the module executes its function. All five modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If the port is not used for the PCA, it can still be used for standard I/O.

| PCA component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2 / ECI       |

| 16-bit Module 0 | P1.3 / CEX0      |

| 16-bit Module 1 | P1.4 / CEX1      |

| 16-bit Module 2 | P1.5 / CEX2      |

| 16-bit Module 3 | P1.6 / CEX3      |

| 16-bit Module 4 | P1.7 / CEX4      |

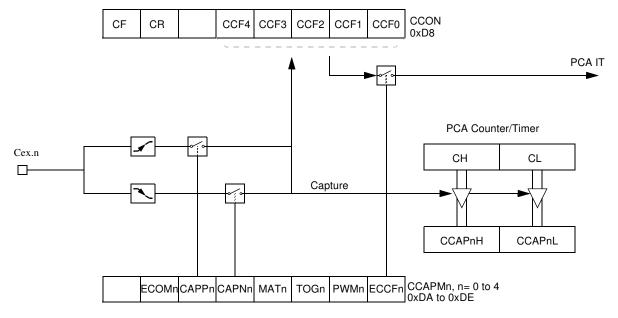

**The PCA timer** is a common time base for all five modules (See Figure 6-4). The timer count source is determined from the CPS1 and CPS0 bits in the **CMOD SFR** (See Table 6-4) and can be programmed to run at:

- 1/12 the oscillator frequency. (Or 1/6 in X2 Mode)

- 1/4 the oscillator frequency. (Or 1/2 in X2 Mode)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

- The CIDL bit which allows the PCA to stop during idle mode.

- The WDTE bit which enables or disables the watchdog function on module 4.

- The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

**The CCON SFR** contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 6-5).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

|        | CCON<br>ress 0D8H                                                       | CF          | CR          | -          | CCF4       | CCF3       | CCF2        | CCF1        | CCF0      |

|--------|-------------------------------------------------------------------------|-------------|-------------|------------|------------|------------|-------------|-------------|-----------|

|        | Reset value                                                             | 0           | 0           | Х          | 0          | 0          | 0           | 0           | 0         |

| Symbol | Function                                                                |             |             |            |            |            |             |             |           |

| CF     | PCA Counter Overflov<br>an interrupt if bit ECF<br>cleared by software. | 0           |             |            |            |            |             | 0           | n only be |

| CR     | PCA Counter Run cor<br>software to turn the P                           |             |             | ware to tu | rn the PCA | A counter  | on. Must b  | be cleared  | by        |

| -      | Not implemented, rese                                                   | erved for   | future use  | . (1)      |            |            |             |             |           |

| CCF4   | PCA Module 4 interru software.                                          | ot flag. Se | et by hardv | ware whei  | n a match  | or capture | e occurs. N | Must be cle | eared by  |

| CCF3   | PCA Module 3 interru software.                                          | ot flag. Se | et by hardv | ware whei  | n a match  | or capture | e occurs. N | Must be cle | eared by  |

| CCF2   | PCA Module 2 interru<br>software.                                       | ot flag. Se | et by hardv | ware whei  | n a match  | or capture | e occurs. N | Must be cle | eared by  |

| CCF1   | PCA Module 1 interru<br>software.                                       | ot flag. Se | et by hardv | ware whe   | n a match  | or capture | e occurs. N | Must be cle | eared by  |

| CCF0   | PCA Module 0 interru software.                                          | ot flag. Se | et by hardv | ware whe   | n a match  | or capture | e occurs. N | Must be cle | eared by  |

# Table 6-5. CCON: PCA Counter Control Register

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

The watchdog timer function is implemented in module 4 (See Figure 6-7).

The PCA interrupt system is shown in Figure 6-5.

#### Figure 6-6. PCA Capture Mode

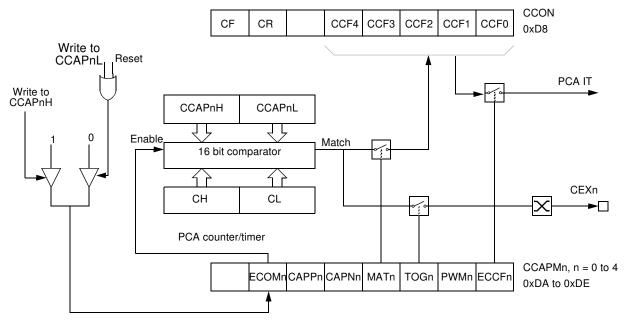

## 6.3.2 16-bit Software Timer/ Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (See Figure 6-7).

Figure 6-8. PCA High Speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

#### 6.3.4 Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 6-9 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

# 6.4 TS80C51Rx2 Serial I/O Port

The serial I/O port in the TS80C51Rx2 is compatible with the serial I/O port in the 80C52.

It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- · Automatic address recognition

#### 6.4.1 Framing Error Detection

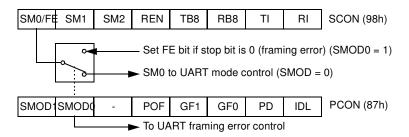

Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 6-10).

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 6-14.) bit is set.

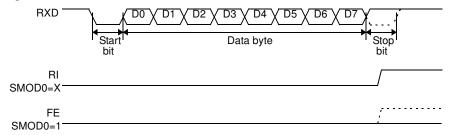

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 6-11 and Figure 6-12).

| Bit<br>Number | Bit<br>Mnemonic | Description                                           |

|---------------|-----------------|-------------------------------------------------------|

| 7             | T4              |                                                       |

| 6             | Т3              |                                                       |

| 5             | T2              | Reserved<br>Do not try to set or clear this bit.      |

| 4             | T1              |                                                       |

| 3             | T0              |                                                       |

| 2             | S2              | WDT Time-out select bit 2                             |

| 1             | S1              | WDT Time-out select bit 1                             |

| 0             | S0              | WDT Time-out select bit 0                             |

|               |                 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

Reset value XXXX X000

#### 6.8.2 WDT during Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Powerdown mode the user does not need to service the WDT. There are 2 methods of exiting Powerdown mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the TS80C51Rx2 is reset. Exiting Powerdown with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is best to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the TS80C51Rx2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

# 7. Power-Off Flag

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (See Table 7-1). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

The POF value is only relevant with a Vcc range from 4.5V to 5.5V. For lower Vcc value, reading POF bit will return indeterminate value.

| 7             | 6               | 5                     | 4                                                                                                                | 3                                           | 2                 | 1              | 0         |  |  |

|---------------|-----------------|-----------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------|----------------|-----------|--|--|

| SMOD1         | SMOD0           | -                     | POF                                                                                                              | GF1                                         | GF0               | PD             | IDL       |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio            | n                                                                                                                |                                             |                   |                |           |  |  |

| 7             | SMOD1           |                       | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                      |                                             |                   |                |           |  |  |

| 6             | SMOD0           | Clear to se           | Gerial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register. |                                             |                   |                |           |  |  |

| 5             | -               | Reserved<br>The value | read from this                                                                                                   | bit is indetermin                           | ate. Do not set   | this bit.      |           |  |  |

| 4             | POF             |                       | cognize next re                                                                                                  | eset type.<br><sub>CC</sub> rises from 0 to | o its nominal vol | tage. Can also | be set by |  |  |

| 3             | GF1             | Cleared by            |                                                                                                                  | ral purpose usag<br>urpose usage.           | ge.               |                |           |  |  |

| 2             | GF0             | Cleared by            |                                                                                                                  | ral purpose usag<br>urpose usage.           | ge.               |                |           |  |  |

| 1             | PD              | Cleared by            | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                   |                                             |                   |                |           |  |  |

| 0             | IDL             | Clear by ha           | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                    |                                             |                   |                |           |  |  |

Table 7-1.PCON RegisterPCON - Power Control Register (87h)

Reset Value = 00X1 0000b

Not bit addressable

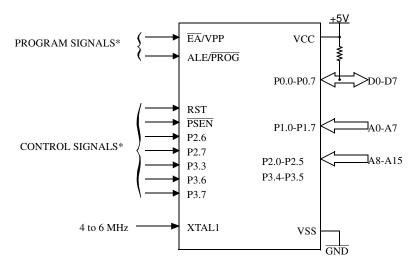

Figure 9-1. Set-Up Modes Configuration

\* See Table 31. for proper value on these inputs

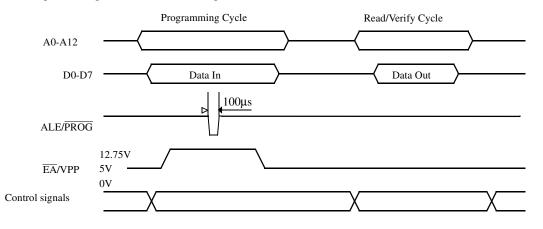

## 9.3.3 Programming Algorithm

The Improved Quick Pulse algorithm is based on the Quick Pulse algorithm and decreases the number of pulses applied during byte programming from 25 to 1.

To program the TS87C51RB2/RC2/RD2 the following sequence must be exercised:

- Step 1: Activate the combination of control signals.

- Step 2: Input the valid address on the address lines.

- Step 3: Input the appropriate data on the data lines.

- Step 4: Raise EA/VPP from VCC to VPP (typical 12.75V).

- Step 5: Pulse ALE/PROG once.

- Step 6: Lower EA/VPP from VPP to VCC

Repeat step 2 through 6 changing the address and data for the entire array or until the end of the object file is reached (See Figure 9-2).

#### 9.3.4 Verify algorithm

Code array verify must be done after each byte or block of bytes is programmed. In either case, a complete verify of the programmed array will ensure reliable programming of the TS87C51RB2/RC2/RD2.

P 2.7 is used to enable data output.

To verify the TS87C51RB2/RC2/RD2 code the following sequence must be exercised:

- Step 1: Activate the combination of program and control signals.

- Step 2: Input the valid address on the address lines.

- Step 3: Read data on the data lines.

Repeat step 2 through 3 changing the address for the entire array verification (See Figure 9-2.)

The encryption array cannot be directly verified. Verification of the encryption array is done by observing that the code array is well encrypted.

Figure 9-2. Programming and Verification Signal's Waveform

# 9.4 EPROM Erasure (Windowed Packages Only)

Erasing the EPROM erases the code array, the encryption array and the lock bits returning the parts to full functionality.

Erasure leaves all the EPROM cells in a 1's state (FF).

#### 9.4.1 Erasure Characteristics

The recommended erasure procedure is exposure to ultraviolet light (at 2537 Å) to an integrated dose at least 15 W-sec/cm<sup>2</sup>. Exposing the EPROM to an ultraviolet lamp of 12,000  $\mu$ W/cm<sup>2</sup> rating for 30 minutes, at a distance of about 25 mm, should be sufficient. An exposure of 1 hour is recommended with most of standard erasers.

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelength shorter than approximately 4,000 Å. Since sunlight and fluorescent lighting have wavelengths in this range, exposure to these light sources over an extended time (about 1 week in sunlight, or 3 years in room-level fluorescent lighting) could cause inadvertent erasure. If an application subjects the device to this type of exposure, it is suggested that an opaque label be placed over the window.

# 10. Signature Bytes

The TS83/87C51RB2/RC2/RD2 has four signature bytes in location 30h, 31h, 60h and 61h. To read these bytes follow the procedure for EPROM verify but activate the control lines provided in Table 31. for Read Signature Bytes. Table 10-1. shows the content of the signature byte for the TS87C51RB2/RC2/RD2.

| Location | Contents | Comment                  |

|----------|----------|--------------------------|

| 30h      | 58h      | Manufacturer Code: Atmel |

| 31h      | 57h      | Family Code: C51 X2      |

| 60h      | 7Ch      | Product name: TS83C51RD2 |

Table 10-1.

Signature Bytes Content

- 4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

- 5. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

- 6. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Port 0: 26 mA Ports 1, 2, 3 and 4 and 5 when available: 15 mA Maximum total I<sub>OL</sub> for all output pins: 71 mA If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

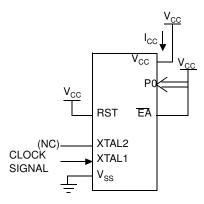

- Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (see Figure 11-5.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ . The internal ROM runs the code 80 FE (label: SJMP label). I<sub>CC</sub> would be slightly higher if a crystal oscillator is used. Measurements are made with OTP products when possible, which is the worst case.

Figure 11-1. I<sub>CC</sub> Test Condition, under reset

All other pins are disconnected.

All other pins are disconnected.

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

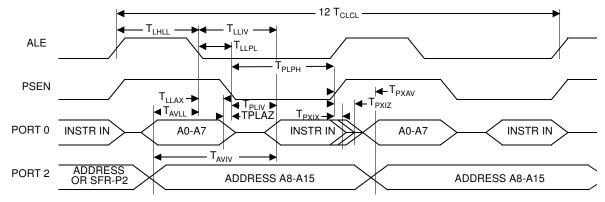

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | x                 | x         | 10 | 10 | 10 | ns    |

Table 11-7. AC Parameters for a Variable Clock: derating formula

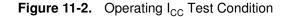

# 11.5.3 External Program Memory Read Cycle

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

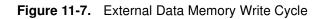

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 11-9. AC Parameters for a Variable Clock: derating formula

# 11.5.5 External Data Memory Write Cycle

11.5.6 External Data Memory Read Cycle

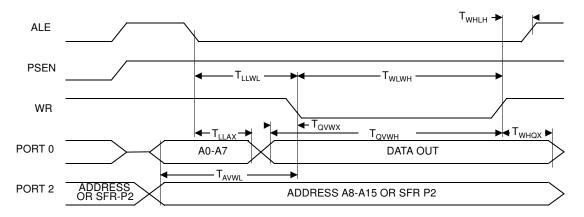

#### 11.5.15 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 signal must be changed to XTAL2 divided by two.

#### Figure 11-14. Clock Waveforms

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

# AT/TS8xC51Rx2

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS87C51RD2-MCA   |               | 1              |                    |                    |         | 1       |

| TS87C51RD2-MCB   |               |                |                    |                    |         |         |

| TS87C51RD2-MCE   |               |                |                    |                    |         |         |

| TS87C51RD2-MIA   |               |                |                    |                    |         |         |

| TS87C51RD2-MIB   |               |                |                    |                    |         |         |

| TS87C51RD2-MIE   |               |                |                    |                    |         |         |

| TS87C51RD2-LCA   |               |                |                    |                    |         |         |

| TS87C51RD2-LCB   |               |                |                    |                    |         |         |

| TS87C51RD2-LCE   | 7             |                |                    |                    |         |         |

| TS87C51RD2-LIA   | 7             |                | OBSOLE             | TE                 |         |         |

| TS87C51RD2-LIB   |               |                |                    |                    |         |         |

| TS87C51RD2-LIE   |               |                |                    |                    |         |         |

| TS87C51RD2-VCA   |               |                |                    |                    |         |         |

| TS87C51RD2-VCB   |               |                |                    |                    |         |         |

| TS87C51RD2-VCE   |               |                |                    |                    |         |         |

| TS87C51RD2-VCL   |               |                |                    |                    |         |         |

| TS87C51RD2-VIA   |               |                |                    |                    |         |         |

| TS87C51RD2-VIB   |               |                |                    |                    |         |         |

| TS87C51RD2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT87C51RD2-3CSUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RD2-SLSUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RD2-RLTUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT87C51RD2-3CSUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RD2-SLSUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RD2-RLTUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |