Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40/20MHz                                                                 |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIL                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts80c51ra2-mca |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

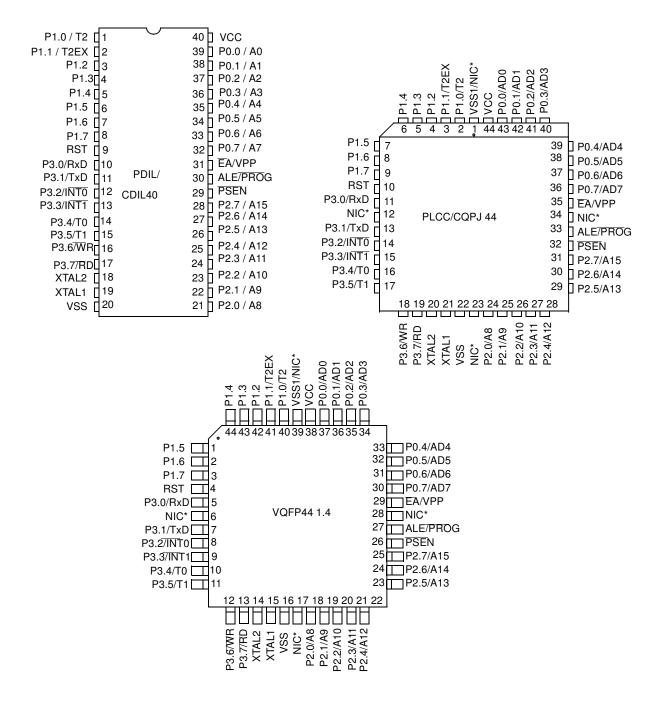

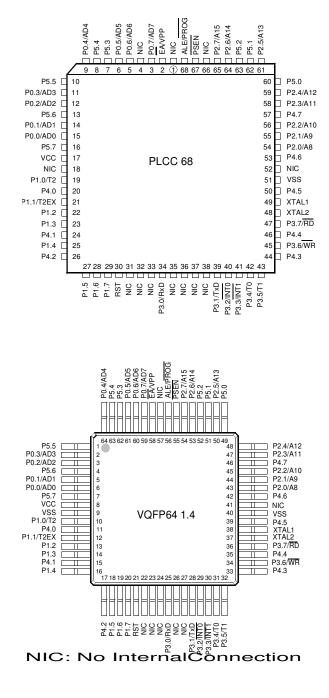

## 5. Pin Configuration

\*NIC: No Internal Connection

| PSEN   | 67 | 55 |

|--------|----|----|

| EA/VPP | 2  | 58 |

| XTAL1  | 49 | 38 |

| XTAL2  | 48 | 37 |

| P4.0   | 20 | 11 |

| P4.1   | 24 | 15 |

| P4.2   | 26 | 17 |

| P4.3   | 44 | 33 |

| P4.4   | 46 | 35 |

| P4.5   | 50 | 39 |

| P4.6   | 53 | 42 |

| P4.7   | 57 | 46 |

| P5.0   | 60 | 49 |

| P5.1   | 62 | 51 |

| P5.2   | 63 | 52 |

| P5.3   | 7  | 62 |

| P5.4   | 8  | 63 |

| P5.5   | 10 | 1  |

| P5.6   | 13 | 4  |

| P5.7   | 16 | 7  |

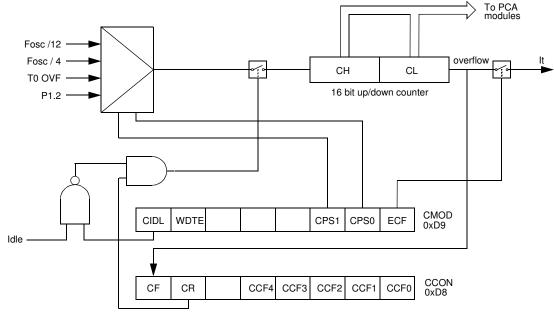

#### Figure 6-4. PCA Timer/Counter

Table 6-4. CMOD: PCA Counter Mode Register

| C<br>Addr | CIDL               | WDTE       | -                                 | -                        | -                          | CPS1       | CPS0                  | ECF         |             |           |

|-----------|--------------------|------------|-----------------------------------|--------------------------|----------------------------|------------|-----------------------|-------------|-------------|-----------|

|           | Re                 | eset value | 0                                 | 0                        | Х                          | Х          | х                     | 0           | 0           | 0         |

| Symbol    | Functio            | n          |                                   |                          |                            |            |                       |             |             |           |

| CIDL      |                    |            | ol: CIDL = 0 p<br>s it to be gate | 0                        |                            | ounter to  | continue f            | functioning | g during id | le Mode.  |

| WDTE      | Watchdo<br>enables | •          | nable: WDTE                       | E = 0 disab              | les Watch                  | dog Timer  | function (            | on PCA M    | odule 4. W  | /DTE = 1  |

| -         | Not impl           | emented,   | reserved for                      | future use               | . (1)                      |            |                       |             |             |           |

| CPS1      | PCA Co             | unt Pulse  | Select bit 1.                     |                          |                            |            |                       |             |             |           |

| CPS0      | PCA Co             | unt Pulse  | Select bit 0.                     |                          |                            |            |                       |             |             |           |

|           | CPS1               | CPS0       | Selected PC                       | A input. <sup>(2)</sup>  |                            |            |                       |             |             |           |

|           | 0                  | 0          | Internal cloc                     | k f <sub>osc</sub> /12(0 | Or f <sub>osc</sub> /6 in  | X2 Mode    | ).                    |             |             |           |

|           | 0                  | 1          | Internal cloc                     | k f <sub>osc</sub> /4(O  | r f <sub>osc</sub> /2 in X | K2 Mode).  |                       |             |             |           |

|           | 1                  | 0          | Timer 0 Ove                       | rflow                    |                            |            |                       |             |             |           |

|           | 1                  | 1          | External cloc                     | k at ECI/P               | 91.2 pin (m                | nax rate = | f <sub>osc</sub> / 8) |             |             |           |

| ECF       |                    |            | ter Overflow that function        |                          | ECF = 1 e                  | nables CF  | bit in CC             | ON to ger   | nerate an i | nterrupt. |

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

2.  $f_{osc} = oscillator frequency$

**The CMOD SFR** includes three additional bits associated with the PCA (See Figure 6-4 and Table 6-4).

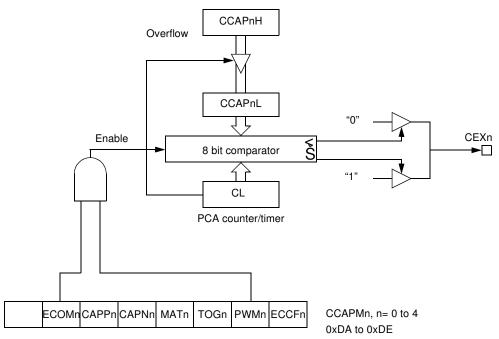

#### Figure 6-9. PCA PWM Mode

#### 6.3.5 PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 6-7 shows a diagram of how the watchdog works. The user preloads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. Periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. Disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

## 6.4 TS80C51Rx2 Serial I/O Port

The serial I/O port in the TS80C51Rx2 is compatible with the serial I/O port in the 80C52.

It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- · Automatic address recognition

#### 6.4.1 Framing Error Detection

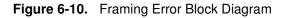

Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 6-10).

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 6-14.) bit is set.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 6-11 and Figure 6-12).

| Bit Number | Bit<br>Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                 |

|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | FE                 | Framing Error bit (SMOD0=1)<br>Clear to reset the error state, not cleared by a valid stop bit.<br>Set by hardware when an invalid stop bit is detected.<br>SMOD0 must be set to enable access to the FE bit                                                                                                                                |

|            | SM0                | Serial port Mode bit 0<br>Refer to SM1 for serial port mode selection.<br>SMOD0 must be cleared to enable access to the SM0 bit                                                                                                                                                                                                             |

| 6          | SM1                | Serial port Mode bit 1         SM0 SM1ModeDescriptionBaud Rate         0       0       0Shift RegisterF <sub>XTAL</sub> /12 (/6 in X2 mode)         0       1       18-bit UARTVariable         1       0       29-bit UARTF <sub>XTAL</sub> /64 or F <sub>XTAL</sub> /32 (/32, /16 in X2 mode)         1       1       39-bit UARTVariable |

| 5          | SM2                | Serial port Mode 2 bit / Multiprocessor Communication Enable bit<br>Clear to disable multiprocessor communication feature.<br>Set to enable multiprocessor communication feature in mode 2 and 3, and eventually<br>mode 1. This bit should be cleared in mode 0.                                                                           |

| 4          | REN                | <b>Reception Enable bit</b><br>Clear to disable serial reception.<br>Set to enable serial reception.                                                                                                                                                                                                                                        |

| 3          | TB8                | Transmitter Bit 8 / Ninth bit to transmit in modes 2 and 3<br>Clear to transmit a logic 0 in the 9th bit.<br>Set to transmit a logic 1 in the 9th bit.                                                                                                                                                                                      |

| 2          | RB8                | Receiver Bit 8 / Ninth bit received in modes 2 and 3<br>Cleared by hardware if 9th bit received is a logic 0.<br>Set by hardware if 9th bit received is a logic 1.<br>In mode 1, if SM2 = 0, RB8 is the received stop bit. In mode 0 RB8 is not used.                                                                                       |

| 1          | TI                 | <b>Transmit Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the stop<br>bit in the other modes.                                                                                                                                                    |

| 0          | RI<br>e = 0000 000 | <b>Receive Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0, see Figure 6-11. and Figure 6-<br>12. in the other modes.                                                                                                                                                     |

Reset Value = 0000 0000b Bit addressable

Table 6-15.PCON RegisterPCON - Power Control Register (87h)

| 7     | 6     | 5 | 4   | 3   | 2   | 1  | 0   |

|-------|-------|---|-----|-----|-----|----|-----|

| SMOD1 | SMOD0 | - | POF | GF1 | GF0 | PD | IDL |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | SMOD1           | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                                                                |

| 6             | SMOD0           | Serial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register.                                           |

| 5             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                     |

| 4             | POF             | <b>Power-Off Flag</b><br>Clear to recognize next reset type.<br>Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set by software. |

| 3             | GF1             | <b>General purpose Flag</b><br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                        |

| 2             | GF0             | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                               |

| 1             | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                             |

| 0             | IDL             | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                              |

Reset Value = 00X1 0000b

Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

## 6.5 Interrupt System

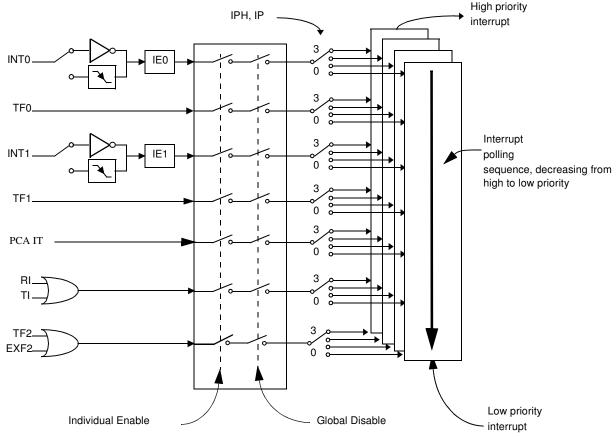

The TS80C51Rx2 has a total of 7 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), three timer interrupts (timers 0, 1 and 2), the serial port interrupt and the PCA global interrupt. These interrupts are shown in Figure 6-13.

WARNING: Note that in the first version of RC devices, the PCA interrupt is in the lowest priority. Thus the order in INTO, TF0, INT1, TF1, RI or TI, TF2 or EXF2, PCA.

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 6-17.Table 6-18.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 6-18.) and in the Interrupt Priority High register (See Table 6-19.). shows the bit values and priority levels associated with each combination.

The PCA interrupt vector is located at address 0033H. All other vector addresses are the same as standard C52 devices.

## 6.9 ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS8xC51Rx2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C51Rx2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the TS80C51Rx2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

Table 6-23.

External Pin Status during ONCE Mode

## 9. TS87C51RB2/RC2/RD2 EPROM

## 9.1 EPROM Structure

The TS87C51RB2/RC2/RD2 EPROM is divided in two different arrays:

- the code array:16/32/64 Kbytes.

- the encryption array:64 bytes.

In addition a third non programmable array is implemented:

• the signature array: 4 bytes.

## 9.2 EPROM Lock System

The program Lock system, when programmed, protects the on-chip program against software piracy.

## 9.2.1 Encryption Array

Within the EPROM array are 64 bytes of encryption array that are initially unprogrammed (all FF's). Every time a byte is addressed during program verify, 6 address lines are used to select a byte of the encryption array. This byte is then exclusive-NOR'ed (XNOR) with the code byte, creating an encrypted verify byte. The algorithm, with the encryption array in the unprogrammed state, will return the code in its original, unmodified form.

When using the encryption array, one important factor needs to be considered. If a byte has the value FFh, verifying the byte will produce the encryption byte value. If a large block (>64 bytes) of code is left unprogrammed, a verification routine will display the content of the encryption array. For this reason all the unused code bytes should be programmed with random values. This will ensure program protection.

## 9.2.2 Program Lock Bits

The three lock bits, when programmed according to Table 9-1.9.2.3, will provide different level of protection for the on-chip code and data.

| Program Lock Bits |   |   |     |                                                                                                                                                                                                                       |

|-------------------|---|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security<br>level | - |   | LB3 | Protection Description                                                                                                                                                                                                |

| 1                 | U | U | U   | No program lock features enabled. Code verify will still be<br>encrypted by the encryption array if programmed. MOVC<br>instruction executed from external program memory returns non<br>encrypted data.              |

| 2                 | Р | U | U   | MOVC instruction executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset, and further programming of the EPROM is disabled. |

| 3                 | U | Р | U   | Same as 2, also verify is disabled.                                                                                                                                                                                   |

| 4                 | U | U | Р   | Same as 3, also external execution is disabled.                                                                                                                                                                       |

Table 9-1.

Program Lock bits

U: unprogrammed,

P: programmed

WARNING: Security level 2 and 3 should only be programmed after EPROM and Core verification.

#### 9.2.3 Signature bytes

The TS87C51RB2/RC2/RD2 contains 4 factory programmed signatures bytes. To read these bytes, perform the process described in Section "Signature bytes".

#### 9.3 EPROM Programming

#### 9.3.1 Set-up Modes

In order to program and verify the EPROM or to read the signature bytes, the TS87C51RB2/RC2/RD2 is placed in specific set-up modes (See Figure 9-1.).

Control and program signals must be held at the levels indicated in Table 9-2.

#### 9.3.2 Definition of Terms

Address Lines: P1.0-P1.7, P2.0-P2.5, P3.4, P3.5 respectively for A0-A15 (P2.5 (A13) for RB, P3.4 (A14) for RC, P3.5 (A15) for RD)

Data Lines: P0.0-P0.7 for D0-D7

Control Signals:RST, PSEN, P2.6, P2.7, P3.3, P3.6, P3.7.

Program Signals: ALE/PROG, EA/VPP.

| Mode                                      | RST | PSEN | ALE/P<br>ROG | EA/VP<br>P | P2.6 | P2.7 | P3.3 | P3.6 | P3.7 |

|-------------------------------------------|-----|------|--------------|------------|------|------|------|------|------|

| Program Code data                         | 1   | 0    | 1.           | 12.75V     | 0    | 1    | 1    | 1    | 1    |

| Verify Code data                          | 1   | 0    | 1            | 1          | 0    |      | 0    | 1    | 1    |

| Program Encryption<br>Array Address 0-3Fh | 1   | 0    | Ŀ            | 12.75V     | 0    | 1    | 1    | 0    | 1    |

| Read Signature Bytes                      | 1   | 0    | 1            | 1          | 0    |      | 0    | 0    | 0    |

| Program Lock bit 1                        | 1   | 0    | 1.1          | 12.75V     | 1    | 1    | 1    | 1    | 1    |

| Program Lock bit 2                        | 1   | 0    | Ŀ            | 12.75V     | 1    | 1    | 1    | 0    | 0    |

| Program Lock bit 3                        | 1   | 0    | IJ           | 12.75V     | 1    | 0    | 1    | 1    | 0    |

#### Table 9-2.EPROM Set-Up Modes

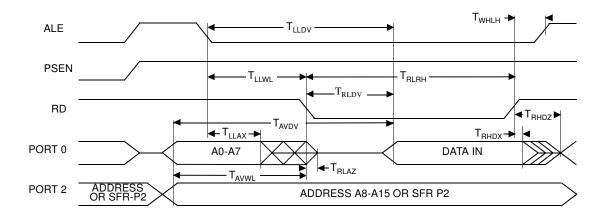

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 11-9. AC Parameters for a Variable Clock: derating formula

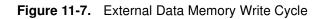

## 11.5.5 External Data Memory Write Cycle

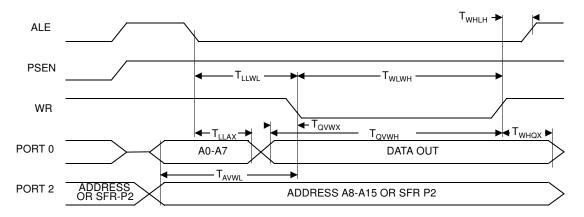

11.5.6 External Data Memory Read Cycle

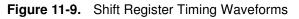

## 11.5.7 Serial Port Timing - Shift Register Mode

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

Table 11-10.

AC Parameters for a Fix Clock

| Speed             | -M<br>40 MHz |     | X2 n | MHz | '۔<br>standard<br>M |     | -<br>X2 n<br>20 I<br>40 MHz | node<br>MHz | -<br>standar<br>30 M | d mode | Units |

|-------------------|--------------|-----|------|-----|---------------------|-----|-----------------------------|-------------|----------------------|--------|-------|

| Symbol            | Min          | Max | Min  | Max | Min                 | Max | Min                         | Max         | Min                  | Max    |       |

| T <sub>XLXL</sub> | 300          |     | 200  |     | 300                 |     | 300                         |             | 400                  |        | ns    |

| T <sub>QVHX</sub> | 200          |     | 117  |     | 200                 |     | 200                         |             | 283                  |        | ns    |

| T <sub>XHQX</sub> | 30           |     | 13   |     | 30                  |     | 30                          |             | 47                   |        | ns    |

| T <sub>XHDX</sub> | 0            |     | 0    |     | 0                   |     | 0                           |             | 0                    |        | ns    |

| T <sub>XHDV</sub> |              | 117 |      | 34  |                     | 117 |                             | 117         |                      | 200    | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock | -M  | -V  | -L  | Units |

|-------------------|------|-------------------|----------|-----|-----|-----|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |     |     |     | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50  | 50  | 50  | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20  | 20  | 20  | ns    |

| T <sub>XHDX</sub> | Min  | x                 | х        | 0   | 0   | 0   | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133 | 133 | 133 | ns    |

Table 11-11. AC Parameters for a Variable Clock: derating formula

## 11.5.8 Shift Register Timing Waveforms

# 12. Ordering Information

| Part Number      | Memory size | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|-------------|----------------|--------------------|--------------------|---------|---------|

| TS80C51RA2-MCA   |             |                |                    |                    |         | 1       |

| TS80C51RA2-MCB   |             |                |                    |                    |         |         |

| TS80C51RA2-MCE   | -           |                |                    |                    |         |         |

| TS80C51RA2-MIA   | -           |                |                    |                    |         |         |

| TS80C51RA2-MIB   | _           |                |                    |                    |         |         |

| TS80C51RA2-MIE   | _           |                |                    |                    |         |         |

| TS80C51RA2-LCA   |             |                |                    |                    |         |         |

| TS80C51RA2-LCB   | _           |                |                    |                    |         |         |

| TS80C51RA2-LCE   | _           |                |                    | тг                 |         |         |

| TS80C51RA2-LIA   |             |                | OBSOLE             |                    |         |         |

| TS80C51RA2-LIB   |             |                |                    |                    |         |         |

| TS80C51RA2-LIE   |             |                |                    |                    |         |         |

| TS80C51RA2-VCA   |             |                |                    |                    |         |         |

| TS80C51RA2-VCB   | _           |                |                    |                    |         |         |

| TS80C51RA2-VCE   |             |                |                    |                    |         |         |

| TS80C51RA2-VIA   |             |                |                    |                    |         |         |

| TS80C51RA2-VIB   |             |                |                    |                    |         |         |

| TS80C51RA2-VIE   |             |                |                    |                    |         |         |

|                  |             |                |                    |                    |         |         |

| AT80C51RA2-3CSUM | Romless     | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT80C51RA2-SLSUM | Romless     | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT80C51RA2-RLTUM | Romless     | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT80C51RA2-3CSIM |             |                |                    |                    |         |         |

| AT80C51RA2-SLSIM |             |                |                    |                    |         |         |

| AT80C51RA2-RLTIM |             |                | OBSOLE             | TE                 |         |         |

| AT80C51RA2-3CSCL |             |                | OBSOLE             |                    |         |         |

| AT80C51RA2-SLSCL |             |                |                    |                    |         |         |

| AT80C51RA2-RLTCL |             |                |                    |                    |         |         |

| AT80C51RA2-3CSUL | Romless     | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT80C51RA2-SLSUL | Romless     | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT80C51RA2-RLTUL | Romless     | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS87C51RD2-MCA   |               | 1              |                    |                    |         | 1       |

| TS87C51RD2-MCB   |               |                |                    |                    |         |         |

| TS87C51RD2-MCE   |               |                |                    |                    |         |         |

| TS87C51RD2-MIA   |               |                |                    |                    |         |         |

| TS87C51RD2-MIB   |               |                |                    |                    |         |         |

| TS87C51RD2-MIE   |               |                |                    |                    |         |         |

| TS87C51RD2-LCA   |               |                |                    |                    |         |         |

| TS87C51RD2-LCB   |               |                |                    |                    |         |         |

| TS87C51RD2-LCE   |               |                |                    |                    |         |         |

| TS87C51RD2-LIA   |               |                | OBSOLE             | TE                 |         |         |

| TS87C51RD2-LIB   |               |                |                    |                    |         |         |

| TS87C51RD2-LIE   |               |                |                    |                    |         |         |

| TS87C51RD2-VCA   |               |                |                    |                    |         |         |

| TS87C51RD2-VCB   |               |                |                    |                    |         |         |

| TS87C51RD2-VCE   |               |                |                    |                    |         |         |

| TS87C51RD2-VCL   |               |                |                    |                    |         |         |

| TS87C51RD2-VIA   |               |                |                    |                    |         |         |

| TS87C51RD2-VIB   |               |                |                    |                    |         |         |

| TS87C51RD2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT87C51RD2-3CSUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RD2-SLSUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RD2-RLTUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT87C51RD2-3CSUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RD2-SLSUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RD2-RLTUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS83C51RD2-MCA   |               | •              | 1                  | •                  | •       | •       |

| TS83C51RD2-MCB   |               |                |                    |                    |         |         |

| TS83C51RD2-MCE   |               |                |                    |                    |         |         |

| TS83C51RD2-MIA   |               |                |                    |                    |         |         |

| TS83C51RD2-MIB   |               |                |                    |                    |         |         |

| TS83C51RD2-MIE   |               |                |                    |                    |         |         |

| TS83C51RD2-LCB   |               |                |                    |                    |         |         |

| TS83C51RD2-LCE   |               |                |                    |                    |         |         |

| TS83C51RD2-LIA   |               |                | OBSOLE             | TE                 |         |         |

| TS83C51RD2-LIB   |               |                |                    |                    |         |         |

| TS83C51RD2-LIE   |               |                |                    |                    |         |         |

| TS83C51RD2-VCA   |               |                |                    |                    |         |         |

| TS83C51RD2-VCB   |               |                |                    |                    |         |         |

| TS83C51RD2-VCE   |               |                |                    |                    |         |         |

| TS83C51RD2-VIA   |               |                |                    |                    |         |         |

| TS83C51RD2-VIB   |               |                |                    |                    |         |         |

| TS83C51RD2-VIE   |               |                |                    |                    |         |         |

|                  | · ·           |                |                    |                    |         |         |

| AT83C51RD2-3CSUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RD2-SLSUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RD2-RLTUM | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RD2-3CSUL | ROM 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RD2-SLSUL | ROM 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RD2-RLTUL | ROM 64k Bytes | 5V             | Industrial & Green | 40 MHz (30 MHz X2) | PDIL40  | Stick   |

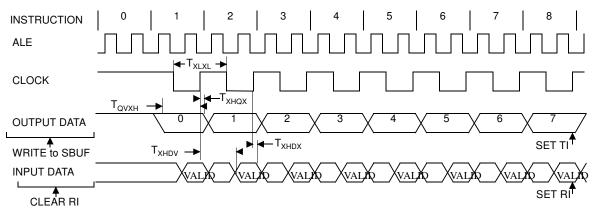

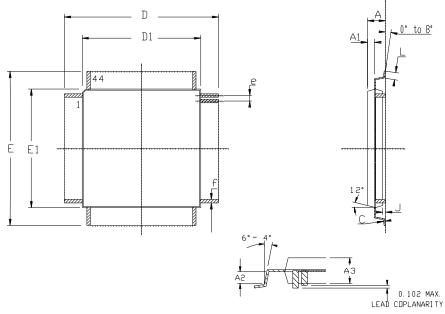

13.2 PDIL40

|    |        | MM      | INCH  |         |  |

|----|--------|---------|-------|---------|--|

| А  | -      | 5.08    | -     | . 200   |  |

| A1 | 0.38   | -       | . 015 | -       |  |

| A2 | 3.18   | 4. 95   | . 125 | . 195   |  |

| В  | 0.36   | 0.56    | . 014 | . 022   |  |

| B1 | 0.76   | 1.78    | . 030 | . 070   |  |

| С  | 0.20   | 0.38    | . 008 | . 015   |  |

| D  | 50.29  | 53. 21  | 1.980 | 2.095   |  |

| E  | 15.24  | 15.87   | . 600 | . 625   |  |

| E1 | 12.32  | 14.73   | . 485 | . 580   |  |

| e  | 2. 54  | B. S. C | . 100 | B. S. C |  |

| eA | 15.24  | B. S. C | . 600 | B. S. C |  |

| еB | -      | 17.78   | -     | . 700   |  |

| L  | 2. 93  | 3. 81   | . 115 | . 150   |  |

| D1 | 0.13   | -       | . 005 | -       |  |

| Р  | KG STD | 02      |       |         |  |

## 13.3 VQFP44

|    | м     | M      | INCH      |       |  |

|----|-------|--------|-----------|-------|--|

|    | Min   | Max    | Min       | Μαχ   |  |

| А  | _     | 1.60   | _         | . 063 |  |

| A1 | Ο.    | 64 REF | .025 REF  |       |  |

| A2 | 0.    | 64 REF | .025 REF  |       |  |

| A3 | 1.35  | 1.45   | . 053     | . 057 |  |

| D  | 11.90 | 12.10  | . 468     | . 476 |  |

| D1 | 9, 90 | 10.10  | . 390     | . 398 |  |

| E  | 11.90 | 12.10  | . 468     | . 476 |  |

| E1 | 9.90  | 10.10  | . 390     | . 398 |  |

| J  | 0.05  | _      | . 002     | -     |  |

| L  | 0.45  | 0.75   | . 018     | . 030 |  |

| e  | 0.8   | 0 BSC  | .0315 BSC |       |  |

| f  | 0.3   | 5 BSC  | .014 BSC  |       |  |