Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40/20MHz                                                                 |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts80c51ra2-mib |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

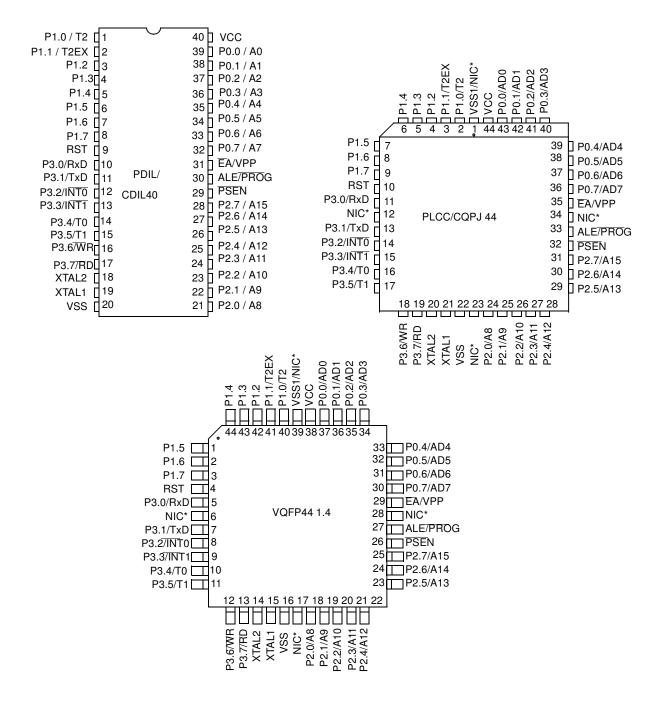

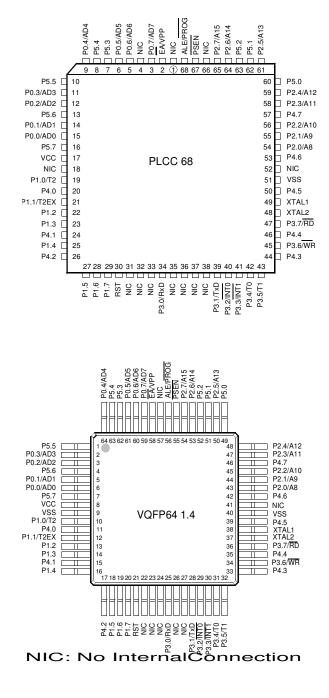

## 5. Pin Configuration

\*NIC: No Internal Connection

| P0.0 | 15 | 6  |

|------|----|----|

| P0.1 | 14 | 5  |

| P0.2 | 12 | 3  |

| P0.3 | 11 | 2  |

| P0.4 | 9  | 64 |

| P0.5 | 6  | 61 |

| P0.6 | 5  | 60 |

| P0.7 | 3  | 59 |

| P1.0 | 19 | 10 |

| P1.1 | 21 | 12 |

| P1.2 | 22 | 13 |

| P1.3 | 23 | 14 |

| P1.4 | 25 | 16 |

| P1.5 | 27 | 18 |

| P1.6 | 28 | 19 |

| P1.7 | 29 | 20 |

| P2.0 | 54 | 43 |

| P2.1 | 55 | 44 |

| P2.2 | 56 | 45 |

| P2.3 | 58 | 47 |

| P2.4 | 59 | 48 |

| P2.5 | 61 | 50 |

| P2.6 | 64 | 53 |

| P2.7 | 65 | 54 |

| P3.0 | 34 | 25 |

| P3.1 | 39 | 28 |

|      |    |    |

AIMEL

| Pin      | PLCC68 | SQUARE VQFP64 1.4 |

|----------|--------|-------------------|

| P3.2     | 40     | 29                |

| P3.3     | 41     | 30                |

| P3.4     | 42     | 31                |

| P3.5     | 43     | 32                |

| P3.6     | 45     | 34                |

| P3.7     | 47     | 36                |

| RESET    | 30     | 21                |

| ALE/PROG | 68     | 56                |

# 10 AT/TS8xC51Rx2

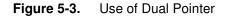

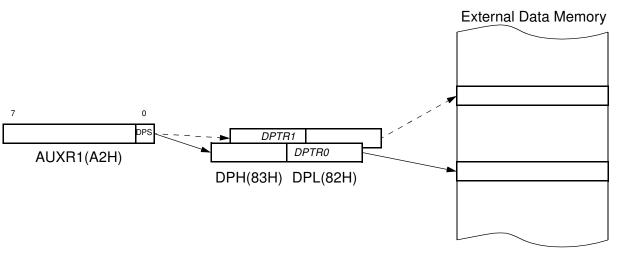

### 5.4 Dual Data Pointer Register

The additional data pointer can be used to speed up code execution and reduce code size in a number of ways.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1/bit0 (Table 5-3) that allows the program code to switch between them (Refer to Figure 5-3).

Table 5-3.

AUXR1: Auxiliary Register 1

| AUXR1<br>Address 0A2H |                                                          |                         | -              | - | - | - | GF3 | - | - | DPS |  |

|-----------------------|----------------------------------------------------------|-------------------------|----------------|---|---|---|-----|---|---|-----|--|

|                       | Reset va                                                 | alue                    | Х              | Х | Х | Х | 0   | Х | х | 0   |  |

| Symbol                | Function                                                 | Function                |                |   |   |   |     |   |   |     |  |

| -                     | Not implemented, reserved for future use <sup>(1)</sup>  |                         |                |   |   |   |     |   |   |     |  |

| DPS                   | Data Pointer S                                           | Data Pointer Selection. |                |   |   |   |     |   |   |     |  |

|                       | DPS                                                      | Operating Mode          |                |   |   |   |     |   |   |     |  |

|                       | 0                                                        | DPTI                    | DPTR0 Selected |   |   |   |     |   |   |     |  |

|                       | 1 DPTR1 Selected                                         |                         |                |   |   |   |     |   |   |     |  |

| GF3                   | This bit is a general purpose user flag <sup>(2)</sup> . |                         |                |   |   |   |     |   |   |     |  |

User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new feature. In that case, the reset value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

GF3 will not be available on first version of the RC devices.

## 6. Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare, search ...) are well served by using one data pointer as a 'source' pointer and the other one as a "destination" pointer.

#### ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Destroys DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added 00A2 AUXR1 EQU 0A2H ; 0000 909000MOV DPTR, #SOURCE ; address of SOURCE 0003 05A2 INC AUXR1 ; switch data pointers 0005 90A000 MOV DPTR, #DEST ; address of DEST 0008 LOOP: 0008 05A2 INC AUXR1 ; switch data pointers 000A EO MOVX A, @DPTR ; get a byte from SOURCE 000B A3 INC DPTR ; increment SOURCE address 000C 05A2 INC AUXR1 ; switch data pointers 000E FO MOVX @DPTR, A ; write the byte to DEST 000F A3 INC DPTR ; increment DEST address 0010 70F6JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

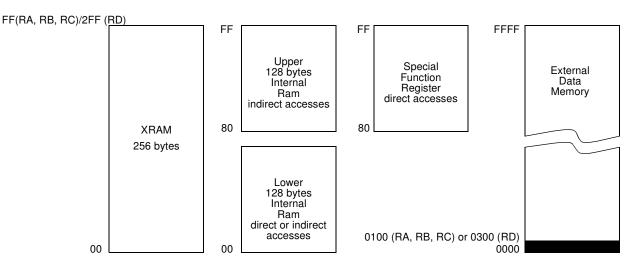

### 6.1 Expanded RAM (XRAM)

The TS80C51Rx2 provide additional Bytes of ramdom access memory (RAM) space for increased data parameter handling and high level language usage.

RA2, RB2 and RC2 devices have 256 bytes of expanded RAM, from 00H to FFH in external data space; RD2 devices have 768 bytes of expanded RAM, from 00H to 2FFH in external data space.

The TS80C51Rx2 has internal data memory that is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register. (See Table 6-1.)

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

- Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data, accesses the SFR at location 0A0H (which is P2).

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

- The 256 or 768 XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first 256 or 768 bytes of external data memory.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, <u>R1</u> of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (i.e. 0100H to FFFFH) (higher than 2FFH (i.e. 0300H to FFFFH for RD devices) will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, so with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Refer to Figure 6-1. For RD devices, accesses to expanded RAM from 100H to 2FFH can only be done thanks to the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the highorder eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight

address bits (DPL) with data. MOVX @ Ri and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

### Figure 6-1. Internal and External Data Memory Address

### Table 6-1. Auxiliary Register AUXR

| AUXR<br>Address 08EH |                  |                                                                                        | -       | -         | -        | -        | -         | -     | EXTRAM | AO     |  |

|----------------------|------------------|----------------------------------------------------------------------------------------|---------|-----------|----------|----------|-----------|-------|--------|--------|--|

|                      | Reset value      | e                                                                                      | Х       | Х         | Х        | х        | Х         | х     | 0      | 0      |  |

| Symbol               | Function         | Function                                                                               |         |           |          |          |           |       |        |        |  |

| -                    | Not implemente   | Not implemented, reserved for future use. (1)                                          |         |           |          |          |           |       |        |        |  |

| AO                   | Disable/Enable   | Disable/Enable ALE                                                                     |         |           |          |          |           |       |        |        |  |

|                      | AO               | ALLE is emitted at a constant rate of $1/6$ the oscillator frequency (or $1/3$ if X2 n |         |           |          |          |           |       |        |        |  |

|                      | 0                |                                                                                        |         |           |          |          |           |       |        | 2 mode |  |

|                      | 1                | ALE is                                                                                 | active  | only duri | ng a MO' | VX or MO | VC instru | ction |        |        |  |

| EXTRAM               | Internal/Externa | I RAM (                                                                                | 00H-F   | FH) acce  | ss using | MOVX @   | Ri/ @ DF  | PTR   |        |        |  |

|                      | EXTRAM           | Operat                                                                                 | ting Mo | ode       |          |          |           |       |        |        |  |

|                      | 0                | Interna                                                                                | al XRA  | M access  | using M  | OVX @ R  | i/ @ DPT  | R     |        |        |  |

|                      | 1                | Extern                                                                                 | al data | i memory  | access   |          |           |       |        |        |  |

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 6             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 5             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 4             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 3             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 2             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 1             | T2OE            | Timer 2 Output Enable bit<br>Clear to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |

| 0             | DCEN            | Down Counter Enable bit<br>Clear to disable timer 2 as up/down counter.<br>Set to enable timer 2 as up/down counter.         |

Reset Value = XXXX XX00b

Not bit addressable

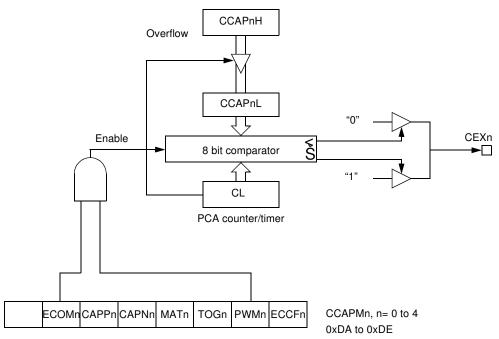

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output (See Table 6-8 & Table 6-9)

Table 6-8.

CCAPnH: PCA Modules Capture/Compare Registers High

| CCAP0H=0FAH<br>CCAP1H=0FBH<br>CCAP2H=0FCH<br>CCAP3H=0FDH<br>CCAP4H=0FEH |

|-------------------------------------------------------------------------|

|                                                                         |

|             | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|---|---|---|---|---|---|---|

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Table 6-9.

CCAPnL: PCA Modules Capture/Compare Registers Low

| CCAPnL Address<br>n = 0 - 4 |

|-----------------------------|

| 11 = 0 - 4                  |

| CCAP2L=0ECH |

|-------------|

| CCAP3L=0EDH |

| CCAP4L=0EEH |

CCAP0L=0EAH

|             | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|---|---|---|---|---|---|---|

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### Table 6-10.CH: PCA Counter High

CH Address 0F9H

| Н |             |   |   |   |   |   |   |   |   |

|---|-------------|---|---|---|---|---|---|---|---|

|   |             | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|   | Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### Table 6-11. CL: PCA Counter Low

CL

Address 0E9H

|             | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|---|---|---|---|---|---|---|

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### 6.3.1 PCA Capture Mode

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (Refer to Figure 6-6).

### Figure 6-9. PCA PWM Mode

### 6.3.5 PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 6-7 shows a diagram of how the watchdog works. The user preloads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. Periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. Disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

## 6.9 ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS8xC51Rx2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C51Rx2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the TS80C51Rx2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

Table 6-23.

External Pin Status during ONCE Mode

### 8.2.4 Verify Algorithm

Refer to Section "Verify algorithm".

# **11. Electrical Characteristics**

### 11.1 Absolute Maximum Ratings

|                                                                        | *NOTICE: | Stresses at or above those listed under " Abso-    |

|------------------------------------------------------------------------|----------|----------------------------------------------------|

|                                                                        |          | lute Maximum Ratings" may cause permanent          |

| Ambiant Temperature Under Bias:                                        |          | damage to the device. This is a stress rating only |

| C = commercial0°C to 70°C                                              |          | and functional operation of the device at these or |

| I = industrial40°C to 85°C                                             |          | any other conditions above those indicated in the  |

| Storage Temperature                                                    |          | operational sections of this specification is not  |

| Voltage on V <sub>CC</sub> to V <sub>SS</sub> 0.5 V to + 7 V           |          | implied. Exposure to absolute maximum rating       |

| Voltage on Any Pin to V <sub>SS</sub> 0.5 V to V <sub>CC</sub> + 0.5 V |          | conditions may affect device reliability.          |

| Power Dissipation 1 W                                                  |          | Power dissipation is based on the maximum          |

|                                                                        |          | allowable die temperature and the thermal resis-   |

|                                                                        |          | tance of the package.                              |

### 11.2 Power Consumption Measurement

Since the introduction of the first C51 devices, every manufacturer made operating lcc measurements under reset, which made sense for the designs were the CPU was running under reset. In Atmel new devices, the CPU is no more active during reset, so the power consumption is very low but is not really representative of what will happen in the customer system. That's why, while keeping measurements under Reset, Atmel presents a new way to measure the operating lcc:

Using an internal test ROM, the following code is executed:

Label:

Ports 1, 2, 3 are disconnected, Port 0 is tied to FFh, EA = Vcc, RST = Vss, XTAL2 is not connected and XTAL1 is driven by the clock.

SJMP Label (80 FE)

This is much more representative of the real operating lcc.

### 11.3 DC Parameters for Standard Voltage

TA = 0°C to +70°C;  $V_{SS} = 0$  V;  $V_{CC} = 5$  V ± 10%; F = 0 to 40 MHz. TA = -40°C to +85°C;  $V_{SS} = 0$  V;  $V_{CC} = 5$  V ± 10%; F = 0 to 40 MHz.

Table 11-1. DC Parameters in Standard Voltage

| Symbol           | Parameter                                              | Min                       | Тур | Max                       | Unit        | Test Conditions                                                                                                      |

|------------------|--------------------------------------------------------|---------------------------|-----|---------------------------|-------------|----------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                      | -0.5                      |     | 0.2 V <sub>CC</sub> - 0.1 | V           |                                                                                                                      |

| V <sub>IH</sub>  | Input High Voltage except XTAL1, RST                   | 0.2 V <sub>CC</sub> + 0.9 |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                      |

| V <sub>IH1</sub> | Input High Voltage, XTAL1, RST                         | 0.7 V <sub>CC</sub>       |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                      |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3, 4, 5 <sup>(6)</sup> |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} I_{OL} &= 100 \; \mu A^{(4)} \\ I_{OL} &= 1.6 \; m A^{(4)} \\ I_{OL} &= 3.5 \; m A^{(4)} \end{split}$ |

| V <sub>OL1</sub> | Output Low Voltage, port 0 <sup>(6)</sup>              |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $I_{OL} = 200 \ \mu A^{(4)}$ $I_{OL} = 3.2 \ m A^{(4)}$ $I_{OL} = 7.0 \ m A^{(4)}$                                   |

| V <sub>OL2</sub> | Output Low Voltage, ALE, PSEN                          |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} I_{OL} &= 100 \; \mu A^{(4)} \\ I_{OL} &= 1.6 \; m A^{(4)} \\ I_{OL} &= 3.5 \; m A^{(4)} \end{split}$ |

| Table 11-1. | DC Parameters in Standard Voltage  |

|-------------|------------------------------------|

|             | 20 · alamotoro in otanda a rollago |

| Symbol                            | Parameter                                                    | Min                                                                     | Тур               | Мах                                                 | Unit        | Test Conditions                                                                                                                    |

|-----------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|-----------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3, 4, 5                     | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                     | V<br>V<br>V | I <sub>OH</sub> = -10 μA<br>I <sub>OH</sub> = -30 μA<br>I <sub>OH</sub> = -60 μA<br>V <sub>CC</sub> = 5 V ± 10%                    |

| V <sub>OH1</sub>                  | Output High Voltage, port 0                                  | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                     | V<br>V<br>V | $\begin{split} I_{OH} &= -200 \; \mu A \\ I_{OH} &= -3.2 \; m A \\ I_{OH} &= -7.0 \; m A \\ V_{CC} &= 5 \; V \pm 10\% \end{split}$ |

| V <sub>OH2</sub>                  | Output High Voltage,ALE, PSEN                                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                     | V<br>V<br>V | $I_{OH} = -100 \ \mu A$<br>$I_{OH} = -1.6 \ m A$<br>$I_{OH} = -3.5 \ m A$<br>$V_{CC} = 5 \ V \pm 10\%$                             |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                        | 50                                                                      | 90 (5)            | 200                                                 | kΩ          |                                                                                                                                    |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2, 3, 4, 5                  |                                                                         |                   | -50                                                 | μA          | Vin = 0.45 V                                                                                                                       |

| I <sub>LI</sub>                   | Input Leakage Current                                        |                                                                         |                   | ±10                                                 | μA          | 0.45 V < Vin < V <sub>CC</sub>                                                                                                     |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3, 4, 5       |                                                                         |                   | -650                                                | μA          | Vin = 2.0 V                                                                                                                        |

| C <sub>IO</sub>                   | Capacitance of I/O Buffer                                    |                                                                         |                   | 10                                                  | pF          | Fc = 1 MHz<br>Ta = 25°C                                                                                                            |

| I <sub>PD</sub>                   | Power-down Current                                           |                                                                         | 20 <sup>(5)</sup> | 50                                                  | μA          | $2.0 \text{ V} < \text{V}_{\text{CC}} < 5.5 \text{ V}^{(3)}$                                                                       |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: (7)            |                                                                         |                   | 1 + 0.4 Freq<br>(MHz)<br>@12MHz 5.8<br>@16MHz 7.4   | mA          | V <sub>CC</sub> = 5.5 V <sup>(1)</sup>                                                                                             |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: (7)            |                                                                         |                   | 3 + 0.6 Freq<br>(MHz)<br>@12MHz 10.2<br>@16MHz 12.6 | mA          | V <sub>CC</sub> = 5.5 V <sup>(8)</sup>                                                                                             |

| I <sub>CC</sub><br>idle           | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                                                                         |                   | 0.25+0.3 Freq<br>(MHz)<br>@12MHz 3.9<br>@16MHz 5.1  | mA          | V <sub>CC</sub> = 5.5 V <sup>(2)</sup>                                                                                             |

### External Program Memory Characteristics Table 11-5. Symbol Description 11.5.2

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| T <sub>PXIZ</sub> | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

Table 11-6.

AC Parameters for Fix Clock

| Speed             |     | M<br>MHz | X2 n<br>30 l | V<br>node<br>MHz<br>z equiv. | stan<br>mo | V<br>dard<br>ode<br>MHz | X2 n<br>20 l | L<br>node<br>MHz<br>z equiv. | stan<br>mo | L<br>dard<br>ode<br>MHz | Units |

|-------------------|-----|----------|--------------|------------------------------|------------|-------------------------|--------------|------------------------------|------------|-------------------------|-------|

| Symbol            | Min | Max      | Min          | Max                          | Min        | Max                     | Min          | Max                          | Min        | Max                     |       |

| Т                 | 25  |          | 33           |                              | 25         |                         | 50           |                              | 33         |                         | ns    |

| T <sub>LHLL</sub> | 40  |          | 25           |                              | 42         |                         | 35           |                              | 52         |                         | ns    |

| T <sub>AVLL</sub> | 10  |          | 4            |                              | 12         |                         | 5            |                              | 13         |                         | ns    |

| T <sub>LLAX</sub> | 10  |          | 4            |                              | 12         |                         | 5            |                              | 13         |                         | ns    |

| T <sub>LLIV</sub> |     | 70       |              | 45                           |            | 78                      |              | 65                           |            | 98                      | ns    |

| T <sub>LLPL</sub> | 15  |          | 9            |                              | 17         |                         | 10           |                              | 18         |                         | ns    |

| T <sub>PLPH</sub> | 55  |          | 35           |                              | 60         |                         | 50           |                              | 75         |                         | ns    |

| T <sub>PLIV</sub> |     | 35       |              | 25                           |            | 50                      |              | 30                           |            | 55                      | ns    |

| T <sub>PXIX</sub> | 0   |          | 0            |                              | 0          |                         | 0            |                              | 0          |                         | ns    |

| T <sub>PXIZ</sub> |     | 18       |              | 12                           |            | 20                      |              | 10                           |            | 18                      | ns    |

| T <sub>AVIV</sub> |     | 85       |              | 53                           |            | 95                      |              | 80                           |            | 122                     | ns    |

| T <sub>PLAZ</sub> |     | 10       |              | 10                           |            | 10                      |              | 10                           |            | 10                      | ns    |

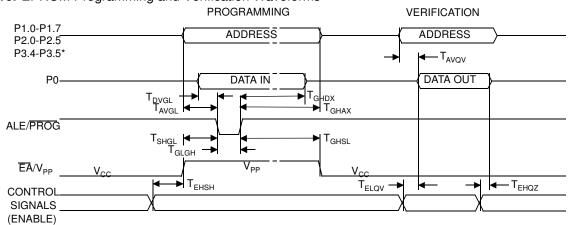

### 11.5.9 EPROM Programming and Verification Characteristics

TA = 21°C to 27°C; V<sub>SS</sub> = 0V; V<sub>CC</sub> = 5V  $\pm$  10% while programming. V<sub>CC</sub> = operating range while

| Symbol              | Parameter                         | Min                  | Max                  | Units |

|---------------------|-----------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage        | 12.5                 | 13                   | V     |

| I <sub>PP</sub>     | Programming Supply Current        |                      | 75                   | mA    |

| 1/T <sub>CLCL</sub> | Oscillator Frquency               | 4                    | 6                    | MHz   |

| T <sub>AVGL</sub>   | Address Setup to PROG Low         | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHAX</sub>   | Adress Hold after PROG            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>DVGL</sub>   | Data Setup to PROG Low            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHDX</sub>   | Data Hold after PROG              | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>EHSH</sub>   | (Enable) High to V <sub>PP</sub>  | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low | 10                   |                      | μs    |

| T <sub>GHSL</sub>   | V <sub>PP</sub> Hold after PROG   | 10                   |                      | μs    |

| T <sub>GLGH</sub>   | PROG Width                        | 90                   | 110                  | μs    |

| T <sub>AVQV</sub>   | Address to Valid Data             |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>ELQV</sub>   | ENABLE Low to Data Valid          |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>EHQZ</sub>   | Data Float after ENABLE           | 0                    | 48 T <sub>CLCL</sub> |       |

verifying

### 11.5.10 EPROM Programming and Verification Waveforms

Figure 11-10. EPROM Programming and Verification Waveforms

\* 8KB: up to P2.4, 16KB: up to P2.5, 32KB: up to P3.4, 64KB: up to P3.5

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |  |  |  |  |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|--|--|--|--|

| TS87C51RC2-MCA   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MCB   | _             |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MCE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MIA   | _             |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MIB   | _             |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-MIE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LCA   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LCB   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LCE   |               |                |                    | <b>T</b> E         |         |         |  |  |  |  |

| TS87C51RC2-LIA   |               |                | OBSOLE             | IE                 |         |         |  |  |  |  |

| TS87C51RC2-LIB   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-LIE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VCA   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VCB   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VCE   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VIA   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VIB   |               |                |                    |                    |         |         |  |  |  |  |

| TS87C51RC2-VIE   |               |                |                    |                    |         |         |  |  |  |  |

|                  |               |                |                    |                    |         |         |  |  |  |  |

| AT87C51RC2-3CSUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |  |  |  |  |

| AT87C51RC2-SLSUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |  |  |  |  |

| AT87C51RC2-RLTUM | OTP 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |  |  |  |  |

| AT87C51RC2-3CSUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |  |  |  |  |

| AT87C51RC2-SLSUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |  |  |  |  |

| AT87C51RC2-RLTUL | OTP 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |  |  |  |  |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS87C51RD2-MCA   |               |                | 1                  |                    | •       |         |

| TS87C51RD2-MCB   |               |                |                    |                    |         |         |

| TS87C51RD2-MCE   |               |                |                    |                    |         |         |

| TS87C51RD2-MIA   |               |                |                    |                    |         |         |

| TS87C51RD2-MIB   |               |                |                    |                    |         |         |

| TS87C51RD2-MIE   |               |                |                    |                    |         |         |

| TS87C51RD2-LCA   |               |                |                    |                    |         |         |

| TS87C51RD2-LCB   |               |                |                    |                    |         |         |

| TS87C51RD2-LCE   |               |                |                    |                    |         |         |

| TS87C51RD2-LIA   |               |                | OBSOLE             | TE                 |         |         |

| TS87C51RD2-LIB   |               |                |                    |                    |         |         |

| TS87C51RD2-LIE   |               |                |                    |                    |         |         |

| TS87C51RD2-VCA   |               |                |                    |                    |         |         |

| TS87C51RD2-VCB   |               |                |                    |                    |         |         |

| TS87C51RD2-VCE   |               |                |                    |                    |         |         |

| TS87C51RD2-VCL   |               |                |                    |                    |         |         |

| TS87C51RD2-VIA   |               |                |                    |                    |         |         |

| TS87C51RD2-VIB   |               |                |                    |                    |         |         |

| TS87C51RD2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT87C51RD2-3CSUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RD2-SLSUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RD2-RLTUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT87C51RD2-3CSUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RD2-SLSUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RD2-RLTUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

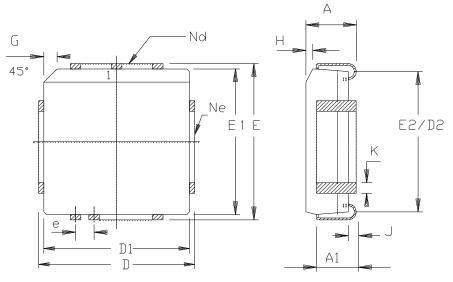

# 13. Package Drawings

# 13.1 PLCC44

|    | Ν      | 1M ·  | ΙN    | СН    |

|----|--------|-------|-------|-------|

| A  | 4.20   | 4. 57 | . 165 | . 180 |

| A1 | 2, 29  | 3.04  | . 090 | . 120 |

| D  | 17.40  | 17.65 | . 685 | . 695 |

| D1 | 16.44  | 16.66 | . 647 | . 656 |

| D5 | 14.99  | 16.00 | . 590 | . 630 |

| E  | 17.40  | 17.65 | . 685 | . 695 |

| E1 | 16.44  | 16.66 | . 647 | . 656 |

| E5 | 14.99  | 16.00 | . 590 | . 630 |

| e  | 1.27   | BSC   | . 050 | BSC   |

| G  | 1.07   | 1.22  | . 042 | . 048 |

| н  | 1.07   | 1.42  | . 042 | .056  |

| J  | 0.51   | -     | . 020 | -     |

| К  | 0.33   | 0.53  | . 013 | . 021 |

| Nd | 1      | 1     | 1     | 1     |

| Ne | 1      | 1     | 1     | 1     |

| P  | KG STD | 00    |       |       |

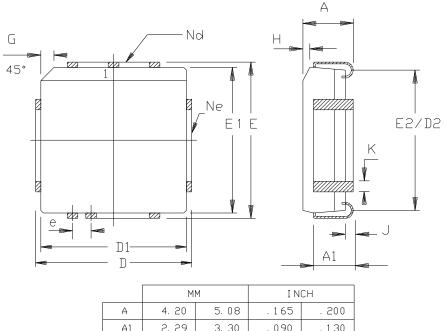

## 13.5 PLCC68

68 PINS PLCC

|    | IMIM   |        | INCH  |        |

|----|--------|--------|-------|--------|

| A  | 4.20   | 5.08   | . 165 | . 200  |

| A1 | 2, 29  | 3.30   | . 090 | . 1 30 |

| D  | 25.02  | 25. 27 | . 985 | . 995  |

| D1 | 24.13  | 24.33  | . 950 | . 958  |

| D2 | 22. 61 | 23. 62 | . 890 | . 930  |

| E  | 25.02  | 25. 27 | . 985 | . 995  |

| E1 | 24.13  | 24.33  | . 950 | . 958  |

| E5 | 22. 61 | 23. 62 | . 890 | . 930  |

| e  | 1.27   | BSC    | . 050 | BSC    |

| G  | 1.07   | 1.22   | . 042 | . 048  |

| н  | 1.07   | 1.42   | . 042 | .056   |

| J  | 0.51   | -      | . 020 | -      |

| К  | 0.33   | 0.53   | . 013 | . 021  |

| Nd | 17     |        | 17    |        |

| Ne | 17     |        | 17    |        |

| P  | KG STD |        |       |        |

## 14. Datasheet Revision History

## 14.1 Changes from 4188E to 4188F

- 1. Removed TS80C51RD2 and AT80C51RD2 from "Ordering Information" on page 73.

- 2. Removed non-green part numbers from ordering information.