Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40/30MHz                                                                 |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIL                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts80c51ra2-via |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Bit<br>addressable                 | Non Bit addres     | Non Bit addressable |                     |                      |                      |                      |                                     |     |  |  |  |

|-----|------------------------------------|--------------------|---------------------|---------------------|----------------------|----------------------|----------------------|-------------------------------------|-----|--|--|--|

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |  |  |

| F8h |                                    | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAPL2H<br>XXXX XXXX | CCAPL3H<br>XXXX XXXX | CCAPL4H<br>XXXX XXXX |                                     | FFh |  |  |  |

| F0h | B<br>0000 0000                     |                    |                     |                     |                      |                      |                      |                                     | F7h |  |  |  |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                                     | EFh |  |  |  |

| E0h | ACC<br>0000 0000                   |                    |                     |                     |                      |                      |                      |                                     | E7h |  |  |  |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000  | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                                     | DFh |  |  |  |

| D0h | PSW<br>0000 0000                   |                    |                     |                     |                      |                      |                      |                                     | D7h |  |  |  |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                                     | CFh |  |  |  |

| C0h | P4 bit<br>addressable<br>1111 1111 |                    |                     |                     |                      |                      |                      | P5 byte<br>addressable<br>1111 1111 | C7h |  |  |  |

| B8h | IP<br>X000 000                     | SADEN<br>0000 0000 |                     |                     |                      |                      |                      |                                     | BFh |  |  |  |

| B0h | P3<br>1111 1111                    |                    |                     |                     |                      |                      |                      | IPH<br>X000 0000                    | B7h |  |  |  |

| A8h | IE<br>0000 0000                    | SADDR<br>0000 0000 |                     |                     |                      |                      |                      |                                     | AFh |  |  |  |

| A0h | P2<br>1111 1111                    |                    | AUXR1<br>XXXX0XX0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000                 | A7h |  |  |  |

| 98h | SCON<br>0000 0000                  | SBUF<br>XXXX XXXX  |                     |                     |                      |                      |                      |                                     | 9Fh |  |  |  |

| 90h | P1<br>1111 1111                    |                    |                     |                     |                      |                      |                      |                                     | 97h |  |  |  |

| 88h | TCON<br>0000 0000                  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XXXXXX00     | CKCON<br>XXXX XXX0                  | 8Fh |  |  |  |

| 80h | P0<br>1111 1111                    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000                   | 87h |  |  |  |

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                                 |     |  |  |  |

Table 4-1.

All SFRs with their address and their reset value

reserved

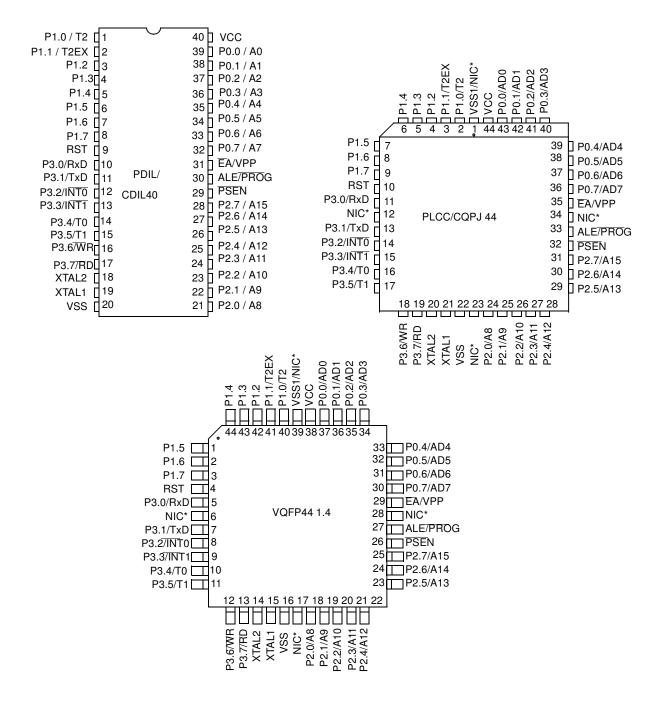

## 5. Pin Configuration

\*NIC: No Internal Connection

| PSEN   | 67 | 55 |

|--------|----|----|

| EA/VPP | 2  | 58 |

| XTAL1  | 49 | 38 |

| XTAL2  | 48 | 37 |

| P4.0   | 20 | 11 |

| P4.1   | 24 | 15 |

| P4.2   | 26 | 17 |

| P4.3   | 44 | 33 |

| P4.4   | 46 | 35 |

| P4.5   | 50 | 39 |

| P4.6   | 53 | 42 |

| P4.7   | 57 | 46 |

| P5.0   | 60 | 49 |

| P5.1   | 62 | 51 |

| P5.2   | 63 | 52 |

| P5.3   | 7  | 62 |

| P5.4   | 8  | 63 |

| P5.5   | 10 | 1  |

| P5.6   | 13 | 4  |

| P5.7   | 16 | 7  |

## 6. Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare, search ...) are well served by using one data pointer as a 'source' pointer and the other one as a "destination" pointer.

#### ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Destroys DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added 00A2 AUXR1 EQU 0A2H ; 0000 909000MOV DPTR, #SOURCE ; address of SOURCE 0003 05A2 INC AUXR1 ; switch data pointers 0005 90A000 MOV DPTR, #DEST ; address of DEST 0008 LOOP: 0008 05A2 INC AUXR1 ; switch data pointers 000A EO MOVX A, @DPTR ; get a byte from SOURCE 000B A3 INC DPTR ; increment SOURCE address 000C 05A2 INC AUXR1 ; switch data pointers 000E FO MOVX @DPTR, A ; write the byte to DEST 000F A3 INC DPTR ; increment DEST address 0010 70F6JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

### 6.1 Expanded RAM (XRAM)

The TS80C51Rx2 provide additional Bytes of ramdom access memory (RAM) space for increased data parameter handling and high level language usage.

RA2, RB2 and RC2 devices have 256 bytes of expanded RAM, from 00H to FFH in external data space; RD2 devices have 768 bytes of expanded RAM, from 00H to 2FFH in external data space.

The TS80C51Rx2 has internal data memory that is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register. (See Table 6-1.)

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

- Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data, accesses the SFR at location 0A0H (which is P2).

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

- The 256 or 768 XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first 256 or 768 bytes of external data memory.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, <u>R1</u> of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (i.e. 0100H to FFFFH) (higher than 2FFH (i.e. 0300H to FFFFH for RD devices) will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, so with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Refer to Figure 6-1. For RD devices, accesses to expanded RAM from 100H to 2FFH can only be done thanks to the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the highorder eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight

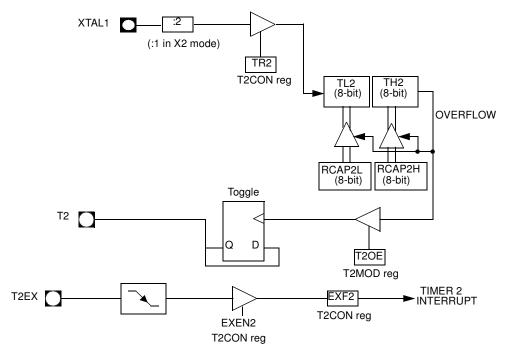

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

#### **Figure 6-3.** Clock-Out Mode $C/\overline{T2} = 0$

| Table 6-2. |      | T2CON Register<br>T2CON - Timer 2 Control Register (C8h) |      |       |     |       |         |  |  |  |

|------------|------|----------------------------------------------------------|------|-------|-----|-------|---------|--|--|--|

| 7          | 6    | 5                                                        | 4    | 3     | 2   | 1     | 0       |  |  |  |

| TF2        | EXF2 | RCLK                                                     | TCLK | EXEN2 | TR2 | C/T2# | CP/RL2# |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 6             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 5             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 4             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 3             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 2             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                       |

| 1             | T2OE            | Timer 2 Output Enable bit<br>Clear to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |

| 0             | DCEN            | Down Counter Enable bit<br>Clear to disable timer 2 as up/down counter.<br>Set to enable timer 2 as up/down counter.         |

Reset Value = XXXX XX00b

Not bit addressable

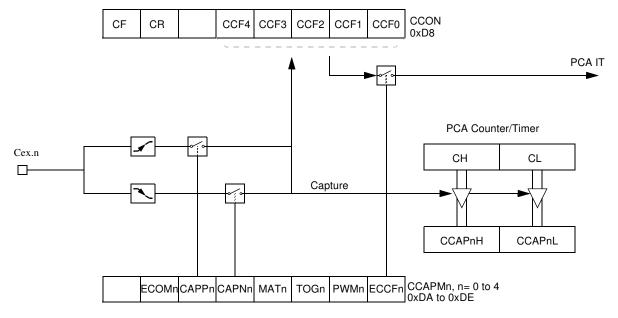

#### Figure 6-6. PCA Capture Mode

#### 6.3.2 16-bit Software Timer/ Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (See Figure 6-7).

## 6.4 TS80C51Rx2 Serial I/O Port

The serial I/O port in the TS80C51Rx2 is compatible with the serial I/O port in the 80C52.

It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- · Automatic address recognition

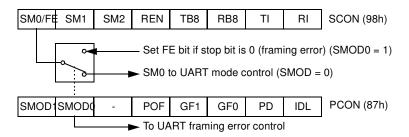

#### 6.4.1 Framing Error Detection

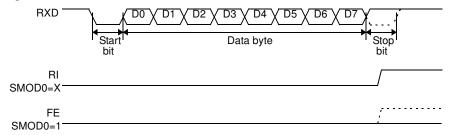

Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 6-10).

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 6-14.) bit is set.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 6-11 and Figure 6-12).

#### Table 6-12. SADEN - Slave Address Mask Register (B9h)

| 7            | 6                        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------------|--------------------------|---|---|---|---|---|---|--|

|              |                          |   |   |   |   |   |   |  |

| Reset Value  | Reset Value = 0000 0000b |   |   |   |   |   |   |  |

| Not bit addr | essable                  |   |   |   |   |   |   |  |

#### Table 6-13. SADDR - Slave Address Register (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|   |   |   | • | • | • | • | · |

Reset Value = 0000 0000b

Not bit addressable

## Table 6-14. SCON Register

SCON - Serial Control Register (98h)

| 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|--------|-----|-----|-----|-----|-----|----|----|

| FE/SM0 | SM1 | SM2 | REN | TB8 | RB8 | ТІ | RI |

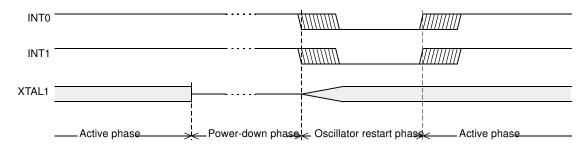

Figure 6-14. Power-Down Exit Waveform

Exit from power-down by reset redefines all the SFRs, exit from power-down by external interrupt does no affect the SFRs.

Exit from power-down by either reset or external interrupt does not affect the internal RAM content.

Note: If idle mode is activated with power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

**Table 6-20.** The state of ports during idle and power-down mode

| Mode       | Program<br>Memory | ALE | PSEN | PORT0      | PORT1     | PORT2     | PORT3     |

|------------|-------------------|-----|------|------------|-----------|-----------|-----------|

| Idle       | Internal          | 1   | 1    | Port Data* | Port Data | Port Data | Port Data |

| Idle       | External          | 1   | 1    | Floating   | Port Data | Address   | Port Data |

| Power-down | Internal          | 0   | 0    | Port Data* | Port Data | Port Data | Port Data |

| Power-down | External          | 0   | 0    | Floating   | Port Data | Port Data | Port Data |

\* Port 0 can force a "zero" level. A "one" will leave port floating.

## 7. Power-Off Flag

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (See Table 7-1). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

The POF value is only relevant with a Vcc range from 4.5V to 5.5V. For lower Vcc value, reading POF bit will return indeterminate value.

| 7             | 6               | 5                            | 4                                                                                                                                                                  | 3                                | 2   | 1  | 0   |  |  |

|---------------|-----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----|----|-----|--|--|

| SMOD1         | SMOD0           | -                            | POF                                                                                                                                                                | GF1                              | GF0 | PD | IDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                   | Description                                                                                                                                                        |                                  |     |    |     |  |  |

| 7             | SMOD1           |                              | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                                                                        |                                  |     |    |     |  |  |

| 6             | SMOD0           | Clear to se                  | Serial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register.                                                   |                                  |     |    |     |  |  |

| 5             | -               | <b>Reserved</b><br>The value | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                    |                                  |     |    |     |  |  |

| 4             | POF             | Clear to re                  | Power-Off Flag<br>Clear to recognize next reset type.<br>Set by hardware when V <sub>CC</sub> rises from 0 to its nominal voltage. Can also be set by<br>software. |                                  |     |    |     |  |  |

| 3             | GF1             | Cleared by                   |                                                                                                                                                                    | ral purpose usa<br>urpose usage. | ge. |    |     |  |  |

| 2             | GF0             | Cleared by                   |                                                                                                                                                                    | ral purpose usa<br>urpose usage. | ge. |    |     |  |  |

| 1             | PD              | Cleared by                   | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                     |                                  |     |    |     |  |  |

| 0             | IDL             | Clear by ha                  | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                                      |                                  |     |    |     |  |  |

Table 7-1.PCON RegisterPCON - Power Control Register (87h)

Reset Value = 00X1 0000b

Not bit addressable

### 7.1 Reduced EMI Mode

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

| 7             | 6               | 5                                                                                                                                  | 4                                                                                      | 3               | 2                 | 1      | 0  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|-------------------|--------|----|--|--|

| -             | -               | -                                                                                                                                  | -                                                                                      | -               | -                 | EXTRAM | AO |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                        | Description                                                                            |                 |                   |        |    |  |  |

| 7             | -               | Reserved<br>The value read                                                                                                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.        |                 |                   |        |    |  |  |

| 6             | -               | Reserved<br>The value read                                                                                                         | d from this bit i                                                                      | s indeterminate | e. Do not set thi | s bit. |    |  |  |

| 5             | -               | Reserved<br>The value read                                                                                                         | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |        |    |  |  |

| 4             | -               | Reserved<br>The value read                                                                                                         | d from this bit i                                                                      | s indeterminate | e. Do not set thi | s bit. |    |  |  |

| 3             | -               | Reserved<br>The value read                                                                                                         | d from this bit i                                                                      | s indeterminate | e. Do not set thi | s bit. |    |  |  |

| 2             | -               | Reserved<br>The value read                                                                                                         | d from this bit i                                                                      | s indeterminate | e. Do not set thi | s bit. |    |  |  |

| 1             | EXTRAM          | EXTRAM bit<br>See Table 6-1                                                                                                        |                                                                                        |                 |                   |        |    |  |  |

| 0             | AO              | ALE Output bit<br>Clear to restore ALE operation during internal fetches.<br>Set to disable ALE operation during internal fetches. |                                                                                        |                 |                   |        |    |  |  |

Table 7-2.AUXR RegisterAUXR - Auxiliary Register (8Eh)

Reset Value = XXXX XX00b Not bit addressable

## 8. TS83C51RB2/RC2/RD2 ROM

## 8.1 ROM Structure

The TS83C51RB2/RC2/RD2 ROM memory is divided in three different arrays:

- the code array:16/32/64 Kbytes.

- the encryption array:64 bytes.

- the signature array:4 bytes.

## 8.2 ROM Lock System

The program Lock system, when programmed, protects the on-chip program against software piracy.

## 8.2.1 8.2.1 Encryption Array

Within the ROM array are 64 bytes of encryption array that are initially unprogrammed (all FF's). Every time a byte is addressed during program verify, 6 address lines are used to select a byte of the encryption array. This byte is then exclusive-NOR'ed (XNOR) with the code byte, creating an encrypted verify byte. The algorithm, with the encryption array in the unprogrammed state, will return the code in its original, unmodified form.

When using the encryption array, one important factor needs to be considered. If a byte has the value FFh, verifying the byte will produce the encryption byte value. If a large block (>64 bytes) of code is left unprogrammed, a verification routine will display the content of the encryption array. For this reason all the unused code bytes should be programmed with random values. This will ensure program protection.

## 8.2.2 Program Lock Bits

The lock bits when programmed according to Table 8-1. will provide different level of protection for the on-chip code and data.

|                   | Program Lock Bits |     |     |                                                                                                                                                                                                       |

|-------------------|-------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security<br>level | LB1               | LB2 | LB3 | Protection Description                                                                                                                                                                                |

| 1                 | U                 | U   | U   | No program lock features enabled. Code verify will still be encrypted<br>by the encryption array if programmed. MOVC instruction executed<br>from external program memory returns non encrypted data. |

| 2                 | Р                 | U   | U   | MOVC instruction executed from external program memory are disabled from fetching code bytes from internal memory, EA is sampled and latched on reset.                                                |

| 3                 | U                 | Р   | U   | Same as level 1+ Verify disable.<br>This security level is only available for 51RDX2 devices.                                                                                                         |

| Table 8-1. | Program Lock bits |

|------------|-------------------|

|            |                   |

U: unprogrammed P: programmed

## 8.2.3 Signature bytes

The TS83C51RB2/RC2/RD2 contains 4 factory programmed signatures bytes. To read these bytes, perform the process described in section 8.3.

## **11. Electrical Characteristics**

## 11.1 Absolute Maximum Ratings

|                                                                        | *NOTICE: | Stresses at or above those listed under " Abso-    |

|------------------------------------------------------------------------|----------|----------------------------------------------------|

|                                                                        |          | lute Maximum Ratings" may cause permanent          |

| Ambiant Temperature Under Bias:                                        |          | damage to the device. This is a stress rating only |

| C = commercial0°C to 70°C                                              |          | and functional operation of the device at these or |

| I = industrial40°C to 85°C                                             |          | any other conditions above those indicated in the  |

| Storage Temperature                                                    |          | operational sections of this specification is not  |

| Voltage on V <sub>CC</sub> to V <sub>SS</sub> 0.5 V to + 7 V           |          | implied. Exposure to absolute maximum rating       |

| Voltage on Any Pin to V <sub>SS</sub> 0.5 V to V <sub>CC</sub> + 0.5 V |          | conditions may affect device reliability.          |

| Power Dissipation 1 W                                                  |          | Power dissipation is based on the maximum          |

|                                                                        |          | allowable die temperature and the thermal resis-   |

|                                                                        |          | tance of the package.                              |

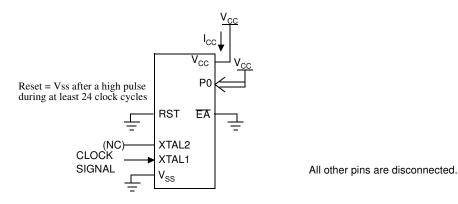

### 11.2 Power Consumption Measurement

Since the introduction of the first C51 devices, every manufacturer made operating lcc measurements under reset, which made sense for the designs were the CPU was running under reset. In Atmel new devices, the CPU is no more active during reset, so the power consumption is very low but is not really representative of what will happen in the customer system. That's why, while keeping measurements under Reset, Atmel presents a new way to measure the operating lcc:

Using an internal test ROM, the following code is executed:

Label:

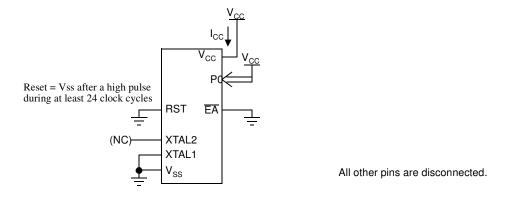

Ports 1, 2, 3 are disconnected, Port 0 is tied to FFh, EA = Vcc, RST = Vss, XTAL2 is not connected and XTAL1 is driven by the clock.

SJMP Label (80 FE)

This is much more representative of the real operating lcc.

### 11.3 DC Parameters for Standard Voltage

TA = 0°C to +70°C;  $V_{SS} = 0$  V;  $V_{CC} = 5$  V ± 10%; F = 0 to 40 MHz. TA = -40°C to +85°C;  $V_{SS} = 0$  V;  $V_{CC} = 5$  V ± 10%; F = 0 to 40 MHz.

Table 11-1. DC Parameters in Standard Voltage

| Symbol           | Parameter                                              | Min                       | Тур | Max                       | Unit        | Test Conditions                                                                                                      |

|------------------|--------------------------------------------------------|---------------------------|-----|---------------------------|-------------|----------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                      | -0.5                      |     | 0.2 V <sub>CC</sub> - 0.1 | V           |                                                                                                                      |

| V <sub>IH</sub>  | Input High Voltage except XTAL1, RST                   | 0.2 V <sub>CC</sub> + 0.9 |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                      |

| V <sub>IH1</sub> | Input High Voltage, XTAL1, RST                         | 0.7 V <sub>CC</sub>       |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                      |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3, 4, 5 <sup>(6)</sup> |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} I_{OL} &= 100 \; \mu A^{(4)} \\ I_{OL} &= 1.6 \; m A^{(4)} \\ I_{OL} &= 3.5 \; m A^{(4)} \end{split}$ |

| V <sub>OL1</sub> | Output Low Voltage, port 0 <sup>(6)</sup>              |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $I_{OL} = 200 \ \mu A^{(4)}$ $I_{OL} = 3.2 \ m A^{(4)}$ $I_{OL} = 7.0 \ m A^{(4)}$                                   |

| V <sub>OL2</sub> | Output Low Voltage, ALE, PSEN                          |                           |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} I_{OL} &= 100 \; \mu A^{(4)} \\ I_{OL} &= 1.6 \; m A^{(4)} \\ I_{OL} &= 3.5 \; m A^{(4)} \end{split}$ |

### 11.4 DC Parameters for Low Voltage

TA = 0°C to +70°C; V<sub>SS</sub> = 0 V; V<sub>CC</sub> = 2.7 V to 5.5 V  $\pm$  10%; F = 0 to 30 MHz. TA = -40°C to +85°C; V<sub>SS</sub> = 0 V; V<sub>CC</sub> = 2.7 V to 5.5 V  $\pm$  10%; F = 0 to 30 MHz.

Table 11-2.

DC Parameters for Low Voltage

| Symbol                            | Parameter                                                           | Min                       | Тур                                    | Мах                                                | Unit | Test Conditions                                                                                      |

|-----------------------------------|---------------------------------------------------------------------|---------------------------|----------------------------------------|----------------------------------------------------|------|------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                                   | -0.5                      |                                        | 0.2 V <sub>CC</sub> - 0.1                          | V    |                                                                                                      |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                                | 0.2 V <sub>CC</sub> + 0.9 |                                        | V <sub>CC</sub> + 0.5                              | V    |                                                                                                      |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                                      | 0.7 V <sub>CC</sub>       |                                        | V <sub>CC</sub> + 0.5                              | V    |                                                                                                      |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3, 4, 5 (6)                         |                           |                                        | 0.45                                               | V    | I <sub>OL</sub> = 0.8 mA <sup>(4)</sup>                                                              |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0, ALE, PSEN (6)                           |                           |                                        | 0.45                                               | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup>                                                              |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3, 4, 5                            | 0.9 V <sub>CC</sub>       |                                        |                                                    | V    | I <sub>OH</sub> = -10 μA                                                                             |

| V <sub>OH1</sub>                  | Output High Voltage, port 0, ALE, PSEN                              | 0.9 V <sub>CC</sub>       |                                        |                                                    | V    | I <sub>OH</sub> = -40 μA                                                                             |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2, 3, 4, 5                         |                           |                                        | -50                                                | μA   | Vin = 0.45 V                                                                                         |

| ILI                               | Input Leakage Current                                               |                           |                                        | ±10                                                | μA   | 0.45 V < Vin < V <sub>CC</sub>                                                                       |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3, 4, 5              |                           |                                        | -650                                               | μA   | Vin = 2.0 V                                                                                          |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                               | 50                        | 90 <sup>(5)</sup>                      | 200                                                | kΩ   |                                                                                                      |

| CIO                               | Capacitance of I/O Buffer                                           |                           |                                        | 10                                                 | pF   | Fc = 1 MHz<br>TA = 25°C                                                                              |

| I <sub>PD</sub>                   | Power-down Current                                                  |                           | 20 <sup>(5)</sup><br>10 <sup>(5)</sup> | 50<br>30                                           | μΑ   | $V_{CC} = 2.0 \text{ V to } 5.5 \text{ V}^{(3)}$<br>$V_{CC} = 2.0 \text{ V to } 3.3 \text{ V}^{(3)}$ |

| I <sub>PD</sub>                   | Power-down Current (Only for TS87C51RD2<br>S287-xxx Very Low power) |                           | 2 <sup>(5)</sup>                       | 15                                                 | μA   | $2.0 \text{ V} < \text{V}_{\text{CC}} < 3.6 \text{ V}^{(3)}$                                         |

| I <sub>cc</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: (7)                   |                           |                                        | 1 + 0.2 Freq<br>(MHz)<br>@12MHz 3.4<br>@16MHz 4.2  | mA   | $V_{CC} = 3.3 V^{(1)}$                                                                               |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: (7)                   |                           |                                        | 1 + 0.3 Freq<br>(MHz)<br>@12MHz 4.6<br>@16MHz 5.8  | mA   | $V_{CC} = 3.3 V^{(8)}$                                                                               |

| I <sub>CC</sub><br>idle           | Power Supply Current Maximum values, X1 mode: (7)                   |                           |                                        | 0.15 Freq<br>(MHz) + 0.2<br>@12MHz 2<br>@16MHz 2.6 | mA   | $V_{CC} = 3.3 V^{(2)}$                                                                               |

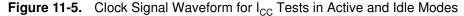

Notes: 1.  $I_{CC}$  under reset is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 11-5.),  $V_{IL} = V_{SS} + 0.5$  V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used...

2. Idle I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V, V<sub>IH</sub> = V<sub>CC</sub> - 0.5 V; XTAL2 N.C; Port 0 = V<sub>CC</sub>;  $\overline{EA}$  = RST = V<sub>SS</sub> (see Figure 11-3.).

Power-down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 11-4.).

### Figure 11-3. I<sub>CC</sub> Test Condition, Idle Mode

Figure 11-4. I<sub>CC</sub> Test Condition, Power-Down Mode

### 11.5 AC Parameters

#### 11.5.1 Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

$\begin{array}{l} \mbox{Example:} T_{AVLL} = \mbox{Time for Address Valid to ALE Low.} \\ T_{LLPL} = \mbox{Time for ALE Low to PSEN Low.} \end{array}$

TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0 V$ ;  $V_{CC} = 5 V \pm 10\%$ ; -M and -V ranges. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0 V$ ;  $V_{CC} = 5 V \pm 10\%$ ; -M and -V ranges.

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS87C51RD2-MCA   |               | 1              |                    |                    |         | 1       |

| TS87C51RD2-MCB   |               |                |                    |                    |         |         |

| TS87C51RD2-MCE   |               |                |                    |                    |         |         |

| TS87C51RD2-MIA   |               |                |                    |                    |         |         |

| TS87C51RD2-MIB   |               |                |                    |                    |         |         |

| TS87C51RD2-MIE   |               |                |                    |                    |         |         |

| TS87C51RD2-LCA   |               |                |                    |                    |         |         |

| TS87C51RD2-LCB   |               |                |                    |                    |         |         |

| TS87C51RD2-LCE   |               |                |                    |                    |         |         |

| TS87C51RD2-LIA   |               |                | OBSOLE             | TE                 |         |         |

| TS87C51RD2-LIB   |               |                |                    |                    |         |         |

| TS87C51RD2-LIE   |               |                |                    |                    |         |         |

| TS87C51RD2-VCA   |               |                |                    |                    |         |         |

| TS87C51RD2-VCB   |               |                |                    |                    |         |         |

| TS87C51RD2-VCE   |               |                |                    |                    |         |         |

| TS87C51RD2-VCL   |               |                |                    |                    |         |         |

| TS87C51RD2-VIA   |               |                |                    |                    |         |         |

| TS87C51RD2-VIB   |               |                |                    |                    |         |         |

| TS87C51RD2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT87C51RD2-3CSUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RD2-SLSUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RD2-RLTUM | OTP 64k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT87C51RD2-3CSUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT87C51RD2-SLSUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT87C51RD2-RLTUL | OTP 64k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

| Part Number      | Memory size   | Supply Voltage | Temperature Range  | Max Frequency      | Package | Packing |

|------------------|---------------|----------------|--------------------|--------------------|---------|---------|

| TS83C51RB2-MCA   |               |                |                    | •                  |         |         |

| TS83C51RB2-MCB   |               |                |                    |                    |         |         |

| TS83C51RB2-MCE   |               |                |                    |                    |         |         |

| TS83C51RB2-MIA   |               |                |                    |                    |         |         |

| TS83C51RB2-MIB   |               |                |                    |                    |         |         |

| TS83C51RB2-MIE   |               |                |                    |                    |         |         |

| TS83C51RB2-LCA   |               |                |                    |                    |         |         |

| TS83C51RB2-LCB   |               |                |                    |                    |         |         |

| TS83C51RB2-LCE   |               |                |                    | TE                 |         |         |

| TS83C51RB2-LIA   |               |                | OBSOLE             |                    |         |         |

| TS83C51RB2-LIB   |               |                |                    |                    |         |         |

| TS83C51RB2-LIE   |               |                |                    |                    |         |         |

| TS83C51RB2-VCA   |               |                |                    |                    |         |         |

| TS83C51RB2-VCB   |               |                |                    |                    |         |         |

| TS83C51RB2-VCE   |               |                |                    |                    |         |         |

| TS83C51RB2-VIA   |               |                |                    |                    |         |         |

| TS83C51RB2-VIB   |               |                |                    |                    |         |         |

| TS83C51RB2-VIE   |               |                |                    |                    |         |         |

|                  |               |                |                    |                    |         |         |

| AT83C51RB2-3CSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RB2-SLSUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RB2-RLTUM | ROM 32k Bytes | 5V             | Industrial & Green | 40 MHz (20 MHz X2) | VQFP44  | Tray    |

| AT83C51RB2-3CSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PDIL40  | Stick   |

| AT83C51RB2-SLSUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | PLCC44  | Stick   |

| AT83C51RB2-RLTUL | ROM 32k Bytes | 3-5V           | Industrial & Green | 30 MHz (20 MHz X2) | VQFP44  | Tray    |

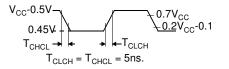

## 13. Package Drawings

## 13.1 PLCC44

|    | Ν      | 1M ·  | ΙN    | СН    |

|----|--------|-------|-------|-------|

| A  | 4.20   | 4. 57 | . 165 | . 180 |

| A1 | 2, 29  | 3.04  | . 090 | . 120 |

| D  | 17.40  | 17.65 | . 685 | . 695 |

| D1 | 16.44  | 16.66 | . 647 | . 656 |

| D5 | 14.99  | 16.00 | . 590 | . 630 |

| E  | 17.40  | 17.65 | . 685 | . 695 |

| E1 | 16.44  | 16.66 | . 647 | . 656 |

| E5 | 14.99  | 16.00 | . 590 | . 630 |

| e  | 1.27   | BSC   | . 050 | BSC   |

| G  | 1.07   | 1.22  | . 042 | . 048 |

| н  | 1.07   | 1.42  | . 042 | .056  |

| J  | 0.51   | -     | . 020 | -     |

| К  | 0.33   | 0.53  | . 013 | . 021 |

| Nd | 11     |       | 1 1   |       |

| Ne | 1      | 1     | 1 1   |       |

| P  | KG STD | 00    |       |       |