Welcome to **E-XFL.COM**

## **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | PowerPC                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 350MHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | -                                                                      |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | -                                                                      |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 2.5V, 3.3V                                                             |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 360-BCBGA, FCCBGA                                                      |

| Supplier Device Package         | 360-CBGA (25x25)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc755crx350te |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Selectable interface voltages of 2.5 and 3.3 V

- Parity checking on both L2 address and data

- Memory management unit

- 128-entry, two-way set-associative instruction TLB

- 128-entry, two-way set-associative data TLB

- Hardware reload for TLBs

- Hardware or optional software tablewalk support

- Eight instruction BATs and eight data BATs

- Eight SPRGs, for assistance with software tablewalks

- Virtual memory support for up to 4 exabytes  $(2^{52})$  of virtual memory

- Real memory support for up to 4 gigabytes (2<sup>32</sup>) of physical memory

- Bus interface

- Compatible with 60x processor interface

- 32-bit address bus

- 64-bit data bus, 32-bit mode selectable

- Bus-to-core frequency multipliers of 2x, 3x, 3.5x, 4x, 4.5x, 5x, 5.5x, 6x, 6.5x, 7x, 7.5x, 8x, 10x supported

- Selectable interface voltages of 2.5 and 3.3 V

- Parity checking on both address and data buses

- Power management

- Low-power design with thermal requirements very similar to MPC740/MPC750

- Three static power saving modes: doze, nap, and sleep

- Dynamic power management

- Integrated thermal management assist unit

- On-chip thermal sensor and control logic

- Thermal management interrupt for software regulation of junction temperature

- Testability

- LSSD scan design

- IEEE 1149.1 JTAG interface

# 3 General Parameters

The following list provides a summary of the general parameters of the MPC755:

Technology 0.22  $\mu$ m CMOS, six-layer metal Die size 6.61 mm  $\times$  7.73 mm (51 mm<sup>2</sup>)

Transistor count 6.75 million Logic design Fully-static

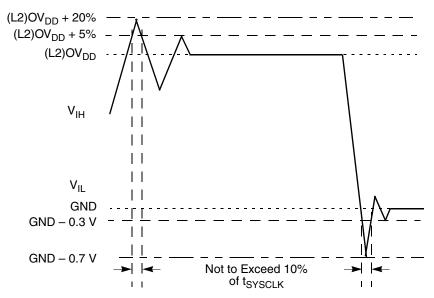

Figure 2 shows the allowable undershoot and overshoot voltage on the MPC755.

Figure 2. Overshoot/Undershoot Voltage

The MPC755 provides several I/O voltages to support both compatibility with existing systems and migration to future systems. The MPC755 core voltage must always be provided at nominal 2.0 V (see Table 3 for actual recommended core voltage). Voltage to the L2 I/Os and processor interface I/Os are provided through separate sets of supply pins and may be provided at the voltages shown in Table 2. The input voltage threshold for each bus is selected by sampling the state of the voltage select pins BVSEL and L2VSEL during operation. These signals must remain stable during part operation and cannot change. The output voltage will swing from GND to the maximum voltage applied to the  $OV_{DD}$  or  $L2OV_{DD}$  power pins.

Table 2 describes the input threshold voltage setting.

**Processor Bus** L2 Bus **Part BVSEL Signal** L2VSEL Signal Interface Voltage Revision **Interface Voltage** Ε 0 Not Available 0 Not Available 2.5 V/3.3 V 2.5 V/3.3 V

Table 2. Input Threshold Voltage Setting

Caution: The input threshold selection must agree with the OV<sub>DD</sub>/L2OV<sub>DD</sub> voltages supplied.

Note: The input threshold settings above are different for all revisions prior to Rev. 2.8 (Rev. E). For more information, refer to Section 10.2, "Part Numbers Not Fully Addressed by This Document."

MPC755 RISC Microprocessor Hardware Specifications, Rev. 8 Freescale Semiconductor 7

#### **Electrical and Thermal Characteristics**

Table 3 provides the recommended operating conditions for the MPC755.

Table 3. Recommended Operating Conditions <sup>1</sup>

| Characte                 | Characteristic |                    | 300 MHz, 350 MHz |                    | 400   | 400 MHz            |    | Notes |

|--------------------------|----------------|--------------------|------------------|--------------------|-------|--------------------|----|-------|

|                          |                |                    | Min              | Max                | Min   | Max                |    |       |

| Core supply voltage      |                | $V_{DD}$           | 1.80             | 2.10               | 1.90  | 2.10               | V  | 3     |

| PLL supply voltage       |                | AV <sub>DD</sub>   | 1.80             | 2.10               | 1.90  | 2.10               | V  | 3     |

| L2 DLL supply voltage    |                | L2AV <sub>DD</sub> | 1.80             | 2.10               | 1.90  | 2.10               | V  | 3     |

| Processor bus supply     | BVSEL = 1      | OV <sub>DD</sub>   | 2.375            | 2.625              | 2.375 | 2.625              | V  | 2, 4  |

| voltage                  |                |                    | 3.135            | 3.465              | 3.135 | 3.465              |    | 5     |

| L2 bus supply voltage    | L2VSEL = 1     | L2OV <sub>DD</sub> | 2.375            | 2.625              | 2.375 | 2.625              | V  | 2, 4  |

|                          |                |                    | 3.135            | 3.465              | 3.135 | 3.465              |    | 5     |

| Input voltage            | Processor bus  | V <sub>in</sub>    | GND              | OV <sub>DD</sub>   | GND   | OV <sub>DD</sub>   | V  |       |

|                          | L2 bus         | V <sub>in</sub>    | GND              | L2OV <sub>DD</sub> | GND   | L2OV <sub>DD</sub> | V  |       |

|                          | JTAG signals   | V <sub>in</sub>    | GND              | OV <sub>DD</sub>   | GND   | OV <sub>DD</sub>   | V  |       |

| Die-junction temperature | •              | Tj                 | 0                | 105                | 0     | 105                | °C |       |

#### Notes:

- 1. These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

- 2. Revisions prior to Rev. 2.8 (Rev. E) offered different I/O voltage support. For more information, refer to Section 10.2, "Part Numbers Not Fully Addressed by This Document."

- 3. 2.0 V nominal.

- 4. 2.5 V nominal.

- 5. 3.3 V nominal.

Table 4 provides the package thermal characteristics for the MPC755 and MPC745. The MPC755 was initially sampled in a CBGA package, but production units are currently provided in both a CBGA and a PBGA package. Because of the better long-term device-to-board interconnect reliability of the PBGA package, Freescale recommends use of a PBGA package except where circumstances dictate use of a CBGA package. The MPC745 is offered in a PBGA package only.

## Table 6. DC Electrical Specifications (continued)

At recommended operating conditions (see Table 3)

| Characteristic                                | Nominal<br>Bus<br>Voltage <sup>1</sup> | Symbol          | Min | Max | Unit | Notes |

|-----------------------------------------------|----------------------------------------|-----------------|-----|-----|------|-------|

| Capacitance, V <sub>in</sub> = 0 V, f = 1 MHz |                                        | C <sub>in</sub> |     | 5.0 | pF   | 3, 4  |

#### Notes:

- 1. Nominal voltages; see Table 3 for recommended operating conditions.

- 2. For processor bus signals, the reference is OV<sub>DD</sub> while L2OV<sub>DD</sub> is the reference for the L2 bus signals.

- 3. Excludes test signals (LSSD\_MODE, L1\_TSTCLK, L2\_TSTCLK) and IEEE 1149.1 boundary scan (JTAG) signals.

- 4. Capacitance is periodically sampled rather than 100% tested.

- 5. The leakage is measured for nominal  $OV_{DD}$  and  $V_{DD}$ , or both  $OV_{DD}$  and  $V_{DD}$  must vary in the same direction (for example, both  $OV_{DD}$  and  $V_{DD}$  vary by either +5% or -5%).

Table 7 provides the power consumption for the MPC755.

**Table 7. Power Consumption for MPC755**

|                                   | Proce     | essor (CPU) Frequ | uency   | l l m i A | Notes   |  |  |  |

|-----------------------------------|-----------|-------------------|---------|-----------|---------|--|--|--|

|                                   | 300 MHz   | 350 MHz           | 400 MHz | - Unit    | Notes   |  |  |  |

|                                   | Full-Powe | r Mode            |         | 1         |         |  |  |  |

| Typical                           | 3.1       | 3.6               | 5.4     | W         | 1, 3, 4 |  |  |  |

| Maximum                           | 4.5       | 6.0               | 8.0     | W         | 1, 2    |  |  |  |

|                                   | Doze M    | lode              |         |           |         |  |  |  |

| Maximum                           | 1.8       | 2.0               | 2.3     | W         | 1, 2, 4 |  |  |  |

|                                   | Nap M     | ode               |         | •         |         |  |  |  |

| Maximum                           | 1.0       | 1.0               | 1.0     | W         | 1, 2, 4 |  |  |  |

|                                   | Sleep N   | /lode             |         |           |         |  |  |  |

| Maximum                           | 550       | 550               | 550     | mW        | 1, 2, 4 |  |  |  |

| Sleep Mode (PLL and DLL Disabled) |           |                   |         |           |         |  |  |  |

| Maximum                           | 510       | 510               | 510     | mW        | 1, 2    |  |  |  |

#### Notes:

- 1. These values apply for all valid processor bus and L2 bus ratios. The values do not include I/O supply power ( $OV_{DD}$  and  $L2OV_{DD}$ ) or PLL/DLL supply power ( $AV_{DD}$  and  $L2AV_{DD}$ ).  $OV_{DD}$  and  $L2OV_{DD}$  power is system dependent, but is typically <10% of  $V_{DD}$  power. Worst case power consumption for  $AV_{DD}$  = 15 mW and  $L2AV_{DD}$  = 15 mW.

- Maximum power is measured at nominal V<sub>DD</sub> (see Table 3) while running an entirely cache-resident, contrived sequence of instructions which keep the execution units maximally busy.

- Typical power is an average value measured at the nominal recommended V<sub>DD</sub> (see Table 3) and 65°C in a system while running a typical code sequence.

- 4. Not 100% tested. Characterized and periodically sampled.

**Electrical and Thermal Characteristics**

#### 4.2 AC Electrical Characteristics

This section provides the AC electrical characteristics for the MPC755. After fabrication, functional parts are sorted by maximum processor core frequency as shown in Section 4.2.1, "Clock AC Specifications," and tested for conformance to the AC specifications for that frequency. The processor core frequency is determined by the bus (SYSCLK) frequency and the settings of the PLL\_CFG[0:3] signals. Parts are sold by maximum processor core frequency; see Section 10, "Ordering Information."

#### 4.2.1 **Clock AC Specifications**

Table 8 provides the clock AC timing specifications as defined in Figure 3.

## **Table 8. Clock AC Timing Specifications**

At recommended operating conditions (see Table 3)

|                                                   |                                            | Maximum Processor Core Frequency |      |         |      |         |      |      |       |

|---------------------------------------------------|--------------------------------------------|----------------------------------|------|---------|------|---------|------|------|-------|

| Characteristic                                    | Symbol                                     | Symbol 300 MHz                   |      | 350 MHz |      | 400 MHz |      | Unit | Notes |

|                                                   |                                            | Min                              | Max  | Min     | Max  | Min     | Max  |      |       |

| Processor frequency                               | f <sub>core</sub>                          | 200                              | 300  | 200     | 350  | 200     | 400  | MHz  | 1     |

| VCO frequency                                     | f <sub>VCO</sub>                           | 400                              | 600  | 400     | 700  | 400     | 800  | MHz  | 1     |

| SYSCLK frequency                                  | f <sub>SYSCLK</sub>                        | 25                               | 100  | 25      | 100  | 25      | 100  | MHz  | 1     |

| SYSCLK cycle time                                 | t <sub>SYSCLK</sub>                        | 10                               | 40   | 10      | 40   | 10      | 40   | ns   |       |

| SYSCLK rise and fall time                         | t <sub>KR</sub> , t <sub>KF</sub>          | _                                | 2.0  | _       | 2.0  | _       | 2.0  | ns   | 2     |

|                                                   | t <sub>KR</sub> , t <sub>KF</sub>          | _                                | 1.4  | _       | 1.4  | _       | 1.4  | ns   | 2     |

| SYSCLK duty cycle measured at OV <sub>DD</sub> /2 | t <sub>KHKL</sub> /<br>t <sub>SYSCLK</sub> | 40                               | 60   | 40      | 60   | 40      | 60   | %    | 3     |

| SYSCLK jitter                                     |                                            | _                                | ±150 | _       | ±150 | _       | ±150 | ps   | 3, 4  |

| Internal PLL relock time                          |                                            | _                                | 100  | _       | 100  | _       | 100  | μS   | 3, 5  |

#### Notes:

- 1. Caution: The SYSCLK frequency and PLL\_CFG[0:3] settings must be chosen such that the resulting SYSCLK (bus) frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0:3] signal description in Section 8.1, "PLL Configuration," for valid PLL\_CFG[0:3]

- 2. Rise and fall times measurements are now specified in terms of slew rates, rather than time to account for selectable I/O bus interface levels. The minimum slew rate of 1 V/ns is equivalent to a 2 ns maximum rise/fall time measured at 0.4 and 2.4 V  $(OV_{DD} = 3.3 \text{ V})$  or a rise/fall time of 1 ns measured at 0.4 and 1.8 V  $(OV_{DD} = 2.5 \text{ V})$ .

- 3. Timing is guaranteed by design and characterization.

- 4. This represents total input jitter—short term and long term combined—and is guaranteed by design.

- 5. Relock timing is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for PLL lock after a stable V<sub>DD</sub> and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRESET must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

MPC755 RISC Microprocessor Hardware Specifications, Rev. 8 12 Freescale Semiconductor

## Table 10. Processor Bus AC Timing Specifications <sup>1</sup>

At recommended operating conditions (see Table 3)

| Parameter                                                    | Symbol              | All Speed | d Grades | Unit                | Notes   |

|--------------------------------------------------------------|---------------------|-----------|----------|---------------------|---------|

| raiametei                                                    | Symbol              | Min       | Max      |                     | Notes   |

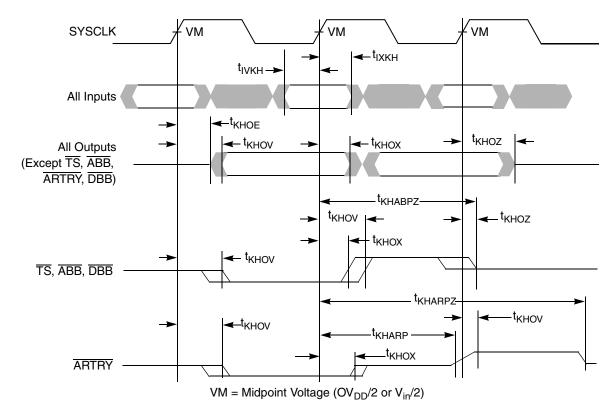

| Setup times: All inputs                                      | t <sub>IVKH</sub>   | 2.5       | _        | ns                  |         |

| Input hold times: TLBISYNC, MCP, SMI                         | t <sub>IXKH</sub>   | 0.6       | _        | ns                  | 6       |

| Input hold times: All inputs, except TLBISYNC, MCP, SMI      | t <sub>IXKH</sub>   | 0.2       | _        | ns                  | 6       |

| Valid times: All outputs                                     | t <sub>KHOV</sub>   | _         | 4.1      | ns                  |         |

| Output hold times: All outputs                               | t <sub>KHOX</sub>   | 1.0       | _        | ns                  |         |

| SYSCLK to output enable                                      | t <sub>KHOE</sub>   | 0.5       | _        | ns                  | 2       |

| SYSCLK to output high impedance (all except ABB, ARTRY, DBB) | t <sub>KHOZ</sub>   | _         | 6.0      | ns                  | 2       |

| SYSCLK to ABB, DBB high impedance after precharge            | t <sub>KHABPZ</sub> | _         | 1.0      | t <sub>sysclk</sub> | 2, 3, 4 |

| Maximum delay to ARTRY precharge                             | t <sub>KHARP</sub>  | _         | 1        | t <sub>sysclk</sub> | 2, 3, 5 |

| SYSCLK to ARTRY high impedance after precharge               | t <sub>KHARPZ</sub> | _         | 2        | t <sub>sysclk</sub> | 2, 3, 5 |

#### Notes:

- 1. Revisions prior to Rev. 2.8 (Rev. E) were limited in performance and did not conform to this specification. For more information, refer to Section 10.2, "Part Numbers Not Fully Addressed by This Document."

- 2. Guaranteed by design and characterization.

- 3. t<sub>sysclk</sub> is the period of the external clock (SYSCLK) in ns. The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.

- 4. Per the 60x bus protocol,  $\overline{TS}$ ,  $\overline{ABB}$ , and  $\overline{DBB}$  are driven only by the currently active bus master. They are asserted low, then precharged high before returning to high-Z as shown in Figure 6. The nominal precharge width for  $\overline{TS}$ ,  $\overline{ABB}$ , or  $\overline{DBB}$  is  $0.5 \times t_{sysclk}$ , that is, less than the minimum  $t_{sysclk}$  period, to ensure that another master asserting  $\overline{TS}$ ,  $\overline{ABB}$ , or  $\overline{DBB}$  on the following clock will not contend with the precharge. Output valid and output hold timing is tested for the signal asserted. Output valid time is tested for precharge. The high-Z behavior is guaranteed by design.

- 5. Per the 60x bus protocol, ARTRY can be driven by multiple bus masters through the clock period immediately following AACK. Bus contention is not an issue since any master asserting ARTRY will be driving it low. Any master asserting it low in the first clock following AACK will then go to high-Z for one clock before precharging it high during the second cycle after the assertion of AACK. The nominal precharge width for ARTRY is 1.0 t<sub>sysclk</sub>; that is, it should be high-Z as shown in Figure 6 before the first opportunity for another master to assert ARTRY. Output valid and output hold timing is tested for the signal asserted. Output valid time is tested for precharge. The high-Z and precharge behavior is guaranteed by design.

- 6. MCP and SRESET must be held asserted for a minimum of two bus clock cycles; INT and SMI should be held asserted until the exception is taken; CKSTP\_IN must be held asserted until the system has been reset. See the MPC750 RISC Microprocessor Family User's Manual for more information.

#### **Electrical and Thermal Characteristics**

Figure 6 provides the input/output timing diagram for the MPC755.

Figure 6. Input/Output Timing Diagram

#### 4.2.3 L2 Clock AC Specifications

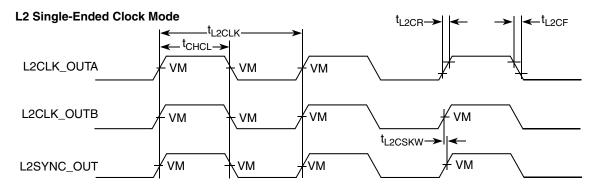

The L2CLK frequency is programmed by the L2 configuration register (L2CR[4–6]) core-to-L2 divisor ratio. See Table 17 for example core and L2 frequencies at various divisors. Table 11 provides the potential range of L2CLK output AC timing specifications as defined in Figure 7.

The minimum L2CLK frequency of Table 11 is specified by the maximum delay of the internal DLL. The variable-tap DLL introduces up to a full clock period delay in the L2CLK OUTA, L2CLK OUTB, and L2SYNC\_OUT signals so that the returning L2SYNC\_IN signal is phase-aligned with the next core clock (divided by the L2 divisor ratio). Do not choose a core-to-L2 divisor which results in an L2 frequency below this minimum, or the L2CLK OUT signals provided for SRAM clocking will not be phase-aligned with the MPC755 core clock at the SRAMs.

The maximum L2CLK frequency shown in Table 11 is the core frequency divided by one. Very few L2 SRAM designs will be able to operate in this mode, especially at higher core frequencies. Therefore, most designs will select a greater core-to-L2 divisor to provide a longer L2CLK period for read and write access to the L2 SRAMs. The maximum L2CLK frequency for any application of the MPC755 will be a function of the AC timings of the MPC755, the AC timings for the SRAM, bus loading, and printed-circuit board trace length. The current AC timing of the MPC755 supports up to 200 MHz with typical, similarly-rated SRAM parts, provided careful design practices are observed. Clock trace lengths must be matched and all trace lengths should be as short as possible. Higher frequencies can be achieved by using better performing

## **Electrical and Thermal Characteristics**

## Table 11. L2CLK Output AC Timing Specification

At recommended operating conditions (see Table 3)

| Parameter                       | Cumbal                                | All Spee | d Grades | Unit  | Notes |

|---------------------------------|---------------------------------------|----------|----------|-------|-------|

| Parameter                       | Symbol                                | Min      | Max      | Unit  | Notes |

| L2CLK frequency                 | f <sub>L2CLK</sub>                    | 80       | 450      | MHz   | 1, 4  |

| L2CLK cycle time                | t <sub>L2CLK</sub>                    | 2.5      | 12.5     | ns    |       |

| L2CLK duty cycle                | t <sub>CHCL</sub> /t <sub>L2CLK</sub> | 45       | 55       | %     | 2, 7  |

| Internal DLL-relock time        |                                       | 640      | _        | L2CLK | 3, 7  |

| DLL capture window              |                                       | 0        | 10       | ns    | 5, 7  |

| L2CLK_OUT output-to-output skew | t <sub>L2CSKW</sub>                   | _        | 50       | ps    | 6, 7  |

| L2CLK_OUT output jitter         |                                       | _        | ±150     | ps    | 6, 7  |

#### Notes:

- L2CLK outputs are L2CLK\_OUTA, L2CLK\_OUTB, L2CLK\_OUT, and L2SYNC\_OUT pins. The L2CLK frequency-to-core

frequency settings must be chosen such that the resulting L2CLK frequency and core frequency do not exceed their

respective maximum or minimum operating frequencies. The maximum L2LCK frequency will be system dependent.

L2CLK\_OUTA and L2CLK\_OUTB must have equal loading.

- 2. The nominal duty cycle of the L2CLK is 50% measured at midpoint voltage.

- 3. The DLL-relock time is specified in terms of L2CLK periods. The number in the table must be multiplied by the period of L2CLK to compute the actual time duration in ns. Relock timing is guaranteed by design and characterization.

- 4. The L2CR[L2SL] bit should be set for L2CLK frequencies less than 110 MHz. This adds more delay to each tap of the DLL.

- 5. Allowable skew between L2SYNC\_OUT and L2SYNC\_IN.

- 6. This output jitter number represents the maximum delay of one tap forward or one tap back from the current DLL tap as the phase comparator seeks to minimize the phase difference between L2SYNC\_IN and the internal L2CLK. This number must be comprehended in the L2 timing analysis. The input jitter on SYSCLK affects L2CLK\_OUT and the L2 address/data/control signals equally and, therefore, is already comprehended in the AC timing and does not have to be considered in the L2 timing analysis.

- 7. Guaranteed by design.

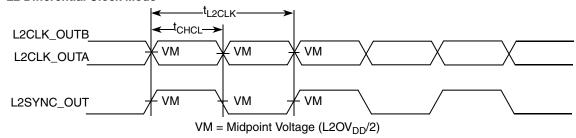

The L2CLK\_OUT timing diagram is shown in Figure 7.

## **L2 Differential Clock Mode**

Figure 7. L2CLK\_OUT Output Timing Diagram

## 4.2.4 L2 Bus AC Specifications

Table 12 provides the L2 bus interface AC timing specifications for the MPC755 as defined in Figure 8 and Figure 9 for the loading conditions described in Figure 10.

**Table 12. L2 Bus Interface AC Timing Specifications**

At recommended operating conditions (see Table 3)

|                        | Parameter                                                                                                                                        | Symbol                                | All Spee                 | d Grades                 | Unit | Notes |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------|--------------------------|------|-------|

|                        | i di dilictei                                                                                                                                    | - Symbol                              | Min                      | Max                      |      | Notes |

| L2SYNC_IN rise and     | fall time                                                                                                                                        | t <sub>L2CR</sub> , t <sub>L2CF</sub> | _                        | 1.0                      | ns   | 1     |

| Setup times: Data and  | d parity                                                                                                                                         | t <sub>DVL2CH</sub>                   | 1.2                      | _                        | ns   | 2     |

| Input hold times: Data | and parity                                                                                                                                       | t <sub>DXL2CH</sub>                   | 0                        | _                        | ns   | 2     |

| Valid times:           | All outputs when L2CR[14–15] = 00<br>All outputs when L2CR[14–15] = 01<br>All outputs when L2CR[14–15] = 10<br>All outputs when L2CR[14–15] = 11 | t <sub>L2CHOV</sub>                   | <br> -<br> -<br> -       | 3.1<br>3.2<br>3.3<br>3.7 | ns   | 3, 4  |

| Output hold times:     | All outputs when L2CR[14–15] = 00<br>All outputs when L2CR[14–15] = 01<br>All outputs when L2CR[14–15] = 10<br>All outputs when L2CR[14–15] = 11 | t <sub>L2CHOX</sub>                   | 0.5<br>0.7<br>0.9<br>1.1 | _<br>_<br>_<br>_         | ns   | 3     |

MPC755 RISC Microprocessor Hardware Specifications, Rev. 8

## **Pin Assignments**

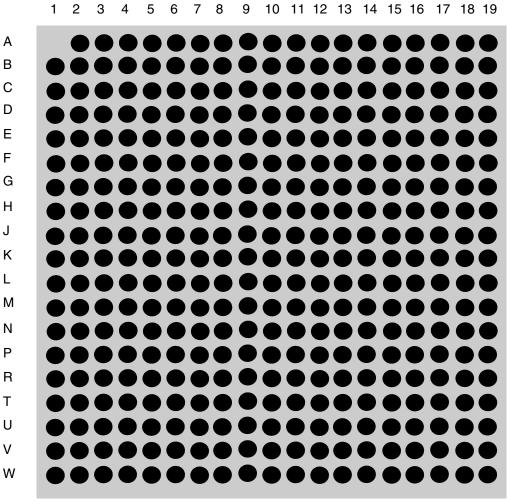

Figure 17 (in Part A) shows the pinout of the MPC755, 360 PBGA and 360 CBGA packages as viewed from the top surface. Part B shows the side profile of the PBGA and CBGA package to indicate the direction of the top surface view.

## Part A

Not to Scale

Part B

Figure 17. Pinout of the MPC755, 360 PBGA and CBGA Packages as Viewed from the Top Surface

## **Pinout Listings**

## Table 15. Pinout Listing for the MPC755, 360 BGA Package (continued)

| Signal Name        | Pin Number                                                                                                                                                                                                                                                                                                                | Active | I/O    | I/F Voltage <sup>1</sup> | Notes      |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------------------------|------------|

| DH[0:31]           | W12, W11, V11, T9, W10, U9, U10, M11, M9, P8, W7, P9, W9, R10, W6, V7, V6, U8, V9, T7, U7, R7, U6, W5, U5, W4, P7, V5, V4, W3, U4, R5                                                                                                                                                                                     | High   | I/O    | OV <sub>DD</sub>         |            |

| DL[0:31]           | M6, P3, N4, N5, R3, M7, T2, N6, U2, N7, P11, V13, U12, P12, T13, W13, U13, V10, W8, T11, U11, V12, V8, T1, P1, V1, U1, N1, R2, V3, U3, W2                                                                                                                                                                                 | High   | I/O    | OV <sub>DD</sub>         |            |

| DP[0:7]            | L1, P2, M2, V2, M1, N2, T3, R1                                                                                                                                                                                                                                                                                            | High   | I/O    | OV <sub>DD</sub>         |            |

| DRTRY              | H6                                                                                                                                                                                                                                                                                                                        | Low    | Input  | OV <sub>DD</sub>         |            |

| GBL                | B1                                                                                                                                                                                                                                                                                                                        | Low    | I/O    | OV <sub>DD</sub>         |            |

| GND                | D10, D14, D16, D4, D6, E12, E8, F4, F6, F10, F14, F16, G9, G11, H5, H8, H10, H12, H15, J9, J11, K4, K6, K8, K10, K12, K14, K16, L9, L11, M5, M8, M10, M12, M15, N9, N11, P4, P6, P10, P14, P16, R8, R12, T4, T6, T10, T14, T16                                                                                            | _      | _      | GND                      |            |

| HRESET             | B6                                                                                                                                                                                                                                                                                                                        | Low    | Input  | OV <sub>DD</sub>         |            |

| ĪNT                | C11                                                                                                                                                                                                                                                                                                                       | Low    | Input  | OV <sub>DD</sub>         |            |

| L1_TSTCLK          | F8                                                                                                                                                                                                                                                                                                                        | High   | Input  | _                        | 2          |

| L2ADDR[16:0]       | G18, H19, J13, J14, H17, H18, J16, J17, J18, J19, K15, K17, K18, M19, L19, L18, L17                                                                                                                                                                                                                                       | High   | Output | L2OV <sub>DD</sub>       |            |

| L2AV <sub>DD</sub> | L13                                                                                                                                                                                                                                                                                                                       | _      | _      | 2.0 V                    |            |

| L2CE               | P17                                                                                                                                                                                                                                                                                                                       | Low    | Output | L2OV <sub>DD</sub>       |            |

| L2CLK_OUTA         | N15                                                                                                                                                                                                                                                                                                                       | _      | Output | L2OV <sub>DD</sub>       |            |

| L2CLK_OUTB         | L16                                                                                                                                                                                                                                                                                                                       | _      | Output | L2OV <sub>DD</sub>       |            |

| L2DATA[0:63]       | U14, R13, W14, W15, V15, U15, W16, V16, W17, V17, U17, W18, V18, U18, V19, U19, T18, T17, R19, R18, R17, R15, P19, P18, P13, N14, N13, N19, N17, M13, M18, H13, G19, G16, G15, G14, G13, F19, F18, F13, E19, E18, E17, E15, D19, D18, D17, C18, C17, B19, B18, B17, A18, A17, A16, B16, C16, A14, A15, C15, B14, C14, E13 | High   | I/O    | L2OV <sub>DD</sub>       |            |

| L2DP[0:7]          | V14, U16, T19, N18, H14, F17, C19, B15                                                                                                                                                                                                                                                                                    | High   | I/O    | L2OV <sub>DD</sub>       |            |

| L2OV <sub>DD</sub> | D15, E14, E16, H16, J15, L15, M16, P15, R14, R16, T15, F15                                                                                                                                                                                                                                                                | _      | _      | L2OV <sub>DD</sub>       |            |

| L2SYNC_IN          | L14                                                                                                                                                                                                                                                                                                                       | _      | Input  | L2OV <sub>DD</sub>       |            |

| L2SYNC_OUT         | M14                                                                                                                                                                                                                                                                                                                       | _      | Output | L2OV <sub>DD</sub>       |            |

| L2_TSTCLK          | F7                                                                                                                                                                                                                                                                                                                        | High   | Input  | _                        | 2          |

| L2VSEL             | A19                                                                                                                                                                                                                                                                                                                       | High   | Input  | L2OV <sub>DD</sub>       | 1, 5, 6, 7 |

| L2WE               | N16                                                                                                                                                                                                                                                                                                                       | Low    | Output | L2OV <sub>DD</sub>       |            |

#### **Package Description**

Table 15. Pinout Listing for the MPC755, 360 BGA Package (continued)

| Signal Name | Pin Number | Active | I/O    | I/F Voltage <sup>1</sup> | Notes |

|-------------|------------|--------|--------|--------------------------|-------|

| VOLTDET     | K13        | High   | Output | L2OV <sub>DD</sub>       | 8     |

#### Notes:

- 1. OV<sub>DD</sub> supplies power to the processor bus, JTAG, and all control signals except the L2 cache controls (L2CE, L2WE, and L2ZZ); L2OV<sub>DD</sub> supplies power to the L2 cache interface (L2ADDR[0:16], L2DATA[0:63], L2DP[0:7], and L2SYNC\_OUT) and the L2 control signals; and V<sub>DD</sub> supplies power to the processor core and the PLL and DLL (after filtering to become AV<sub>DD</sub> and L2AV<sub>DD</sub>, respectively). These columns serve as a reference for the nominal voltage supported on a given signal as selected by the BVSEL/L2VSEL pin configurations of Table 2 and the voltage supplied. For actual recommended value of Vin or supply voltages, see Table 3.

- 2. These are test signals for factory use only and must be pulled up to OV<sub>DD</sub> for normal machine operation.

- 3. This pin must be pulled up to OV<sub>DD</sub> for proper operation of the processor interface. To allow for future I/O voltage changes, provide the option to connect BVSEL independently to either OV<sub>DD</sub> or GND.

- 4. These pins are reserved for potential future use as additional L2 address pins.

- 5. Uses one of nine existing no connects in the MPC750, 360 BGA package.

- 6. Internal pull-up on die.

- 7. This pin must be pulled up to L2OV<sub>DD</sub> for proper operation of the processor interface. To allow for future I/O voltage changes, provide the option to connect L2VSEL independently to either L2OV<sub>DD</sub> or GND.

- 8. Internally tied to L2OV<sub>DD</sub> in the MPC755, 360 BGA package to indicate the power present at the L2 cache interface. This signal is not a power supply input.

Caution: This differs from the MPC745, 255 BGA package.

#### **Package Description** 7

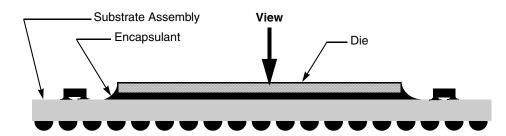

The following sections provide the package parameters and mechanical dimensions for the MPC745, 255 PBGA package, as well as the MPC755, 360 CBGA and PBGA packages. While both the MPC755 plastic and ceramic packages are described here, both packages are not guaranteed to be available at the same time. All new designs should allow for either ceramic or plastic BGA packages for this device. For more information on designing a common footprint for both plastic and ceramic package types, see the Freescale Flip-Chip Plastic Ball Grid Array Presentation. The MPC755 was initially sampled in a CBGA package, but production units are currently provided in both a CBGA and a PBGA package. Because of the better long-term device-to-board interconnect reliability of the PBGA package, Freescale recommends use of a PBGA package except where circumstances dictate use of a CBGA package.

Max

2.80

0.70

1.20

0.60

0.90

6.75

7.87

#### Package Parameters for the MPC745 PBGA 7.1

The package parameters are as provided in the following list. The package type is  $21 \times 21$  mm, 255-lead plastic ball grid array (PBGA).

Package outline  $21 \times 21 \text{ mm}$

Interconnects  $255 (16 \times 16 \text{ ball array} - 1)$

Pitch 1.27 mm (50 mil)

Minimum module height 2.25 mm Maximum module height 2.80 mm

Ball diameter (typical) 0.75 mm (29.5 mil)

#### 7.2 Mechanical Dimensions for the MPC745 PBGA

Figure 18 provides the mechanical dimensions and bottom surface nomenclature for the MPC745, 255 PBGA package.

Figure 18. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC745, 255 PBGA Package

MPC755 RISC Microprocessor Hardware Specifications, Rev. 8

**System Design Information**

# 8 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC755.

# 8.1 PLL Configuration

The MPC755 PLL is configured by the PLL\_CFG[0:3] signals. For a given SYSCLK (bus) frequency, the PLL configuration signals set the internal CPU and VCO frequency of operation. These must be chosen such that they comply with Table 8. Table 16 shows the valid configurations of these signals and an example illustrating the core and VCO frequencies resulting from various PLL configurations and example bus frequencies. In this example, shaded cells represent settings that, for a given SYSCLK frequency, result in core and/or VCO frequencies that do not comply with the 400-MHz column in Table 8.

Table 16. MPC755 Microprocessor PLL Configuration Example for 400 MHz Parts

|                  |                               | Example E                     | Bus-to-Core   | Frequency     | in MHz (VCC   | ) Frequency   | in MHz)       |                |

|------------------|-------------------------------|-------------------------------|---------------|---------------|---------------|---------------|---------------|----------------|

| PLL_CFG<br>[0:3] | Bus-to-<br>Core<br>Multiplier | Core-to-<br>VCO<br>Multiplier | Bus<br>33 MHz | Bus<br>50 MHz | Bus<br>66 MHz | Bus<br>75 MHz | Bus<br>80 MHz | Bus<br>100 MHz |

| 0100             | 2x                            | 2x                            | _             | _             | _             | _             | _             | 200<br>(400)   |

| 1000             | 3x                            | 2x                            | _             | _             | 200<br>(400)  | 225<br>(450)  | 240<br>(480)  | 300<br>(600)   |

| 1110             | 3.5x                          | 2x                            | _             | _             | 233<br>(466)  | 263<br>(525)  | 280<br>(560)  | 350<br>(700)   |

| 1010             | 4x                            | 2x                            | -             | 200<br>(400)  | 266<br>(533)  | 300<br>(600)  | 320<br>(640)  | 400<br>(800)   |

| 0111             | 4.5x                          | 2x                            | _             | 225<br>(450)  | 300<br>(600)  | 338<br>(675)  | 360<br>(720)  | _              |

| 1011             | 5x                            | 2x                            |               | 250<br>(500)  | 333<br>(666)  | 375<br>(750)  | 400<br>(800)  | _              |

| 1001             | 5.5x                          | 2x                            | _             | 275<br>(550)  | 366<br>(733)  | _             | _             | _              |

| 1101             | 6x                            | 2x                            | 200<br>(400)  | 300<br>(600)  | 400<br>(800)  | _             | _             | _              |

| 0101             | 6.5x                          | 2x                            | 216<br>(433)  | 325<br>(650)  | _             |               | _             | _              |

| 0010             | 7x                            | 2x                            | 233<br>(466)  | 350<br>(700)  | _             | _             | _             | _              |

| 0001             | 7.5x                          | 2x                            | 250<br>(500)  | 375<br>(750)  | _             | _             | _             | _              |

| 1100             | 8x                            | 2x                            | 266<br>(533)  | 400<br>(800)  | _             | _             | _             | _              |

| 0110             | 10x                           | 2x                            | 333<br>(666)  | _             | _             | _             | _             | _              |

These capacitors should have a value of 0.01 or 0.1 µF. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0508 or 0603 orientations where connections are made along the length of the part.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the V<sub>DD</sub>, L2OV<sub>DD</sub>, and OV<sub>DD</sub> planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors: 100–330 µF (AVX TPS tantalum or Sanyo OSCON).

#### 8.4 **Connection Recommendations**

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level through a resistor. Unused active low inputs should be tied to OV<sub>DD</sub>. Unused active high inputs should be connected to GND. All NC (no connect) signals must remain unconnected.

Power and ground connections must be made to all external V<sub>DD</sub>, OV<sub>DD</sub>, L2OV<sub>DD</sub>, and GND pins of the MPC755. Note that power must be supplied to L2OV<sub>DD</sub> even if the L2 interface of the MPC755 will not be used; it is recommended to connect L2OV<sub>DD</sub> to OV<sub>DD</sub> and L2VSEL to BVSEL if the L2 interface is unused. (This requirement does not apply to the MPC745 since it has neither an L2 interface nor L2OV<sub>DD</sub> pins.)

#### **Output Buffer DC Impedance** 8.5

The MPC755 60x and L2 I/O drivers are characterized over process, voltage, and temperature. To measure  $Z_0$ , an external resistor is connected from the chip pad to (L2)OV<sub>DD</sub> or GND. Then, the value of each resistor is varied until the pad voltage is (L2)OV<sub>DD</sub>/2 (see Figure 22).

The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held low, SW2 is closed (SW1 is open), and R<sub>N</sub> is trimmed until the voltage at the pad equals (L2)OV<sub>DD</sub>/2. R<sub>N</sub> then becomes the resistance of the pull-down devices. When data is held high, SW1 is closed (SW2 is open), and  $R_P$  is trimmed until the voltage at the pad equals (L2)OV<sub>DD</sub>/2.  $R_P$  then becomes the resistance of the pull-up devices.

MPC755 RISC Microprocessor Hardware Specifications, Rev. 8 Freescale Semiconductor 39

Table 18 summarizes the signal impedance results. The driver impedance values were characterized at 0°, 65°, and 105°C. The impedance increases with junction temperature and is relatively unaffected by bus voltage.

**Table 18. Impedance Characteristics**

$V_{DD} = 2.0 \text{ V}, \text{ OV}_{DD} = 3.3 \text{ V}, \text{ T}_{i} = 0^{\circ} - 105^{\circ}\text{C}$

| Impedance      | Processor Bus | L2 Bus | Symbol         | Unit |

|----------------|---------------|--------|----------------|------|

| R <sub>N</sub> | 25–36         | 25–36  | Z <sub>0</sub> | Ω    |

| R <sub>P</sub> | 26–39         | 26–39  | Z <sub>0</sub> | Ω    |

#### 8.6 **Pull-Up Resistor Requirements**

The MPC755 requires pull-up resistors (1–5 k $\Omega$ ) on several control pins of the bus interface to maintain the control signals in the negated state after they have been actively negated and released by the MPC755 or other bus masters. These pins are TS, ABB, AACK, ARTRY, DBB, DBWO, TA, TEA, and DBDIS. DRTRY should also be connected to a pull-up resistor  $(1-5 \text{ k}\Omega)$  if it will be used by the system; otherwise, this signal should be connected to HRESET to select NO-DRTRY mode (see the MPC750 RISC Microprocessor Family User's Manual for more information on this mode).

Three test pins also require pull-up resistors (100  $\Omega$ –1 k $\Omega$ ). These pins are L1 TSTCLK, L2 TSTCLK, and LSSD\_MODE. These signals are for factory use only and must be pulled up to OV<sub>DD</sub> for normal machine operation.

In addition,  $\overline{\text{CKSTP OUT}}$  is an open-drain style output that requires a pull-up resistor (1–5 k $\Omega$ ) if it is used by the system.

During inactive periods on the bus, the address and transfer attributes may not be driven by any master and may, therefore, float in the high-impedance state for relatively long periods of time. Since the MPC755 must continually monitor these signals for snooping, this float condition may cause additional power draw by the input receivers on the MPC755 or by other receivers in the system. These signals can be pulled up through weak (10-k $\Omega$ ) pull-up resistors by the system or may be otherwise driven by the system during inactive periods of the bus to avoid this additional power draw, but address bus pull-up resistors are not necessary for proper device operation. The snooped address and transfer attribute inputs are: A[0:31], AP[0:3], TT[0:4],  $\overline{TBST}$ , and  $\overline{GBL}$ .

The data bus input receivers are normally turned off when no read operation is in progress and, therefore, do not require pull-up resistors on the bus. Other data bus receivers in the system, however, may require pull-ups, or that those signals be otherwise driven by the system during inactive periods by the system. The data bus signals are: DH[0:31], DL[0:31], and DP[0:7].

If 32-bit data bus mode is selected, the input receivers of the unused data and parity bits will be disabled, and their outputs will drive logic zeros when they would otherwise normally be driven. For this mode, these pins do not require pull-up resistors, and should be left unconnected by the system to minimize possible output switching.

If address or data parity is not used by the system, and the respective parity checking is disabled through HID0, the input receivers for those pins are disabled, and those pins do not require pull-up resistors and

MPC755 RISC Microprocessor Hardware Specifications, Rev. 8 Freescale Semiconductor 41

## Notes:

- 1. RUN/STOP, normally found on pin 5 of the COP header, is not implemented on the MPC755. Connect pin 5 of the COP header to  $OV_{DD}$  with a 10-k $\Omega$  pull-up resistor.

- 2. Key location; pin 14 is not physically present on the COP header.

- 3. Component not populated. Populate only if debug tool does not drive QACK.

- 4. Populate only if debug tool uses an open-drain type output and does not actively deassert QACK.

- 5. If the JTAG interface is implemented, connect HRESET from the target source to TRST from the COP header though an AND gate to TRST of the part. If the JTAG interface is not implemented, connect HRESET from the target source to TRST of the part through a 0-Ω isolation resistor.

- 6. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown above.

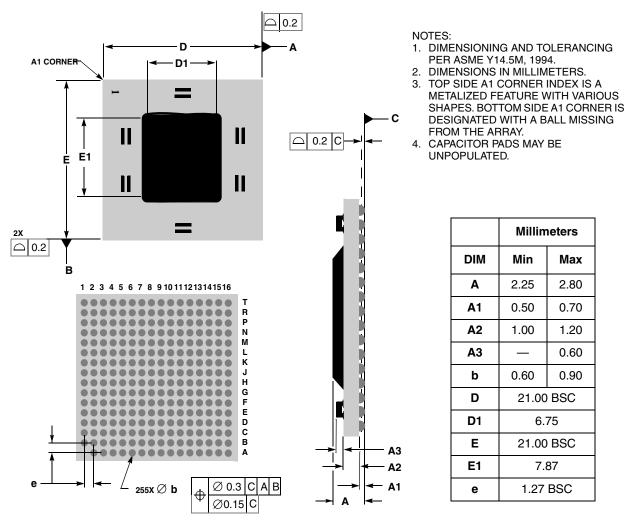

Figure 24. JTAG Interface Connection

Freescale Semiconductor 43

MPC755 RISC Microprocessor Hardware Specifications, Rev. 8

## **System Design Information**

Shin-Etsu MicroSi, Inc. 888-642-7674

10028 S. 51st St.

Phoenix, AZ 85044

Internet: www.microsi.com

Thermagon Inc. 888-246-9050

4707 Detroit Ave. Cleveland, OH 44102

Internet: www.thermagon.com

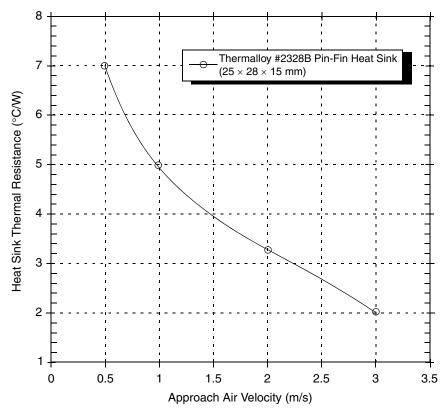

# 8.8.3 Heat Sink Selection Example

This section provides a heat sink selection example using one of the commercially-available heat sinks. For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_i = T_a + T_r + (\theta_{ic} + \theta_{int} + \theta_{sa}) \times P_d$$

where:

T<sub>i</sub> is the die-junction temperature

T<sub>a</sub> is the inlet cabinet ambient temperature

T<sub>r</sub> is the air temperature rise within the computer cabinet

$\theta_{ic}$  is the junction-to-case thermal resistance

$\theta_{\text{int}}$  is the adhesive or interface material thermal resistance

$\boldsymbol{\theta}_{sa}$  is the heat sink base-to-ambient thermal resistance

P<sub>d</sub> is the power dissipated by the device

During operation the die-junction temperatures  $(T_j)$  should be maintained less than the value specified in Table 3. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_a)$  may range from 30° to 40°C. The air temperature rise within a cabinet  $(T_r)$  may be in the range of 5° to 10°C. The thermal resistance of the thermal interface material  $(\theta_{int})$  is typically about 1°C/W. Assuming a  $T_a$  of 30°C, a  $T_r$  of 5°C, a CBGA package  $R_{\theta jc} < 0.1$ , and a power consumption  $(P_d)$  of 5.0 W, the following expression for  $T_j$  is obtained:

Die-junction temperature:  $T_i = 30^{\circ}C + 5^{\circ}C + (0.1^{\circ}C/W + 1.0^{\circ}C/W + \theta_{sa}) \times 5.0 \text{ W}$

For a Thermalloy heat sink #2328B, the heat sink-to-ambient thermal resistance ( $\theta_{sa}$ ) versus airflow velocity is shown in Figure 28.

Assuming an air velocity of 0.5 m/s, we have an effective  $R_{sa}$  of 7°C/W, thus

$$T_i = 30^{\circ}C + 5^{\circ}C + (0.1^{\circ}C/W + 1.0^{\circ}C/W + 7^{\circ}C/W) \times 5.0 W,$$

resulting in a die-junction temperature of approximately 76°C which is well within the maximum operating temperature of the component.

Other heat sinks offered by Aavid Thermalloy, Alpha Novatech, The Bergquist Company, IERC, Chip Coolers, and Wakefield Engineering offer different heat sink-to-ambient thermal resistances, and may or may not need airflow.

Figure 28. Thermalloy #2328B Heat Sink-to-Ambient Thermal Resistance Versus Airflow Velocity

Though the die junction-to-ambient and the heat sink-to-ambient thermal resistances are a common figure-of-merit used for comparing the thermal performance of various microelectronic packaging technologies, one should exercise caution when only using this metric in determining thermal management because no single parameter can adequately describe three-dimensional heat flow. The final die-junction operating temperature, is not only a function of the component-level thermal resistance, but the system-level design and its operating conditions. In addition to the component's power consumption, a number of factors affect the final operating die-junction temperature—airflow, board population (local heat flux of adjacent components), heat sink efficiency, heat sink attach, heat sink placement, next-level interconnect technology, system air temperature rise, altitude, etc.

Due to the complexity and the many variations of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection, and conduction) may vary widely. For these reasons, we recommend using conjugate heat transfer models for the board, as well as, system-level designs.

# 10.3 Part Marking

Parts are marked as the example shown in Figure 29.

## Notes:

MMMMMM is the 6-digit mask number. ATWLYYWWA is the traceability code.

CCCCC is the country of assembly. This space is left blank if parts are assembled in the United States.

Figure 29. Part Marking for BGA Device