Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | ARM® Cortex®-M4                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 180MHz                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                            |

| Number of I/O              | 100                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | 4K x 8                                                                               |

| RAM Size                   | 256K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                         |

| Data Converters            | A/D 2x16b; D/A 2x12b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | 144-LQFP (20x20)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk66fx1m0vlq18               |

## 1 Ratings

#### 1.1 Thermal handling ratings

| Symbol           | Description                   | Min.        | Max. | Unit | Notes |

|------------------|-------------------------------|-------------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | <b>–</b> 55 | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _           | 260  | °C   | 2     |

- 1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

- 2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

#### 1.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | _    | 3    | _    | 1     |

Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

#### 1.3 ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| $V_{HBM}$        | Electrostatic discharge voltage, human body model     | -2000 | +2000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 105°C      | -100  | +100  | mA   | 3     |

- 1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

- 2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

- 3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

### 1.4 Voltage and current operating ratings

# 2.2.5 Power consumption operating behaviors

#### **NOTE**

The maximum values represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma)

Table 7. Power consumption operating behaviors

| Symbol                      | Description                                                                                                                                         | Min. | Тур. | Max.     | Unit  | Notes |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|-------|-------|

| I <sub>DDA</sub>            | Analog supply current                                                                                                                               | _    | _    | See note | mA    | 1     |

| I <sub>DD_RUN</sub>         | Run mode current — all peripheral clocks disabled, code executing from flash                                                                        |      |      |          |       | 2     |

|                             | • @ 1.8V                                                                                                                                            | _    | 32.3 | 71.03    | mA    |       |

|                             | • @ 3.0V                                                                                                                                            | _    | 32.4 | 71.81    | mA    |       |

| I <sub>DD_RUN</sub>         | Run mode current — all peripheral clocks enabled, code executing from flash                                                                         |      |      |          |       | 3, 4  |

|                             | • @ 1.8V                                                                                                                                            | _    | 50.5 | 89.58    | mA    |       |

|                             | • @ 3.0V                                                                                                                                            |      |      |          |       |       |

|                             | • @ 25°C                                                                                                                                            | _    | 50.6 | 55.95    | mA    |       |

|                             | • @ 105°C                                                                                                                                           | _    | 69.7 | 99.85    | mA    |       |

| I <sub>DD_RUNC</sub>        | Run mode current in compute operation - 120 MHz core / 24 MHz flash / bus clock disabled, code of while(1) loop executing from flash                | _    | 28.5 | 67.74    | mA    | 5     |

|                             | • at 3.0 V                                                                                                                                          |      |      |          |       |       |

| I <sub>DD_HSRUN</sub>       | Run mode current — all peripheral clocks disabled, code executing from flash                                                                        |      |      |          |       | 6     |

|                             | • @ 1.8V                                                                                                                                            | _    | 47.2 | 91.25    | mA    |       |

|                             | • @ 3.0V                                                                                                                                            | _    | 47.3 | 91.62    | mA    |       |

| I <sub>DD_HSRUN</sub>       | Run mode current — all peripheral clocks enabled, code executing from flash                                                                         |      |      |          |       | 7, 4  |

|                             | • @ 1.8V                                                                                                                                            | _    | 71.4 | 103.58   | mA    |       |

|                             | • @ 3.0V                                                                                                                                            |      | 71.5 | 79.13    | mA    |       |

|                             | • @ 25°C                                                                                                                                            | _    | 93.3 | 115.08   | mA    |       |

|                             | • @ 105°C                                                                                                                                           | _    | 55.5 | 110.00   | 111/1 |       |

| I <sub>DD_HSRUN</sub><br>CO | HSRun mode current in compute operation – 168<br>MHz core/ 28 MHz flash / bus clock disabled,<br>code of while(1) loop executing from flash at 3.0V | _    | 42.9 | 91.97    | mA    | 5     |

| I <sub>DD_WAIT</sub>        | Wait mode high frequency current at 3.0 V — all peripheral clocks disabled                                                                          | _    | 16.9 | 45.2     | mA    | 8     |

Table continues on the next page...

- 8. 120 MHz core and system clock, 60MHz bus clock, and FlexBus. MCG configured for PEE mode.

- 9. 4 MHz core, system, FlexBus, and bus clock and 1 MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 10. 4 MHz core, system, FlexBus, and bus clock and 1 MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing from flash.

- MCG configured for BLPI mode. CoreMark benchmark compiled using IAR 6.40 with optimization level high, optimized for balanced.

- 12. 4 MHz core, system, FlexBus, and bus clock and 1 MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

- 13. Includes 32kHz oscillator current and RTC operation.

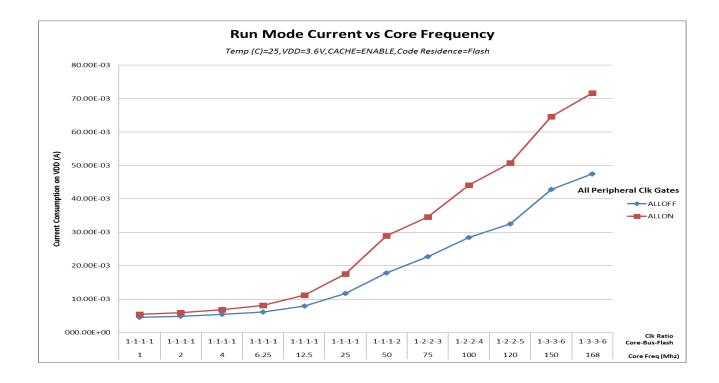

#### 2.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFE

Figure 3. Run mode supply current vs. core frequency

#### 3.3.2 IRC48M specifications

Table 17. IRC48M specifications

| Symbol                     | Description                                                                                                                                                  | Min. | Тур.  | Max.  | Unit                 | Notes |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|----------------------|-------|

| V <sub>DD</sub>            | Supply voltage                                                                                                                                               | 1.71 | _     | 3.6   | V                    |       |

| I <sub>DD48M</sub>         | Supply current                                                                                                                                               | _    | 520   | _     | μA                   |       |

| f <sub>irc48m</sub>        | Internal reference frequency                                                                                                                                 | _    | 48    | _     | MHz                  |       |

| Δf <sub>irc48m_ol_lv</sub> | Open loop total deviation of IRC48M frequency at low voltage (VDD=1.71V-1.89V) over full temperature  • Regulator disable                                    | _    | ± 0.4 | ± 1.0 | %f <sub>irc48m</sub> | 1     |

|                            | (USB_CLK_RECOVER_IRC_EN[REG_EN]=0 ) • Regulator enable (USB_CLK_RECOVER_IRC_EN[REG_EN]=1 )                                                                   | _    | ± 0.5 | ± 1.5 |                      |       |

| Δf <sub>irc48m_ol_hv</sub> | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over 0—70°C  • Regulator enable (USB_CLK_RECOVER_IRC_EN[REG_EN]=1             |      | ± 0.2 | ± 0.5 | %f <sub>irc48m</sub> | 1     |

| Δf <sub>irc48m_ol_hv</sub> | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over full temperature  • Regulator enable  (USB_CLK_RECOVER_IRC_EN[REG_EN]=1) | _    | ± 0.4 | ± 1.0 | %f <sub>irc48m</sub> | 1     |

| Δf <sub>irc48m_cl</sub>    | Closed loop total deviation of IRC48M frequency over voltage and temperature                                                                                 | _    | _     | ± 0.1 | %f <sub>host</sub>   | 2     |

| J <sub>cyc_irc48m</sub>    | Period Jitter (RMS)                                                                                                                                          |      | 35    | 150   | ps                   |       |

| t <sub>irc48mst</sub>      | Startup time                                                                                                                                                 | _    | 2     | 3     | μs                   | 3     |

<sup>1.</sup> The maximum value represents characterized results equivalent to mean plus or minus three times the standard deviation (mean ± 3 sigma)

- USB\_CLK\_RECOVER\_IRC\_EN[IRC\_EN]=1, or

- MCG\_C7[OSCSEL]=10, or

- SIM\_SOPT2[PLLFLLSEL]=11

### 3.3.3 Oscillator electrical specifications

<sup>2.</sup> Closed loop operation of the IRC48M is only feasible for USB device operation; it is not usable for USB host operation. It is enabled by configuring for USB Device, selecting IRC48M as USB clock source, and enabling the clock recover function (USB\_CLK\_RECOVER\_IRC\_CTRL[CLOCK\_RECOVER\_EN]=1, USB\_CLK\_RECOVER\_IRC\_EN[IRC\_EN]=1).

<sup>3.</sup> IRC48M startup time is defined as the time between clock enablement and clock availability for system use. Enable the clock by one of the following settings:

# 3.4.1.3 Flash high voltage current behaviors Table 24. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation | _    | 3.5  | 7.5  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       |      | 1.5  | 4.0  | mA   |

#### 3.4.1.4 Reliability specifications

#### Table 25. NVM reliability specifications

| Symbol                   | Description                                  |        | Typ. <sup>1</sup> | Max. | Unit   | Notes |  |  |  |  |

|--------------------------|----------------------------------------------|--------|-------------------|------|--------|-------|--|--|--|--|

|                          | Program Flash                                |        |                   |      |        |       |  |  |  |  |

| t <sub>nvmretp10k</sub>  | Data retention after up to 10 K cycles       | 5      | 50                | _    | years  |       |  |  |  |  |

| t <sub>nvmretp1k</sub>   | Data retention after up to 1 K cycles        | 20     | 100               | _    | years  |       |  |  |  |  |

| n <sub>nvmcycp</sub>     | Cycling endurance                            | 10 K   | 50 K              | _    | cycles | 2     |  |  |  |  |

|                          | Data Flas                                    | sh     |                   |      |        |       |  |  |  |  |

| t <sub>nvmretd10k</sub>  | Data retention after up to 10 K cycles       | 5      | 50                | _    | years  |       |  |  |  |  |

| t <sub>nvmretd1k</sub>   | Data retention after up to 1 K cycles        | 20     | 100               | _    | years  |       |  |  |  |  |

| n <sub>nvmcycd</sub>     | Cycling endurance                            | 10 K   | 50 K              | _    | cycles | 2     |  |  |  |  |

|                          | FlexRAM as El                                | EPROM  |                   |      |        |       |  |  |  |  |

| t <sub>nvmretee100</sub> | Data retention up to 100% of write endurance | 5      | 50                | _    | years  |       |  |  |  |  |

| t <sub>nvmretee10</sub>  | Data retention up to 10% of write endurance  | 20     | 100               | _    | years  |       |  |  |  |  |

| n <sub>nvmcycee</sub>    | Cycling endurance for EEPROM backup          | 20 K   | 50 K              | _    | cycles | 2     |  |  |  |  |

|                          | Write endurance                              |        |                   |      |        | 3     |  |  |  |  |

| n <sub>nvmwree16</sub>   | EEPROM backup to FlexRAM ratio = 16          | 140 K  | 400 K             | _    | writes |       |  |  |  |  |

| n <sub>nvmwree128</sub>  | EEPROM backup to FlexRAM ratio = 128         | 1.26 M | 3.2 M             | _    | writes |       |  |  |  |  |

| n <sub>nvmwree512</sub>  | EEPROM backup to FlexRAM ratio = 512         | 5 M    | 12.8 M            | _    | writes |       |  |  |  |  |

| n <sub>nvmwree2k</sub>   | EEPROM backup to FlexRAM ratio = 2,048       | 20 M   | 50 M              | _    | writes |       |  |  |  |  |

| n <sub>nvmwree8k</sub>   | EEPROM backup to FlexRAM ratio = 8,192       | 80 M   | 200 M             | _    | writes |       |  |  |  |  |

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

<sup>2.</sup> Cycling endurance represents number of program/erase cycles at -40°C ≤ T<sub>i</sub> ≤ 125°C.

<sup>3.</sup> Write endurance represents the number of writes to each FlexRAM location at -40°C ≤Tj ≤ 125°C influenced by the cycling endurance of the FlexNVM and the allocated EEPROM backup per subsystem. Minimum and typical values assume all 16-bit or 32-bit writes to FlexRAM; all 8-bit writes result in 50% less endurance.

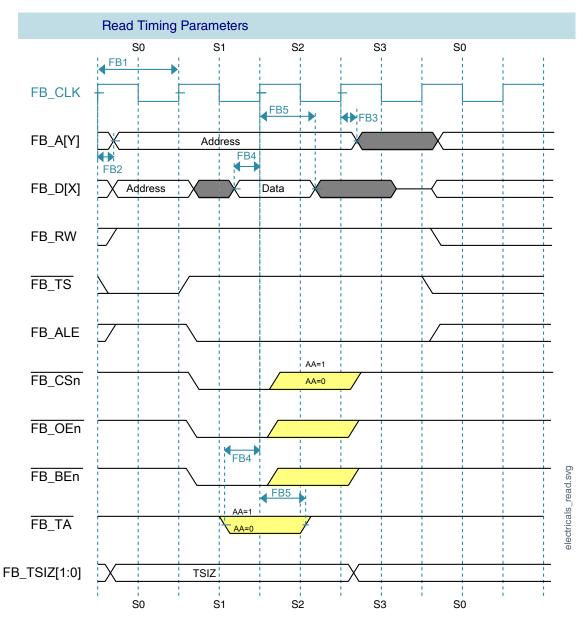

Figure 13. FlexBus read timing diagram

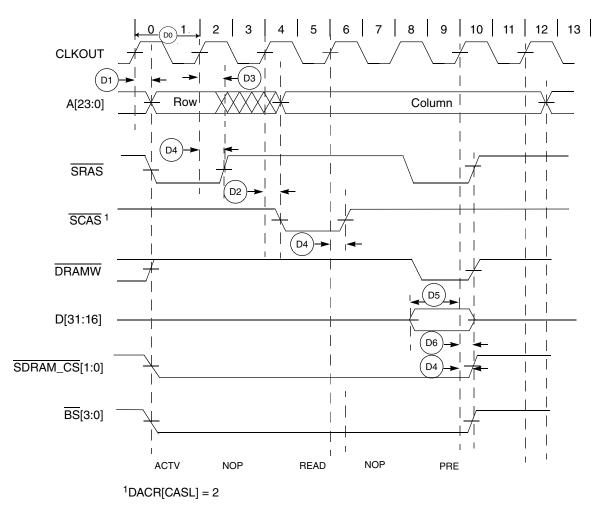

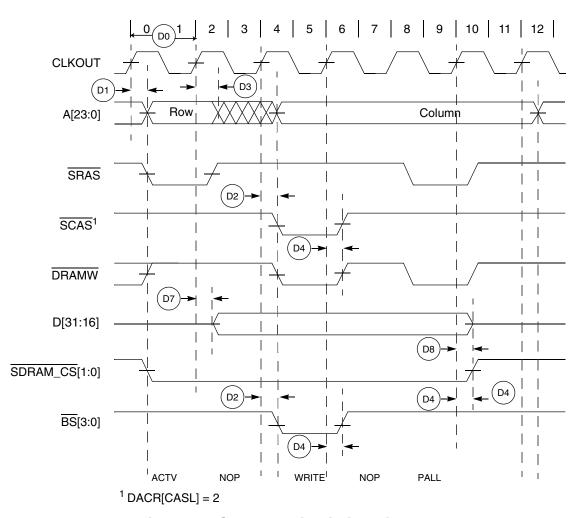

Figure 15. SDRAM read timing diagram

**Table 29. SDRAM Timing (Full voltage range)**

| NUM             | Characteristic <sup>1</sup>          | Symbol              | MIn    | Max  | Unit |

|-----------------|--------------------------------------|---------------------|--------|------|------|

|                 | Operating voltage                    | 1.71                | 3.6    | V    |      |

|                 | Frequency of operation               | _                   | CLKOUT | MHz  |      |

| D0              | Clock period                         | 1/CLKOUT            | _      | ns   | 2    |

| D1              | CLKOUT high to SDRAM address valid   | t <sub>CHDAV</sub>  | -      | 11.2 | ns   |

| D2              | CLKOUT high to SDRAM control valid   | t <sub>CHDCV</sub>  |        | 11.1 | ns   |

| D3              | CLKOUT high to SDRAM address invalid | t <sub>CHDAI</sub>  | 1.0    | -    | ns   |

| D4              | CLKOUT high to SDRAM control invalid | t <sub>CHDCI</sub>  | 1.0    | -    | ns   |

| D5              | SDRAM data valid to CLKOUT high      | t <sub>DDVCH</sub>  | 12.0   | -    | ns   |

| D6              | CLKOUT high to SDRAM data invalid    | tchddi              | 1.0    | -    | ns   |

| D7 <sup>3</sup> | CLKOUT high to SDRAM data valid      | t <sub>CHDDVW</sub> | -      | 12.0 | ns   |

| D8 <sup>3</sup> | CLKOUT high to SDRAM data invalid    | t <sub>CHDDIW</sub> | 1.0    | -    | ns   |

<sup>1.</sup> All timing specifications are based on taking into account, a 25pF load on the SDRAM output pins.

<sup>2.</sup> CLKOUT is same as FB\_CLK, maximum frequency can be 60 MHz

Figure 16. SDRAM write timing diagram

## 3.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

#### 3.6 Analog

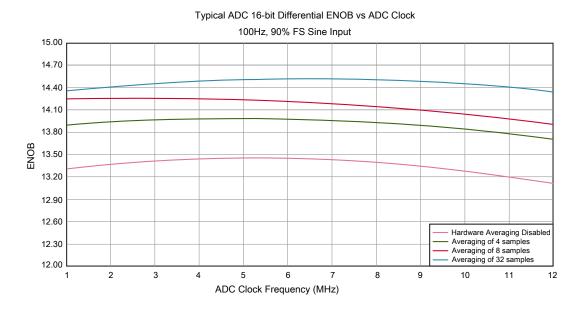

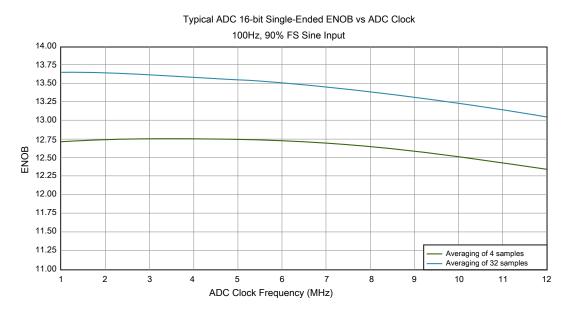

#### 3.6.1 ADC electrical specifications

The 16-bit accuracy specifications listed in Table 31 and Table 32 are achievable on the differential pins ADCx\_DP0, ADCx\_DM0.

- 2. Typical values assume  $V_{DDA} = 3.0 \text{ V}$ , Temp = 25 °C,  $f_{ADCK} = 2.0 \text{ MHz}$  unless otherwise stated. Typical values are for reference only and are not tested in production.

- 3. The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4.  $1 LSB = (V_{REFH} V_{REFL})/2^{N}$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Figure 18. Typical ENOB vs. ADC\_CLK for 16-bit differential mode

Figure 19. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

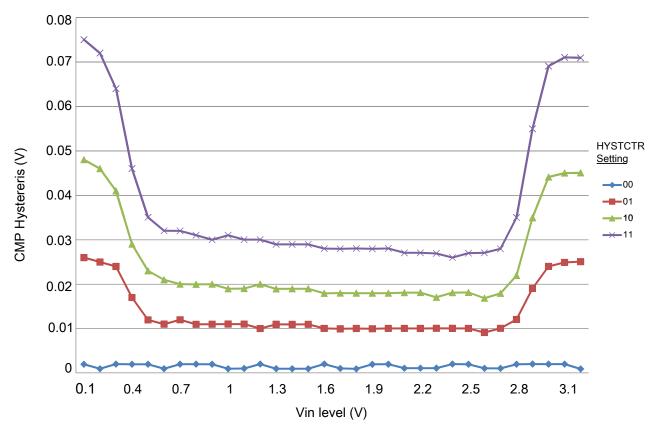

### 3.6.2 CMP and 6-bit DAC electrical specifications

Table 33. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| $V_{DD}$           | Supply voltage                                      | 1.71                  | _    | 3.6             | V                |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)     | _                     | _    | 200             | μΑ               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      | _                     | _    | 20              | μΑ               |

| V <sub>AIN</sub>   | Analog input voltage                                | V <sub>SS</sub> - 0.3 | _    | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | _                     | _    | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | _                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | _                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | _                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | _                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 | _    | _               | V                |

| V <sub>CMPOI</sub> | Output low                                          | _                     | _    | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> | _                     | _    | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   | _                     | 7    | _               | μΑ               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  | _    | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  | _    | 0.3             | LSB              |

<sup>1.</sup> Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD}$ -0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

<sup>3.</sup>  $1 LSB = V_{reference}/64$

Figure 20. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

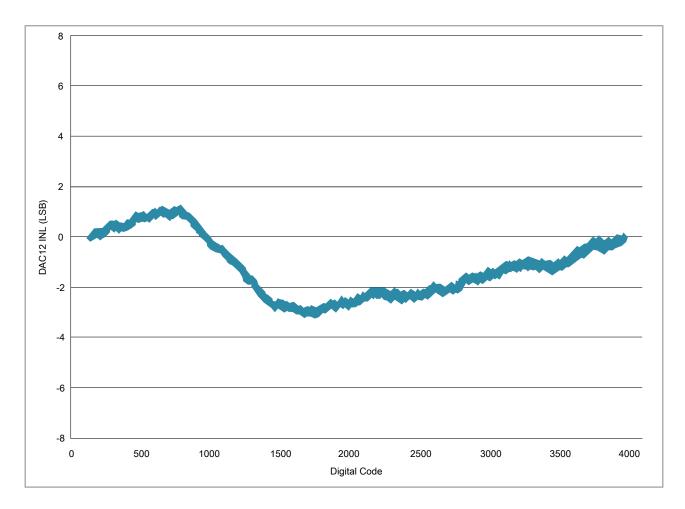

6.  $V_{DDA} = 3.0 \text{ V}$ , reference select set for  $V_{DDA}$  (DACx\_CO:DACRFS = 1), high power mode (DACx\_C0:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

Figure 22. Typical INL error vs. digital code

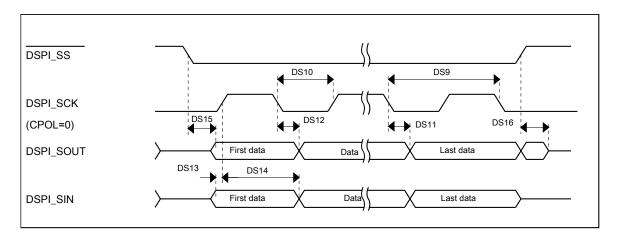

Figure 30. DSPI classic SPI timing — slave mode

# 3.8.8 Inter-Integrated Circuit Interface (I<sup>2</sup>C) timing Table 51. I<sup>2</sup>C timing

| Characteristic                                                                               | Symbol                | Standa           | rd Mode           | Fast                               | Mode             | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------|------------------------------------|------------------|------|

|                                                                                              |                       | Minimum          | Maximum           | Minimum                            | Maximum          |      |

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>      | 0                | 100               | 0                                  | 400              | kHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | t <sub>HD</sub> ; STA | 4                | _                 | 0.6                                | _                | μs   |

| LOW period of the SCL clock                                                                  | t <sub>LOW</sub>      | 4.7              | _                 | 1.25                               | _                | μs   |

| HIGH period of the SCL clock                                                                 | t <sub>HIGH</sub>     | 4                | _                 | 0.6                                | _                | μs   |

| Set-up time for a repeated START condition                                                   | t <sub>SU</sub> ; STA | 4.7              | _                 | 0.6                                | _                | μs   |

| Data hold time for I <sup>2</sup> C bus devices                                              | t <sub>HD</sub> ; DAT | 01               | 3.45 <sup>2</sup> | 0 <sup>3</sup>                     | 0.9 <sup>1</sup> | μs   |

| Data set-up time                                                                             | t <sub>SU</sub> ; DAT | 250 <sup>4</sup> | _                 | 100 <sup>2, 5</sup>                | _                | ns   |

| Rise time of SDA and SCL signals                                                             | t <sub>r</sub>        | _                | 1000              | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns   |

| Fall time of SDA and SCL signals                                                             | t <sub>f</sub>        | _                | 300               | 20 +0.1C <sub>b</sub> <sup>5</sup> | 300              | ns   |

| Set-up time for STOP condition                                                               | t <sub>SU</sub> ; STO | 4                | _                 | 0.6                                | _                | μs   |

| Bus free time between STOP and START condition                                               | t <sub>BUF</sub>      | 4.7              | _                 | 1.3                                | _                | μs   |

| Pulse width of spikes that must be suppressed by the input filter                            | t <sub>SP</sub>       | N/A              | N/A               | 0                                  | 50               | ns   |

- The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves

acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL

lines.

- 2. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 3. Input signal Slew = 10 ns and Output Load = 50 pF

- 4. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 5. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement  $t_{SU; DAT} \ge 250$  ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such

### 3.8.10 Low Power UART switching specifications

See General switching specifications.

#### 3.8.11 SDHC specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

Table 53. SDHC full voltage range switching specifications

| Num | Symbol           | Description                                     | Min.          | Max.      | Unit |

|-----|------------------|-------------------------------------------------|---------------|-----------|------|

|     |                  | Operating voltage                               | 1.71          | 3.6       | V    |

|     |                  | Card input clock                                |               |           |      |

| SD1 | fpp              | Clock frequency (low speed)                     | 0             | 400       | kHz  |

|     | fpp              | Clock frequency (SD\SDIO full speed\high speed) | 0             | 25\50     | MHz  |

|     | fpp              | Clock frequency (MMC full speed\high speed)     | 0             | 20\50     | MHz  |

|     | f <sub>OD</sub>  | Clock frequency (identification mode)           | 0             | 400       | kHz  |

| SD2 | t <sub>WL</sub>  | Clock low time                                  | 7             | _         | ns   |

| SD3 | t <sub>WH</sub>  | Clock high time                                 | 7             | _         | ns   |

| SD4 | t <sub>TLH</sub> | Clock rise time                                 | _             | 3         | ns   |

| SD5 | t <sub>THL</sub> | Clock fall time                                 | _             | 3         | ns   |

|     |                  | SDHC output / card inputs SDHC_CMD, SDHC_DAT    | (reference to | SDHC_CLK) |      |

| SD6 | t <sub>OD</sub>  | SDHC output delay (output valid)                | -5            | 8.6 8.3   | ns   |

|     |                  | SDHC input / card inputs SDHC_CMD, SDHC_DAT     | reference to  | SDHC_CLK) |      |

| SD7 | t <sub>ISU</sub> | SDHC input setup time                           | 5             | _         | ns   |

| SD8 | t <sub>IH</sub>  | SDHC input hold time                            | 0             |           | ns   |

Table 54. SDHC limited voltage range switching specifications

| Num | Symbol           | Description                                     | Min. | Max.  | Unit |  |  |  |

|-----|------------------|-------------------------------------------------|------|-------|------|--|--|--|

|     |                  | Operating voltage                               | 2.7  | 3.6   | V    |  |  |  |

|     | Card input clock |                                                 |      |       |      |  |  |  |

| SD1 | fpp              | Clock frequency (low speed)                     | 0    | 400   | kHz  |  |  |  |

|     | fpp              | Clock frequency (SD\SDIO full speed\high speed) | 0    | 25\50 | MHz  |  |  |  |

|     | fpp              | Clock frequency (MMC full speed\high speed)     | 0    | 20\50 | MHz  |  |  |  |

|     | f <sub>OD</sub>  | Clock frequency (identification mode)           | 0    | 400   | kHz  |  |  |  |

| SD2 | t <sub>WL</sub>  | Clock low time                                  | 7    | _     | ns   |  |  |  |

| SD3 | t <sub>WH</sub>  | Clock high time                                 | 7    | _     | ns   |  |  |  |

| SD4 | t <sub>TLH</sub> | Clock rise time                                 | _    | 3     | ns   |  |  |  |

| SD5 | t <sub>THL</sub> | Clock fall time                                 | _    | 3     | ns   |  |  |  |

Table continues on the next page...

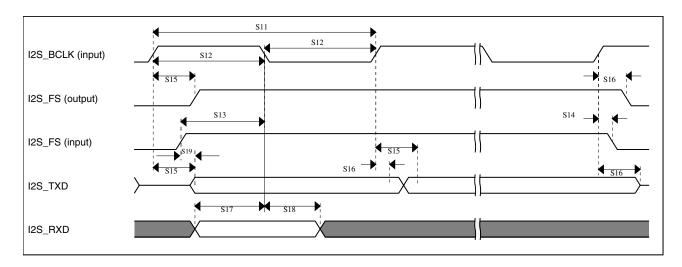

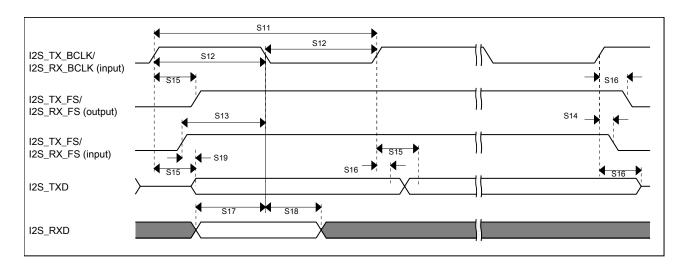

Figure 34. I<sup>2</sup>S timing — slave modes

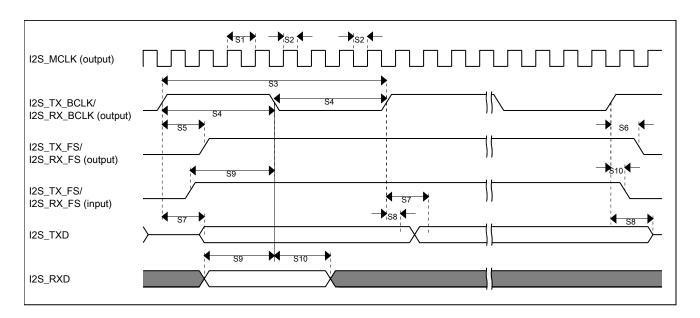

# 3.8.12.1 Normal Run, Wait and Stop mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in Normal Run, Wait and Stop modes.

Num. Characteristic Min. Max. Unit Operating voltage 1.71 3.6 ٧ S1 I2S\_MCLK cycle time 40 ns S2 I2S\_MCLK (as an input) pulse width high/low 45% 55% MCLK period S3 I2S\_TX\_BCLK/I2S\_RX\_BCLK cycle time (output) 80 I2S\_TX\_BCLK/I2S\_RX\_BCLK pulse width high/low S4 45% 55% BCLK period **S5** I2S\_TX\_BCLK/I2S\_RX\_BCLK to I2S\_TX\_FS/ 15 ns I2S\_RX\_FS output valid **S6** I2S\_TX\_BCLK/I2S\_RX\_BCLK to I2S\_TX\_FS/ 0 ns I2S\_RX\_FS output invalid S7 I2S\_TX\_BCLK to I2S\_TXD valid 15 ns S8 I2S\_TX\_BCLK to I2S\_TXD invalid 0 ns S9 I2S\_RXD/I2S\_RX\_FS input setup before 15 ns I2S\_RX\_BCLK S10 I2S\_RXD/I2S\_RX\_FS input hold after 0 ns I2S\_RX\_BCLK

Table 57. I2S/SAI master mode timing

Figure 35. I2S/SAI timing — master modes

Table 58. I2S/SAI slave mode timing

| Num. | Characteristic                                                 | Min. | Max. | Unit        |

|------|----------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                              | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                     | 80   | _    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)           | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before I2S_TX_BCLK/I2S_RX_BCLK | 4.5  | _    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after I2S_TX_BCLK/I2S_RX_BCLK   | 2    | _    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                  | _    | 23.1 | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                | 0    | _    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                               | 4.5  | _    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                 | 2    | _    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup> | _    | 25   | ns          |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

Figure 38. I2S/SAI timing — slave modes

## 3.9 Human-machine interfaces (HMI)

## 3.9.1 TSI electrical specifications

Table 61. TSI electrical specifications

| Symbol    | Description                                                                        | Min. | Тур. | Max. | Unit |

|-----------|------------------------------------------------------------------------------------|------|------|------|------|

| TSI_RUNF  | Fixed power consumption in run mode                                                | _    | 100  | _    | μΑ   |

| TSI_RUNV  | Variable power consumption in run mode (depends on oscillator's current selection) | 1.0  | _    | 128  | μΑ   |

| TSI_EN    | Power consumption in enable mode                                                   | _    | 100  | _    | μΑ   |

| TSI_DIS   | Power consumption in disable mode                                                  | _    | 1.2  | _    | μΑ   |

| TSI_TEN   | TSI analog enable time                                                             | _    | 66   | _    | μs   |

| TSI_CREF  | TSI reference capacitor                                                            | _    | 1.0  | _    | pF   |

| TSI_DVOLT | Voltage variation of VP & VM around nominal values                                 | 0.19 | _    | 1.03 | V    |

#### 4 Dimensions

# 4.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

| 144<br>LQFP | 144<br>MAP<br>BGA | Pin Name           | Default                              | ALT0                                 | ALT1               | ALT2      | ALT3             | ALT4                | ALT5                                                                      | ALT6             | ALT7           | EzPort |

|-------------|-------------------|--------------------|--------------------------------------|--------------------------------------|--------------------|-----------|------------------|---------------------|---------------------------------------------------------------------------|------------------|----------------|--------|

| 103         | B12               | PTC0               | ADC0_SE14/<br>TSI0_CH13              | ADC0_SE14/<br>TSI0_CH13              | PTC0               | SPI0_PCS4 | PDB0_<br>EXTRG   | USB0_SOF_<br>OUT    | FB_AD14/<br>SDRAM_A22                                                     | 12S0_TXD1        |                |        |

| 104         | B11               | PTC1/<br>LLWU_P6   | ADC0_SE15/<br>TSI0_CH14              | ADC0_SE15/<br>TSI0_CH14              | PTC1/<br>LLWU_P6   | SPI0_PCS3 | UART1_<br>RTS_b  | FTM0_CH0            | FB_AD13/<br>SDRAM_A21                                                     | I2S0_TXD0        |                |        |

| 105         | A12               | PTC2               | ADC0_SE4b/<br>CMP1_IN0/<br>TSI0_CH15 | ADC0_SE4b/<br>CMP1_IN0/<br>TSI0_CH15 | PTC2               | SPI0_PCS2 | UART1_<br>CTS_b  | FTM0_CH1            | FB_AD12/<br>SDRAM_A20                                                     | I2S0_TX_FS       |                |        |

| 106         | A11               | PTC3/<br>LLWU_P7   | CMP1_IN1                             | CMP1_IN1                             | PTC3/<br>LLWU_P7   | SPI0_PCS1 | UART1_RX         | FTM0_CH2            | CLKOUT                                                                    | I2S0_TX_<br>BCLK |                |        |

| 107         | H8                | VSS                | VSS                                  | VSS                                  |                    |           |                  |                     |                                                                           |                  |                |        |

| 108         | _                 | VDD                | VDD                                  | VDD                                  |                    |           |                  |                     |                                                                           |                  |                |        |

| 109         | A9                | PTC4/<br>LLWU_P8   | DISABLED                             |                                      | PTC4/<br>LLWU_P8   | SPI0_PCS0 | UART1_TX         | FTM0_CH3            | FB_AD11/<br>SDRAM_A19                                                     | CMP1_OUT         |                |        |

| 110         | D8                | PTC5/<br>LLWU_P9   | DISABLED                             |                                      | PTC5/<br>LLWU_P9   | SPI0_SCK  | LPTMR0_<br>ALT2  | I2S0_RXD0           | FB_AD10/<br>SDRAM_A18                                                     | CMP0_OUT         | FTM0_CH2       |        |

| 111         | C8                | PTC6/<br>LLWU_P10  | CMP0_IN0                             | CMP0_IN0                             | PTC6/<br>LLWU_P10  | SPI0_SOUT | PDB0_<br>EXTRG   | I2S0_RX_<br>BCLK    | FB_AD9/<br>SDRAM_A17                                                      | I2S0_MCLK        |                |        |

| 112         | B8                | PTC7               | CMP0_IN1                             | CMP0_IN1                             | PTC7               | SPI0_SIN  | USB0_SOF_<br>OUT | 12S0_RX_FS          | FB_AD8/<br>SDRAM_A16                                                      |                  |                |        |

| 113         | A8                | PTC8               | ADC1_SE4b/<br>CMP0_IN2               | ADC1_SE4b/<br>CMP0_IN2               | PTC8               |           | FTM3_CH4         | I2S0_MCLK           | FB_AD7/<br>SDRAM_A15                                                      |                  |                |        |

| 114         | D7                | PTC9               | ADC1_SE5b/<br>CMP0_IN3               | ADC1_SE5b/<br>CMP0_IN3               | PTC9               |           | FTM3_CH5         | I2S0_RX_<br>BCLK    | FB_AD6/<br>SDRAM_A14                                                      | FTM2_FLT0        |                |        |

| 115         | C7                | PTC10              | ADC1_SE6b                            | ADC1_SE6b                            | PTC10              | I2C1_SCL  | FTM3_CH6         | 12S0_RX_FS          | FB_AD5/<br>SDRAM_A13                                                      |                  |                |        |

| 116         | В7                | PTC11/<br>LLWU_P11 | ADC1_SE7b                            | ADC1_SE7b                            | PTC11/<br>LLWU_P11 | I2C1_SDA  | FTM3_CH7         | 12S0_RXD1           | FB_RW_b                                                                   |                  |                |        |

| 117         | A7                | PTC12              | DISABLED                             |                                      | PTC12              |           | UART4_<br>RTS_b  | FTM_CLKIN0          | FB_AD27/<br>SDRAM_D27                                                     | FTM3_FLT0        | TPM_<br>CLKIN0 |        |

| 118         | D6                | PTC13              | DISABLED                             |                                      | PTC13              |           | UART4_<br>CTS_b  | FTM_CLKIN1          | FB_AD26/<br>SDRAM_D26                                                     |                  | TPM_<br>CLKIN1 |        |

| 119         | C6                | PTC14              | DISABLED                             |                                      | PTC14              |           | UART4_RX         |                     | FB_AD25/<br>SDRAM_D25                                                     |                  |                |        |

| 120         | В6                | PTC15              | DISABLED                             |                                      | PTC15              |           | UART4_TX         |                     | FB_AD24/<br>SDRAM_D24                                                     |                  |                |        |

| 121         | _                 | VSS                | VSS                                  | VSS                                  |                    |           |                  |                     |                                                                           |                  |                |        |

| 122         | -                 | VDD                | VDD                                  | VDD                                  |                    |           |                  |                     |                                                                           |                  |                |        |

| 123         | A6                | PTC16              | DISABLED                             |                                      | PTC16              | CAN1_RX   | UART3_RX         | ENETO_<br>1588_TMR0 | FB_CS5_b/<br>FB_TSIZ1/<br>FB_BE23_<br>16_BLS15_<br>8_b/<br>SDRAM_<br>DQM2 |                  |                |        |

| 124         | D5                | PTC17              | DISABLED                             |                                      | PTC17              | CAN1_TX   | UART3_TX         | ENET0_<br>1588_TMR1 | FB_CS4_b/<br>FB_TSIZ0/                                                    |                  |                |        |

Table 62. Recommended connection for unused analog interfaces (continued)

| Pin Type | K66       | Short recommendation                  | Detailed recommendation                      |

|----------|-----------|---------------------------------------|----------------------------------------------|

| USB      | VREG_IN1  | Tie to output and ground through 10kΩ | Tie to output and ground through $10k\Omega$ |

| USB      | USB1_VSS  | Always connect to VSS                 | Always connect to VSS                        |

| USB      | USB1_DP   | Float                                 | Float                                        |

| USB      | USB1_DM   | Float                                 | Float                                        |

| USB      | USB1_VBUS | Float                                 | Float                                        |

| VBAT     | VBAT      | Float                                 | Float                                        |

| VDDA     | VDDA      | Always connect to VDD potential       | Always connect to VDD potential              |

| VREFH    | VREFH     | Always connect to VDD potential       | Always connect to VDD potential              |

| VREFL    | VREFL     | Always connect to VSS potential       | Always connect to VSS potential              |

| VSSA     | VSSA      | Always connect to VSS potential       | Always connect to VSS potential              |

#### 5.3 K66 Pinouts

The below figure shows the pinout diagram for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

#### 8.3 Typical-value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol         | Description         | Value | Unit |

|----------------|---------------------|-------|------|

| T <sub>A</sub> | Ambient temperature | 25    | °C   |

| $V_{DD}$       | Supply voltage      | 3.3   | V    |

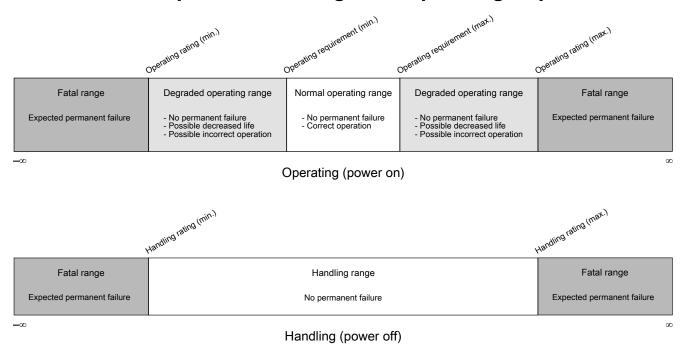

#### 8.4 Relationship between ratings and operating requirements

#### 8.5 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.