#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, Ethernet, IrDA, SD, SPI, UART/USART, USB               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 117                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                |                                                                         |

| RAM Size                   | 128K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4e8ea-au |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

All faults exceptions except for hard fault have configurable exception priority, see "System Handler Priority Registers". The software can disable the execution of the handlers for these faults, see "System Handler Control and State Register"

Usually, the exception priority, together with the values of the exception mask registers, determines whether the processor enters the fault handler, and whether a fault handler can preempt another fault handler, as described in "Exception Model".

In some situations, a fault with configurable priority is treated as a hard fault. This is called *priority escalation*, and the fault is described as *escalated to hard fault*. Escalation to hard fault occurs when:

- A fault handler causes the same kind of fault as the one it is servicing. This escalation to hard fault occurs because a fault handler cannot preempt itself; it must have the same priority as the current priority level.

- A fault handler causes a fault with the same or lower priority as the fault it is servicing. This is because the handler for the new fault cannot preempt the currently executing fault handler.

- An exception handler causes a fault for which the priority is the same as or lower than the currently executing exception.

- A fault occurs and the handler for that fault is not enabled.

If a bus fault occurs during a stack push when entering a bus fault handler, the bus fault does not escalate to a hard fault. This means that if a corrupted stack causes a fault, the fault handler executes even though the stack push for the handler failed. The fault handler operates but the stack contents are corrupted.

Note: Only Reset and NMI can preempt the fixed priority hard fault. A hard fault can preempt any exception other than Reset, NMI, or another hard fault.

### Fault Status Registers and Fault Address Registers

The fault status registers indicate the cause of a fault. For bus faults and memory management faults, the fault address register indicates the address accessed by the operation that caused the fault, as shown in Table 12-12.

| Handler                    | Status Register<br>Name | Address<br>Register Name | Register Description                                                                         |

|----------------------------|-------------------------|--------------------------|----------------------------------------------------------------------------------------------|

| Hard fault                 | SCB_HFSR                | -                        | "Hard Fault Status Register"                                                                 |

| Memory<br>management fault | MMFSR                   | SCB_MMFAR                | "MMFSR: Memory Management Fault<br>Status Subregister"<br>"MemManage Fault Address Register" |

| Bus fault                  | BFSR                    | SCB_BFAR                 | "BFSR: Bus Fault Status Subregister"<br>"Bus Fault Address Register"                         |

| Usage fault                | UFSR                    | -                        | "UFSR: Usage Fault Status<br>Subregister"                                                    |

Table 12-12. Fault Status and Fault Address Registers

### Lockup

The processor enters a lockup state if a hard fault occurs when executing the NMI or hard fault handlers. When the processor is in lockup state, it does not execute any instructions. The processor remains in lockup state until either:

- It is reset

- An NMI occurs

- It is halted by a debugger.

Note: If the lockup state occurs from the NMI handler, a subsequent NMI does not cause the processor to leave the lockup state.

#### 12.6.5.12 SHSUB16 and SHSUB8

Signed Halving Subtract 16 and Signed Halving Subtract 8

Syntax

op{cond}{Rd,} Rn, Rm

where:

| ор   | is any of:                                                 |

|------|------------------------------------------------------------|

|      | SHSUB16 Signed Halving Subtract 16.                        |

|      | SHSUB8 Signed Halving Subtract 8.                          |

| cond | is an optional condition code, see "Conditional Execution" |

| Rd   | is the destination register.                               |

| Rn   | is the first operand register.                             |

| Rm   | is the second operand register.                            |

Operation

Use these instructions to add 16-bit and 8-bit data and then to halve the result before writing the result to the destination register:

The SHSUB16 instruction:

- 1. Subtracts each halfword of the second operand from the corresponding halfwords of the first operand.

- 2. Shuffles the result by one bit to the right, halving the data.

- 3. Writes the halved halfword results in the destination register.

The SHSUBB8 instruction:

- 1. Subtracts each byte of the second operand from the corresponding byte of the first operand,

- 2. Shuffles the result by one bit to the right, halving the data,

- 3. Writes the corresponding signed byte results in the destination register.

Restrictions

Do not use SP and do not use PC.

Condition Flags

These instructions do not change the flags.

#### Examples

```

SHSUB16 R1, R0 ; Subtracts halfwords in R0 from corresponding halfword

; of R1 and writes to corresponding halfword of R1

SHSUB8 R4, R0, R5 ; Subtracts bytes of R0 from corresponding byte in R5,

; and writes to corresponding byte in R4.

```

#### 12.6.11.18 VMOV ARM Core Register to Scalar

Transfers one word to a floating-point register from an ARM core register.

| Syntax |

|--------|

|--------|

$VMOV{cond}{.32} Dd[x], Rt$

## where:

| cond  | is an optional condition code, see "Conditional Execution".                                                                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32    | is an optional data size specifier.                                                                                                                                                       |

| Dd[x] | is the destination, where $[x]$ defines which half of the doubleword is transferred, as follows:<br>If $x$ is 0, the lower half is extracted<br>If $x$ is 1, the upper half is extracted. |

| Rt    | is the source ARM core register.                                                                                                                                                          |

Operation

This instruction transfers one word to the upper or lower half of a doubleword floating-point register from an ARM core register.

Restrictions

Rt cannot be PC or SP.

**Condition Flags**

These instructions do not change the flags.

#### 12.6.11.19 VMRS

Move to ARM Core register from floating-point System Register.

Syntax

```

VMRS{cond} Rt, FPSCR

VMRS{cond} APSR_nzcv, FPSCR

```

where:

cond is an optional condition code, see "Conditional Execution" .

Rt is the destination ARM core register. This register can be R0-R14.

APSR\_nzcv Transfer floating-point flags to the APSR flags.

Operation

This instruction performs one of the following actions:

- Copies the value of the FPSCR to a general-purpose register. •

- Copies the value of the FPSCR flag bits to the APSR N, Z, C, and V flags. ٠

Restrictions

Rt cannot be PC or SP.

**Condition Flags**

These instructions optionally change the flags: N, Z, C, V

## 12.8.3 Nested Vectored Interrupt Controller (NVIC) User Interface

| Offset     | Register                            | Name       | Access     | Reset      |

|------------|-------------------------------------|------------|------------|------------|

| 0xE000E100 | Interrupt Set-enable Register 0     | NVIC_ISER0 | Read-write | 0x00000000 |

|            |                                     |            |            |            |

| 0xE000E11C | Interrupt Set-enable Register 7     | NVIC_ISER7 | Read-write | 0x00000000 |

| 0XE000E180 | Interrupt Clear-enable Register0    | NVIC_ICER0 | Read-write | 0x00000000 |

|            |                                     |            |            |            |

| 0xE000E19C | Interrupt Clear-enable Register 7   | NVIC_ICER7 | Read-write | 0x00000000 |

| 0XE000E200 | Interrupt Set-pending Register 0    | NVIC_ISPR0 | Read-write | 0x00000000 |

|            |                                     |            |            |            |

| 0xE000E21C | Interrupt Set-pending Register 7    | NVIC_ISPR7 | Read-write | 0x00000000 |

| 0XE000E280 | Interrupt Clear-pending Register 0  | NVIC_ICPR0 | Read-write | 0x00000000 |

|            |                                     |            |            |            |

| 0xE000E29C | Interrupt Clear-pending Register 7  | NVIC_ICPR7 | Read-write | 0x00000000 |

| 0xE000E300 | Interrupt Active Bit Register 0     | NVIC_IABR0 | Read-write | 0x00000000 |

|            |                                     |            |            |            |

| 0xE000E31C | Interrupt Active Bit Register 7     | NVIC_IABR7 | Read-write | 0x00000000 |

| 0xE000E400 | Interrupt Priority Register 0       | NVIC_IPR0  | Read-write | 0x00000000 |

|            |                                     |            |            |            |

| 0XE000E42C | Interrupt Priority Register 12      | NVIC_IPR12 | Read-write | 0x00000000 |

| 0xE000EF00 | Software Trigger Interrupt Register | NVIC_STIR  | Write-only | 0x00000000 |

#### Table 12-32. Nested Vectored Interrupt Controller (NVIC) Register Mapping

## 13.6.10 ID Code Register

Access: Read-only

| 31 | 30                                | 29   | 28     | 27    | 26     | 25    | 24 |

|----|-----------------------------------|------|--------|-------|--------|-------|----|

|    | VER                               | SION |        |       | PART N | UMBER |    |

| 23 | 22                                | 21   | 20     | 19    | 18     | 17    | 16 |

|    |                                   |      | PART N | UMBER |        |       |    |

| 15 | 14                                | 13   | 12     | 11    | 10     | 9     | 8  |

|    | PART NUMBER MANUFACTURER IDENTITY |      |        |       |        |       |    |

| 7  | 6                                 | 5    | 4      | 3     | 2      | 1     | 0  |

|    | MANUFACTURER IDENTITY             |      |        |       | 1      |       |    |

## • VERSION[31:28]: Product Version Number

Set to 0x0.

## • PART NUMBER[27:12]: Product Part Number

| Chip Name | Chip ID     |

|-----------|-------------|

| SAM4E     | 0xA3CC_0CE0 |

### • MANUFACTURER IDENTITY[11:1]

Set to 0x01F.

### • Bit[0] Required by IEEE Std. 1149.1.

Set to 0x1.

| Chip Name | JTAG ID Code |

|-----------|--------------|

| SAM4E     | 0x05B3_703F  |

### 18.6.7 RTC Status Register

| Name:    | RTC_SR     |       |       |       |     |       |        |

|----------|------------|-------|-------|-------|-----|-------|--------|

| Address: | 0x400E1878 |       |       |       |     |       |        |

| Access:  | Read-only  |       |       |       |     |       |        |

| 31       | 30         | 29    | 28    | 27    | 26  | 25    | 24     |

| -        | -          | _     | _     | _     | _   | _     | _      |

| 23       | 22         | 21    | 20    | 19    | 18  | 17    | 16     |

| _        | -          | -     | _     | _     | -   | -     | _      |

| 15       | 14         | 13    | 12    | 11    | 10  | 9     | 8      |

| _        | -          | _     | _     | _     | _   | _     | _      |

| 7        | 6          | 5     | 4     | 3     | 2   | 1     | 0      |

| _        | -          | TDERR | CALEV | TIMEV | SEC | ALARM | ACKUPD |

#### • ACKUPD: Acknowledge for Update

0 (FREERUN) = Time and calendar registers cannot be updated.

1 (UPDATE) = Time and calendar registers can be updated.

#### • ALARM: Alarm Flag

0 (NO\_ALARMEVENT) = No alarm matching condition occurred.

1 (ALARMEVENT) = An alarm matching condition has occurred.

#### • SEC: Second Event

0 (NO\_SECEVENT) = No second event has occurred since the last clear.

1 (SECEVENT) = At least one second event has occurred since the last clear.

## • TIMEV: Time Event

0 (NO\_TIMEVENT) = No time event has occurred since the last clear.

1 (TIMEVENT) = At least one time event has occurred since the last clear.

The time event is selected in the TIMEVSEL field in RTC\_CR (Control Register) and can be any one of the following events: minute change, hour change, noon, midnight (day change).

### • CALEV: Calendar Event

0 (NO\_CALEVENT) = No calendar event has occurred since the last clear.

1 (CALEVENT) = At least one calendar event has occurred since the last clear.

The calendar event is selected in the CALEVSEL field in RTC\_CR and can be any one of the following events: week change, month change and year change.

### • TDERR: Time and/or Date Free Running Error

0 (CORRECT) = The internal free running counters are carrying valid values since the last read of RTC\_SR.

1 (ERR\_TIMEDATE) = The internal free running counters have been corrupted (invalid date or time, non-BCD values) since the last read and/or they are still invalid.

read operations to the EEFC\_FRR register are done after the last word of the descriptor has been returned, then the EEFC\_FRR register value is 0 until the next valid command.

| Table 22-3. | Flash | Descriptor | Definition |

|-------------|-------|------------|------------|

|-------------|-------|------------|------------|

| Symbol                  | Word Index          | Description                                                                                                                                       |

|-------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| FL_ID                   | 0                   | Flash Interface Description                                                                                                                       |

| FL_SIZE                 | 1                   | Flash size in bytes                                                                                                                               |

| FL_PAGE_SIZE            | 2                   | Page size in bytes                                                                                                                                |

| FL_NB_PLANE             | 3                   | Number of planes. (only for SAM3SD8).                                                                                                             |

| FL_PLANE[0]             | 4                   | Number of bytes in the first plane.                                                                                                               |

|                         |                     |                                                                                                                                                   |

| FL_PLANE[FL_NB_PLANE-1] | 4 + FL_NB_PLANE - 1 | Number of bytes in the last plane.                                                                                                                |

| FL_NB_LOCK              | 4 + FL_NB_PLANE     | Number of lock bits. A bit is associated<br>with a lock region. A lock bit is used to<br>prevent write or erase operations in the<br>lock region. |

| FL_LOCK[0]              | 4 + FL_NB_PLANE + 1 | Number of bytes in the first lock region.                                                                                                         |

|                         |                     |                                                                                                                                                   |

#### 22.4.3.2 Write Commands

Several commands can be used to program the Flash.

Flash technology requires that an erase be done before programming. The full memory plane can be erased at the same time, or several pages can be erased at the same time (refer to Figure 22-7, "Example of Partial Page Programming", and the paragraph below the figure.). Also, a page erase can be automatically done before a page write using EWP or EWPL commands.

After programming, the page (the whole lock region) can be locked to prevent miscellaneous write or erase sequences. The lock bit can be automatically set after page programming using WPL or EWPL commands.

Data to be written are stored in an internal latch buffer. The size of the latch buffer corresponds to the page size. The latch buffer wraps around within the internal memory area address space and is repeated as many times as the number of pages within this address space.

Note: Writing of 8-bit and 16-bit data is not allowed and may lead to unpredictable data corruption.

Write operations are performed in a number of wait states equal to the number of wait states for read operations.

Data are written to the latch buffer before the programming command is written to the Flash Command Register EEFC\_FCR. The sequence is as follows:

- Write the full page, at any page address, within the internal memory area address space.

- Programming starts as soon as the page number and the programming command are written to the Flash Command Register. The FRDY bit in the Flash Programming Status Register (EEFC\_FSR) is automatically cleared.

- When programming is completed, the FRDY bit in the Flash Programming Status Register (EEFC\_FSR) rises. If an interrupt has been enabled by setting the bit FRDY in EEFC\_FMR, the corresponding interrupt line of the NVIC is activated.

Two errors can be detected in the EEFC\_FSR register after a programming sequence:

- Command Error: a bad keyword has been written in the EEFC\_FCR register.

- Lock Error: the page to be programmed belongs to a locked region. A command must be previously run to unlock the corresponding region.

- Flash Error: at the end of the programming, the WriteVerify test of the Flash memory has failed.

## • FARG: Flash Command Argument

| Erase all command    | Field is meaningless.                                                   |

|----------------------|-------------------------------------------------------------------------|

| Erase sector command | FARG must be set with a page number that is in the sector to be erased. |

|                      | FARG[1:0] defines the number of pages to be erased.                     |

|                      | The page number from which the erase will start is defined as follows:  |

|                      | FARG[1:0]=0, start page = 4*FARG[15:2]                                  |

| Frees pages command  | FARG[1:0]=1, start page = 8*FARG[15:3], FARG[2] undefined               |

| Erase pages command  | FARG[1:0]=2, start page = 16*FARG[15:4], FARG[3:2] undefined            |

|                      | FARG[1:0]=3, start page = 32*FARG[15:5], FARG[4:2] undefined            |

|                      | Note: undefined bit must be written to 0.                               |

|                      | Refer to Table 22-4 on page 367                                         |

| Programming command  | FARG defines the page number to be programmed.                          |

| Lock command         | FARG defines the page number to be locked.                              |

| GPNVM command        | FARG defines the GPNVM number.                                          |

## • FKEY: Flash Writing Protection Key

| Value | Name   | Description                                                                                                                                                                        |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x5A  | PASSWD | The 0x5A value enables the command defined by the bits of<br>the register. If the field is written with a different value, the write<br>is not performed and no action is started. |

### 23.3.5 Device Operations

Several commands on the Flash memory are available. These commands are summarized in Table 23-3 on page 380. Each command is driven by the programmer through the parallel interface running several read/write handshaking sequences.

When a new command is executed, the previous one is automatically achieved. Thus, chaining a read command after a write automatically flushes the load buffer in the Flash.

#### 23.3.5.1 Flash Read Command

This command is used to read the contents of the Flash memory. The read command can start at any valid address in the memory plane and is optimized for consecutive reads. Read handshaking can be chained; an internal address buffer is automatically increased.

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]         |

|------|--------------------|-----------|--------------------|

| 1    | Write handshaking  | CMDE      | READ               |

| 2    | Write handshaking  | ADDR0     | Memory Address LSB |

| 3    | Write handshaking  | ADDR1     | Memory Address     |

| 4    | Read handshaking   | DATA      | *Memory Address++  |

| 5    | Read handshaking   | DATA      | *Memory Address++  |

|      |                    |           |                    |

| n    | Write handshaking  | ADDR0     | Memory Address LSB |

| n+1  | Write handshaking  | ADDR1     | Memory Address     |

| n+2  | Read handshaking   | DATA      | *Memory Address++  |

| n+3  | Read handshaking   | DATA      | *Memory Address++  |

|      |                    |           |                    |

#### Table 23-6. Read Command

#### 23.3.5.2 Flash Write Command

This command is used to write the Flash contents.

The Flash memory plane is organized into several pages. Data to be written are stored in a load buffer that corresponds to a Flash memory page. The load buffer is automatically flushed to the Flash:

- Before access to any page other than the current one

- When a new command is validated (MODE = CMDE)

The **Write Page** command **(WP)** is optimized for consecutive writes. Write handshaking can be chained; an internal address buffer is automatically increased.

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]               |

|------|--------------------|-----------|--------------------------|

| 1    | Write handshaking  | CMDE      | WP or WPL or EWP or EWPL |

| 2    | Write handshaking  | ADDR0     | Memory Address LSB       |

| 3    | Write handshaking  | ADDR1     | Memory Address           |

| 4    | Write handshaking  | DATA      | *Memory Address++        |

| 5    | Write handshaking  | DATA      | *Memory Address++        |

|      |                    |           |                          |

| n    | Write handshaking  | ADDR0     | Memory Address LSB       |

Table 23-8. Write Command

## 29.5.6 Receive Next Counter Register

| Name:   | PERIPH_RNCR |    |     |     |    |    |    |

|---------|-------------|----|-----|-----|----|----|----|

| Access: | Read-write  |    |     |     |    |    |    |

| 31      | 30          | 29 | 28  | 27  | 26 | 25 | 24 |

| _       | -           | -  | -   | -   | -  | -  | -  |

| 23      | 22          | 21 | 20  | 19  | 18 | 17 | 16 |

| _       | -           | -  | -   | -   | -  | -  | -  |

| 15      | 14          | 13 | 12  | 11  | 10 | 9  | 8  |

|         |             |    | RXN | CTR |    |    |    |

| 7       | 6           | 5  | 4   | 3   | 2  | 1  | 0  |

|         |             |    | RXN | CTR |    |    |    |

#### • RXNCTR: Receive Next Counter

RXNCTR contains next receive buffer size.

When a half duplex peripheral is connected to the PDC, RXNCTR = TXNCTR.

## 31.6.10 AES Initialization Vector Register x

| Name:    | AES_IVRx   |    |     |    |    |    |    |

|----------|------------|----|-----|----|----|----|----|

| Address: | 0x40004060 |    |     |    |    |    |    |

| Access:  | Write-only |    |     |    |    |    |    |

| 31       | 30         | 29 | 28  | 27 | 26 | 25 | 24 |

|          |            |    | P   | V  |    |    |    |

| 23       | 22         | 21 | 20  | 19 | 18 | 17 | 16 |

|          |            |    | N   | V  |    |    |    |

| 15       | 14         | 13 | 12  | 11 | 10 | 9  | 8  |

|          |            |    | N   | V  |    |    |    |

| 7        | 6          | 5  | 4   | 3  | 2  | 1  | 0  |

|          |            |    | N I | V  |    |    |    |

#### • IV: Initialization Vector

The four 32-bit Initialization Vector registers set the 128-bit Initialization Vector data block that is used by some modes of operation as an additional initial input.

AES\_IVR0 corresponds to the first word of the Initialization Vector, AES\_IVR3 to the last one.

These registers are write-only to prevent the Initialization Vector from being read by another application.

For CBC, OFB and CFB modes, the Initialization Vector corresponds to the initialization vector.

For CTR mode, it corresponds to the counter value.

Note: These registers are not used in ECB mode and must not be written.

# 32.7 CAN Controller Features

#### 32.7.1 CAN Protocol Overview

The Controller Area Network (CAN) is a multi-master serial communication protocol that efficiently supports real-time control with a very high level of security with bit rates up to 1 Mbit/s.

The CAN protocol supports four different frame types:

- Data frames: They carry data from a transmitter node to the receiver nodes. The overall maximum data frame length is 108 bits for a standard frame and 128 bits for an extended frame.

- Remote frames: A destination node can request data from the source by sending a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node then sends a data frame as a response to this node request.

- Error frames: An error frame is generated by any node that detects a bus error.

- Overload frames: They provide an extra delay between the preceding and the successive data frames or remote frames.

The Atmel CAN controller provides the CPU with full functionality of the CAN protocol V2.0 Part A and V2.0 Part B. It minimizes the CPU load in communication overhead. The Data Link Layer and part of the physical layer are automatically handled by the CAN controller itself.

The CPU reads or writes data or messages via the CAN controller mailboxes. An identifier is assigned to each mailbox. The CAN controller encapsulates or decodes data messages to build or to decode bus data frames. Remote frames, error frames and overload frames are automatically handled by the CAN controller under supervision of the software application.

#### 32.7.2 Mailbox Organization

The CAN module has 8 buffers, also called channels or mailboxes. An identifier that corresponds to the CAN identifier is defined for each active mailbox. Message identifiers can match the standard frame identifier or the extended frame identifier. This identifier is defined for the first time during the CAN initialization, but can be dynamically reconfigured later so that the mailbox can handle a new message family. Several mailboxes can be configured with the same ID.

Each mailbox can be configured in receive or in transmit mode independently. The mailbox object type is defined in the MOT field of the CAN\_MMRx register.

#### 32.7.2.1 Message Acceptance Procedure

If the MIDE field in the CAN\_MIDx register is set, the mailbox can handle the extended format identifier; otherwise, the mailbox handles the standard format identifier. Once a new message is received, its ID is masked with the CAN\_MAMx value and compared with the CAN\_MIDx value. If accepted, the message ID is copied to the CAN\_MIDx register.

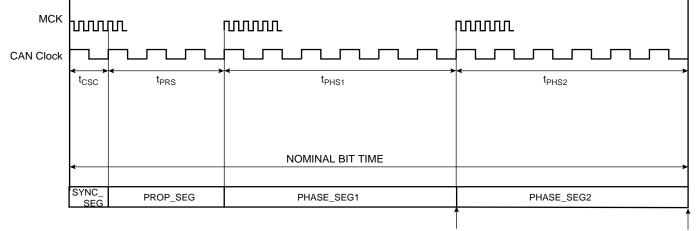

In the CAN controller, the length of a bit on the CAN bus is determined by the parameters (BRP, PROPAG, PHASE1 and PHASE2).

$$t_{BIT} = t_{CSC} + t_{PRS} + t_{PHS1} + t_{PHS2}$$

The time quantum is calculated as follows:

$$t_{CSC} = (BRP + 1) / MCK$$

Note: The BRP field must be within the range [1, 0x7F], i.e., BRP = 0 is not authorized.

$$t_{PRS} = t_{CSC} \times (PROPAG + 1)$$

$$t_{PHS1} = t_{CSC} \times (PHASE1 + 1)$$

$$t_{PHS2} = t_{CSC} \times (PHASE2 + 1)$$

To compensate for phase shifts between clock oscillators of different controllers on the bus, the CAN controller must resynchronize on any relevant signal edge of the current transmission. The resynchronization shortens or lengthens the bit time so that the position of the sample point is shifted with regard to the detected edge. The resynchronization jump width (SJW) defines the maximum of time by which a bit period may be shortened or lengthened by resynchronization.

$$t_{SJW} = t_{CSC} \times (SJW + 1)$$

Sample Point

**Transmission Point**

Example of bit timing determination for CAN baudrate of 500 Kbps:

```

MCK = 48 MHz

CAN baudrate= 500 Kbps => bit time= 2us

Delay of the bus driver: 50 ns

Delay of the receiver: 30ns

Delay of the bus line (20m): 110ns

The total number of time quanta in a bit time must be comprised between 8 and

25. If we fix the bit time to 16 time quanta:

Tcsc = 1 time quanta = bit time / 16 = 125 ns

=> BRP = (Tcsc x MCK) - 1 = 5

The propagation segment time is equal to twice the sum of the signal's

propagation time on the bus line, the receiver delay and the output driver

delay:

Tprs = 2 * (50+30+110) ns = 380 ns = 3 Tcsc

=> PROPAG = Tprs/Tcsc - 1 = 2

The remaining time for the two phase segments is:

Tphs1 + Tphs2 = bit time - Tcsc - Tprs = (16 - 1 - 3)Tcsc

```

# Atmel

## 33.7.38 PIO Additional Interrupt Modes Mask Register

| Name:    | PIO_AIMMR       |                |                 |                |               |                |           |

|----------|-----------------|----------------|-----------------|----------------|---------------|----------------|-----------|

| Address: | 0x400E0EB8 (PI0 | DA), 0x400E10E | 38 (PIOB), 0x40 | 0E12B8 (PIOC), | 0x400E14B8 (P | IOD), 0x400E16 | B8 (PIOE) |

| Access:  | Read-only       |                |                 |                |               |                |           |

| 31       | 30              | 29             | 28              | 27             | 26            | 25             | 24        |

| P31      | P30             | P29            | P28             | P27            | P26           | P25            | P24       |

| 23       | 22              | 21             | 20              | 19             | 18            | 17             | 16        |

| P23      | P22             | P21            | P20             | P19            | P18           | P17            | P16       |

| 15       | 14              | 13             | 12              | 11             | 10            | 9              | 8         |

| P15      | P14             | P13            | P12             | P11            | P10           | P9             | P8        |

| 7        | 6               | 5              | 4               | 3              | 2             | 1              | 0         |

| P7       | P6              | P5             | P4              | P3             | P2            | P1             | P0        |

|          |                 |                |                 |                |               |                |           |

## • P0-P31: Peripheral CD Status

0: The interrupt source is a Both Edge detection event.

1: The interrupt source is described by the registers PIO\_ELSR and PIO\_FRLHSR.

#### 34.8.9 SPI Chip Select Register

| Name:    | SPI_CSRx[x=03] |            |      |       |        |       |      |  |  |  |

|----------|----------------|------------|------|-------|--------|-------|------|--|--|--|

| Address: | 0x40088030     | 0x40088030 |      |       |        |       |      |  |  |  |

| Access:  | Read/Write     |            |      |       |        |       |      |  |  |  |

| 31       | 30             | 29         | 28   | 27    | 26     | 25    | 24   |  |  |  |

|          |                |            | DLYI | ВСТ   |        |       |      |  |  |  |

| 23       | 22             | 21         | 20   | 19    | 18     | 17    | 16   |  |  |  |

|          |                |            | DLY  | BS    |        |       |      |  |  |  |

| 15       | 14             | 13         | 12   | 11    | 10     | 9     | 8    |  |  |  |

|          |                |            | SCI  | BR    |        |       |      |  |  |  |

| 7        | 6              | 5          | 4    | 3     | 2      | 1     | 0    |  |  |  |

|          | BITS           |            |      | CSAAT | CSNAAT | NCPHA | CPOL |  |  |  |

This register can only be written if the WPEN bit is cleared in "SPI Write Protection Mode Register".

Note: SPI\_CSRx registers must be written even if the user wants to use the defaults. The BITS field will not be updated with the translated value unless the register is written.

#### • CPOL: Clock Polarity

0 = The inactive state value of SPCK is logic level zero.

1 = The inactive state value of SPCK is logic level one.

CPOL is used to determine the inactive state value of the serial clock (SPCK). It is used with NCPHA to produce the required clock/data relationship between master and slave devices.

#### • NCPHA: Clock Phase

0 = Data is changed on the leading edge of SPCK and captured on the following edge of SPCK.

1 = Data is captured on the leading edge of SPCK and changed on the following edge of SPCK.

NCPHA determines which edge of SPCK causes data to change and which edge causes data to be captured. NCPHA is used with CPOL to produce the required clock/data relationship between master and slave devices.

## • CSNAAT: Chip Select Not Active After Transfer (Ignored if CSAAT = 1)

0 = The Peripheral Chip Select does not rise between two transfers if the SPI\_TDR is reloaded before the end of the first transfer and if the two transfers occur on the same Chip Select.

1 = The Peripheral Chip Select rises systematically after each transfer performed on the same slave. It remains active after the end of transfer for a minimal duration of:

$- \frac{DLYBCT}{MCK}$  (if DLYBCT field is different from 0)

$- \frac{DLYBCT + 1}{MCK}$  (if DLYBCT field equals 0)

### • CSAAT: Chip Select Active After Transfer

0 = The Peripheral Chip Select Line rises as soon as the last transfer is achieved.

1 = The Peripheral Chip Select does not rise after the last transfer is achieved. It remains active until a new transfer is requested on a different chip select.

### • BITS: Bits Per Transfer

Atmel

## 37.8.2 USART Control Register (SPI\_MODE)

| Name:<br>Address: | US_CR (SPI_MODE)<br>0x400A0000 (0), 0x400A4000 (1) |       |      |           |           |    |        |  |

|-------------------|----------------------------------------------------|-------|------|-----------|-----------|----|--------|--|

| Access:           | Write-only                                         |       |      |           |           |    |        |  |

| 31                | 30                                                 | 29    | 28   | 27        | 26        | 25 | 24     |  |

| _                 | -                                                  | —     | —    | —         | —         | —  | -      |  |

| 23                | 22                                                 | 21    | 20   | 19<br>RCS | 18<br>FCS | 17 | 16     |  |

| 15                | 14                                                 | 13    | 12   | 11        | 10        | 9  | 8      |  |

| -                 | -                                                  | -     | -    | -         | -         | -  | RSTSTA |  |

| 7                 | 6                                                  | 5     | 4    | 3         | 2         | 1  | 0      |  |

| TXDIS             | TXEN                                               | RXDIS | RXEN | RSTTX     | RSTRX     | -  | -      |  |

This configuration is relevant only if USART\_MODE=0xE or 0xF in "USART Mode Register" on page 865.

#### • RSTRX: Reset Receiver

0: No effect.

1: Resets the receiver.

#### • RSTTX: Reset Transmitter

0: No effect.

1: Resets the transmitter.

#### • RXEN: Receiver Enable

0: No effect.

1: Enables the receiver, if RXDIS is 0.

#### • RXDIS: Receiver Disable

0: No effect.

1: Disables the receiver.

### • TXEN: Transmitter Enable

0: No effect.

1: Enables the transmitter if TXDIS is 0.

## • TXDIS: Transmitter Disable

0: No effect.

1: Disables the transmitter.

Atmel

## 37.8.18 USART FI DI RATIO Register

| Name:        | US_FIDI           |                |        |       |    |    |    |  |

|--------------|-------------------|----------------|--------|-------|----|----|----|--|

| Address:     | 0x400A0040 (0), ( | 0x400A4040 (1) |        |       |    |    |    |  |

| Access:      | Read-write        |                |        |       |    |    |    |  |

| Reset Value: | 0x174             |                |        |       |    |    |    |  |

| 31           | 30                | 29             | 28     | 27    | 26 | 25 | 24 |  |

| -            | -                 | _              | -      | -     | -  | _  | -  |  |

| 23           | 22                | 21             | 20     | 19    | 18 | 17 | 16 |  |

| _            | -                 | _              | _      | _     | —  | _  | -  |  |

| 15           | 14                | 13             | 12     | 11    | 10 | 9  | 8  |  |

|              |                   |                | FI_DI_ | RATIO |    |    |    |  |

| 7            | 6                 | 5              | 4      | 3     | 2  | 1  | 0  |  |

|              |                   |                | FI_DI_ | RATIO |    |    |    |  |

This register can only be written if the WPEN bit is cleared in "USART Write Protect Mode Register" on page 893.

## • FI\_DI\_RATIO: FI Over DI Ratio Value

0: If ISO7816 mode is selected, the Baud Rate Generator generates no signal.

1 - : If ISO7816 mode is selected, the Baud Rate is the clock provided on SCK divided by FI\_DI\_RATIO.

0 = Counter clock is not disabled when counter reaches RC.

1 = Counter clock is disabled when counter reaches RC.

#### • EEVTEDG: External Event Edge Selection

| Value | Name    | Description  |

|-------|---------|--------------|

| 0     | NONE    | None         |

| 1     | RISING  | Rising edge  |

| 2     | FALLING | Falling edge |

| 3     | EDGE    | Each edge    |

## • EEVT: External Event Selection

Signal selected as external event.

| Value | Name | Description         | TIOB Direction |

|-------|------|---------------------|----------------|

| 0     | TIOB | TIOB <sup>(1)</sup> | input          |

| 1     | XC0  | XC0                 | output         |

| 2     | XC1  | XC1                 | output         |

| 3     | XC2  | XC2                 | output         |

Note: 1. If TIOB is chosen as the external event signal, it is configured as an input and no longer generates waveforms and subsequently no IRQs.

#### • ENETRG: External Event Trigger Enable

0 = The external event has no effect on the counter and its clock.

1 = The external event resets the counter and starts the counter clock.

Note: Whatever the value programmed in ENETRG, the selected external event only controls the TIOA output and TIOB if not used as input (trigger event input or other input used).

#### • WAVSEL: Waveform Selection

| Value | Name      | Description                                         |

|-------|-----------|-----------------------------------------------------|

| 0     | UP        | UP mode without automatic trigger on RC Compare     |

| 1     | UPDOWN    | UPDOWN mode without automatic trigger on RC Compare |

| 2     | UP_RC     | UP mode with automatic trigger on RC Compare        |

| 3     | UPDOWN_RC | UPDOWN mode with automatic trigger on RC Compare    |

### • WAVE: Waveform Mode

0 = Waveform Mode is disabled (Capture Mode is enabled).

1 = Waveform Mode is enabled.

## 40.7.8 PWM Interrupt Status Register 1

| Name:    | PWM_ISR1   |    |    |        |        |        |        |

|----------|------------|----|----|--------|--------|--------|--------|

| Address: | 0x4000001C |    |    |        |        |        |        |

| Access:  | Read-only  |    |    |        |        |        |        |

| 31       | 30         | 29 | 28 | 27     | 26     | 25     | 24     |

| -        | -          | -  | -  | -      | _      | -      | -      |

| 23       | 22         | 21 | 20 | 19     | 18     | 17     | 16     |

| -        | -          | -  | -  | FCHID3 | FCHID2 | FCHID1 | FCHID0 |

| 15       | 14         | 13 | 12 | 11     | 10     | 9      | 8      |

| -        | -          | -  | -  | -      | -      | -      | -      |

| 7        | 6          | 5  | 4  | 3      | 2      | 1      | 0      |

| -        | -          | -  | _  | CHID3  | CHID2  | CHID1  | CHID0  |

#### • CHIDx: Counter Event on Channel x

0 = No new counter event has occurred since the last read of the PWM\_ISR1 register.

1 = At least one counter event has occurred since the last read of the PWM\_ISR1 register.

## • FCHIDx: Fault Protection Trigger on Channel x

0 = No new trigger of the fault protection since the last read of the PWM\_ISR1 register.

1 = At least one trigger of the fault protection since the last read of the PWM\_ISR1 register.

Note: Reading PWM\_ISR1 automatically clears CHIDx and FCHIDx flags.

Atmel

## 44.7.81 1588 Timer Sync Strobe Seconds Register

| Name:    | GMAC_TSSS  |    |    |    |    |    |    |  |

|----------|------------|----|----|----|----|----|----|--|

| Address: | 0x400341C8 |    |    |    |    |    |    |  |

| Access:  | Read-write |    |    |    |    |    |    |  |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24 |  |

| VTS      |            |    |    |    |    |    |    |  |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16 |  |

| VTS      |            |    |    |    |    |    |    |  |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8  |  |

| VTS      |            |    |    |    |    |    |    |  |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0  |  |

| VTS      |            |    |    |    |    |    |    |  |

#### • VTS: Value of Timer Seconds Register Capture

The value of the Timer Seconds Register is captured.

#### 44.7.82 1588 Timer Sync Strobe Nanoseconds Register

| Name:<br>Address:<br>Access: | GMAC_TSSN<br>0x400341CC<br>Read-write |     |          |          |    |    |    |  |

|------------------------------|---------------------------------------|-----|----------|----------|----|----|----|--|

| 31                           | 30                                    | 29  | 28       | 27       | 26 | 25 | 24 |  |

| -                            | -                                     | VTN |          |          |    |    |    |  |

| 23                           | 22                                    | 21  | 20<br>V1 | 19<br>「N | 18 | 17 | 16 |  |

| 15                           | 14                                    | 13  | 12<br>VT | 11<br>「N | 10 | 9  | 8  |  |

| 7                            | 6                                     | 5   | 4<br>V1  | 3<br>TN  | 2  | 1  | 0  |  |

## VTN: Value Timer Nanoseconds Register Capture

The value of the Timer Nanoseconds Register is captured.