Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                   |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 13                                                                              |

| Program Memory Size        | 6KB (6K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 18-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs101-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

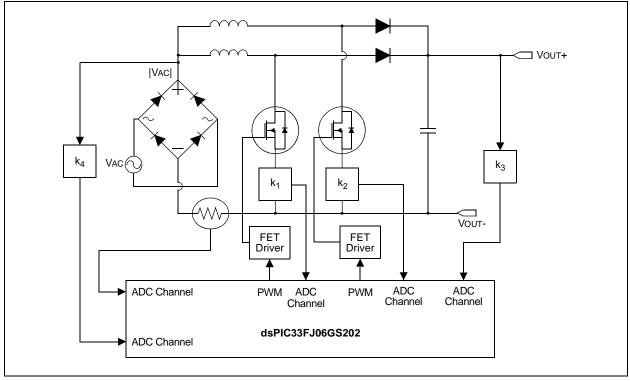

#### FIGURE 2-9: INTERLEAVED PFC

### 3.3 Special MCU Features

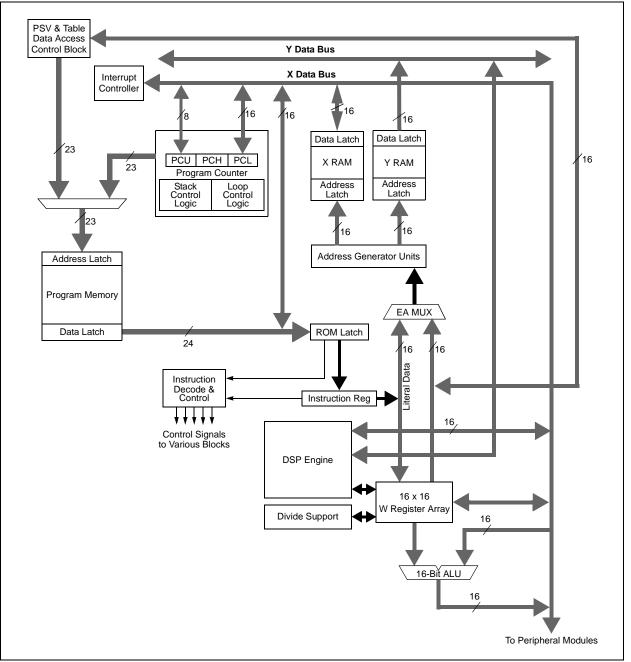

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices feature a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (1.0).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices support 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

FIGURE 3-1: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 CPU CORE BLOCK DIAGRAM

### 4.2 Data Address Space

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 CPU has a separate, 16-bit-wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices implement up to 2 Kbytes of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] that results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

| Note: | The actual set of peripheral features and interrupts varies by the device. Refer to |

|-------|-------------------------------------------------------------------------------------|

|       | the corresponding device tables and                                                 |

|       | pinout diagrams for device-specific                                                 |

|       | information.                                                                        |

#### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field or by using Indirect Addressing mode using a Working register as an Address Pointer.

#### TABLE 4-11: TIMER REGISTER MAP FOR dsPIC33FJ06GS101 AND dsPIC33FJ06GSX02

| File<br>Name | SFR<br>Addr | Bit 15            | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7   | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|-------------------|-------------------|--------|--------|--------|--------|-------|-----------|---------|-------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 0100        |                   |                   |        |        |        |        |       | Timer1 Re | egister |       |        |        |       |       |       |       | 0000          |

| PR1          | 0102        | Period Register 1 |                   |        |        |        |        |       |           |         |       |        | FFFF   |       |       |       |       |               |

| T1CON        | 0104        | TON               | —                 | TSIDL  | —      | _      | —      | _     | _         | _       | TGATE | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2         | 0106        |                   |                   |        |        |        |        |       | Timer2 Re | egister |       |        |        |       |       |       |       | 0000          |

| PR2          | 010C        |                   | Period Register 2 |        |        |        |        |       |           |         |       |        |        | FFFF  |       |       |       |               |

| T2CON        | 0110        | TON               | _                 | TSIDL  | _      | —      | _      | _     | —         | _       | TGATE | TCKPS1 | TCKPS0 | _     | _     | TCS   | —     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: TIMER REGISTER MAP FOR dsPIC33FJ16GSX02 AND dsPIC33FJ16GSX04

| File<br>Name | SFR<br>Addr | Bit 15            | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8         | Bit 7         | Bit 6       | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|-------------------|--------|--------|--------|--------|--------|------------|---------------|---------------|-------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 0100        |                   |        |        |        |        |        |            | Timer1 Re     | egister       |             |        |        |       |       |       |       | 0000          |

| PR1          | 0102        | Period Register 1 |        |        |        |        |        |            |               |               |             |        |        | FFFF  |       |       |       |               |

| T1CON        | 0104        | TON               | _      | TSIDL  | _      | -      | _      | _          | _             | -             | TGATE       | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2         | 0106        | Timer2 Register   |        |        |        |        |        |            |               |               |             |        |        | 0000  |       |       |       |               |

| TMR3HLD      | 0108        |                   |        |        |        |        | Timer3 | Holding Re | gister (for 3 | 2-bit timer o | perations o | nly)   |        |       |       |       |       | xxxx          |

| TMR3         | 010A        |                   |        |        |        |        |        |            | Timer3 Re     | egister       |             |        |        |       |       |       |       | 0000          |

| PR2          | 010C        |                   |        |        |        |        |        |            | Period Reg    | gister 2      |             |        |        |       |       |       |       | FFFF          |

| PR3          | 010E        |                   |        |        |        |        |        |            | Period Reg    | gister 3      |             |        |        |       |       |       |       | FFFF          |

| T2CON        | 0110        | TON               |        | TSIDL  | _      | _      | _      |            | —             | _             | TGATE       | TCKPS1 | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON        | 0112        | TON               | _      | TSIDL  | _      | _      | _      |            | _             | _             | TGATE       | TCKPS1 | TCKPS0 |       | -     | TCS   | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: INPUT CAPTURE REGISTER MAP FOR dsPIC33FJ06GS202

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| IC1BUF       | 0140        |        | Input Capture 1 Register |        |        |        |        |       |       |       |       |       |       |       | xxxx  |       |       |               |

| IC1CON       | 0142        | _      | _                        | ICSIDL | _      |        | _      | _     |       | ICTMR | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

The address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

#### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

## 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM bits (W register selection) in the MODCON register are any value other than 15 (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed         |

|-------|--------------------------------------------|

|       | Addressing should not be enabled           |

|       | together. If an application attempts to do |

|       | so, Bit-Reversed Addressing will assume    |

|       | priority when active for the X WAGU and X  |

|       | WAGU; Modulo Addressing will be dis-       |

|       | abled. However, Modulo Addressing will     |

|       | continue to function in the X RAGU.        |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

| R/W-0           | R/W-0        | U-0                                | U-0            | U-0               | U-0             | R/W-0           | R/W-0  |

|-----------------|--------------|------------------------------------|----------------|-------------------|-----------------|-----------------|--------|

| ADCP1IE         | ADCP0IE      | —                                  | —              | —                 | _               | AC4IE           | AC3IE  |

| bit 15          |              |                                    |                |                   |                 |                 | bit    |

| R/W-0           | U-0          | U-0                                | U-0            | U-0               | U-0             | R/W-0           | R/W-0  |

| AC2IE           |              | _                                  | _              |                   | _               | PWM4IE          | PWM3IE |

| bit 7           |              |                                    |                |                   |                 |                 | bit (  |

| Legend:         |              |                                    |                |                   |                 |                 |        |

| R = Readable    | bit          | W = Writable                       | bit            | U = Unimplem      | nented bit. rea | d as '0'        |        |

| -n = Value at F | POR          | '1' = Bit is set                   |                | '0' = Bit is clea |                 | x = Bit is unkr | iown   |

|                 |              |                                    |                |                   |                 |                 |        |

| bit 15          | ADCP1IE: AD  | DC Pair 1 Conv                     | ersion Done    | Interrupt Enable  | e bit           |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

|                 |              | request is not e                   |                |                   |                 |                 |        |

| bit 14          |              |                                    |                | Interrupt Enable  | bit             |                 |        |

|                 | •            | equest is enab<br>equest is not e  |                |                   |                 |                 |        |

| bit 13-10       | •            | ted: Read as '                     |                |                   |                 |                 |        |

| bit 9           | -            | g Comparator                       |                | able bit          |                 |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

|                 |              | equest is not e                    |                |                   |                 |                 |        |

| bit 8           | AC3IE: Analo | g Comparator                       | 3 Interrupt Er | nable bit         |                 |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

|                 |              | equest is not e                    |                |                   |                 |                 |        |

| bit 7           |              | g Comparator<br>equest is enat     | •              | hable bit         |                 |                 |        |

|                 |              | equest is enaction equest is not e |                |                   |                 |                 |        |

| bit 6-2         | •            | ted: Read as '                     |                |                   |                 |                 |        |

| bit 1           | -            | /M4 Interrupt E                    |                |                   |                 |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

|                 | •            | equest is not e                    |                |                   |                 |                 |        |

| bit 0           | PWM3IE: PW   | /M3 Interrupt E                    | nable bit      |                   |                 |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

#### REGISTER 7-17: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

| U-0          | U-0          | U-0                 | U-0             | U-0              | U-0              | U-0             | U-0     |

|--------------|--------------|---------------------|-----------------|------------------|------------------|-----------------|---------|

| _            |              |                     |                 | —                |                  |                 | _       |

| bit 15       |              |                     |                 |                  |                  |                 | bit     |

|              |              |                     |                 |                  |                  |                 |         |

| U-0          | R/W-1        | R/W-0               | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0   |

| —            | ADIP2        | ADIP1               | ADIP0           | —                | U1TXIP2          | U1TXIP1         | U1TXIP0 |

| bit 7        |              |                     |                 |                  |                  |                 | bit (   |

| Legend:      |              |                     |                 |                  |                  |                 |         |

| R = Readat   | ole bit      | W = Writable        | bit             | U = Unimple      | mented bit, read | l as '0'        |         |

| -n = Value a | at POR       | '1' = Bit is set    |                 | '0' = Bit is cl  | eared            | x = Bit is unkı | nown    |

|              |              |                     |                 |                  |                  |                 |         |

| bit 15-7     | Unimpleme    | ented: Read as '    | 0'              |                  |                  |                 |         |

| bit 6-4      | ADIP<2:0>    | ADC1 Convers        | ion Complete    | Interrupt Prior  | ity bits         |                 |         |

|              | 111 = Interr | upt is Priority 7 ( | (highest priori | ty interrupt)    |                  |                 |         |

|              | •            |                     |                 |                  |                  |                 |         |

|              | •            |                     |                 |                  |                  |                 |         |

|              | 001 = Interr | upt is Priority 1   |                 |                  |                  |                 |         |

|              | 000 = Interr | upt source is dis   | abled           |                  |                  |                 |         |

| bit 3        | Unimpleme    | ented: Read as '    | 0'              |                  |                  |                 |         |

| bit 2-0      | U1TXIP<2:    | D>: UART1 Tran      | smitter Interru | pt Priority bits |                  |                 |         |

|              | 111 = Interr | upt is Priority 7 ( | (highest priori | ty interrupt)    |                  |                 |         |

|              | •            |                     |                 |                  |                  |                 |         |

|              | •            |                     |                 |                  |                  |                 |         |

|              | 001 = Interr | upt is Priority 1   |                 |                  |                  |                 |         |

|              |              |                     |                 |                  |                  |                 |         |

#### REGISTER 7-22: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| REGISTER 7-26: IPC14: INTERRUPT PRIORITY CONTROL REGISTER | 14 |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | PSEMIP2 | PSEMIP1 | PSEMIP0 | —   | —   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

|            | l   | - |  |

|------------|-----|---|--|

| <b>e</b> 0 | ena |   |  |

|            |     |   |  |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15-7<br>bit 6-4 | <b>Unimplemented:</b> Read as '0'<br><b>PSEMIP&lt;2:0&gt;:</b> PWM Special Event Match Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |  |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                     | •<br>•<br>001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                                                                |  |  |  |  |  |

Unimplemented: Read as '0' bit 3-0

### REGISTER 7-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0             | U-0                                                                       | U-0    | U-0    | U-0  | U-0 | U-0 | U-0   |

|-----------------|---------------------------------------------------------------------------|--------|--------|------|-----|-----|-------|

| —               | —                                                                         | —      | _      | —    | —   | —   | —     |

| bit 15          |                                                                           |        |        |      | •   |     | bit 8 |

|                 |                                                                           |        |        |      |     |     |       |

| U-0             | R/W-1                                                                     | R/W-0  | R/W-0  | U-0  | U-0 | U-0 | U-0   |

| —               | U1EIP2                                                                    | U1EIP1 | U1EIP0 | —    | —   | —   | —     |

| bit 7           |                                                                           |        |        |      |     |     | bit 0 |

|                 |                                                                           |        |        |      |     |     |       |

| Legend:         |                                                                           |        |        |      |     |     |       |

| R = Readable    | eadable bit W = Writable bit U = Unimplemented bit, read as '0'           |        |        |      |     |     |       |

| -n = Value at F | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |        |        | nown |     |     |       |

| bit 15-7 | Unimplemented: Read as '0' |  |

|----------|----------------------------|--|

| bit 6-4 | <b>U1EIP&lt;2:0&gt;:</b> UART1 Error Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |

|---------|----------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                          |

|         | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                        |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                 |

| 11.0                | 11.0                                                                                                                            | 11.0                                                                    | 11.0                           |                   |                  |                 | DAVO   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------|-------------------|------------------|-----------------|--------|

| U-0                 | U-0                                                                                                                             | U-0                                                                     | U-0                            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| —                   | —                                                                                                                               | —                                                                       |                                | PWM4MD            | PWM3MD           | PWM2MD          | PWM1MD |

| bit 15              |                                                                                                                                 |                                                                         |                                |                   |                  |                 | bit 8  |

| U-0                 | U-0                                                                                                                             | U-0                                                                     | U-0                            | U-0               | U-0              | U-0             | U-0    |

| _                   | _                                                                                                                               | _                                                                       | _                              | _                 | _                | _               | _      |

| bit 7               |                                                                                                                                 |                                                                         |                                |                   |                  |                 | bit C  |

| Legend:             |                                                                                                                                 |                                                                         |                                |                   |                  |                 |        |

| R = Readable        | e bit                                                                                                                           | W = Writable b                                                          | oit                            | U = Unimplem      | nented bit, read | 1 as '0'        |        |

| -n = Value at       | POR                                                                                                                             | '1' = Bit is set                                                        |                                | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| bit 15-12<br>bit 11 | <b>PWM4MD</b> : P<br>1 = PWM Gei                                                                                                | ted: Read as '0<br>WM Generator 4<br>nerator 4 modul<br>nerator 4 modul | 4 Module Disa<br>e is disabled | ble bit           |                  |                 |        |

| bit 10              | 1 = PWM Gei                                                                                                                     | WM Generator 3<br>nerator 3 modul<br>nerator 3 modul                    | e is disabled                  | ıble bit          |                  |                 |        |

| bit 9               | 1 = PWM Gei                                                                                                                     | WM Generator 2<br>nerator 2 modul<br>nerator 2 modul                    | e is disabled                  | able bit          |                  |                 |        |

|                     | <b>PWM1MD</b> : PWM Generator 1 Module Disable bit 1 = PWM Generator 1 module is disabled 0 = PWM Generator 1 module is enabled |                                                                         |                                |                   |                  |                 |        |

| bit 8               | 1 = PWM Ger                                                                                                                     | nerator 1 modul                                                         | e is disabled                  |                   |                  |                 |        |

#### REGISTER 9-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

| U-0                | U-0                                                                                                                                                          | R/W-1                                                                                                                                                                                                                  | R/W-1                                              | R/W-1             | R/W-1            | R/W-1           | R/W-1  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|------------------|-----------------|--------|--|--|--|

| _                  |                                                                                                                                                              | T3CKR5                                                                                                                                                                                                                 | T3CKR4                                             | T3CKR3            | T3CKR2           | T3CKR1          | T3CKR0 |  |  |  |

| bit 15             |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 | bit    |  |  |  |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |  |  |  |

| U-0                | U-0                                                                                                                                                          | R/W-1                                                                                                                                                                                                                  | R/W-1                                              | R/W-1             | R/W-1            | R/W-1           | R/W-1  |  |  |  |

|                    |                                                                                                                                                              | T2CKR5                                                                                                                                                                                                                 | T2CKR4                                             | T2CKR3            | T2CKR2           | T2CKR1          | T2CKR0 |  |  |  |

| bit 7              |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 | bit    |  |  |  |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |  |  |  |

| Legend:            | la h:t                                                                                                                                                       |                                                                                                                                                                                                                        | L:4                                                |                   | antad hit waar   | L == (0)        |        |  |  |  |

| R = Readab         |                                                                                                                                                              | W = Writable                                                                                                                                                                                                           |                                                    | •                 | nented bit, read |                 |        |  |  |  |

| -n = Value a       | t POR                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                                                       |                                                    | '0' = Bit is clea | ared             | x = Bit is unkr | IOWN   |  |  |  |

| bit 15-14          | Unimploment                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                         | o'                                                 |                   |                  |                 |        |  |  |  |

|                    | -                                                                                                                                                            |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |  |  |  |

| bit 13-8           | T3CKR<5:0>: Assign Timer3 External Clock (T3CK) to the Corresponding RPn Pin bits                                                                            |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |  |  |  |

|                    | 111111 = Input tied to Vss                                                                                                                                   |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |  |  |  |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                        | _                                                  |                   |                  |                 |        |  |  |  |

|                    | 100011 <b>= Inp</b>                                                                                                                                          | ut tied to RP35                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp                                                                                                                                 | out tied to RP35<br>out tied to RP34                                                                                                                                                                                   | 1                                                  |                   |                  |                 |        |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                               | 1<br>3                                             |                   |                  |                 |        |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34                                                                                                                                                                                   | 1<br>3                                             |                   |                  |                 |        |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                               | 1<br>3                                             |                   |                  |                 |        |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                               | 1<br>3                                             |                   |                  |                 |        |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                 | ut tied to RP34<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                                               | 1<br>3                                             |                   |                  |                 |        |  |  |  |

| hit 7-6            | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                 | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32                                                                                                                             | 4<br>3<br>2                                        |                   |                  |                 |        |  |  |  |

| bit 7-6            | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>000000 = Inpu<br>Unimplemen                                                                   | ut tied to RP35<br>out tied to RP34<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '                                                                                                  | 4<br>3<br>2<br>0'                                  | ole (T2CK) to th  | oo Corroopondi   | ng PDn Din hit  |        |  |  |  |

| bit 7-6<br>bit 5-0 | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | ut tied to RP35<br>out tied to RP33<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer?                                                                               | 4<br>3<br>2<br>0'                                  | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP32<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer:<br>out tied to Vss                                                             | 1<br>3<br>2<br>0'<br>2 External Clo                | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 5      |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP32<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer<br>out tied to Vss<br>out tied to RP35                                          | 1<br>3<br>2<br>0'<br>2 External Clo                | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP34<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>out tied to RP35<br>out tied to RP34                                                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1      | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>out tied to RP34<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>out tied to RP35<br>out tied to RP34                                                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ie Correspondi   | ng RPn Pin bits | 5      |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |  |  |  |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>tut tied to RP32<br>tut tied to RP33<br>tut tied to RP33<br>tut tied to RP34<br>t tied to RP0<br><b>ted:</b> Read as '<br>t tied to RP35<br>tut tied to RP34<br>tut tied to RP32<br>tut tied to RP32 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |  |  |  |

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

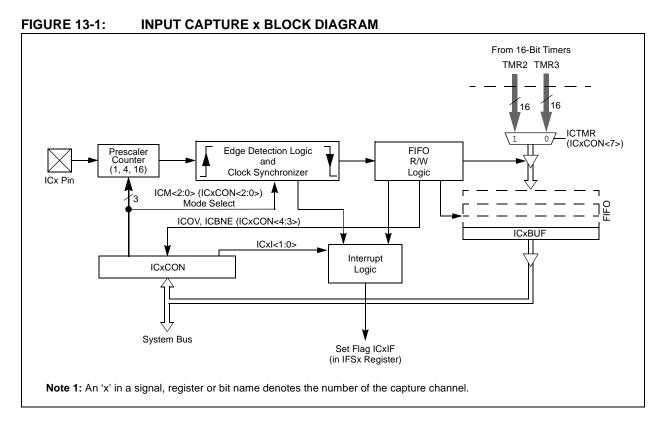

### 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70198) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices support up to two input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select one of the two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Use of input capture to provide additional sources of external interrupts

© 2008-2014 Microchip Technology Inc.

| R-0               | R-0                      | R-0                       | R-0                  | R-0                                | R-0                | R-0 | R-0   |

|-------------------|--------------------------|---------------------------|----------------------|------------------------------------|--------------------|-----|-------|

|                   |                          |                           | PWMCA                | \P<15:8> <sup>(1,2)</sup>          |                    |     |       |

| bit 15            |                          |                           |                      |                                    |                    |     | bit 8 |

| R-0               | R-0                      | R-0                       | R-0                  | R-0                                | U-0                | U-0 | U-0   |

|                   | P١                       | VMCAP<7:3> <sup>(1,</sup> | 2)                   |                                    |                    | _   |       |

| bit 7             |                          |                           |                      |                                    |                    | ·   | bit C |

| Legend:           |                          |                           |                      |                                    |                    |     |       |

| R = Readable bit  | ble bit W = Writable bit |                           |                      | U = Unimplemented bit, read as '0' |                    |     |       |

| -n = Value at POR | OR '1' = Bit is set      |                           | '0' = Bit is cleared |                                    | x = Bit is unknown |     |       |

#### REGISTER 15-19: PWMCAPx: PRIMARY PWMx TIME BASE CAPTURE REGISTER

bit 15-3 **PWMCAP<15:3>:** Captured PWM Time Base Value bits<sup>(1,2)</sup> The value in this register represents the captured PWM time base value when a leading edge is detected on the current-limit input.

bit 2-0 Unimplemented: Read as '0'

**Note 1:** The capture feature is only available on the primary output (PWMxH).

2: This feature is active only after LEB processing on the current-limit input signal is complete.

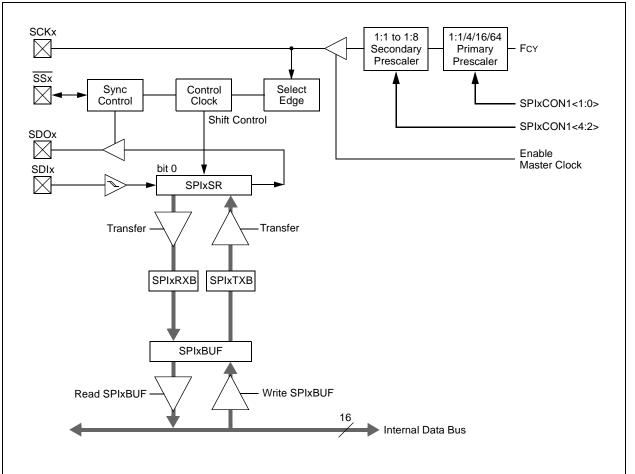

### 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70206) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters and so on. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

The SPI module consists of a 16-bit shift register, SPIxSR (where x = 1), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of the following four pins:

- SDIx (Serial Data Input)

- SDOx (Serial Data Output)

- SCKx (Shift Clock Input Or Output)

- SSx (Active-Low Slave Select).

In Master mode operation, SCK is a clock output; in Slave mode, it is a clock input.

#### FIGURE 16-1: SPIX MODULE BLOCK DIAGRAM

### 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CxSTAT are read/write:

- I2CxRSR is the shift register used for shifting data internal to the module and the user application has no access to it

- I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- The I2CxADD register holds the slave address

- A status bit, ADD10, indicates 10-Bit Addressing mode

- The I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV, and an interrupt pulse is generated.

| R-0, HSC     | R-0, HSC                     | U-0                            | U-0             | U-0                          | R/C-0, HSC         | R-0, HSC                              | R-0, HSC        |

|--------------|------------------------------|--------------------------------|-----------------|------------------------------|--------------------|---------------------------------------|-----------------|

| ACKSTAT      | TRSTAT                       | _                              |                 | —                            | BCL                | GCSTAT                                | ADD10           |

| bit 15       |                              |                                |                 |                              |                    |                                       | bit 8           |

|              |                              |                                |                 |                              |                    |                                       |                 |

| R/C-0, HS    | R/C-0, HS                    | R-0, HSC                       | R/C-0, HSC      | R/C-0, HSC                   | R-0, HSC           | R-0, HSC                              | R-0, HSC        |

| IWCOL        | I2COV                        | D_A                            | Р               | S                            | R_W                | RBF                                   | TBF             |

| bit 7        |                              |                                |                 |                              |                    |                                       | bit 0           |

|              |                              |                                |                 |                              |                    |                                       |                 |

| Legend:      |                              | C = Clearab                    | ole bit         | HSC = Hardw                  | vare Settable/C    | learable bit                          |                 |

| R = Readab   | le bit                       | W = Writabl                    | e bit           | U = Unimpler                 | nented bit, read   | l as '0'                              |                 |

| -n = Value a | It POR                       | '1' = Bit is s                 | et              | '0' = Bit is cle             | ared               | x = Bit is unknown                    | n               |

| HS = Hardw   | are Settable                 | bit                            |                 |                              |                    |                                       |                 |

| bit 15       | ACKSTAT:                     | Acknowledge                    | e Status bit    |                              |                    |                                       |                 |

|              |                              |                                |                 | licable to mas               | ter transmit ope   | eration)                              |                 |

|              |                              | eceived from                   |                 |                              |                    |                                       |                 |

|              |                              | ceived from s                  |                 | ve Acknowledg                | ie                 |                                       |                 |

| bit 14       |                              |                                |                 |                              |                    | able to master tran                   | smit operation) |

|              |                              |                                | progress (8 k   | -                            |                    |                                       | onne oporation) |

|              |                              |                                | ot in progress  | ,                            |                    |                                       |                 |

|              | Hardware is                  | s set at begin                 | ning of maste   | er transmissior              | . Hardware is c    | lear at end of slave                  | e Acknowledge.  |

| bit 13-11    | Unimpleme                    | ented: Read                    | <b>as</b> '0'   |                              |                    |                                       |                 |

| bit 10       |                              | er Bus Collisio                |                 |                              |                    |                                       |                 |

|              |                              |                                | een detected    | l during a mas               | ter operation      |                                       |                 |

|              | 0 = No collis<br>Hardware is |                                | tion of bus co  | Ilision                      |                    |                                       |                 |

| bit 9        |                              | eneral Call S                  |                 |                              |                    |                                       |                 |

| Sit 0        |                              |                                | was receive     | d                            |                    |                                       |                 |

|              |                              |                                | was not rece    |                              |                    |                                       |                 |

|              | Hardware is                  | s set when ac                  | dress match     | es general call              | address. Hard      | ware is clear at Sto                  | p detection.    |

| bit 8        |                              | -Bit Address                   |                 |                              |                    |                                       |                 |

|              |                              | ddress was n                   |                 |                              |                    |                                       |                 |

|              |                              | ddress was r<br>s set at match |                 | of matched 10                | -bit address Ha    | ardware is clear at                   | Stop detection  |

| bit 7        |                              |                                | sion Detect b   |                              |                    |                                       |                 |

|              |                              |                                |                 |                              | d because the      | I <sup>2</sup> C module is busy       | ,               |

|              | 0 = No collis                |                                |                 | - 9                          |                    | · · · · · · · · · · · · · · · · · · · |                 |

|              | Hardware is                  | s set at occur                 | rence of write  | e to I2CxTRN                 | while busy (clea   | red by software).                     |                 |

| bit 6        |                              |                                | /erflow Flag b  |                              |                    |                                       |                 |

|              | -                            |                                | while the I2C   | xRCV register                | is still holding t | the previous byte                     |                 |

|              | 0 = No over<br>Hardware is   |                                | nt to transfer  | 12CxRSR to 12                | CxRCV (cleare      | ed by software).                      |                 |

| bit 5        |                              |                                | •               | ng as I <sup>2</sup> C slave |                    | a by converg.                         |                 |

|              | _                            | · ·                            | st byte receive | 0                            | ~/                 |                                       |                 |

|              | 0 = Indicate                 | s that the las                 | t byte receive  | ed was a devid               |                    |                                       |                 |

|              | Hardware is                  | s clear at dev                 | ice address n   | natch. Hardwa                | re is set by rece  | eption of slave byte                  | <b>)</b> .      |

|              |                              |                                |                 |                              |                    |                                       |                 |

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Stop bit has been detected last                                                                                                                                                                                               |

|       | 0 = Stop bit was not detected last                                                                                                                                                                                                                 |

|       | Hardware is set or clear when Start, Repeated Start or Stop is detected.                                                                                                                                                                           |

| bit 3 | S: Start bit                                                                                                                                                                                                                                       |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                                         |

|       | Hardware is set or clear when Start, Repeated Start or Stop is detected.                                                                                                                                                                           |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                  |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware is set or clear after reception of an I<sup>2</sup>C device address byte.</li> </ul>             |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> <li>Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads</li> <li>I2CxRCV.</li> </ul> |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                               |

|       | 1 = Transmit is in progress, I2CxTRN is full                                                                                                                                                                                                       |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                                                                                                                                                                         |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of data transmission.                                                                                                                                             |

NOTES:

#### REGISTER 19-7: ADCPC2: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 2<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0  | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|--------|-------|--------|----------|----------|----------|----------|----------|

| IRQEN5 | PEND5 | SWTRG5 | TRGSRC54 | TRGSRC53 | TRGSRC52 | TRGSRC51 | TRGSRC50 |

| bit 15 |       |        |          |          |          |          | bit 8    |

| R/W-0  | R/W-0 | R/W-0  | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|--------|-------|--------|----------|----------|----------|----------|----------|

| IRQEN4 | PEND4 | SWTRG4 | TRGSRC44 | TRGSRC43 | TRGSRC42 | TRGSRC41 | TRGSRC40 |

| bit 7  |       |        |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

| bit 15  | IRQEN5: Interrupt Request Enable 5 bit                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables IRQ generation when requested conversion of Channels AN11 and AN10 is completed</li> <li>0 = IRQ is not generated</li> </ul>  |

| bit 14  | PEND5: Pending Conversion Status 5 bit                                                                                                             |

|         | <ul> <li>1 = Conversion of Channels AN11 and AN10 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul> |

| bit 13  | SWTRG5: Software Trigger 5 bit                                                                                                                     |

|         | 1 = Starts conversion of AN11 and AN10 (if selected by the TRGSRCx bits) <sup>(2)</sup>                                                            |