Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 6KB (6K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the ADPCFG register.

The bits in the registers that correspond to the A/D pins that are initialized by MPLAB ICD 2, ICD 3, or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the ADPCFG register during initialization of the ADC module.

When MPLAB ICD 2, ICD 3, or REAL ICE is used as a programmer, the user application firmware must correctly configure the ADPCFG register. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins and drive the output to logic low.

## 2.10 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-4 through Figure 2-11.

## 3.3 Special MCU Features

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices feature a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (1.0).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices support 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

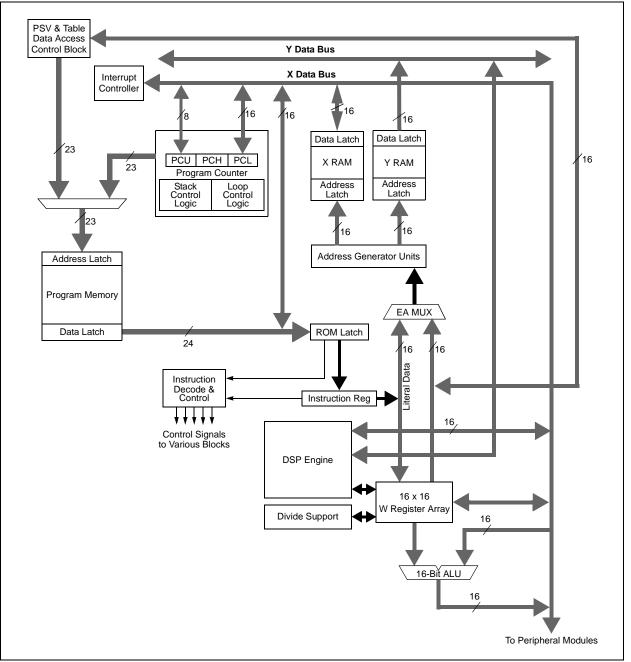

FIGURE 3-1: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 CPU CORE BLOCK DIAGRAM

### TABLE 4-22: I2C1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                 | Bit 7 | Bit 6 | Bit 5     | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|---------|--------|---------|--------|--------|--------|--------|-----------------------|-------|-------|-----------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200        | —       | _      |         | _      | _      | —      | —      | _                     |       |       |           | 2C1 Receiv  | e Register   |       |       |       | 0000          |

| I2C1TRN      | 0202        | _       |        | _       | _      |        | _      | _      |                       |       |       | I         | 2C1 Transn  | nit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204        | _       |        | _       | _      |        | _      | _      |                       |       |       | Baud Rate | e Generator | Register     |       |       |       | 0000          |

| I2C1CON      | 0206        | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                  | GCEN  | STREN | ACKDT     | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208        | ACKSTAT | TRSTAT | _       | _      |        | BCL    | GCSTAT | ADD10                 | IWCOL | I2COV | D_A       | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A        | _       | _      | _       |        | _      | —      |        | I2C1 Address Register |       |       |           |             |              | 0000  |       |       |               |

| I2C1MSK      | 020C        | —       | _      |         | _      | _      | _      |        |                       |       |       | AMSK      | <9:0>       |              |       |       |       | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-23: UART1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7        | Bit 6    | Bit 5 | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|----------|--------|----------|--------|--------|--------|-------|------------------------|--------------|----------|-------|-------------|---------|--------|--------|-------|---------------|

| U1MODE       | 0220        | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                   | WAKE         | LPBACK   | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1     | URXISEL0 | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224        | _        | _      | _        | _      | _      | —      | _     |                        |              |          | UART1 | Transmit Re | egister |        |        |       | xxxx          |

| U1RXREG      | 0226        | _        | _      | _        | _      | _      | —      | _     | UART1 Receive Register |              |          |       |             |         |        | 0000   |       |               |

| U1BRG        | 0228        |          |        |          |        |        |        | E     | Baud Rate C            | Generator Pr | escaler  |       |             |         |        |        |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-24: SPI1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7       | Bit 6      | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|--------|--------|---------|--------|--------|--------|-----------|-------------|-------------|------------|-------|-------|-------|-------|--------|--------|---------------|

| SPI1STAT     | 0240        | SPIEN  |        | SPISIDL | —      |        | _      |           | _           | _           | SPIROV     | _     | _     |       |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242        | —      | _      | _       | DISSCK | DISSDO | MODE16 | SMP       | CKE         | SSEN        | CKP        | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244        | FRMEN  | SPIFSD | FRMPOL  | —      | _      | _      | _         | _           | _           | _          | _     | _     | _     | _     | FRMDLY | —      | 0000          |

| SPI1BUF      | 0248        |        |        |         |        |        |        | SPI1 Tran | smit and Re | ceive Buffe | r Register |       |       |       |       |        |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2 STKERR: Stack Error Trap Status bit

- 1 = Stack error trap has occurred

- 0 = Stack error trap has not occurred

- bit 1 OSCFAIL: Oscillator Failure Trap Status bit

- 1 = Oscillator failure trap has occurred

- 0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

| 11.0                | 11.0                             | 11.0                                                                    | 11.0                           |                   |                  |                 | DAVO   |

|---------------------|----------------------------------|-------------------------------------------------------------------------|--------------------------------|-------------------|------------------|-----------------|--------|

| U-0                 | U-0                              | U-0                                                                     | U-0                            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| —                   | —                                | —                                                                       |                                | PWM4MD            | PWM3MD           | PWM2MD          | PWM1MD |

| bit 15              |                                  |                                                                         |                                |                   |                  |                 | bit 8  |

| U-0                 | U-0                              | U-0                                                                     | U-0                            | U-0               | U-0              | U-0             | U-0    |

| _                   | _                                | _                                                                       | _                              | _                 | _                | _               | _      |

| bit 7               |                                  |                                                                         |                                |                   |                  |                 | bit C  |

| Legend:             |                                  |                                                                         |                                |                   |                  |                 |        |

| R = Readable        | e bit                            | W = Writable b                                                          | oit                            | U = Unimplem      | nented bit, read | 1 as '0'        |        |

| -n = Value at       | POR                              | '1' = Bit is set                                                        |                                | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| bit 15-12<br>bit 11 | <b>PWM4MD</b> : P<br>1 = PWM Gei | ted: Read as '0<br>WM Generator 4<br>nerator 4 modul<br>nerator 4 modul | 4 Module Disa<br>e is disabled | able bit          |                  |                 |        |

| bit 10              | 1 = PWM Gei                      | WM Generator 3<br>nerator 3 modul<br>nerator 3 modul                    | e is disabled                  | ıble bit          |                  |                 |        |

| bit 9               | 1 = PWM Gei                      | WM Generator 2<br>nerator 2 modul<br>nerator 2 modul                    | e is disabled                  | able bit          |                  |                 |        |

|                     |                                  |                                                                         | 1 Module Disa                  | bla bit           |                  |                 |        |

| bit 8               | 1 = PWM Ger                      | nerator 1 modul<br>nerator 1 modul                                      | e is disabled                  |                   |                  |                 |        |

### REGISTER 9-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

| U-0          | U-0           | U-0                              | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0    |

|--------------|---------------|----------------------------------|-----------------|-------------------|-----------------|-----------------|----------|

|              | —             | —                                |                 | CMP4MD            | CMP3MD          | CMP2MD          | CMP1MD   |

| bit 15       |               |                                  |                 |                   |                 |                 | bit      |

| U-0          | U-0           | U-0                              | U-0             | U-0               | U-0             | U-0             | U-0      |

| _            |               | <u> </u>                         | <u> </u>        | <u> </u>          | _               | <u> </u>        | <u> </u> |

| bit 7        |               |                                  |                 |                   |                 |                 | bit (    |

|              |               |                                  |                 |                   |                 |                 |          |

| Legend:      |               |                                  |                 |                   |                 |                 |          |

| R = Readab   | le bit        | W = Writable I                   | oit             | U = Unimplem      | ented bit, read | l as '0'        |          |

| -n = Value a | t POR         | '1' = Bit is set                 |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown     |

|              |               |                                  |                 |                   |                 |                 |          |

| bit 15-12    | Unimplemen    | ted: Read as '0                  | )'              |                   |                 |                 |          |

| bit 11       | CMP4MD: An    | alog Comparat                    | or 4 Module D   | isable bit        |                 |                 |          |

|              | 0             | omparator 4 mo                   |                 |                   |                 |                 |          |

|              | •             | omparator 4 mo                   |                 |                   |                 |                 |          |

| bit 10       |               | alog Comparat                    |                 |                   |                 |                 |          |

|              | Ų             | omparator 3 mo<br>omparator 3 mo |                 |                   |                 |                 |          |

| bit 9        | •             | alog Comparat                    |                 |                   |                 |                 |          |

|              | 1 = Analog Co | omparator 2 mo                   | dule is disable | ed                |                 |                 |          |

|              | 0 = Analog Co | omparator 2 mo                   | dule is enable  | ed                |                 |                 |          |

| bit 8        | CMP1MD: An    | alog Comparat                    | or 1 Module D   | isable bit        |                 |                 |          |

|              | •             | omparator 1 mo                   |                 |                   |                 |                 |          |

|              | C C           | omparator 1 mo                   |                 | ed                |                 |                 |          |

| bit 7-0      | Unimplemen    |                                  |                 |                   |                 |                 |          |

#### REGISTER 9-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

#### 10.6.2.3 Virtual Pins

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices support four virtual RPn pins (RP32, RP33, RP34 and RP35), which are identical in functionality to all other RPn pins, with the exception of pinouts. These four pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP32 and the PWM Fault input can be configured for RP32 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

# 10.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 10.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |

|-------|--------------------------------------------------------------------------------------------------|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |

|       | See the MPLAB C30 Help files for more information.                                               |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 10.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent many write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| U-0                   | U-0                                                                                                                                                         | R/W-1                                                                                                                                                                                                                                    | R/W-1                                              | R/W-1             | R/W-1           | R/W-1           | R/W-1 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|-----------------|-----------------|-------|

|                       | _                                                                                                                                                           | IC2R5                                                                                                                                                                                                                                    | IC2R4                                              | IC2R3             | IC2R2           | IC2R1           | IC2R0 |

| bit 15                |                                                                                                                                                             |                                                                                                                                                                                                                                          |                                                    |                   |                 |                 | bit   |

| U-0                   | U-0                                                                                                                                                         | R/W-1                                                                                                                                                                                                                                    | R/W-1                                              | R/W-1             | R/W-1           | R/W-1           | R/W-1 |

|                       | —                                                                                                                                                           | IC1R5                                                                                                                                                                                                                                    | IC1R4                                              | IC1R3             | IC1R2           | IC1R1           | IC1R0 |

| bit 7                 |                                                                                                                                                             |                                                                                                                                                                                                                                          |                                                    |                   |                 |                 | bit   |

| Legend:               |                                                                                                                                                             |                                                                                                                                                                                                                                          |                                                    |                   |                 |                 |       |

| R = Readab            | le bit                                                                                                                                                      | W = Writable                                                                                                                                                                                                                             | bit                                                | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value a          | t POR                                                                                                                                                       | '1' = Bit is set                                                                                                                                                                                                                         | t                                                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-14<br>bit 13-8 | IC2R<5:0>: /                                                                                                                                                | ÷ .                                                                                                                                                                                                                                      |                                                    | to the Correspo   | onding RPn Pi   | n bits          |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                | but tied to Vss<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3                                                                                                                           | 4<br>3                                             |                   |                 |                 |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                | out tied to RP3<br>out tied to RP3<br>out tied to RP3                                                                                                                                                                                    | 4<br>3                                             |                   |                 |                 |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                | but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3                                                                                                                                              | 4<br>3                                             |                   |                 |                 |       |

| bit 7-6               | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•                                                                                      | but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3                                                                                                                                              | 4<br>3<br>2                                        |                   |                 |                 |       |

| bit 7-6<br>bit 5-0    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>ut tied to RP0<br>hted: Read as f                                                                                                         | 4<br>3<br>2<br>0'                                  | to the Correspo   | onding RPn Pi   | n bits          |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>ut tied to RP0<br>hted: Read as f                                                                                                         | 4<br>3<br>2<br>0'<br>apture 1 (IC1)<br>5<br>4<br>3 | to the Correspo   | onding RPn Pi   | n bits          |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | but tied to RP3<br>but tied to RP0<br><b>Ited:</b> Read as '<br>Assign Input Ca<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3; | 4<br>3<br>2<br>0'<br>apture 1 (IC1)<br>5<br>4<br>3 | to the Correspo   | onding RPn Pi   | n bits          |       |

### REGISTER 10-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0                | U-0                                                                                                                                                                                                           | R/W-1                                                                                                                                                                                                           | R/W-1                                    | R/W-1            | R/W-1            | R/W-1           | R/W-1   |  |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| —                  | —                                                                                                                                                                                                             | U1CTSR5                                                                                                                                                                                                         | U1CTSR4                                  | U1CTSR3          | U1CTSR2          | U1CTSR1         | U1CTSR0 |  |  |  |  |  |  |

| bit 15             |                                                                                                                                                                                                               |                                                                                                                                                                                                                 |                                          |                  |                  |                 | bit 8   |  |  |  |  |  |  |

| U-0                | U-0                                                                                                                                                                                                           | R/W-1                                                                                                                                                                                                           | R/W-1                                    | R/W-1            | R/W-1            | R/W-1           | R/W-1   |  |  |  |  |  |  |

| 0-0                | 0-0                                                                                                                                                                                                           | U1RXR5                                                                                                                                                                                                          | U1RXR4                                   | U1RXR3           | U1RXR2           | U1RXR1          | U1RXR0  |  |  |  |  |  |  |

| bit 7              |                                                                                                                                                                                                               | UTIXIL                                                                                                                                                                                                          | 01101104                                 | 0110010          | OTIVITZ          | UIIXI           | bit (   |  |  |  |  |  |  |

|                    |                                                                                                                                                                                                               |                                                                                                                                                                                                                 |                                          |                  |                  |                 |         |  |  |  |  |  |  |

| Legend:            |                                                                                                                                                                                                               |                                                                                                                                                                                                                 |                                          |                  |                  |                 |         |  |  |  |  |  |  |

| R = Readab         | le bit                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                    | bit                                      | U = Unimplen     | nented bit, read | l as '0'        |         |  |  |  |  |  |  |

| -n = Value a       | t POR                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                |                                          | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |

| bit 15-14          | Unimplement                                                                                                                                                                                                   | ted. Dood oo '                                                                                                                                                                                                  | <u>,</u>                                 |                  |                  |                 |         |  |  |  |  |  |  |

|                    | -                                                                                                                                                                                                             | ted: Read as '                                                                                                                                                                                                  |                                          |                  |                  |                 |         |  |  |  |  |  |  |

| bit 13-8           | U1CTSR<5:0>: Assign UART1 Clear-to-Send (U1CTS) to the Corresponding RPn Pin bits                                                                                                                             |                                                                                                                                                                                                                 |                                          |                  |                  |                 |         |  |  |  |  |  |  |

|                    |                                                                                                                                                                                                               |                                                                                                                                                                                                                 | 111111 = Input tied to Vss               |                  |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 <b>= I</b> np                                                                                                                                                                                          |                                                                                                                                                                                                                 |                                          |                  |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp                                                                                                                                                                                  | ut tied to RP35                                                                                                                                                                                                 |                                          |                  |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp                                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34                                                                                                                                                                              | ŀ                                        |                  |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                                                                                                                                                           | L<br>3                                   |                  |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34                                                                                                                                                                              | L<br>3                                   |                  |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                                                                                                                                                           | L<br>3                                   |                  |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                                                                                                                                                           | L<br>3                                   |                  |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                                                  | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                                        | L<br>3                                   |                  |                  |                 |         |  |  |  |  |  |  |

| bit 7-6            | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>00000 = Inpu                                                                                                              | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0                                                                                                                       | 4<br>3<br>2                              |                  |                  |                 |         |  |  |  |  |  |  |

| bit 7-6<br>bit 5-0 | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Inpu<br>Unimplemen                                                                                                                    | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '(                                                                                             | L<br>3<br>2                              | IRX) to the Co   | rresponding RF   | Pn Pin bits     |         |  |  |  |  |  |  |

| bit 7-6<br>bit 5-0 | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                   | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART                                                                            | L<br>3<br>2                              | IRX) to the Co   | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Inpu<br>Unimplement<br>U1RXR<5:0><br>111111 = Inp                                                                                     | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART                                                                            | )<br>)<br>1 Receive (U <sup>7</sup>      | IRX) to the Co   | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Inpu<br>Unimplement<br>U1RXR<5:0><br>111111 = Inp<br>100011 = Inp                                                                     | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss                                                          | 1<br>2<br>1 Receive (U <sup>7</sup>      | IRX) to the Co   | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33 | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co   | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34                    | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co   | rresponding RF   | Pn Pin bits     |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33 | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co   | rresponding RF   | 'n Pin bits     |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33 | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co   | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33 | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co   | rresponding RF   | Pn Pin bits     |         |  |  |  |  |  |  |

### REGISTER 10-6: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| R/W-0              | U-0                              | R/W-0                                    | U-0                   | U-0                          | U-0             | U-0                | U-0   |

|--------------------|----------------------------------|------------------------------------------|-----------------------|------------------------------|-----------------|--------------------|-------|

| TON <sup>(2)</sup> | —                                | TSIDL <sup>(1)</sup>                     |                       | _                            | _               | —                  |       |

| bit 15             |                                  |                                          |                       |                              |                 |                    | bit 8 |

| U-0                | R/W-0                            | R/W-0                                    | R/W-0                 | U-0                          | U-0             | R/W-0              | U-0   |

|                    | TGATE <sup>(2)</sup>             | TCKPS1 <sup>(2)</sup>                    | TCKPS0 <sup>(2)</sup> |                              |                 | TCS <sup>(2)</sup> |       |

| bit 7              |                                  |                                          |                       |                              |                 |                    | bit ( |

| Legend:            |                                  |                                          |                       |                              |                 |                    |       |

| R = Readabl        | e bit                            | W = Writable                             | bit                   | U = Unimplem                 | nented bit, rea | d as '0'           |       |

| -n = Value at      | POR                              | '1' = Bit is set                         |                       | '0' = Bit is clea            | ared            | x = Bit is unkn    | own   |

|                    |                                  |                                          |                       |                              |                 |                    |       |

| bit 15             | TON: Timery                      |                                          |                       |                              |                 |                    |       |

|                    | 1 = Starts 16-                   |                                          |                       |                              |                 |                    |       |

|                    | 0 = Stops 16-                    | -                                        |                       |                              |                 |                    |       |

| bit 14             | -                                | ted: Read as '                           |                       |                              |                 |                    |       |

| bit 13             |                                  | ry Stop in Idle N                        |                       |                              |                 |                    |       |

|                    |                                  | ues timer operation<br>s timer operation |                       | vice enters Idle             | mode            |                    |       |

| bit 12-7           |                                  | ited: Read as '                          |                       |                              |                 |                    |       |

| bit 6              | TGATE: Time                      | ery Gated Time                           | Accumulation          | n Enable bit <sup>(2)</sup>  |                 |                    |       |

|                    | When TCS =                       |                                          |                       |                              |                 |                    |       |

|                    | This bit is ign                  |                                          |                       |                              |                 |                    |       |

|                    | When TCS =                       |                                          |                       |                              |                 |                    |       |

|                    |                                  | ne accumulation<br>ne accumulation       |                       |                              |                 |                    |       |

| bit 5-4            |                                  | : Timery Input                           |                       | e Select bits <sup>(2)</sup> |                 |                    |       |

|                    | 11 = 1:256 pr                    |                                          |                       |                              |                 |                    |       |

|                    | 10 = 1:64 pre                    |                                          |                       |                              |                 |                    |       |

|                    | 01 = 1:8 pres                    |                                          |                       |                              |                 |                    |       |

|                    | 00 = 1:1 pres                    |                                          |                       |                              |                 |                    |       |

| bit 3-2            | -                                | ted: Read as '                           |                       |                              |                 |                    |       |

| bit 1              |                                  | Clock Source S                           |                       |                              |                 |                    |       |

|                    | 1 = External o<br>0 = Internal c | clock from TxC<br>lock (Fosc/2)          | K pin                 |                              |                 |                    |       |

|                    |                                  |                                          |                       |                              |                 |                    |       |

### REGISTER 12-2: TyCON: TIMERY CONTROL REGISTER (y = 3)

bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timerx Control (TxCON<3>) register, these

**2:** When the 32-bit timer operation is enabled (T32 = 1) in the Timerx Control (TxCON<3>) register, these bits have no effect.

| REGISTER 14-1: | OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2) |

|----------------|------------------------------------------------------|

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | OCSIDL | —   | —   | _   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R-0, HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|---------|--------|-------|-------|-------|

| —     | —   | —   | OCFLT   | OCTSEL | OCM2  | OCM1  | OCM0  |

| bit 7 |     |     |         |        |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit |                           |                    |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                                                                                                                   |

|           | 1 = Output Compare x halts in CPU Idle mode                                                                                                                                            |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                                                                                                                             |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                             |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                  |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in hardware only)</li> <li>0 = No PWM Fault condition has occurred (this bit is only used when OCM&lt;2:0&gt; = 111)</li> </ul> |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                                                                                                                                |

|           | 1 = Timer3 is the clock source for Output Compare x                                                                                                                                    |

|           | 0 = Timer2 is the clock source for Output Compare x                                                                                                                                    |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                                                                                                                              |

|           | 111 = PWM mode on OCx, Fault pin is enabled                                                                                                                                            |

|           | 110 = PWM mode on OCx, Fault pin is disabled                                                                                                                                           |

|           | 101 = Initializes OCx pin low, generates continuous output pulses on OCx pin                                                                                                           |

|           | 100 = Initializes OCx pin low, generates single output pulse on OCx pin                                                                                                                |

|           | <ul> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initializes OCx pin high, compare event forces OCx pin low</li> </ul>                                                      |

|           | 001 = Initializes OCx pin low, compare event forces OCx pin high                                                                                                                       |

|           | 000 = Output compare channel is disabled                                                                                                                                               |

|           |                                                                                                                                                                                        |

## 15.3 Control Registers

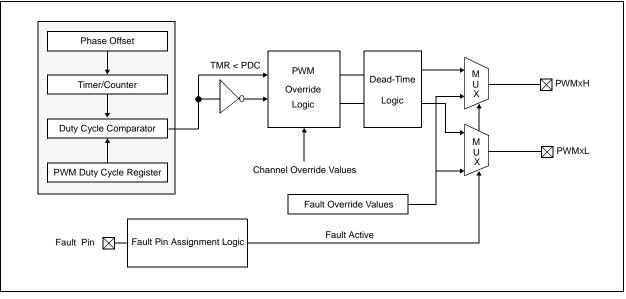

The following registers control the operation of the high-speed PWM module.

- PTCON: PWM Time Base Control Register

- PTCON2: PWM Clock Divider Select Register

- PTPER: PWM Master Time Base Register(1)

- SEVTCMP: PWM Special Event Compare Register

- MDC: PWM Master Duty Cycle Register(1,2)

- PWMCONx: PWMx Control Register

- PDCx: PWMx Generator Duty Cycle Register(1,2)

- PHASEx: PWMx Primary Phase-Shift Register(1,2) (provides the local time base period for PWMxH)

- DTRx: PWMx Dead-Time Register

- ALTDTRx: PWMx Alternate Dead-Time Register

- SDCx: PWMx Secondary Duty Cycle Register(1,2)

- SPHASEx: PWMx Secondary Phase-Shift Register(1,2) (provides the local time base period for PWMxL)

- TRGCONx: PWMx Trigger Control Register

- IOCONx: PWMx I/O Control Register

- FCLCONx: PWMx Fault Current-Limit Control Register

- TRIGx: PWMx Primary Trigger Compare Value Register

- STRIGx: PWMx Secondary Trigger Compare Value Register

- LEBCONx: Leading-Edge Blanking Control Register(1)

- PWMCAPx: Primary PWMx Time Base Capture Register

## © 2008-2014 Microchip Technology Inc.

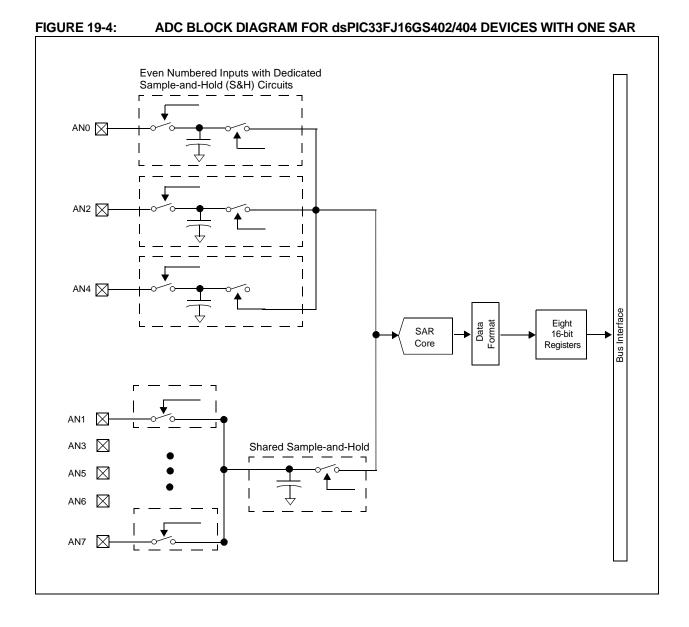

| REGISTE            | R 19-1: ADO                      | CON: ANALOO                                               | G-TO-DIGITAL (                                                                                           | CONTROL                                       | REGISTER                                                 |                                                          |                                           |  |  |

|--------------------|----------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|-------------------------------------------|--|--|

| R/W-0              | U-0                              | R/W-0                                                     | R/W-0                                                                                                    | U-0                                           | R/W-0                                                    | U-0                                                      | R/W-0                                     |  |  |

| ADON               |                                  | ADSIDL                                                    | SLOWCLK <sup>(1)</sup>                                                                                   |                                               | GSWTRG                                                   |                                                          | FORM <sup>(1)</sup>                       |  |  |

| bit 15             |                                  |                                                           |                                                                                                          |                                               |                                                          | ·                                                        | bit                                       |  |  |

| R/W-0              | R/W-0                            | R/W-0                                                     | R/W-0                                                                                                    | U-0                                           | R/W-0                                                    | R/W-1                                                    | R/W-1                                     |  |  |

| EIE <sup>(1)</sup> | ORDER <sup>(1,2)</sup>           | SEQSAMP <sup>(1,2)</sup>                                  |                                                                                                          |                                               | ADCS2 <sup>(1)</sup>                                     | ADCS1 <sup>(1)</sup>                                     | ADCS0 <sup>(1)</sup>                      |  |  |

| bit 7              | ORDER                            |                                                           | //011100/////                                                                                            |                                               | AB002                                                    | 7,0001                                                   | bit                                       |  |  |

| Legend:            |                                  |                                                           |                                                                                                          |                                               |                                                          |                                                          |                                           |  |  |

| R = Reada          | able bit                         | W = Writable bi                                           | it                                                                                                       | U = Unimple                                   | emented bit, rea                                         | d as '0'                                                 |                                           |  |  |

| -n = Value         | at POR                           | '1' = Bit is set                                          |                                                                                                          | '0' = Bit is c                                |                                                          | x = Bit is unk                                           | nown                                      |  |  |

| bit 15             | ADON: Anal                       | og-to-Digital Ope                                         | arating Mode bit                                                                                         |                                               |                                                          |                                                          |                                           |  |  |

| bit 15             |                                  | o-Digital Convert                                         | er (ADC) module                                                                                          | is operating                                  |                                                          |                                                          |                                           |  |  |

| bit 14             | Unimpleme                        | nted: Read as '0                                          | ,                                                                                                        |                                               |                                                          |                                                          |                                           |  |  |

| bit 13             | ADSIDL: AD                       | C Stop in Idle M                                          | ode bit                                                                                                  |                                               |                                                          |                                                          |                                           |  |  |

|                    |                                  |                                                           | eration when devid                                                                                       | ce enters Idle                                | mode                                                     |                                                          |                                           |  |  |

| bit 12             | SLOWCLK:                         | SLOWCLK: Enable The Slow Clock Divider bit <sup>(1)</sup> |                                                                                                          |                                               |                                                          |                                                          |                                           |  |  |

|                    |                                  | clocked by the au<br>clock by the prim                    | uxiliary PLL (ACLI<br>ary PLL (Fvco)                                                                     | <)                                            |                                                          |                                                          |                                           |  |  |

| bit 11             | Unimplemented: Read as '0'       |                                                           |                                                                                                          |                                               |                                                          |                                                          |                                           |  |  |

| bit 10             | GSWTRG: G                        | Blobal Software                                           | Trigger bit                                                                                              |                                               |                                                          |                                                          |                                           |  |  |

|                    |                                  | isters. This bit m                                        | ser, it will trigger o<br>oust be cleared by                                                             |                                               |                                                          |                                                          |                                           |  |  |

| bit 9              |                                  | nted: Read as '0                                          | ,                                                                                                        |                                               |                                                          |                                                          |                                           |  |  |

| bit 8              | -                                | Output Format I                                           |                                                                                                          |                                               |                                                          |                                                          |                                           |  |  |

|                    | 1 = Fractiona                    | al (Dout = dddd                                           | l dddd dd00 00<br>Odd dddd dddd                                                                          |                                               |                                                          |                                                          |                                           |  |  |

| bit 7              |                                  | terrupt Enable bi                                         |                                                                                                          | ,                                             |                                                          |                                                          |                                           |  |  |

|                    | 1 = Interrupt                    | is generated after                                        | er first conversion<br>er second convers                                                                 |                                               |                                                          |                                                          |                                           |  |  |

| bit 6              |                                  | nversion Order b                                          |                                                                                                          | •                                             |                                                          |                                                          |                                           |  |  |

|                    | 1 = Odd num                      | nbered analog in                                          | put is converted fingut is converted                                                                     |                                               |                                                          |                                                          |                                           |  |  |

| bit 5              |                                  | -                                                         | ple Enable bit <sup>(1,2)</sup>                                                                          |                                               | 5                                                        |                                                          |                                           |  |  |

|                    | ORDER<br>0 = Shared<br>currently | = 0. If ORDER =<br>S&H is sampled<br>/ busy with an e     | Id (S&H) circuit<br>= 1, then the shar<br>at the same time<br>existing conversion<br>ed, then the shared | ed S&H is sa<br>the dedicate<br>on process. I | impled at the sta<br>ed S&H is sampl<br>If the shared Sa | art of the first co<br>led if the share<br>&H is busy at | onversion.<br>ed S&H is no<br>the time th |  |  |

|                    |                                  | -                                                         | hanged while AD<br>devices with one                                                                      |                                               | (ADON = 0).                                              |                                                          |                                           |  |  |

## REGISTER 19-1: ADCON: ANALOG-TO-DIGITAL CONTROL REGISTER

2: These bits are only available on devices with one SAR.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

The double-word instructions execute in two instruction cycles.