Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| 2 010                      |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 6KB (6K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

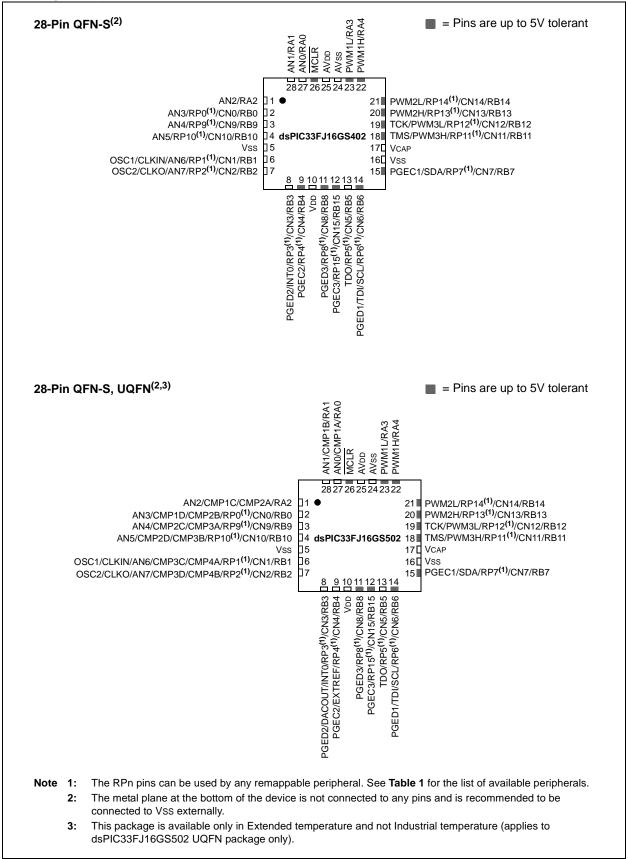

# Pin Diagrams (Continued)

# TABLE 4-27: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6          | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|--------|--------|----------|----------|----------|----------|----------|-------------|----------------|---------|-----------|----------|----------|----------|----------|---------------|

| ADCON        | 0300        | ADON   | —      | ADSIDL | SLOWCLK  | —        | GSWTRG   | —        | FORM     | EIE         | ORDER          | SEQSAMP | ASYNCSAMP | —        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _      | -      | —      | _        | _        |          | _        | —        | _           | _              | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _      | -      | —      | _        | _        |          | _        | —        | _           | P6RDY          | _       | _         | _        | P2RDY    | P1RDY    | PORDY    | 0000          |

| ADBASE       | 0308        |        |        |        |          |          |          |          | ADBASE<1 | 5:1>        |                |         |           |          |          |          | —        | 0000          |

| ADCPC0       | 030A        | IRQEN1 | PEND1  | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0          | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | _      | -      | —      | _        | _        |          | _        | —        | IRQEN2      | PEND2          | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCPC3       | 0310        | _      |        | —      | _        | _        | _        | —        | —        | IRQEN6      | PEND6          | SWTRG6  | TRGSRC64  | TRGSRC63 | TRGSRC62 | TRGSRC61 | TRGSRC60 | 0000          |

| ADCBUF0      | 0320        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 0              |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |        |        |        |          |          |          |          | ADC E    | Data Buffer | <sup>.</sup> 1 |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 2              |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 3              |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 4              |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 5              |         |           |          |          |          |          | xxxx          |

| ADCBUF12     | 0338        |        |        |        |          |          |          |          | ADC D    | ata Buffer  | 12             |         |           |          |          |          |          | xxxx          |

| ADCBUF13     | 033A        |        |        |        |          |          |          |          | ADC D    | Data Buffer | 13             |         |           |          |          |          |          | xxxx          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

# TABLE 4-28: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ16GS402/404 DEVICES ONLY

|              | -           |         |          |            | -           |                 |               |               |              |            |       | -       |           |          |          |          |          |               |

|--------------|-------------|---------|----------|------------|-------------|-----------------|---------------|---------------|--------------|------------|-------|---------|-----------|----------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13     | Bit 12      | Bit 11          | Bit 10        | Bit 9         | Bit 8        | Bit 7      | Bit 6 | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADCON        | 0300        | ADON    | —        | ADSIDL     | SLOWCLK     | _               | GSWTRG        | _             | FORM         | EIE        | ORDER | SEQSAMP | ASYNCSAMP | -        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _       | -        | _          | _           | —               | _             | _             | _            | PCFG7      | PCFG6 | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _       | _        | _          | _           | —               | _             | _             | _            | _          | _     | _       | _         | P3RDY    | P2RDY    | P1RDY    | P0RDY    | 0000          |

| ADBASE       | 0308        |         |          |            |             |                 |               |               | ADBASE<15    | :1>        |       |         |           |          |          |          | —        | 0000          |

| ADCPC0       | 030A        | IRQEN1  | PEND1    | SWTRG1     | TRGSRC14    | TRGSRC13        | TRGSRC12      | TRGSRC11      | TRGSRC10     | IRQEN0     | PEND0 | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | IRQEN3  | PEND3    | SWTRG3     | TRGSRC34    | TRGSRC33        | TRGSRC32      | TRGSRC31      | TRGSRC30     | IRQEN2     | PEND2 | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCBUF0      | 0320        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 0     |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 1     |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 2     |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 3     |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 4     |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 5     |         |           |          |          |          |          | xxxx          |

| ADCBUF6      | 032C        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 6     |         |           |          |          |          |          | xxxx          |

| ADCBUF7      | 032E        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 7     |         |           |          |          |          |          | xxxx          |

| Legend:      | x =         | unknown | value on | Reset, — = | unimplement | ed, read as '0' | . Reset value | s are shown i | n hexadecima | al.        |       |         |           |          |          |          |          |               |

# TABLE 4-33: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|--------|----------|----------|----------|----------|----------|----------|-------|-------|----------|----------|----------|----------|----------|----------|---------------|

| RPINR0       | 0680        | _      | -      | INT1R5   | INT1R4   | INT1R3   | INT1R2   | INT1R1   | INT1R0   | _     |       | -        | _        | _        | —        | _        | _        | 3F00          |

| RPINR1       | 0682        |        |        | _        | _        | _        | _        | _        | _        | _     | _     | INT2R5   | INT2R4   | INT2R3   | INT2R2   | INT2R1   | INT2R0   | 003F          |

| RPINR2       | 0684        |        |        | T1CKR5   | T1CKR4   | T1CKR3   | T1CKR2   | T1CKR1   | T1CKR0   | _     | _     | _        | _        | _        | _        | _        | _        | 0000          |

| RPINR3       | 0686        |        |        | T3CKR5   | T3CKR4   | T3CKR3   | T3CKR2   | T3CKR1   | T3CKR0   | _     | _     | T2CKR5   | T2CKR4   | T2CKR3   | T2CKR2   | T2CKR1   | T2CKR0   | 3F3F          |

| RPINR7       | 068E        | _      | _      | IC2R5    | IC2R4    | IC2R3    | IC2R2    | IC2R1    | IC2R0    | _     | _     | IC1R5    | IC1R4    | IC1R3    | IC1R2    | IC1R1    | IC1R0    | 3F3F          |

| RPINR11      | 0696        | _      | _      | _        | _        | —        | _        | _        | _        | _     | _     | OCFAR5   | OCFAR4   | OCFAR3   | OCFAR2   | OCFAR1   | OCFAR0   | 3F3F          |

| RPINR18      | 06A4        |        |        | U1CTSR5  | U1CTSR4  | U1CTSR3  | U1CTSR2  | U1CTSR1  | U1CTSR0  | _     | _     | U1RXR5   | U1RXR4   | U1RXR3   | U1RXR2   | U1RXR1   | U1RXR0   | 003F          |

| RPINR20      | 06A8        | -      |        | SCK1R5   | SCK1R4   | SCK1R3   | SCK1R2   | SCK1R1   | SCK1R0   | _     | _     | SDI1R5   | SDI1R4   | SDI1R3   | SDI1R2   | SDI1R1   | SDI1R0   | 3F3F          |

| RPINR21      | 06AA        |        |        | _        | _        | _        | _        | _        | _        | _     | _     | SS1R5    | SS1R54   | SS1R3    | SS1R2    | SS1R1    | SS1R0    | 0000          |

| RPINR29      | 06BA        |        |        | FLT1R5   | FLT1R4   | FLT1R3   | FLT1R2   | FLT1R1   | FLT1R0   | _     | _     | _        | _        | _        | _        | _        | _        | 3F00          |

| RPINR30      | 06BC        |        |        | FLT3R5   | FLT3R4   | FLT3R3   | FLT3R2   | FLT3R1   | FLT3R0   | _     | _     | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | 3F3F          |

| RPINR31      | 06BE        |        |        | FLT5R5   | FLT5R4   | FLT5R3   | FLT5R2   | FLT5R1   | FLT5R0   | _     | _     | FLT4R5   | FLT4R4   | FLT4R3   | FLT4R2   | FLT4R1   | FLT4R0   | 3F3F          |

| RPINR32      | 06C0        |        |        | FLT7R5   | FLT7R4   | FLT7R3   | FLT7R2   | FLT7R1   | FLT7R0   | _     | _     | FLT6R5   | FLT6R4   | FLT6R3   | FLT6R2   | FLT6R1   | FLT6R0   | 3F3F          |

| RPINR33      | 06C2        | _      | _      | SYNCI1R5 | SYNCI1R4 | SYNCI1R3 | SYNCI1R2 | SYNCI1R1 | SYNCI1R0 | _     | _     | FLT8R5   | FLT8R4   | FLT8R3   | FLT8R2   | FLT8R1   | FLT8R0   | 3F3F          |

| RPINR34      | 06C4        | _      | _      | _        | _        | -        |          | _        | —        | —     |       | SYNCI2R5 | SYNCI2R4 | SYNCI2R3 | SYNCI2R2 | SYNCI2R1 | SYNCI2R0 | 3F3F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-34: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ06GS101

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| RPOR0        | 06D0        | _      |        | RP1R5  | RP1R4  | RP1R3  | RP1R2  | RP1R1  | RP1R0  | _     |       | RP0R5  | RP0R4  | RP0R3  | RP0R2  | RP0R1  | RP0R0  | 0000          |

| RPOR1        | 06D2        |        | _      | RP3R5  | RP3R4  | RP3R3  | RP3R2  | RP3R1  | RP3R0  |       | _     | RP2R5  | RP2R4  | RP2R3  | RP2R2  | RP2R1  | RP2R0  | 0000          |

| RPOR2        | 06D4        |        | _      | RP5R5  | RP5R4  | RP5R3  | RP5R2  | RP5R1  | RP5R0  |       | _     | RP4R5  | RP4R4  | RP4R3  | RP4R2  | RP4R1  | RP4R0  | 0000          |

| RPOR3        | 06D6        |        | _      | RP7R5  | RP7R4  | RP7R3  | RP7R2  | RP7R1  | RP7R0  |       | _     | RP6R5  | RP6R4  | RP6R3  | RP6R2  | RP6R1  | RP6R0  | 0000          |

| RPOR16       | 06F0        |        | _      | RP33R5 | RP33R4 | RP33R3 | RP33R2 | RP33R1 | RP33R0 |       | _     | RP32R5 | RP32R4 | RP32R3 | RP32R2 | RP32R1 | RP32R0 | 0000          |

| RPOR17       | 06F2        |        | _      | RP35R5 | RP35R4 | RP35R3 | RP35R2 | RP35R1 | RP35R0 | -     | _     | RP34R5 | RP34R4 | RP34R3 | RP34R2 | RP34R1 | RP34R0 | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-41: SYSTEM CONTROL REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets       |

|--------------|-------------|--------|--------|---------|--------|--------|-----------|-----------|-----------|----------|----------|--------|----------|---------|---------|---------|---------|---------------------|

| RCON         | 0740        | TRAPR  | IOPUWR |         |        | _      |           | CM        | VREGS     | EXTR     | SWR      | SWDTEN | WDTO     | SLEEP   | IDLE    | BOR     | POR     | <sub>xxxx</sub> (1) |

| OSCCON       | 0742        | —      | COSC2  | COSC1   | COSC0  |        | NOSC2     | NOSC1     | NOSC0     | CLKLOCK  | IOLOCK   | LOCK   | _        | CF      |         |         | OSWEN   | 0300 <b>(2)</b>     |

| CLKDIV       | 0744        | ROI    | DOZE2  | DOZE1   | DOZE0  | DOZEN  | FRCDIV2   | FRCDIV1   | FRCDIV0   | PLLPOST1 | PLLPOST0 | _      | PLLPRE4  | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 3040                |

| PLLFBD       | 0746        | _      | —      | _       | _      | _      | —         | _         |           |          |          | PLLI   | OIV<8:0> |         |         |         |         | 0030                |

| REFOCON      | 074E        | ROON   | —      | ROSSLP  | ROSEL  | RODIV3 | RODIV2    | RODIV1    | RODIV0    | _        |          | _      | _        | _       |         |         | —       | 0000                |

| OSCTUN       | 0748        |        | —      |         | _      | -      |           | -         | -         | _        | -        |        |          | TUN<    | :5:0>   |         |         | 0000                |

| ACLKCON      | 0750        | ENAPLL | APLLCK | SELACLK | -      | _      | APSTSCLR2 | APSTSCLR1 | APSTSCLR0 | ASRCSEL  | FRCSEL   | _      | _        | _       | _       | _       | —       | 2300                |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The RCON register Reset values are dependent on the type of Reset.

2: The OSCCON register Reset values are dependent on the FOSCx Configuration bits and on type of Reset.

#### TABLE 4-42: NVM REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------|--------|--------|--------|---------------------|

| NVMCON       | 0760        | WR     | WREN   | WRERR  | —      | _      |        | —     | _     | _     | ERASE | _     |       | NVMOP3  | NVMOP2 | NVMOP1 | NVMOP0 | <sub>0000</sub> (1) |

| NVMKEY       | 0766        | _      | _      | _      | _      | _      |        | -     | _     |       |       |       | NVMKE | EY<7:0> |        |        |        | 0000                |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. The value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-43: PMD REGISTER MAP FOR dsPIC33FJ06GS101 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1         | 0770        | _      | —      | _      | T2MD   | T1MD   | _      | PWMMD | _      | I2C1MD | _     | U1MD  | —     | SPI1MD | —     | —     | ADCMD | 0000          |

| PMD2         | 0772        | _      | _      | _      | _      | _      | _      | IC2MD | IC1MD  | _      |       | _     | _     | -      | _     | OC2MD | OC1MD | 0000          |

| PMD3         | 0774        | _      |        |        | I      | -      | CMPMD  |       | I      | _      | -     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4         | 0776        | _      | —      | _      | -      | _      | _      | _     | _      | —      | _     | —     | —     | REFOMD | —     | —     | _     | 0000          |

| PMD6         | 077A        | _      | -      | -      |        | PWM4MD | -      | -     | PWM1MD | _      | -     | _     | _     | -      | -     | _     | —     | 0000          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-44: PMD REGISTER MAP FOR dsPIC33FJ06GS102 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1         | 0770        | _      | —      | _      | T2MD   | T1MD   | —      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD |       | —     | ADCMD | 0000          |

| PMD2         | 0772        | Ι      | _      | _      | _      | _      | _      | IC2MD  | IC1MD  | _      | _     | _     | _     | _      | _     | OC2MD | OC1MD | 0000          |

| PMD3         | 0774        | Ι      | —      | —      | —      | —      | CMPMD  |        |        | -      |       | _     | —     | —      | _     | —     | -     | 0000          |

| PMD4         | 0776        | -      | —      | —      | —      | _      | —      | —      | _      | _      | —     | —     | _     | REFOMD | —     | —     | _     | 0000          |

| PMD6         | 077A        | _      | —      | _      | —      | —      | —      | PWM2MD | PWM1MD | _      |       | _     | _     | —      | _     | -     | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000318G-page 71

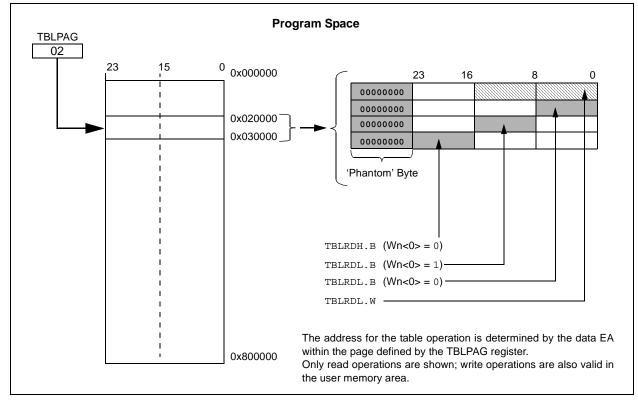

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70192) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: Software RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), which is set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

# FIGURE 6-1: **RESET SYSTEM BLOCK DIAGRAM RESET** Instruction Glitch Filter MCLR WDT Module Sleep or Idle BOR Internal SYSRST Regulator Vdd POR VDD Rise Detect Trap Conflict Illegal Opcode Uninitialized W Register Configuration Mismatch

# 6.1 System Reset

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 families of devices have two types of Reset:

- Cold Reset

- Warm Reset

A Cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a Cold Reset, the FNOSCx Configuration bits in the FOSC Configuration register select the device clock source. A Warm Reset is the result of all the other Reset sources, including the RESET instruction. On Warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection (COSC<2:0>) bits in the Oscillator Control (OSCCON<14:12>) register.

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is detailed in Figure 6-2.

| Oscillator Mode           | Oscillator<br>Startup Delay | Oscillator<br>Startup Timer | PLL Lock Time        | Total Delay                             |

|---------------------------|-----------------------------|-----------------------------|----------------------|-----------------------------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd <sup>(1)</sup>        | _                           | _                    | Toscd <sup>(1)</sup>                    |

| FRCPLL                    | Toscd <sup>(1)</sup>        | _                           | ТLОСК <sup>(3)</sup> | Toscd + Tlock <sup>(1,3)</sup>          |

| XT                        | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| HS                        | Toscd(1)                    | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| EC                        | —                           | —                           | —                    | —                                       |

| XTPLL                     | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | ТLОСК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| HSPLL                     | Toscd(1)                    | Tost <sup>(2)</sup>         | ТLOCК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| ECPLL                     | —                           | —                           | ТLОСК <sup>(3)</sup> | TLOCK <sup>(3)</sup>                    |

| LPRC                      | Toscd <sup>(1)</sup>        | _                           | —                    | Toscd <sup>(1)</sup>                    |

## TABLE 6-1:OSCILLATOR DELAY

**Note 1:** TOSCD = Oscillator start-up delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal) if PLL is enabled.

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

# FIGURE 7-1: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 INTERRUPT VECTOR TABLE

|                                   |                             | -         |                                                        |

|-----------------------------------|-----------------------------|-----------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction    | 0x000000  |                                                        |

|                                   | Reset – GOTO Address        | 0x000002  |                                                        |

|                                   | Reserved                    | 0x000004  |                                                        |

|                                   | Oscillator Fail Trap Vector |           |                                                        |

|                                   | Address Error Trap Vector   |           |                                                        |

|                                   | Stack Error Trap Vector     |           |                                                        |

|                                   | Math Error Trap Vector      |           |                                                        |

|                                   | Reserved                    |           |                                                        |

|                                   | Reserved                    |           |                                                        |

|                                   | Reserved                    |           |                                                        |

|                                   | Interrupt Vector 0          | 0x000014  |                                                        |

|                                   | Interrupt Vector 1          |           |                                                        |

|                                   | ~                           |           |                                                        |

|                                   | ~                           |           |                                                        |

|                                   | ~                           |           |                                                        |

|                                   | Interrupt Vector 52         | 0x00007C  | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

|                                   | Interrupt Vector 53         | 0x00007E  |                                                        |

| rity                              | Interrupt Vector 54         | 0x000080  |                                                        |

| Jric                              | ~                           |           |                                                        |

| ж<br>Н                            | ~                           |           |                                                        |

| rde                               | ~                           |           |                                                        |

| 0                                 | Interrupt Vector 116        | 0x0000FC  |                                                        |

| nra                               | Interrupt Vector 117        | 0x0000FE  |                                                        |

| Decreasing Natural Order Priority | Reserved                    | 0x000100  |                                                        |

| l b                               | Reserved                    | 0x000102  |                                                        |

| asir                              | Reserved                    | _         |                                                        |

| rea                               | Oscillator Fail Trap Vector | _         |                                                        |

| Dec                               | Address Error Trap Vector   | _         |                                                        |

|                                   | Stack Error Trap Vector     | _         |                                                        |

|                                   | Math Error Trap Vector      | -         |                                                        |

|                                   | Reserved                    |           | 1                                                      |

|                                   | Reserved                    | _         |                                                        |

|                                   | Reserved                    | 00001111  |                                                        |

|                                   | Interrupt Vector 0          | 0x000114  |                                                        |

|                                   | Interrupt Vector 1          | -         |                                                        |

|                                   | ~                           | -         |                                                        |

|                                   | ~                           | -         | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   |                             | 0x00017C  |                                                        |

|                                   | Interrupt Vector 53         | 0x00017E  |                                                        |

|                                   | Interrupt Vector 54         | 0x00017L  |                                                        |

|                                   |                             | 0,000,100 |                                                        |

|                                   | ~                           | -         |                                                        |

|                                   |                             | -         |                                                        |

|                                   | Interrupt Vector 116        |           | 1                                                      |

|                                   | Interrupt Vector 117        | 0x0001FE  |                                                        |

| *                                 | Start of Code               | 0x000200  |                                                        |

|                                   |                             |           |                                                        |

|                                   |                             |           |                                                        |

|                                   |                             |           |                                                        |

|                                   |                             |           |                                                        |

#### REGISTER 15-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (CONTINUED)

- FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits<sup>(2,3)</sup> bit 7-3 11111 = Reserved01000 = Reserved 00111 = Fault 8 00110 = Fault 7 00101 = Fault 6 00100 = Fault 5 00011 = Fault 4 00010 = Fault 3 00001 = Fault 2 00000 = Fault 1 FLTPOL: Fault Polarity for PWM Generator # bit<sup>(1)</sup> bit 2 1 = The selected Fault source is active-low 0 = The selected Fault source is active-high bit 1-0 FLTMOD<1:0>: Fault Mode for PWM Generator # bits 11 = Fault input is disabled 10 = Reserved 01 = The selected Fault source forces the PWMxH and PWMxL pins to FLTDAT values (cycle) 00 = The selected Fault source forces the PWMxH and PWMxL pins to FLTDAT values (latched condition) Note 1: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 2: When Independent Fault mode is enabled (IFLTMOD = 1), and Fault 1 is used for Current-Limit mode (CLSRC<4:0> = b0000), the Fault Control Source Select bits (FLTSRC<4:0>) should be set to an unused Fault source to prevent Fault 1 from disabling both the PWMxL and PWMxH outputs.

- 3: When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Fault mode (FLTSRC<4:0> = b0000), the Current-Limit Control Source Select bits (CLSRC<4:0>) should be set to an unused current-limit source to prevent the current-limit source from disabling both the PWMxH and PWMxL outputs.

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0             | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| _               |       | —                | _     | _                |                 | AMSk            | <9:8> |

| bit 15          | ·     |                  |       |                  | -               |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | AMS   | K<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

# REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Mask for Address bit x Select bits

1 = Enables masking for bit x of incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | <b>URXINV:</b> UARTx Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <b>BRGH:</b> High Baud Rate Enable bit<br>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)<br>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode) |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                              |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                                      |

- **Note 1:** Refer to "**UART**" (DS70188) in the "*dsPIC33F/PIC24H Family Reference Manual*" for information on enabling the UART module for receive or transmit operation.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                       | R/W-0, HC                                              | R/W-0                             | R-0                        | R-1        |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------|----------------------------|------------|--|

| UTXISEL1        | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UTXISEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           | UTXBRK                                                 | UTXEN <sup>(1)</sup>              | UTXBF                      | TRMT       |  |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |                                                        |                                   |                            | bit 8      |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R-1                                                                       | R-0                                                    | R-0                               | R/C-0                      | R-0        |  |

| URXISEL1        | URXISEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADDEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RIDLE                                                                     | PERR                                                   | FERR                              | OERR                       | URXDA      |  |

| bit 7           | UKAISELU                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADDEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RIDLE                                                                     | FERR                                                   | FERR                              | UERK                       | bit (      |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |                                                        |                                   |                            | Dir v      |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | HC = Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Clearable bit                                                             | C = Clearable                                          | e bit                             |                            |            |  |

| R = Readable    | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           | U = Unimpler                                           | mented bit, rea                   | ad as '0'                  |            |  |

| -n = Value at I | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           | '0' = Bit is cle                                       | ared                              | x = Bit is unk             | known      |  |

| bit 15,13       | 11 = Reserve<br>10 = Interrupt<br>the trans<br>01 = Interrupt<br>operatio<br>00 = Interrupt                                                                                                                                                                                                                                                                                                                                                                                         | Contraction of the second state of the seco | er is transferren<br>nes empty<br>character is s<br>t<br>er is transferre | d to the Transn<br>hifted out of th<br>d to the Transn | nit Shift Regist<br>ne Transmit S | Shift Register;            | all transm |  |

| bit 14          | If IREN = 0:           1 = UxTX Idle           0 = UxTX Idle           If IREN = 1:                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           | bit                                                    |                                   |                            |            |  |