Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 6KB (6K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the primary reference for the operation of a particular module or device feature.

| Note: | To access the documents listed below,<br>browse to the documentation section<br>of the dsPIC33FJ16GS504 product<br>page of the Microchip web site<br>(www.microchip.com). |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | In addition to parameters, features, and<br>other documentation, the resulting page<br>provides links to the related family<br>reference manual sections.                 |

- "Introduction" (DS70197)

- "CPU" (DS70204)

- "Data Memory" (DS70202)

- "Program Memory" (DS70203)

- "Flash Programming" (DS70191)

- "Reset" (DS70192)

- "Watchdog Timer (WDT) and Power-Saving Modes" (DS70196)

- "I/O Ports" (DS70193)

- "Timers" (DS70205)

- "Input Capture" (DS70198)

- "Output Compare" (DS70005157)

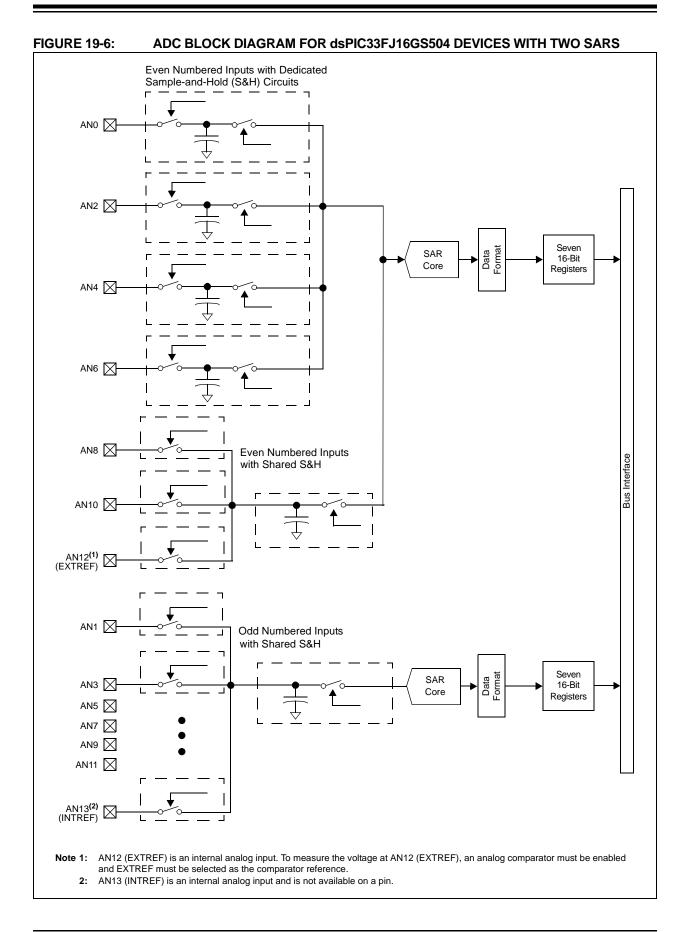

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70188)

- "Serial Peripheral Interface (SPI)" (DS70206)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195)

- "CodeGuard™ Security (DS70199)

- "Programming and Diagnostics" (DS70207)

- "Device Configuration" (DS70194)

- "Interrupts (Part IV)" (DS70300)

- "Oscillator (Part IV)" (DS70307)

- "High- Speed PWM Module" (DS70000323)

- "High-Speed 10-Bit ADC" (DS70000321)

- "High-Speed Analog Comparator" (DS70296)

- "Oscillator (Part VI)" (DS70644)

#### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the ADPCFG register.

The bits in the registers that correspond to the A/D pins that are initialized by MPLAB ICD 2, ICD 3, or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the ADPCFG register during initialization of the ADC module.

When MPLAB ICD 2, ICD 3, or REAL ICE is used as a programmer, the user application firmware must correctly configure the ADPCFG register. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins and drive the output to logic low.

### 2.10 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-4 through Figure 2-11.

#### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/ 16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (for example, ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- Signed or Unsigned DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation | ACC<br>Write Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value that is sign-extended to 40 bits. Integer data is inherently represented as a signed 2's complement value, where the Most Significant bit (MSb) is defined as a sign bit. The range of an N-bit 2's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ .

- For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0.

- For a 32-bit integer, the data range is

-2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a 2's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit 2's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product that has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiply operations.

The MUL instruction can be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

# 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled using the barrel shifter prior to accumulation.

# 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side, and either true or complement data into the other input.

- In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented).

- In the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented.

The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS Register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits, 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block that controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described previously and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS Register bits support saturation and overflow:

- OA: ACCA overflowed into guard bits

- · OB: ACCB overflowed into guard bits

- SA: ACCA saturated (bit 31 overflow and saturation) or

~

or

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation)

• SB: ACCB saturated (bit 31 overflow and saturation)

ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- OAB: Logical OR of OA and OB

- SAB: Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register are set (refer to **Section 7.0 "Interrupt Controller"**). This allows the user application to take immediate action, for example, to correct system gain.

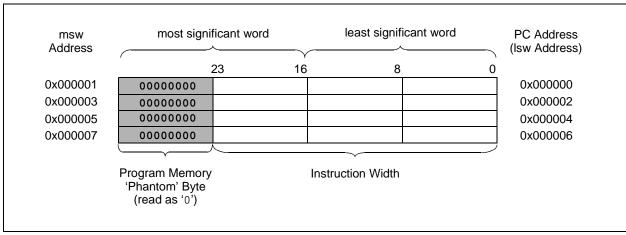

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate consider each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (see Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during the code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

#### TABLE 4-35: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ06GS102, dsPIC33FJ06GS202, dsPIC33FJ16GS402 AND dsPIC33FJ16GS502

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| RPOR0        | 06D0        | _      |        | RP1R5  | RP1R4  | RP1R3  | RP1R2  | RP1R1  | RP1R0  | _     |       | RP0R5  | RP0R4  | RP0R3  | RP0R2  | RP0R1  | RP0R0  | 0000          |

| RPOR1        | 06D2        | _      | _      | RP3R5  | RP3R4  | RP3R3  | RP3R2  | RP3R1  | RP3R0  | _     | _     | RP2R5  | RP2R4  | RP2R3  | RP2R2  | RP2R1  | RP2R0  | 0000          |

| RPOR2        | 06D4        | _      | _      | RP5R5  | RP5R4  | RP5R3  | RP5R2  | RP5R1  | RP5R0  | _     |       | RP4R5  | RP4R4  | RP4R3  | RP4R2  | RP4R1  | RP4R0  | 0000          |

| RPOR3        | 06D6        | _      | _      | RP7R5  | RP7R4  | RP7R3  | RP7R2  | RP7R1  | RP7R0  | _     |       | RP6R5  | RP6R4  | RP6R3  | RP6R2  | RP6R1  | RP6R0  | 0000          |

| RPOR4        | 06D8        | _      |        | RP9R5  | RP9R4  | RP9R3  | RP9R2  | RP9R1  | RP9R0  |       |       | RP8R5  | RP8R4  | RP8R3  | RP8R2  | RP8R1  | RP8R0  | 0000          |

| RPOR5        | 06DA        | _      |        | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |       |       | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 | 0000          |

| RPOR6        | 06DC        | _      |        | RP13R5 | RP13R4 | RP13R3 | RP13R2 | RP13R1 | RP13R0 |       |       | RP12R5 | RP12R4 | RP12R3 | RP12R2 | RP12R1 | RP12R0 | 0000          |

| RPOR7        | 06DE        |        | _      | RP15R5 | RP15R4 | RP15R3 | RP15R2 | RP15R1 | RP15R0 |       | _     | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 | 0000          |

| RPOR16       | 06F0        | _      | _      | RP33R5 | RP33R4 | RP33R3 | RP33R2 | RP33R1 | RP33R0 | _     |       | RP32R5 | RP32R4 | RP32R3 | RP32R2 | RP32R1 | RP32R0 | 0000          |

| RPOR17       | 06F2        | _      | _      | RP35R5 | RP35R4 | RP35R3 | RP35R2 | RP35R1 | RP35R0 | _     | _     | RP34R5 | RP34R4 | RP34R3 | RP34R2 | RP34R1 | RP34R0 | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### TABLE 4-36: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ16GS404 AND dsPIC33FJ16GS504

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| RPOR0        | 06D0        | _      |        | RP1R5  | RP1R4  | RP1R3  | RP1R2  | RP1R1  | RP1R0  | _     |       | RP0R5  | RP0R4  | RP0R3  | RP0R2  | RP0R1  | RP0R0  | 0000          |

| RPOR1        | 06D2        |        | _      | RP3R5  | RP3R4  | RP3R3  | RP3R2  | RP3R1  | RP3R0  |       | _     | RP2R5  | RP2R4  | RP2R3  | RP2R2  | RP2R1  | RP2R0  | 0000          |

| RPOR2        | 06D4        |        | _      | RP5R5  | RP5R4  | RP5R3  | RP5R2  | RP5R1  | RP5R0  |       | _     | RP4R5  | RP4R4  | RP4R3  | RP4R2  | RP4R1  | RP4R0  | 0000          |

| RPOR3        | 06D6        |        | _      | RP7R5  | RP7R4  | RP7R3  | RP7R2  | RP7R1  | RP7R0  |       | _     | RP6R5  | RP6R4  | RP6R3  | RP6R2  | RP6R1  | RP6R0  | 0000          |

| RPOR4        | 06D8        |        | _      | RP9R5  | RP9R4  | RP9R3  | RP9R2  | RP9R1  | RP9R0  |       | _     | RP8R5  | RP8R4  | RP8R3  | RP8R2  | RP8R1  | RP8R0  | 0000          |

| RPOR5        | 06DA        |        | _      | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |       | _     | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 | 0000          |

| RPOR6        | 06DC        |        | _      | RP13R5 | RP13R4 | RP13R3 | RP13R2 | RP13R1 | RP13R0 |       | _     | RP12R5 | RP12R4 | RP12R3 | RP12R2 | RP12R1 | RP12R0 | 0000          |

| RPOR7        | 06DE        |        | _      | RP15R5 | RP15R4 | RP15R3 | RP15R2 | RP15R1 | RP15R0 |       | _     | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 | 0000          |

| RPOR8        | 06E0        |        | _      | RP17R5 | RP17R4 | RP17R3 | RP17R2 | RP17R1 | RP17R0 |       | _     | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 | 0000          |

| RPOR9        | 06E2        |        | _      | RP19R5 | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |       | _     | RP18R5 | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 | 0000          |

| RPOR10       | 06E4        |        | _      | RP21R5 | RP21R4 | RP21R3 | RP21R2 | RP21R1 | RP21R0 |       | _     | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 | 0000          |

| RPOR11       | 06E6        |        | _      | RP23R5 | RP23R4 | RP23R3 | RP23R2 | RP23R1 | RP23R0 |       | _     | RP22R5 | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 | 0000          |

| RPOR12       | 06E8        |        | _      | RP25R5 | RP25R4 | RP25R3 | RP25R2 | RP25R1 | RP25R0 |       | _     | RP24R5 | RP24R4 | RP24R3 | RP24R2 | RP24R1 | RP24R0 | 0000          |

| RPOR13       | 06EA        |        | _      | RP27R5 | RP27R4 | RP27R3 | RP27R2 | RP27R1 | RP27R0 |       | _     | RP26R5 | RP26R4 | RP26R3 | RP26R2 | RP26R1 | RP26R0 | 0000          |

| RPOR14       | 06EC        | _      | -      | RP29R5 | RP29R4 | RP29R3 | RP29R2 | RP29R1 | RP29R0 | _     |       | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 | 0000          |

| RPOR16       | 06F0        | _      | _      | RP33R5 | RP33R4 | RP33R3 | RP33R2 | RP33R1 | RP33R0 | _     | _     | RP32R5 | RP32R4 | RP32R3 | RP32R2 | RP32R1 | RP32R0 | 0000          |

| RPOR17       | 06F2        | _      | _      | RP35R5 | RP35R4 | RP35R3 | RP35R2 | RP35R1 | RP35R0 | _     | _     | RP34R5 | RP34R4 | RP34R3 | RP34R2 | RP34R1 | RP34R0 | 0000          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### TABLE 4-41: SYSTEM CONTROL REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets       |

|--------------|-------------|--------|--------|---------|--------|--------|-----------|-----------|-----------|----------|----------|--------|----------|---------|---------|---------|---------|---------------------|

| RCON         | 0740        | TRAPR  | IOPUWR |         |        | _      |           | CM        | VREGS     | EXTR     | SWR      | SWDTEN | WDTO     | SLEEP   | IDLE    | BOR     | POR     | <sub>xxxx</sub> (1) |

| OSCCON       | 0742        | —      | COSC2  | COSC1   | COSC0  |        | NOSC2     | NOSC1     | NOSC0     | CLKLOCK  | IOLOCK   | LOCK   | _        | CF      |         |         | OSWEN   | 0300 <b>(2)</b>     |

| CLKDIV       | 0744        | ROI    | DOZE2  | DOZE1   | DOZE0  | DOZEN  | FRCDIV2   | FRCDIV1   | FRCDIV0   | PLLPOST1 | PLLPOST0 | _      | PLLPRE4  | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 3040                |

| PLLFBD       | 0746        | _      | —      | _       | _      | _      | —         | _         |           |          |          | PLLI   | OIV<8:0> |         |         |         |         | 0030                |

| REFOCON      | 074E        | ROON   | —      | ROSSLP  | ROSEL  | RODIV3 | RODIV2    | RODIV1    | RODIV0    | _        |          | _      | _        | _       |         |         | —       | 0000                |

| OSCTUN       | 0748        |        | —      |         | _      | -      |           | -         | -         | _        | -        |        |          | TUN<    | :5:0>   |         |         | 0000                |

| ACLKCON      | 0750        | ENAPLL | APLLCK | SELACLK | -      | _      | APSTSCLR2 | APSTSCLR1 | APSTSCLR0 | ASRCSEL  | FRCSEL   | _      | _        | _       | _       | _       | —       | 2300                |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The RCON register Reset values are dependent on the type of Reset.

2: The OSCCON register Reset values are dependent on the FOSCx Configuration bits and on type of Reset.

#### TABLE 4-42: NVM REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------|--------|--------|--------|---------------------|

| NVMCON       | 0760        | WR     | WREN   | WRERR  | —      | _      |        | —     | _     | _     | ERASE | _     |       | NVMOP3  | NVMOP2 | NVMOP1 | NVMOP0 | <sub>0000</sub> (1) |

| NVMKEY       | 0766        | _      | _      | _      | _      | _      |        | -     | _     |       |       |       | NVMKE | EY<7:0> |        |        |        | 0000                |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. The value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-43: PMD REGISTER MAP FOR dsPIC33FJ06GS101 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1         | 0770        | _      | —      | _      | T2MD   | T1MD   | _      | PWMMD | _      | I2C1MD | —     | U1MD  | _     | SPI1MD | —     | —     | ADCMD | 0000          |

| PMD2         | 0772        | _      | _      | _      | _      | _      | _      | IC2MD | IC1MD  | _      |       | _     | _     | -      | _     | OC2MD | OC1MD | 0000          |

| PMD3         | 0774        | —      |        |        | I      | -      | CMPMD  |       |        | _      | -     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4         | 0776        | _      | —      | _      | -      | _      | _      | _     | _      | —      | _     | —     | —     | REFOMD | —     | —     | _     | 0000          |

| PMD6         | 077A        | _      | -      | -      |        | PWM4MD | -      | -     | PWM1MD | _      | -     | _     | _     | -      | -     | _     | —     | 0000          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-44: PMD REGISTER MAP FOR dsPIC33FJ06GS102 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1         | 0770        | _      | —      | _      | T2MD   | T1MD   | —      | PWMMD  | _      | I2C1MD | _     | U1MD  | —     | SPI1MD |       | —     | ADCMD | 0000          |

| PMD2         | 0772        | Ι      | _      | _      | _      | _      | _      | IC2MD  | IC1MD  | _      | _     | _     | _     | _      | _     | OC2MD | OC1MD | 0000          |

| PMD3         | 0774        | Ι      | —      | —      | —      | —      | CMPMD  |        |        | -      |       | —     | —     | —      | _     | —     | -     | 0000          |

| PMD4         | 0776        | -      | —      | —      | —      | _      | —      | —      | _      | _      | —     | —     | _     | REFOMD | —     | —     | _     | 0000          |

| PMD6         | 077A        | _      | —      | _      | —      | —      | —      | PWM2MD | PWM1MD | _      | -     | _     | _     | _      | _     | -     | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000318G-page 71

### 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70192) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: Software RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), which is set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

#### FIGURE 6-1: **RESET SYSTEM BLOCK DIAGRAM RESET** Instruction Glitch Filter MCLR WDT Module Sleep or Idle BOR Internal SYSRST Regulator Vdd POR VDD Rise Detect Trap Conflict Illegal Opcode Uninitialized W Register Configuration Mismatch

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit |

|-------|----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                       |

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| U-0          | R/W-1                          | R/W-0                                      | R/W-0             | U-0             | R/W-1            | R/W-0           | R/W-0          |

|--------------|--------------------------------|--------------------------------------------|-------------------|-----------------|------------------|-----------------|----------------|

| _            | U1RXIP2                        | U1RXIP1                                    | U1RXIP0           | _               | SPI1IP2          | SPI1IP1         | SPI1IP0        |

| pit 15       |                                |                                            |                   |                 |                  | _               | bit            |

|              |                                | DAMO                                       | DAMO              |                 | <b>D</b> 444 4   | DAMA            | DAMO           |

| U-0          | R/W-1<br>SPI1EIP2              | R/W-0<br>SPI1EIP1                          | R/W-0<br>SPI1EIP0 | U-0             | R/W-1<br>T3IP2   | R/W-0<br>T3IP1  | R/W-0<br>T3IP0 |

| <br>bit 7    | 3FITEIF2                       | SFILEIFT                                   | SFILEIFU          | —               | TOIFZ            | ISIFI           | bit            |

| <u> </u>     |                                |                                            |                   |                 |                  |                 |                |

| Legend:      |                                |                                            |                   |                 |                  |                 |                |

| R = Readab   | le bit                         | W = Writable                               | bit               | U = Unimple     | mented bit, read | d as '0'        |                |

| -n = Value a | t POR                          | '1' = Bit is set                           | t                 | '0' = Bit is cl | eared            | x = Bit is unkr | nown           |

| bit 15       | Unimplomen                     | ted: Read as '                             | 0'                |                 |                  |                 |                |

| bit 14-12    | -                              | : UART1 Rec                                |                   | Priority bits   |                  |                 |                |

| 510 T T T 2  |                                | pt is Priority 7                           | •                 | •               |                  |                 |                |

|              | •                              |                                            |                   |                 |                  |                 |                |

|              | •                              |                                            |                   |                 |                  |                 |                |

|              | 001 = Interru                  | pt is Priority 1                           |                   |                 |                  |                 |                |

|              | 000 = Interru                  | pt source is dis                           | sabled            |                 |                  |                 |                |

| bit 11       | Unimplemen                     | ted: Read as '                             | 0'                |                 |                  |                 |                |

| bit 10-8     |                                | SPI1 Event Ir                              | • •               |                 |                  |                 |                |

|              | 111 = Interru                  | pt is Priority 7                           | (highest priorit  | y interrupt)    |                  |                 |                |

|              | •                              |                                            |                   |                 |                  |                 |                |

|              | •                              |                                            |                   |                 |                  |                 |                |

|              | 001 = Interru                  |                                            |                   |                 |                  |                 |                |

| bit 7        |                                | pt source is dis<br>t <b>ed:</b> Read as ' |                   |                 |                  |                 |                |

| bit 6-4      | =                              | >: SPI1 Error I                            |                   | hy hito         |                  |                 |                |

| DIL 0-4      |                                | pt is Priority 7                           |                   |                 |                  |                 |                |

|              | •                              | prior nonty r                              | (ingricor priorit | y monupi)       |                  |                 |                |

|              | •                              |                                            |                   |                 |                  |                 |                |

|              | •                              | nt in Driarity 1                           |                   |                 |                  |                 |                |

|              | 001 = Interru<br>000 = Interru | pt is Phonity 1<br>pt source is dis        | sabled            |                 |                  |                 |                |

| bit 3        |                                | ted: Read as                               |                   |                 |                  |                 |                |

| bit 2-0      | -                              | imer3 Interrupt                            |                   |                 |                  |                 |                |

|              |                                | pt is Priority 7                           | -                 | y interrupt)    |                  |                 |                |

|              | •                              |                                            |                   |                 |                  |                 |                |

|              | •                              |                                            |                   |                 |                  |                 |                |

|              |                                |                                            |                   |                 |                  |                 |                |

|              | 001 = Interru                  | pt is Priority 1                           |                   |                 |                  |                 |                |

#### IDC2. INTERDURT PRIORITY CONTROL RECISTER 2

| U-0    | U-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|------|--------|--------|--------|--------|--------|--------|

|        | —    | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |      |        |        |        |        |        | bit 8  |

|        |      |        |        |        |        |        |        |

| 11.0   | 11.0 |        |        |        |        |        |        |

### REGISTER 10-20: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5<sup>(1)</sup>

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP11R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP10R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is not implemented in the dsPIC33FJ06GS101 device.

| U-0         | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0           | R/W-0  | R/W-0  |

|-------------|-----|--------|--------|--------|-----------------|--------|--------|

| —           | —   | RP13R5 | RP13R4 | RP13R3 | RP13R2          | RP13R1 | RP13R0 |

| bit 15      |     |        |        |        |                 |        | bit 8  |

|             |     |        |        |        |                 |        |        |

| U-0         | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0           | R/W-0  | R/W-0  |

| —           | —   | RP12R5 | RP12R4 | RP12R3 | RP12R2          | RP12R1 | RP12R0 |

| bit 7       |     |        |        |        |                 |        | bit 0  |

|             |     |        |        |        |                 |        |        |

| Legend:     |     |        |        |        |                 |        |        |

| D Doodoblob | :+  |        | h:+    |        | nonted hit read | oo 'O' |        |

### **REGISTER 10-21:** RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6<sup>(1)</sup>

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP13R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP13 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP12R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP12 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is not implemented in the dsPIC33FJ06GS101 device.

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0   | U-0          | U-0   |

|--------|-----|-----|-----|-----|-------|--------------|-------|

| —      | —   | —   | —   | —   | —     | —            | —     |

| bit 15 | -   |     |     |     |       | •            | bit 8 |

|        |     |     |     |     |       |              |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0        | R/W-0 |

| _      | —   | —   | _   | _   | P     | CLKDIV<2:0>( | 1)    |

| bit 7  |     |     | •   |     |       |              | bit 0 |

|        |     |     |     |     |       |              |       |

#### REGISTER 15-2: PTCON2: PWM CLOCK DIVIDER SELECT REGISTER

## Γ.

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

- bit 2-0 PCLKDIV<2:0>: PWM Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64, maximum PWM timing resolution

- 101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

- Note 1: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will vield unpredictable results.

#### REGISTER 15-3: PTPER: PWM MASTER TIME BASE REGISTER<sup>(1)</sup>

| R/W-1                                                                  | R/W-1 | R/W-1 | R/W-1                              | R/W-1    | R/W-1 | R/W-1 | R/W-1 |

|------------------------------------------------------------------------|-------|-------|------------------------------------|----------|-------|-------|-------|

|                                                                        |       |       | PTPE                               | R <15:8> |       |       |       |

| bit 15                                                                 |       |       |                                    |          |       |       | bit 8 |

| R/W-1                                                                  | R/W-1 | R/W-1 | R/W-1                              | R/W-1    | R/W-0 | R/W-0 | R/W-0 |

|                                                                        |       |       | PTPE                               | R <7:0>  |       |       |       |

| bit 7                                                                  |       |       |                                    |          |       |       | bit 0 |

| Legend:                                                                |       |       |                                    |          |       |       |       |

| R = Readable bit $W = Writable bit$                                    |       | bit   | U = Unimplemented bit, read as '0' |          |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk |       |       | nown                               |          |       |       |       |

#### bit 15-0 PTPER<15:0>: PWM Master Time Base (PMTMR) Period Value bits

Note 1: The minimum value that can be loaded into the PTPER register is 0x0010 and the maximum value is 0xFFF8.

## 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CxSTAT are read/write:

- I2CxRSR is the shift register used for shifting data internal to the module and the user application has no access to it

- I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- The I2CxADD register holds the slave address

- A status bit, ADD10, indicates 10-Bit Addressing mode

- The I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV, and an interrupt pulse is generated.

| R/W-0           | U-0                                                                                                                                                                                        | R/W-0                                | R/W-1, HC      | R/W-0             | R/W-0                          | R/W-0               | R/W-0           |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|--------------------------------|---------------------|-----------------|--|--|--|--|

| I2CEN           | —                                                                                                                                                                                          | I2CSIDL                              | SCLREL         | IPMIEN            | A10M                           | DISSLW              | SMEN            |  |  |  |  |

| bit 15          |                                                                                                                                                                                            |                                      |                |                   |                                |                     | bit 8           |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                                                      | R/W-0                                | R/W-0, HC      | R/W-0, HC         | R/W-0, HC                      | R/W-0, HC           | R/W-0, HC       |  |  |  |  |

| GCEN            | STREN                                                                                                                                                                                      | ACKDT                                | ACKEN          | RCEN              | PEN                            | RSEN                | SEN             |  |  |  |  |

| bit 7           |                                                                                                                                                                                            |                                      |                |                   |                                |                     | bit (           |  |  |  |  |

| Legend:         |                                                                                                                                                                                            |                                      | mented bit, re | ad as 'O'         |                                |                     |                 |  |  |  |  |

| R = Readable    | hit                                                                                                                                                                                        | W = Writable                         |                |                   | re Clearable bit               |                     |                 |  |  |  |  |

| -n = Value at F |                                                                                                                                                                                            | (1) = Bit is set                     |                | 0' = Bit is clear |                                | x = Bit is unkno    | nwn             |  |  |  |  |

|                 |                                                                                                                                                                                            |                                      |                |                   |                                |                     |                 |  |  |  |  |

| bit 15          | 12CEN · 120                                                                                                                                                                                | Cx Enable bit                        |                |                   |                                |                     |                 |  |  |  |  |

|                 |                                                                                                                                                                                            |                                      | odule, and cor | nfigures the SE   | Ax and SCLx pir                | ns as serial port r | oins            |  |  |  |  |

|                 |                                                                                                                                                                                            |                                      |                |                   | trolled by port fur            |                     |                 |  |  |  |  |

| bit 14          | Unimplem                                                                                                                                                                                   | ented: Read                          | <b>as</b> '0'  |                   |                                |                     |                 |  |  |  |  |

| bit 13          | I2CSIDL:                                                                                                                                                                                   | 2Cx Stop in Ic                       | lle Mode bit   |                   |                                |                     |                 |  |  |  |  |

|                 |                                                                                                                                                                                            | tinues module<br>ues module o        | •              |                   | ers an Idle mode               |                     |                 |  |  |  |  |

| bit 12          | SCLREL: SCLx Release Control bit (when operating as I <sup>2</sup> C slave)                                                                                                                |                                      |                |                   |                                |                     |                 |  |  |  |  |

|                 | 1 = Releases SCLx clock<br>0 = Holds SCLx clock low (clock stretch)                                                                                                                        |                                      |                |                   |                                |                     |                 |  |  |  |  |

|                 | If STREN = 1:                                                                                                                                                                              |                                      |                |                   |                                |                     |                 |  |  |  |  |

|                 | Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception. |                                      |                |                   |                                |                     |                 |  |  |  |  |

|                 | -                                                                                                                                                                                          | -                                    | nsmission. Ha  | ardware clear a   | it end of slave red            | ception.            |                 |  |  |  |  |

|                 | If STREN =                                                                                                                                                                                 |                                      | can only wri   | te '1' to releas  | se clock). Hardw               | are clear at heri   | nning of slav   |  |  |  |  |

|                 | transmissi                                                                                                                                                                                 | •                                    |                |                   |                                | are clear at begi   | Thing of Slav   |  |  |  |  |

| bit 11          | IPMIEN: Ir                                                                                                                                                                                 | ntelligent Perip                     | heral Manage   | ement Interface   | e (IPMI) Enable b              | bit                 |                 |  |  |  |  |

|                 | 1 = IPMI m                                                                                                                                                                                 | node is enable                       | d; all address | es are Acknow     | . ,                            |                     |                 |  |  |  |  |

| h:+ 40          |                                                                                                                                                                                            | node is disable                      |                |                   |                                |                     |                 |  |  |  |  |

| bit 10          |                                                                                                                                                                                            | Bit Slave Add                        |                | _                 |                                |                     |                 |  |  |  |  |

|                 | 1 = I2CxADD is a 10-bit slave address<br>0 = I2CxADD is a 7-bit slave address                                                                                                              |                                      |                |                   |                                |                     |                 |  |  |  |  |

| bit 9           |                                                                                                                                                                                            | Disable Slew F                       |                | bit               |                                |                     |                 |  |  |  |  |

|                 |                                                                                                                                                                                            | ate control is o<br>ate control is e |                |                   |                                |                     |                 |  |  |  |  |

| bit 8           |                                                                                                                                                                                            |                                      |                |                   |                                |                     |                 |  |  |  |  |

| bit 0           | SMEN: SMBus Input Levels bit                                                                                                                                                               |                                      |                |                   |                                |                     |                 |  |  |  |  |

|                 | <ol> <li>Enables I/O pin thresholds compliant with SMBus specification</li> <li>Disables SMBus input thresholds</li> </ol>                                                                 |                                      |                |                   |                                |                     |                 |  |  |  |  |

| bit 7           | GCEN: Ge                                                                                                                                                                                   | eneral Call Ena                      | able bit (when | operating as I    | <sup>2</sup> C slave)          |                     |                 |  |  |  |  |

|                 | 1 = Enable<br>recept                                                                                                                                                                       | -                                    | nen a general  | call address is   | received in the la             | 2CxRSR (module      | e is enabled fo |  |  |  |  |

|                 |                                                                                                                                                                                            | al call addres                       | s is disabled  |                   |                                |                     |                 |  |  |  |  |

| bit 6           | STREN: S                                                                                                                                                                                   | CLx Clock Str                        | etch Enable b  | oit (when opera   | ting as I <sup>2</sup> C slave | )                   |                 |  |  |  |  |

|                 |                                                                                                                                                                                            | njunction with                       |                |                   |                                |                     |                 |  |  |  |  |

|                 |                                                                                                                                                                                            | es software or                       |                | -                 |                                |                     |                 |  |  |  |  |

|                 | v = v sable                                                                                                                                                                                | es software or                       | receive clock  | stretching        |                                |                     |                 |  |  |  |  |

#### REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

| R-0, HSC     | R-0, HSC                     | U-0                            | U-0             | U-0                          | R/C-0, HSC         | R-0, HSC                              | R-0, HSC        |

|--------------|------------------------------|--------------------------------|-----------------|------------------------------|--------------------|---------------------------------------|-----------------|

| ACKSTAT      | TRSTAT                       | _                              |                 | —                            | BCL                | GCSTAT                                | ADD10           |

| bit 15       |                              |                                |                 |                              |                    |                                       | bit 8           |

|              |                              |                                |                 |                              |                    |                                       |                 |

| R/C-0, HS    | R/C-0, HS                    | R-0, HSC                       | R/C-0, HSC      | R/C-0, HSC                   | R-0, HSC           | R-0, HSC                              | R-0, HSC        |

| IWCOL        | I2COV                        | D_A                            | Р               | S                            | R_W                | RBF                                   | TBF             |

| bit 7        |                              |                                |                 |                              |                    |                                       | bit 0           |

|              |                              |                                |                 |                              |                    |                                       |                 |

| Legend:      |                              | C = Clearab                    | ole bit         | HSC = Hardw                  | vare Settable/C    | learable bit                          |                 |

| R = Readab   | le bit                       | W = Writabl                    | e bit           | U = Unimpler                 | nented bit, read   | l as '0'                              |                 |

| -n = Value a | It POR                       | '1' = Bit is s                 | et              | '0' = Bit is cle             | ared               | x = Bit is unknown                    | n               |

| HS = Hardw   | are Settable                 | bit                            |                 |                              |                    |                                       |                 |

| bit 15       | ACKSTAT:                     | Acknowledge                    | e Status bit    |                              |                    |                                       |                 |

|              |                              |                                |                 | licable to mas               | ter transmit ope   | eration)                              |                 |

|              |                              | eceived from                   |                 |                              |                    |                                       |                 |

|              |                              | ceived from s                  |                 | ve Acknowledg                | ie                 |                                       |                 |

| bit 14       |                              |                                |                 |                              |                    | able to master tran                   | smit operation) |

|              |                              |                                | progress (8 k   | -                            |                    |                                       | onne oporation) |

|              |                              |                                | ot in progress  | ,                            |                    |                                       |                 |

|              | Hardware is                  | s set at begin                 | ning of maste   | er transmissior              | . Hardware is c    | lear at end of slave                  | e Acknowledge.  |

| bit 13-11    | Unimpleme                    | ented: Read                    | <b>as</b> '0'   |                              |                    |                                       |                 |

| bit 10       |                              | er Bus Collisio                |                 |                              |                    |                                       |                 |

|              |                              |                                | een detected    | l during a mas               | ter operation      |                                       |                 |

|              | 0 = No collis<br>Hardware is |                                | tion of bus co  | Ilision                      |                    |                                       |                 |

| bit 9        |                              | eneral Call S                  |                 |                              |                    |                                       |                 |

| Sit 0        |                              |                                | was receive     | d                            |                    |                                       |                 |

|              |                              |                                | was not rece    |                              |                    |                                       |                 |

|              | Hardware is                  | s set when ac                  | dress match     | es general call              | address. Hard      | ware is clear at Sto                  | p detection.    |

| bit 8        |                              | -Bit Address                   |                 |                              |                    |                                       |                 |

|              |                              | ddress was n                   |                 |                              |                    |                                       |                 |

|              |                              | ddress was r<br>s set at match |                 | of matched 10                | -bit address Ha    | ardware is clear at                   | Stop detection  |

| bit 7        |                              |                                | sion Detect b   |                              |                    |                                       |                 |

|              |                              |                                |                 |                              | d because the      | I <sup>2</sup> C module is busy       | ,               |

|              | 0 = No collis                |                                |                 | - 9                          |                    | · · · · · · · · · · · · · · · · · · · |                 |

|              | Hardware is                  | s set at occur                 | rence of write  | e to I2CxTRN                 | while busy (clea   | red by software).                     |                 |

| bit 6        |                              |                                | /erflow Flag b  |                              |                    |                                       |                 |

|              | -                            |                                | while the I2C   | xRCV register                | is still holding t | the previous byte                     |                 |

|              | 0 = No over<br>Hardware is   |                                | nt to transfer  | 12CxRSR to 12                | CxRCV (cleare      | ed by software).                      |                 |

| bit 5        |                              |                                | •               | ng as I <sup>2</sup> C slave |                    | a by converg.                         |                 |

|              | _                            | · ·                            | st byte receive | 0                            | ~/                 |                                       |                 |

|              | 0 = Indicate                 | s that the las                 | t byte receive  | ed was a devid               |                    |                                       |                 |

|              | Hardware is                  | s clear at dev                 | ice address n   | natch. Hardwa                | re is set by rece  | eption of slave byte                  | <b>)</b> .      |

|              |                              |                                |                 |                              |                    |                                       |                 |

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| U-0               | U-0   | U-0              | U-0   | U-0                                | U-0       | R/W-0              | R/W-0 |  |

|-------------------|-------|------------------|-------|------------------------------------|-----------|--------------------|-------|--|

|                   |       | _                |       |                                    | AMSK<9:8> |                    |       |  |

| bit 15            | ·     |                  |       | ·                                  |           |                    | bit 8 |  |

|                   |       |                  |       |                                    |           |                    |       |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0     | R/W-0              | R/W-0 |  |

|                   |       |                  | AMS   | K<7:0>                             |           |                    |       |  |

| bit 7 bit         |       |                  |       |                                    |           |                    |       |  |

|                   |       |                  |       |                                    |           |                    |       |  |

| Legend:           |       |                  |       |                                    |           |                    |       |  |

| R = Readable bit  |       | W = Writable     | bit   | U = Unimplemented bit, read as '0' |           |                    |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cle                   | eared     | x = Bit is unknown |       |  |

### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Mask for Address bit x Select bits

1 = Enables masking for bit x of incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

| DC CHARACTERISTICS                 |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                       |      |                    |     |       |                         |  |

|------------------------------------|------|-----------------------------------------------------------------------------|------|--------------------|-----|-------|-------------------------|--|

| Param<br>No. Symbol Characteristic |      | Characteristic                                                              | Min  | Typ <sup>(1)</sup> | Max | Units | Conditions              |  |

| Operating Voltage                  |      |                                                                             |      |                    |     |       |                         |  |

| DC10                               | Vdd  | Supply Voltage <sup>(4)</sup>                                               | 3.0  | _                  | 3.6 | V     | Industrial and Extended |  |

| DC12                               | Vdr  | RAM Data Retention Voltage <sup>(2)</sup>                                   | 1.8  | _                  | _   | V     |                         |  |

| DC16                               | VPOR | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal            | _    | _                  | Vss | V     |                         |  |

| DC17                               | SVDD | VDD Rise Rate <sup>(3)</sup><br>to Ensure Internal<br>Power-on Reset Signal | 0.03 | —                  |     | V/ms  | 0V-3.0V in 0.1 seconds  |  |

## TABLE 24-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: This is the limit to which VDD may be lowered without losing RAM data.

3: These parameters are characterized but not tested in manufacturing.

**4:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 24-11 for BOR values.