Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 6KB (6K × 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the ADPCFG register.

The bits in the registers that correspond to the A/D pins that are initialized by MPLAB ICD 2, ICD 3, or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the ADPCFG register during initialization of the ADC module.

When MPLAB ICD 2, ICD 3, or REAL ICE is used as a programmer, the user application firmware must correctly configure the ADPCFG register. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins and drive the output to logic low.

## 2.10 Typical Application Connection Examples

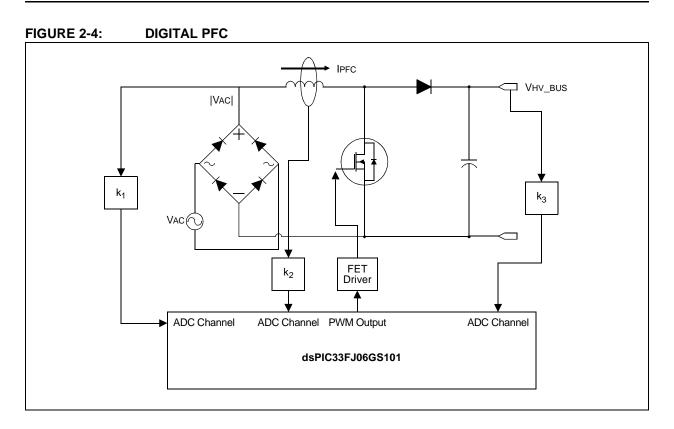

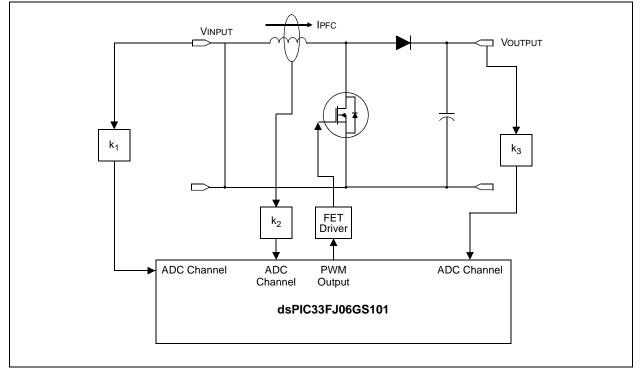

Examples of typical application connections are shown in Figure 2-4 through Figure 2-11.

## dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

#### 6.8.2 UNINITIALIZED W REGISTER RESET

Any attempt to use the Uninitialized W register as an Address Pointer will reset the device. The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to.

#### 6.8.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (boot and secure segment), that operation will cause a Security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a call, jump, computed jump, return, return from subroutine or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an interrupt or trap vector.

Refer to Section 21.8 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

## 6.9 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the Reset.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

Table 6-3 provides a summary of the Reset flag bit operation.

| Flag Bit            | Set by:                                                             | Cleared by:                                      |

|---------------------|---------------------------------------------------------------------|--------------------------------------------------|

| TRAPR (RCON<15>)    | Trap conflict event                                                 | POR, BOR                                         |

| IOPWR (RCON<14>)    | Illegal opcode or Uninitialized W register access or Security Reset | POR, BOR                                         |

| <b>CM</b> (RCON<9>) | Configuration Mismatch                                              | POR, BOR                                         |

| EXTR (RCON<7>)      | MCLR Reset                                                          | POR                                              |

| SWR (RCON<6>)       | RESET instruction                                                   | POR, BOR                                         |

| WDTO (RCON<4>)      | WDT time-out                                                        | PWRSAV instruction, CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)     | PWRSAV #SLEEP instruction                                           | POR, BOR                                         |

| IDLE (RCON<2>)      | PWRSAV #IDLE instruction                                            | POR, BOR                                         |

| BOR (RCON<1>)       | POR, BOR                                                            | —                                                |

| POR (RCON<0>)       | POR                                                                 | _                                                |

#### TABLE 6-3: RESET FLAG BIT OPERATION

Note: All Reset flag bits can be set or cleared by user software.

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| R/W-0           | R/W-0                                                                                          | U-0                               | U-0            | U-0               | U-0             | R/W-0           | R/W-0  |  |

|-----------------|------------------------------------------------------------------------------------------------|-----------------------------------|----------------|-------------------|-----------------|-----------------|--------|--|

| ADCP1IE         | ADCP0IE                                                                                        | —                                 | —              | —                 | _               | AC4IE           | AC3IE  |  |

| bit 15          |                                                                                                |                                   |                |                   |                 |                 | bit    |  |

| R/W-0           | U-0                                                                                            | U-0                               | U-0            | U-0               | U-0             | R/W-0           | R/W-0  |  |

| AC2IE           |                                                                                                | _                                 | _              |                   | _               | PWM4IE          | PWM3IE |  |

| bit 7           |                                                                                                |                                   |                |                   |                 |                 | bit (  |  |

| Legend:         |                                                                                                |                                   |                |                   |                 |                 |        |  |

| R = Readable    | bit                                                                                            | W = Writable                      | bit            | U = Unimplem      | nented bit. rea | d as '0'        |        |  |

| -n = Value at F | POR                                                                                            | '1' = Bit is set                  |                | '0' = Bit is clea |                 | x = Bit is unkr | iown   |  |

|                 |                                                                                                |                                   |                |                   |                 |                 |        |  |

| bit 15          | ADCP1IE: AD                                                                                    | DC Pair 1 Conv                    | ersion Done    | Interrupt Enable  | e bit           |                 |        |  |

|                 |                                                                                                | equest is enab                    |                |                   |                 |                 |        |  |

|                 |                                                                                                | request is not e                  |                |                   |                 |                 |        |  |

| bit 14          |                                                                                                |                                   |                | Interrupt Enable  | bit             |                 |        |  |

|                 | •                                                                                              | equest is enab<br>equest is not e |                |                   |                 |                 |        |  |

| bit 13-10       | •                                                                                              | ted: Read as '                    |                |                   |                 |                 |        |  |

| bit 9           | -                                                                                              | g Comparator                      |                | able bit          |                 |                 |        |  |

|                 |                                                                                                | equest is enab                    |                |                   |                 |                 |        |  |

|                 |                                                                                                | equest is not e                   |                |                   |                 |                 |        |  |

| bit 8           | AC3IE: Analo                                                                                   | g Comparator                      | 3 Interrupt Er | nable bit         |                 |                 |        |  |

|                 |                                                                                                | equest is enab                    |                |                   |                 |                 |        |  |

|                 |                                                                                                | equest is not e                   |                |                   |                 |                 |        |  |

| bit 7           |                                                                                                | g Comparator                      | •              | hable bit         |                 |                 |        |  |

|                 | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |                                   |                |                   |                 |                 |        |  |

| bit 6-2         | •                                                                                              | ted: Read as '                    |                |                   |                 |                 |        |  |

| bit 1           | -                                                                                              | PWM4IE: PWM4 Interrupt Enable bit |                |                   |                 |                 |        |  |

|                 |                                                                                                | equest is enab                    |                |                   |                 |                 |        |  |

|                 | •                                                                                              | equest is not e                   |                |                   |                 |                 |        |  |

| bit 0           | PWM3IE: PW                                                                                     | /M3 Interrupt E                   | nable bit      |                   |                 |                 |        |  |

|                 |                                                                                                | equest is enab                    |                |                   |                 |                 |        |  |

## REGISTER 7-17: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

## 8.2 Auxiliary Clock Generation

The auxiliary clock generation is used for a peripherals that need to operate at a frequency unrelated to the system clock such as a PWM or ADC.

The primary oscillator and internal FRC oscillator sources can be used with an auxiliary PLL to obtain the auxiliary clock. The auxiliary PLL has a fixed 16x multiplication factor.

The auxiliary clock has the following configuration restrictions:

- For proper PWM operation, auxiliary clock generation must be configured for 120 MHz (see Parameter OS56 in Table 24-18 in Section 24.0 "Electrical Characteristics"). If a slower frequency is desired, the PWM Input Clock Prescaler (Divider) Select bits (PCLKDIV<2:0>) should be used.

- To achieve 1.04 ns PWM resolution, the auxiliary clock must use the 16x auxiliary PLL (APLL). All other clock sources will have a minimum PWM resolution of 8 ns.

- If the primary PLL is used as a source for the auxiliary clock, the primary PLL should be configured up to a maximum operation of 30 MIPS or less

### 8.3 Reference Clock Generation

The reference clock output logic provides the user with the ability to output a clock signal based on the system clock or the crystal oscillator on a device pin. The user application can specify a wide range of clock scaling prior to outputting the reference clock.

## 8.4 Oscillator Control Registers

## **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,2)</sup>

| U-0     | R-0    | R-0   | R-0   | U-0   | R/W-y                | R/W-y                | R/W-y                |

|---------|--------|-------|-------|-------|----------------------|----------------------|----------------------|

| —       | COSC2  | COSC1 | COSC0 | —     | NOSC2 <sup>(3)</sup> | NOSC1 <sup>(3)</sup> | NOSC0 <sup>(3)</sup> |

| bit 15  |        |       |       |       |                      |                      | bit 8                |

|         |        |       |       |       |                      |                      |                      |

| R/W-0   | R/W-0  | R-0   | U-0   | R/C-0 | U-0                  | U-0                  | R/W-0                |

| CLKLOCK | IOLOCK | LOCK  | —     | CF    | _                    | —                    | OSWEN                |

| bit 7   |        |       |       |       |                      |                      | bit 0                |

| Legend:           | y = Value set from Configuration bits on POR |                       |                    |  |  |

|-------------------|----------------------------------------------|-----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit | t, read as '0'     |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared  | x = Bit is unknown |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits (read-only)                                                                                                                                                                                                                                                                    |

|           | <pre>111 = Fast RC oscillator (FRC) with divide-by-n 110 = Fast RC oscillator (FRC) with divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Reserved 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL 000 = Fast RC oscillator (FRC)</pre> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(3)</sup>                                                                                                                                                                                                                                                                     |

|           | <pre>111 = Fast RC oscillator (FRC) with divide-by-n 110 = Fast RC oscillator (FRC) with divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Reserved 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL</pre>                                |

|           | 000 = Fast RC oscillator (FRC)                                                                                                                                                                                                                                                                                              |

| bit 7     | CLKLOCK: Clock Lock Enable bit                                                                                                                                                                                                                                                                                              |

|           | <pre>If Clock Switching is Enabled and FSCM is Disabled, (FOSC<fcksm> = 0b01): 1 = Clock switching is disabled, system clock source is locked 0 = Clock switching is enabled, system clock source can be modified by clock switching</fcksm></pre>                                                                          |

| bit 6     | IOLOCK: Peripheral Pin Select Lock bit                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Peripheral Pin Select is locked, write to Peripheral Pin Select registers not allowed</li> <li>0 = Peripheral Pin Select is not locked, write to Peripheral Pin Select registers allowed</li> </ul>                                                                                                            |

| bit 5     | LOCK: PLL Lock Status bit (read-only)                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Indicates that PLL is in lock, or PLL start-up timer is satisfied</li> <li>0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled</li> </ul>                                                                                                                                  |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

| Note 1:   | Writes to this register require an unlock sequence. Refer to " <b>Oscillator (Part IV)</b> " (DS70307) in the<br>"dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.                                                                                                             |

| 2:        | This register is reset only on a Power-on Reset (POR).                                                                                                                                                                                                                                                                      |

| 3:        | Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.<br>This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.                                            |

mode as a transition clock source between the two PLL modes.

## **10.6** Peripheral Pin Select

Peripheral Pin Select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 10.6.1 AVAILABLE PINS

The Peripheral Pin Select feature is used with a range of up to 30 pins. The number of available pins depends on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

#### 10.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and another one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 10.6.2.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-14). Each register contains sets of 6-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

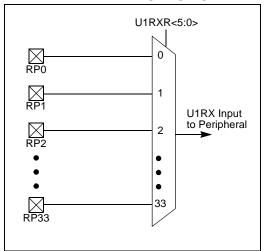

Figure 10-2 Illustrates remappable pin selection for U1RX input.

Note: For input mapping only, the Peripheral Pin Select (PPS) functionality does not have priority over the TRISx settings. Therefore, when configuring the RPx pin for input, the corresponding bit in the TRISx register must also be configured for input (i.e., set to '1').

#### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

| U-0                         | U-0                         | U-0              | U-0           | U-0                                | U-0            | U-0                | U-0   |

|-----------------------------|-----------------------------|------------------|---------------|------------------------------------|----------------|--------------------|-------|

| —                           | —                           | _                | —             |                                    | —              | —                  | —     |

| bit 15                      |                             |                  |               |                                    |                |                    | bit 8 |

|                             |                             |                  |               |                                    |                |                    |       |

| U-0                         | U-0                         | R/W-1            | R/W-1         | R/W-1                              | R/W-1          | R/W-1              | R/W-1 |

| _                           | _                           | SS1R5            | SS1R4         | SS1R3                              | SS1R2          | SS1R1              | SS1R0 |

| bit 7                       |                             |                  |               |                                    |                |                    | bit 0 |

|                             |                             |                  |               |                                    |                |                    |       |

| Legend:                     |                             |                  |               |                                    |                |                    |       |

| R = Readat                  | ole bit                     | W = Writable bit |               | U = Unimplemented bit, read as '0' |                |                    |       |

| -n = Value a                | at POR                      | '1' = Bit is set |               | '0' = Bit is cleared               |                | x = Bit is unknown |       |

|                             |                             |                  |               |                                    |                |                    |       |

| bit 15-6                    | Unimplemen                  | ted: Read as '   | 0'            |                                    |                |                    |       |

| bit 5-0                     | SS1R<5:0>:                  | Assign SPI1 SI   | ave Select In | put (SS1IN) to                     | the Correspond | ing RPn Pin bit    | S     |

|                             | 111111 = Inp                | out tied to Vss  |               |                                    |                |                    |       |

|                             | 100011 = Inp                | out tied to RP35 | 5             |                                    |                |                    |       |

|                             | 100010 = Input tied to RP34 |                  |               |                                    |                |                    |       |

| 100001 = Input tied to RP33 |                             | 3                |               |                                    |                |                    |       |

| 100000 = Input tied to RP32 |                             | 2                |               |                                    |                |                    |       |

|                             | •                           |                  |               |                                    |                |                    |       |

|                             | •                           |                  |               |                                    |                |                    |       |

|                             | •                           |                  |               |                                    |                |                    |       |

|                             | 00000 1000                  |                  |               |                                    |                |                    |       |

## REGISTER 10-8: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

00000 = Input tied to RP0

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| HS/HC-0      | ) HS/HC-0                | HS/HC-0                                       | R/W-0                        | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

|--------------|--------------------------|-----------------------------------------------|------------------------------|------------------|----------------------|----------------------|---------------------|

| FLTSTAT(     | 1) CLSTAT <sup>(1)</sup> | TRGSTAT                                       | FLTIEN                       | CLIEN            | TRGIEN               | ITB <sup>(3)</sup>   | MDCS <sup>(3)</sup> |

| bit 15       | ł                        |                                               |                              |                  |                      |                      | bit 8               |

|              |                          |                                               |                              |                  |                      |                      |                     |

| R/W-0        | R/W-0                    | U-0                                           | U-0                          | U-0              | R/W-0                | R/W-0                | R/W-0               |

| DTC1         | DTC0                     | —                                             | —                            |                  | CAM <sup>(2,3)</sup> | XPRES <sup>(4)</sup> | IUE                 |

| bit 7        |                          |                                               |                              |                  |                      |                      | bit                 |

| Legend:      |                          | HC = Hardware                                 | Clearable bit                | HS = Hardw       | are Settable bi      | it                   |                     |

| R = Readal   | hle hit                  | W = Writable bit                              |                              |                  | mented bit, rea      |                      |                     |

| -n = Value a |                          | '1' = Bit is set                              |                              | '0' = Bit is cle |                      | x = Bit is unl       | nown                |

|              |                          | 1 – Dit 13 Set                                |                              |                  | caleu                |                      | NIOWI               |

| bit 15       | FLTSTAT: F               | ault Interrupt Statu                          | us bit <sup>(1)</sup>        |                  |                      |                      |                     |

|              |                          | rrupt is pending                              |                              |                  |                      |                      |                     |

|              |                          | interrupt is pendin                           | g; this bit is cle           | ared by setting  | FLTIEN = 0           |                      |                     |

| bit 14       | CLSTAT: Cu               | urrent-Limit Interru                          | pt Status bit <sup>(1)</sup> |                  |                      |                      |                     |

|              |                          | mit interrupt is per<br>nt-limit interrupt is | Q                            | t is cleared by  | setting CLIEN        | = 0                  |                     |

| bit 13       | TRGSTAT: Tr              | rigger Interrupt Sta                          | itus bit                     |                  |                      |                      |                     |

|              |                          | terrupt is pending                            |                              |                  |                      |                      |                     |

|              | 0 = No trigge            | r interrupt is pendi                          | ng; this bit is cl           | eared by settin  | g TRGIEN = 0         | )                    |                     |

| bit 12       | FLTIEN: Fai              | ult Interrupt Enable                          | e bit                        |                  |                      |                      |                     |

|              |                          | rrupt is enabled                              |                              |                  |                      |                      |                     |

|              |                          | rrupt is disabled a                           |                              | T bit is cleared |                      |                      |                     |

| bit 11       |                          | CLIEN: Current-Limit Interrupt Enable bit     |                              |                  |                      |                      |                     |

|              |                          | mit interrupt is ena<br>mit interrupt is dis  |                              | CLSTAT bit is c  | leared               |                      |                     |

| bit 10       | TRGIEN: Trig             | ger Interrupt Enat                            | ole bit                      |                  |                      |                      |                     |

|              |                          | event generates a<br>vent interrupts are      |                              |                  | it is cleared        |                      |                     |

| bit 9        | ITB: Indepe              | ndent Time Base I                             | Mode bit <sup>(3)</sup>      |                  |                      |                      |                     |

|              | 1 = PHASEx/              | /SPHASEx registe<br>egister provides tir      | r provides time              |                  | r this PWM ge        | enerator             |                     |

| bit 8        |                          | ster Duty Cycle Re                            | -                            |                  |                      |                      |                     |

|              |                          | ister provides duty<br>Cx register provid     |                              |                  |                      | erator               |                     |

| bit 7-6      |                          | ead-Time Control                              |                              |                  | lie i till gene      |                      |                     |

|              | 11 = Reserve             |                                               | 513                          |                  |                      |                      |                     |

|              |                          | ne function is disa                           | bled                         |                  |                      |                      |                     |

|              |                          | e dead time is acti<br>dead time is activ     |                              |                  |                      |                      |                     |

| bit 5-3      |                          | ited: Read as '0'                             | - ,                          |                  |                      |                      |                     |

| Note 1:      | Software must clo        | ar the interrupt sta                          | tue here and th              | e correspondir   | a IFSy hit in t      | he interrupt or      | ontroller           |

| 2:           |                          | Time Base mode (                              |                              |                  | -                    | -                    |                     |

| 3:           | -                        | be changed only v                             | when PTEN = 0                | . Changing the   | e clock selectio     | on during ope        | ration will         |

|              |                          | real Dariad Deast                             | modo confirm                 |                  |                      |                      |                     |

#### REGISTER 15-6: PWMCONx: PWMx CONTROL REGISTER

4: To operate in External Period Reset mode, configure FCLCONx<CLMOD> = 0 and PWMCONx<ITB> = 1.

#### REGISTER 15-6: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 2 | <b>CAM:</b> Center-Aligned Mode Enable bit <sup>(2,3)</sup> |  |

|-------|-------------------------------------------------------------|--|

|       | 1 = Center-Aligned mode is enabled                          |  |

|       | 0 = Center-Aligned mode is disabled                         |  |

|       |                                                             |  |

- bit 1 **XPRES:** External PWM Reset Control bit<sup>(4)</sup>

- 1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base (ITB) mode

- 0 = External pins do not affect PWM time base

- bit 0 IUE: Immediate Update Enable bit

- 1 = Updates to the active MDC/PDCx/SDCx registers are immediate

- 0 = Updates to the active MDC/PDCx/SDCx registers are synchronized to the PWM time base

- Note 1: Software must clear the interrupt status here and the corresponding IFSx bit in the interrupt controller.

- 2: The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- **3:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 4: To operate in External Period Reset mode, configure FCLCONx<CLMOD> = 0 and PWMCONx<ITB> = 1.

| R/W-0                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                              | U-0                                         | U-0              | U-0             | U-0                              | U-0          |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------|------------------|-----------------|----------------------------------|--------------|

| SPIEN                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                 | SPISIDL                            | —                                           | —                |                 | —                                | —            |

| bit 15                                |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |                                             |                  |                 |                                  | bit 8        |

| U-0                                   | R/C-0                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0                                | U-0                                         | U-0              | U-0             | R-0                              | R-0          |

|                                       | SPIROV                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                  | —                                           | _                |                 | SPITBF                           | SPIRBF       |

| bit 7                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |                                             |                  |                 |                                  | bit 0        |

| Legend:                               |                                                                                                                                                                                                                                                                                                                                                                                                                                   | C = Clearable                      | bit                                         |                  |                 |                                  |              |

| R = Readab                            | ole bit                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable I                     | oit                                         | U = Unimpler     | nented bit, rea | d as '0'                         |              |

| -n = Value a                          | at POR                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                   |                                             | '0' = Bit is cle | ared            | x = Bit is unkr                  | nown         |

| bit 14<br>bit 13<br>bit 12-7<br>bit 6 | <ul> <li>1 = Enables module and configures SCKx, SDOx, SDIx and SSx as serial port pins</li> <li>0 = Disables module</li> <li>Unimplemented: Read as '0'</li> <li>SPISIDL: SPIx Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>Unimplemented: Read as '0'</li> <li>SPIROV: SPIx Receive Overflow Flag bit</li> </ul> |                                    |                                             |                  |                 |                                  |              |

|                                       | previous<br>0 = No overfl                                                                                                                                                                                                                                                                                                                                                                                                         | data in the SPI<br>low has occurre | xBUF registe                                |                  | arded. The use  | er software has                  | not read the |

| bit 5-2                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                 | ted: Read as '0                    |                                             |                  |                 |                                  |              |

| bit 1                                 | <ul> <li>SPITBF: SPIx Transmit Buffer Full Status bit</li> <li>1 = Transmit not yet started, SPIxTXB is full</li> <li>0 = Transmit started, SPIxTXB is empty. Automatically set in hardware when CPU writes the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.</li> </ul>                                                                       |                                    |                                             |                  |                 |                                  |              |

| bit 0                                 | 1 = Receive<br>0 = Receive<br>data from                                                                                                                                                                                                                                                                                                                                                                                           |                                    | RXB is full<br>, SPIxRXB is<br>IxRXB. Auton | empty. Autom     |                 | hardware when<br>when core reads |              |

## REGISTER 16-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Table Writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

| Note: | For more details on the instruction set, |

|-------|------------------------------------------|

|       | refer to the "16-bit MCU and DSC         |

|       | Programmer's Reference Manual"           |

|       | (DS70157).                               |

| Field           | Description                                                                          |

|-----------------|--------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                      |

| (text)          | Means "content of text"                                                              |

| [text]          | Means "the location addressed by text"                                               |

| { }             | Optional field or operation                                                          |

| <n:m></n:m>     | Register bit field                                                                   |

| .b              | Byte mode selection                                                                  |

| .d              | Double-Word mode selection                                                           |

| .S              | Shadow register select                                                               |

| .W              | Word mode selection (default)                                                        |

| Acc             | One of two accumulators {A, B}                                                       |

| AWB             | Accumulator Write-Back Destination Address register $\in$ {W13, [W13]+ = 2}          |

| bit4            | 4-bit bit selection field (used in word-addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |

| f               | File register address ∈ {0x00000x1FFF}                                               |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                       |

| lit4            | 4-bit unsigned literal ∈ {015}                                                       |

| lit5            | 5-bit unsigned literal ∈ {031}                                                       |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10           | 10-bit unsigned literal $\in \{0255\}$ for Byte mode, $\{0:1023\}$ for Word mode     |

| lit14           | 14-bit unsigned literal $\in \{016384\}$                                             |

| lit16           | 16-bit unsigned literal $\in \{065535\}$                                             |

| lit23           | 23-bit unsigned literal $\in$ {08388608}; LSb must be '0'                            |

| None            | Field does not require an entry, can be blank                                        |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC              | Program Counter                                                                      |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6           | 6-bit signed literal $\in$ {-1616}                                                   |

| Wb              | Base W register ∈ {W0W15}                                                            |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor Working register pair (Direct Addressing)                          |

TABLE 22-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

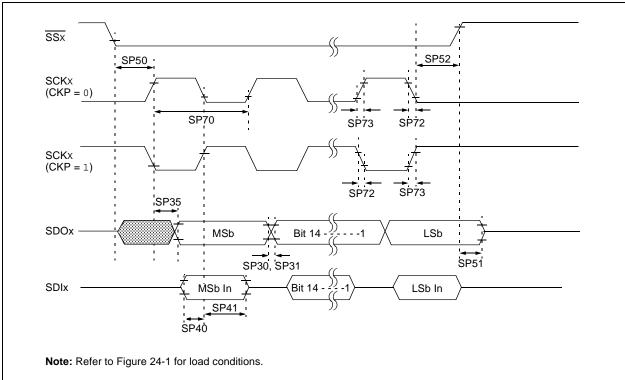

# TABLE 24-36:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                      |

|--------------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70               | TscP                  | Maximum SCKx Input<br>Frequency                              | _                                                     | —                  | 15  | MHz   | See Note 3                           |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                     | _                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                     | _                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                                     | —                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | —                                                     | _                  |     | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                     | 6                  | 20  | ns    |                                      |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                    | —                  | _   | ns    |                                      |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                    | _                  | _   | ns    |                                      |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                    | _                  | _   | ns    |                                      |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                   | —                  | —   | ns    |                                      |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                    | —                  | 50  | ns    | See Note 4                           |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                          | —                  | _   | ns    | See Note 4                           |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

# FIGURE 24-18: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS |        |                                                   | Standard Operating Conditions (see Note 2): 3.0V to 3.6V<br>Operating temperature: $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                            |            |    |                                                                                                                         |  |

|--------------------|--------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|----|-------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristic                                    | Min                                                                                                                                                                                              | Min Typ Max Units Comments |            |    |                                                                                                                         |  |

| CM10               | VIOFF  | Input Offset Voltage                              | -58                                                                                                                                                                                              | +14/-40                    | 66         | mV |                                                                                                                         |  |

| CM11               | VICM   | Input Common-Mode<br>Voltage Range <sup>(1)</sup> | 0                                                                                                                                                                                                | —                          | AVDD - 1.5 | V  |                                                                                                                         |  |

| CM12               | Vgain  | Open Loop Gain <sup>(1)</sup>                     | 90                                                                                                                                                                                               | —                          | -          | db |                                                                                                                         |  |

| CM13               | CMRR   | Common-Mode<br>Rejection Ratio <sup>(1)</sup>     | 70                                                                                                                                                                                               | —                          | -          | db |                                                                                                                         |  |

| CM14               | TRESP  | Large Signal Response                             | 21                                                                                                                                                                                               | 30                         | 49         | ns | V+ input step of 100 mv while<br>V- input held at AVDD/2. Delay<br>measured from analog input pin to<br>PWM output pin. |  |

#### TABLE 24-42: COMPARATOR MODULE SPECIFICATIONS

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: Module is functional at VBOR < VDD < VDDMIN, but with degraded performance. Module functionality is tested but not characterized.

| AC and DC CHARACTERISTICS |        |                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |            |          |                                                                                                   |

|---------------------------|--------|-------------------------------------------|-------------------------------------------------------|------|------------|----------|---------------------------------------------------------------------------------------------------|

| Param.<br>No.             | Symbol | Characteristic                            | Min Typ Max                                           |      | Units      | Comments |                                                                                                   |

| DA01                      | EXTREF | External Voltage Reference <sup>(1)</sup> | 0                                                     |      | AVDD - 1.6 | V        |                                                                                                   |

| DA08                      | INTREF | Internal Voltage Reference <sup>(1)</sup> | 1.25                                                  | 1.32 | 1.41       | V        |                                                                                                   |

| DA02                      | CVRES  | Resolution                                |                                                       | 10   |            | Bits     |                                                                                                   |

| DA03                      | INL    | Integral Nonlinearity Error               | -7                                                    | -1   | +7         | LSB      | AVDD = 3.3V,<br>DACREF = (AVDD/2)V                                                                |

| DA04                      | DNL    | Differential Nonlinearity Error           | -5                                                    | -0.5 | +5         | LSB      |                                                                                                   |

| DA05                      | EOFF   | Offset Error                              | 0.4                                                   | -0.8 | 2.6        | %        |                                                                                                   |

| DA06                      | EG     | Gain Error                                | 0.4                                                   | -1.8 | 5.2        | %        |                                                                                                   |

| DA07                      | TSET   | Settling Time <sup>(1)</sup>              | 711                                                   | 1551 | 2100       | nsec     | Measured when<br>range = 1 (high range),<br>and CMREF<9:0><br>transitions from 0x1FF<br>to 0x300. |

#### TABLE 24-43: DAC MODULE SPECIFICATIONS

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: Module is functional at VBOR < VDD < VDDMIN, but with degraded performance. Module functionality is tested but not characterized.

## 25.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

#### Note: Programming of the Flash memory is not allowed above +125°C.

The specifications between -40°C to +150°C are identical to those shown in **Section 24.0** "**Electrical Characteristics**" for operation between -40°C to +125°C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 24.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(3)</sup>                                 | 40°C to +150°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +160°C       |

| Voltage on VDD with respect to VSS                                            | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(4)}$    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\geq 3.0V^{(4)}$ | -0.3V to 5.6V        |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into VDD pin <sup>(2)</sup>                                   |                      |

| Maximum junction temperature                                                  | +155°C               |

| Maximum current sourced/sunk by any 4x I/O pin                                |                      |

| Maximum current sourced/sunk by any 8x I/O pin                                | 8 mA                 |

| Maximum current sourced/sunk by any 16x I/O pin                               |                      |

| Maximum current sunk by all ports combined                                    |                      |

| Maximum current sourced by all ports combined <sup>(2)</sup>                  | 180 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 25-2).

- 3: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 4: Refer to the "Pin Diagrams" section for 5V tolerant pins.

## dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

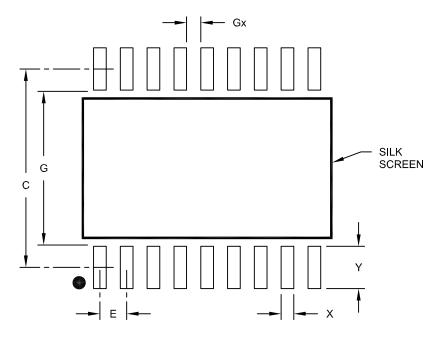

## RECOMMENDED LAND PATTERN

|                       | MILLIMETERS |      |          |      |

|-----------------------|-------------|------|----------|------|

| Dimension             | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch         | Е           |      | 1.27 BSC |      |

| Contact Pad Spacing   | С           |      | 9.40     |      |

| Contact Pad Width     | Х           |      |          | 0.60 |

| Contact Pad Length    | Y           |      |          | 2.00 |

| Distance Between Pads | Gx          | 0.67 |          |      |

| Distance Between Pads | G           | 7.40 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

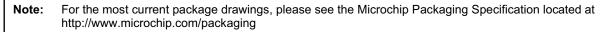

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

|                              | MILLIMETERS |       |          |       |  |

|------------------------------|-------------|-------|----------|-------|--|

| Dimension                    | Limits      | MIN   | NOM      | MAX   |  |

| Number of Terminals          | N           | 44    |          |       |  |

| Number of Terminals per Side | ND          | 12    |          |       |  |

| Number of Terminals per Side | NE          | 10    |          |       |  |

| Pitch                        | е           |       | 0.50 BSC |       |  |

| Overall Height               | Α           | 0.80  | 0.90     | 1.00  |  |

| Standoff                     | A1          | 0.025 | -        | 0.075 |  |

| Overall Width                | Е           |       | 6.00 BSC |       |  |

| Exposed Pad Width            | E2          | 4.40  | 4.55     | 4.70  |  |

| Overall Length               | D           |       | 6.00 BSC |       |  |

| Exposed Pad Length           | D2          | 4.40  | 4.55     | 4.70  |  |

| Terminal Width               | b           | 0.20  | 0.25     | 0.30  |  |

| Terminal Length              | L           | 0.20  | 0.25     | 0.30  |  |

| Terminal-to-Exposed Pad      | К           | 0.20  | -        | -     |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157D Sheet 2 of 2

## **Revision E (December 2009)**

The revision includes the following global update:

• Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

| Section Name                                                                                                                                                | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers and Digital<br>Signal Controllers (up to 16-Kbyte<br>Flash and up to 2-Kbyte SRAM) with<br>High-Speed PWM, ADC and<br>Comparators" | Changed CN6 to CN5 on pin 16 of dsPIC33FJ16GS502 28-pin SPDIP,<br>SOIC pin diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Section 2.0 "Guidelines for Getting<br>Started with 16-bit Digital Signal<br>Controllers"                                                                   | Removed the 10 Ohm resistor from Figure 2-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Section 4.0 "Memory Organization"                                                                                                                           | Renamed bit 13 of the REFOCON SFR in the System Control Register<br>Map from ROSIDL to ROSSLP and changed the All Resets value from<br>'0000' to '2300' for the ACLKCON SFR (see 4-41).                                                                                                                                                                                                                                                                                                                                              |