Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 6KB (6K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256 x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

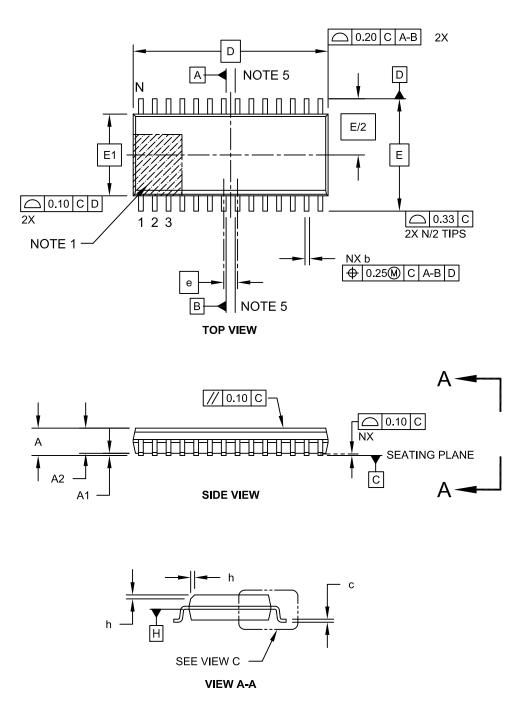

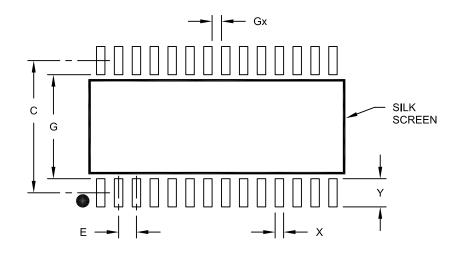

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.2 RTSP Operation

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 24-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the Table Write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

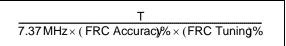

The programming time depends on the FRC accuracy (see Table 24-20) and the value of the FRC Oscillator Tuning register (see Register 8-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time, and Word Write Cycle Time parameters (see Table 24-12).

| EQUATION 5-1: | PROGRAMMING TIME |

|---------------|------------------|

|               |                  |

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm$ 5%. If the TUN<5:0> bits (see Register 8-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

| <br>= 1.435ms   |

|-----------------|

| 375) = 1.43311S |

|                 |

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \text{ Cycles}}{7.37 \text{ MHz} \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 \text{ms}$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

### 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

| REGISTER 5-2     |                                                                      |                  |      |                   |      |                 |       |  |  |

|------------------|----------------------------------------------------------------------|------------------|------|-------------------|------|-----------------|-------|--|--|

| U-0              | U-0                                                                  | U-0              | U-0  | U-0               | U-0  | U-0             | U-0   |  |  |

| —                |                                                                      | —                | _    | —                 | _    | —               | —     |  |  |

| bit 15           |                                                                      |                  |      |                   |      |                 | bit 8 |  |  |

|                  |                                                                      |                  |      |                   |      |                 |       |  |  |

| W-0              | W-0                                                                  | W-0              | W-0  | W-0               | W-0  | W-0             | W-0   |  |  |

|                  |                                                                      |                  | NVMK | EY<7:0>           |      |                 |       |  |  |

| bit 7            |                                                                      |                  |      |                   |      |                 | bit 0 |  |  |

|                  |                                                                      |                  |      |                   |      |                 |       |  |  |

| Legend:          |                                                                      |                  |      |                   |      |                 |       |  |  |

| R = Readable b   | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |      |                   |      |                 |       |  |  |

| -n = Value at PO | OR                                                                   | '1' = Bit is set |      | '0' = Bit is clea | ared | x = Bit is unkr | nown  |  |  |

### REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Nonvolatile Memory Key bits (write-only)

| R/W-0         | R/W-0                                                                                                                      | U-0                                  | U-0           | U-0              | U-0              | R/W-0             | R/W-0        |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|------------------|------------------|-------------------|--------------|--|--|

| TRAPR         | IOPUWR                                                                                                                     |                                      |               |                  |                  | СМ                | VREGS        |  |  |

| bit 15        |                                                                                                                            |                                      |               |                  |                  |                   | bit 8        |  |  |

| DAMO          | DAM 0                                                                                                                      | DANO                                 | DAMO          | DAMO             | D/M/ O           |                   |              |  |  |

| R/W-0         | R/W-0                                                                                                                      | R/W-0<br>SWDTEN <sup>(2)</sup>       | R/W-0         | R/W-0            | R/W-0            | R/W-1             | R/W-1        |  |  |

| EXTR<br>bit 7 | SWR                                                                                                                        | SWDIEN                               | WDTO          | SLEEP            | IDLE             | BOR               | POR<br>bit ( |  |  |

|               |                                                                                                                            |                                      |               |                  |                  |                   |              |  |  |

| Legend:       |                                                                                                                            |                                      |               |                  |                  |                   |              |  |  |

| R = Readable  | e bit                                                                                                                      | W = Writable b                       | bit           | U = Unimpler     | nented bit, rea  | d as '0'          |              |  |  |

| -n = Value at | POR                                                                                                                        | '1' = Bit is set                     |               | '0' = Bit is cle | ared             | x = Bit is unk    | nown         |  |  |

| bit 15        | TRAPR: Trap                                                                                                                | Reset Flag bit                       |               |                  |                  |                   |              |  |  |

|               | •                                                                                                                          | onflict Reset has                    | s occurred    |                  |                  |                   |              |  |  |

|               | 0 = A Trap Co                                                                                                              | onflict Reset has                    | s not occurre | d                |                  |                   |              |  |  |

| bit 14        |                                                                                                                            | gal Opcode or                        |               |                  | -                |                   |              |  |  |

|               | •                                                                                                                          | l opcode detec                       |               | gal address mo   | ode or Uninitia  | lized W registe   | er used as a |  |  |

|               |                                                                                                                            | Pointer caused<br>I opcode or Unit   |               | egister Reset h  | as not occurre   | d                 |              |  |  |

| bit 13-10     |                                                                                                                            | ted: Read as '0                      |               | og.oto: 11000111 |                  | -                 |              |  |  |

| bit 9         | -                                                                                                                          |                                      |               |                  |                  |                   |              |  |  |

|               | <b>CM:</b> Configuration Mismatch Flag bit<br>1 = A Configuration Mismatch Reset has occurred                              |                                      |               |                  |                  |                   |              |  |  |

|               | 0 = A Configu                                                                                                              | uration Mismatc                      | h Reset has   | NOT occurred     |                  |                   |              |  |  |

| bit 8         | VREGS: Voltage Regulator Standby During Sleep bit                                                                          |                                      |               |                  |                  |                   |              |  |  |

|               | 1 = Voltage regulator is active during Sleep                                                                               |                                      |               |                  |                  |                   |              |  |  |

| h:+ 7         | <ul> <li>0 = Voltage regulator goes into Standby mode during Sleep</li> <li>EXTR: External Reset Pin (MCLR) bit</li> </ul> |                                      |               |                  |                  |                   |              |  |  |

| bit 7         |                                                                                                                            | •                                    | ,             | rod              |                  |                   |              |  |  |

|               | <ul> <li>1 = A Master Clear (pin) Reset has occurred</li> <li>0 = A Master Clear (pin) Reset has not occurred</li> </ul>   |                                      |               |                  |                  |                   |              |  |  |

| bit 6         | SWR: Software Reset Flag (Instruction) bit                                                                                 |                                      |               |                  |                  |                   |              |  |  |

|               | 1 = A RESET instruction has been executed                                                                                  |                                      |               |                  |                  |                   |              |  |  |

|               | 0 = A reset                                                                                                                | instruction has                      | not been exe  | ecuted           |                  |                   |              |  |  |

| bit 5         | SWDTEN: Software Enable/Disable of WDT bit <sup>(2)</sup>                                                                  |                                      |               |                  |                  |                   |              |  |  |

|               | 1 = WDT is e<br>0 = WDT is di                                                                                              |                                      |               |                  |                  |                   |              |  |  |

| bit 4         | WDT is disabled<br>WDTO: Watchdog Timer Time-out Flag bit                                                                  |                                      |               |                  |                  |                   |              |  |  |

|               | 1 = WDT time                                                                                                               | e-out has occuri<br>e-out has not oc | ed            |                  |                  |                   |              |  |  |

| bit 3         | SLEEP: Wake-up from Sleep Flag bit                                                                                         |                                      |               |                  |                  |                   |              |  |  |

|               |                                                                                                                            | as been in Sleep                     | -             |                  |                  |                   |              |  |  |

|               | 0 = Device ha                                                                                                              | as not been in S                     | leep mode     |                  |                  |                   |              |  |  |

| bit 2         |                                                                                                                            | up from Idle Fla                     | g bit         |                  |                  |                   |              |  |  |

|               |                                                                                                                            | as in Idle mode<br>as not in Idle m  | ode           |                  |                  |                   |              |  |  |

|               | of the Reset sta<br>use a device Re                                                                                        | atus bits can be                     |               | d in software. S | etting one of th | nese bits in soft | ware does no |  |  |

## REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| REGISTER 7-26: IPC14: INTERRUPT PRIORITY CONTROL REGISTER | 14 |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | PSEMIP2 | PSEMIP1 | PSEMIP0 | —   | —   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

|            | l   | - |  |

|------------|-----|---|--|

| <b>e</b> 0 | ena |   |  |

|            |     |   |  |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15-7<br>bit 6-4 | Unimplemented: Read as '0'<br>PSEMIP<2:0>: PWM Special Event Match Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | •<br>001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                                                 |

Unimplemented: Read as '0' bit 3-0

### REGISTER 7-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0                               | U-0    | U-0              | U-0    | U-0                                | U-0  | U-0             | U-0   |  |

|-----------------------------------|--------|------------------|--------|------------------------------------|------|-----------------|-------|--|

| _                                 | —      | —                | _      | —                                  | —    | —               | —     |  |

| bit 15                            |        |                  |        |                                    | •    |                 | bit 8 |  |

|                                   |        |                  |        |                                    |      |                 |       |  |

| U-0                               | R/W-1  | R/W-0            | R/W-0  | U-0                                | U-0  | U-0             | U-0   |  |

| —                                 | U1EIP2 | U1EIP1           | U1EIP0 | —                                  | —    | —               | —     |  |

| bit 7                             |        |                  |        |                                    |      |                 | bit 0 |  |

|                                   |        |                  |        |                                    |      |                 |       |  |

| Legend:                           |        |                  |        |                                    |      |                 |       |  |

| R = Readable bit W = Writable bit |        |                  | bit    | U = Unimplemented bit, read as '0' |      |                 |       |  |

| -n = Value at POR                 |        | '1' = Bit is set |        | '0' = Bit is cle                   | ared | x = Bit is unkr | nown  |  |

| bit 15-7 | Unimplemented: Read as '0' |  |

|----------|----------------------------|--|

| bit 6-4 | <b>U1EIP&lt;2:0&gt;:</b> UART1 Error Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |

|---------|----------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                          |

|         | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                        |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                 |

| R/W-0         | U-0                                                                                                                                         | R/W-0             | R/W-0           | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| ROON          | _                                                                                                                                           | ROSSLP            | ROSEL           | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                                                                                             |                   |                 |                       |                       | •                     | bit 8                 |  |  |  |

|               |                                                                                                                                             |                   |                 |                       |                       |                       |                       |  |  |  |

| U-0           | U-0                                                                                                                                         | U-0               | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

|               |                                                                                                                                             | —                 |                 | —                     | —                     | —                     | —                     |  |  |  |

| bit 7         |                                                                                                                                             |                   |                 |                       |                       |                       | bit 0                 |  |  |  |

| Legend:       |                                                                                                                                             |                   |                 |                       |                       |                       |                       |  |  |  |

| R = Readabl   | e bit                                                                                                                                       | W = Writable      | bit             | U = Unimplen          | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at | POR                                                                                                                                         | '1' = Bit is set  |                 | '0' = Bit is cle      |                       | x = Bit is unkr       | own                   |  |  |  |

|               |                                                                                                                                             |                   |                 |                       |                       |                       |                       |  |  |  |

| bit 15        | ROON: Refer                                                                                                                                 | ence Oscillator   | Output Enab     | ole bit               |                       |                       |                       |  |  |  |

|               |                                                                                                                                             |                   |                 | on the REFCL          | K0 pin <sup>(2)</sup> |                       |                       |  |  |  |

|               | 0 = Reference                                                                                                                               | e oscillator outp | out is disabled | ł                     |                       |                       |                       |  |  |  |

| bit 14        | Unimplemented: Read as '0'                                                                                                                  |                   |                 |                       |                       |                       |                       |  |  |  |

| bit 13        | ROSSLP: Reference Oscillator Run in Sleep bit                                                                                               |                   |                 |                       |                       |                       |                       |  |  |  |

|               | <ul> <li>1 = Reference oscillator output continues to run in Sleep</li> <li>0 = Reference oscillator output is disabled in Sleep</li> </ul> |                   |                 |                       |                       |                       |                       |  |  |  |

|               |                                                                                                                                             |                   |                 |                       |                       |                       |                       |  |  |  |

| bit 12        | ROSEL: Reference Oscillator Source Select bit                                                                                               |                   |                 |                       |                       |                       |                       |  |  |  |

|               | <ul> <li>1 = Oscillator crystal is used as the reference clock</li> <li>0 = System clock is used as the reference clock</li> </ul>          |                   |                 |                       |                       |                       |                       |  |  |  |

| bit 11-8      | <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divider bits <sup>(1)</sup>                                                                   |                   |                 |                       |                       |                       |                       |  |  |  |

|               | 1111 = Reference clock divided by 32,768                                                                                                    |                   |                 |                       |                       |                       |                       |  |  |  |

|               | 1110 = Reference clock divided by 16,384                                                                                                    |                   |                 |                       |                       |                       |                       |  |  |  |

|               | 1101 = Reference clock divided by 8,192<br>1100 = Reference clock divided by 4,096                                                          |                   |                 |                       |                       |                       |                       |  |  |  |

|               |                                                                                                                                             |                   | -               |                       |                       |                       |                       |  |  |  |

|               | 1011 = Reference clock divided by 2,048<br>1010 = Reference clock divided by 1,024                                                          |                   |                 |                       |                       |                       |                       |  |  |  |

|               |                                                                                                                                             | ence clock divi   |                 |                       |                       |                       |                       |  |  |  |

|               | 1000 = Reference clock divided by 256                                                                                                       |                   |                 |                       |                       |                       |                       |  |  |  |

|               | 0111 = Reference clock divided by 128                                                                                                       |                   |                 |                       |                       |                       |                       |  |  |  |

|               | 0110 = Reference clock divided by 64                                                                                                        |                   |                 |                       |                       |                       |                       |  |  |  |

|               | 0101 = Reference clock divided by 32<br>0100 = Reference clock divided by 16                                                                |                   |                 |                       |                       |                       |                       |  |  |  |

|               | 0100 = Reference clock divided by 16<br>0011 = Reference clock divided by 8                                                                 |                   |                 |                       |                       |                       |                       |  |  |  |

|               | 0010 = Reference clock divided by 4                                                                                                         |                   |                 |                       |                       |                       |                       |  |  |  |

|               |                                                                                                                                             | ence clock divi   | -               |                       |                       |                       |                       |  |  |  |

|               | 0000 = Refer                                                                                                                                |                   | , =             |                       |                       |                       |                       |  |  |  |

|               |                                                                                                                                             | EIICE CIUCK       |                 |                       |                       |                       |                       |  |  |  |

#### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

Note 1: The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

2: This pin is remappable. Refer to Section 10.6 "Peripheral Pin Select" for more information.

| U-0            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                | R/W-0   | R/W-0            | U-0  | R/W-0                | U-0   |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------|------------------|------|----------------------|-------|--|--|--|

| _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | T3MD                                 | T2MD    | T1MD             | _    | PWMMD <sup>(1)</sup> | _     |  |  |  |

| oit 15         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |         |                  |      |                      | bit   |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |         |                  |      |                      |       |  |  |  |

| R/W-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                | U-0     | R/W-0            | U-0  | U-0                  | R/W-0 |  |  |  |

| I2C1MD         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U1MD                                 | —       | SPI1MD           | —    | —                    | ADCMD |  |  |  |

| bit 7          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |         |                  |      |                      | bit   |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |         |                  |      |                      |       |  |  |  |

| Legend:        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |         |                  |      |                      |       |  |  |  |

| R = Readab     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable                         |         | U = Unimpler     |      |                      |       |  |  |  |

| -n = Value a   | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | '1' = Bit is set                     | l       | '0' = Bit is cle | ared | x = Bit is unkno     | own   |  |  |  |

| bit 15-14      | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nted: Read as '                      | 0'      |                  |      |                      |       |  |  |  |

| bit 13         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3 Module Disal                       |         |                  |      |                      |       |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nodule is disabl                     |         |                  |      |                      |       |  |  |  |

|                | 0 = Timer3 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nodule is enable                     | ed      |                  |      |                      |       |  |  |  |

| bit 12         | T2MD: Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 Module Disa                        | ble bit |                  |      |                      |       |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nodule is disabl                     |         |                  |      |                      |       |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nodule is enable                     |         |                  |      |                      |       |  |  |  |