Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 6KB (6K × 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

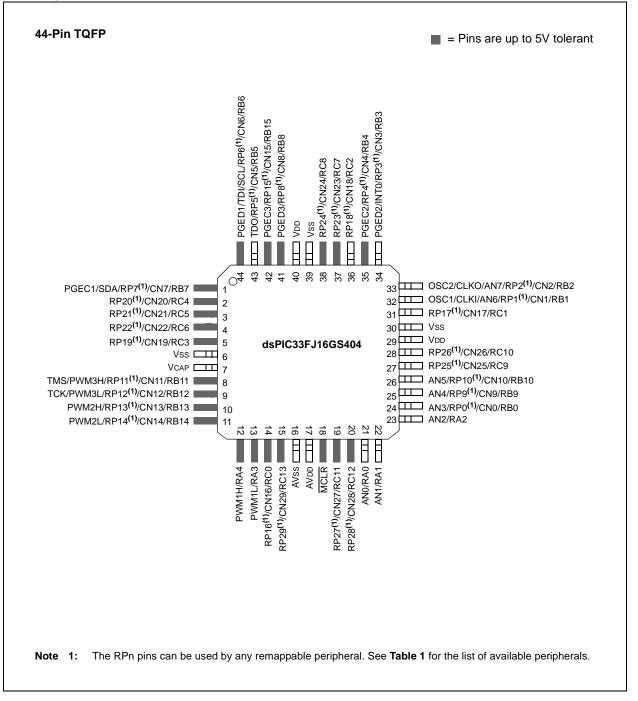

### Pin Diagrams (Continued)

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### TABLE 4-1: CPU CORE REGISTER MAP (CONTINUED)

| File Name | SFR<br>Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8         | Bit 7     | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------------|--------|----------|--------|--------|--------|--------|----------|---------------|-----------|--------|-------|-------|-------|-------|-------|-------|---------------|

| XMODSRT   | 0048        |        | XS<15:1> |        |        |        |        |          |               |           | 0      | xxxx  |       |       |       |       |       |               |

| XMODEND   | 004A        |        |          |        |        |        |        | XE<15:1> |               |           |        |       |       |       |       |       | 1     | xxxx          |

| YMODSRT   | 004C        |        |          |        |        |        |        | YS<15:1> |               |           |        |       |       |       |       |       | 0     | xxxx          |

| YMODEND   | 004E        |        |          |        |        |        |        | YE<15:1> |               |           |        |       |       |       |       |       | 1     | xxxx          |

| XBREV     | 0050        | BREN   | XB14     | XB13   | XB12   | XB11   | XB10   | XB9      | XB8           | XB7       | XB6    | XB5   | XB4   | XB3   | XB2   | XB1   | XB0   | xxxx          |

| DISICNT   | 0052        | _      | _        |        |        |        |        | Disable  | Interrupts Co | ounter Re | gister |       |       |       |       |       |       | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dspic33FJ06GS101

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| CNEN1        | 0060        |        | _      | _      | _      | _      | _      | —     | _     | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE  | 0000          |

| CNPU1        | 0068        | _      | _      | _      | _      |        | _      | _     |       | CN7PUE | CN6PUE | CN5PUE | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-3:CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ06GS102, dsPIC33FJ06GS202, dsPIC33FJ16GS402 AND<br/>dsPIC33FJ16GS502

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3         | Bit 2  | Bit 1  | Bit 0         | All<br>Resets |

|--------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|---------------|--------|--------|---------------|---------------|

| CNEN1        | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE         | CN2IE  | CN1IE  | CN0IE         | 0000          |

| CNPU1        | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE | CN4PUE | <b>CN3PUE</b> | CN2PUE | CN1PUE | <b>CN0PUE</b> | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ16GS404 AND dsPIC33FJ16GS504

|   | File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3         | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|---|--------------|-------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|---------|---------|---------------|---------------|

| ( | CNEN1        | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE   | CN8IE   | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE         | CN2IE   | CN1IE   | CN0IE         | 0000          |

| ( | CNEN2        | 0062        | _       | -       | CN29IE  | CN28IE  | CN27IE  | CN26IE  | CN25IE  | CN24IE  | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE        | CN18IE  | CN17IE  | CN16IE        | 0000          |

| ( | CNPU1        | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE  | CN8PUE  | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | <b>CN3PUE</b> | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| ( | CNPU2        | 006A        | _       | _       | CN29PUE | CN28PUE | CN27PUE | CN26PUE | CN25PUE | CN24PUE | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE       | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx, and three other lines for

power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the Digital Signal Controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data, either in blocks or 'rows' of 64 instructions (192 bytes) at a time, or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

#### 5.1 Table Instructions and Flash Programming

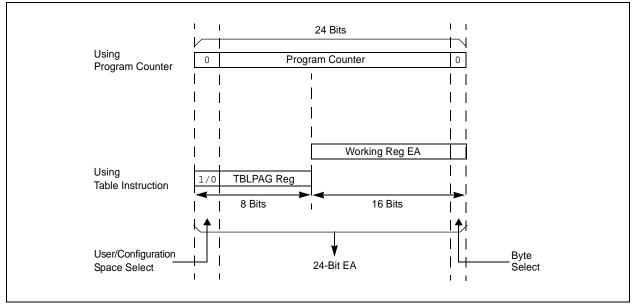

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

© 2008-2014 Microchip Technology Inc.

## 6.3 External Reset (EXTR)

The External Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to **Section 24.0** "**Electrical Characteristics**" for minimum pulse width specifications. The External Reset (MCLR) pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

#### 6.3.0.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate Reset signals to reset multiple devices in the system. This External Reset signal can be directly connected to the MCLR pin to reset the device when the rest of the system is reset.

#### 6.3.0.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to reset the device, the External Reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The External Reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.4 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle and the Reset vector fetch will commence.

The Software Reset (SWR) flag (instruction) in the Reset Control (RCON<6>) register is set to indicate the Software Reset.

# 6.5 Watchdog Timer Time-out Reset (WDTO)

Whenever a Watchdog time-out occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out (WDTO) flag in the Reset Control (RCON<4>) register is set to indicate the Watchdog Timer Reset. Refer to **Section 21.4 "Watchdog Timer (WDT)"** for more information on the Watchdog Timer Reset.

## 6.6 Trap Conflict Reset

If a lower priority hard trap occurs while a higher priority trap is being processed, a hard Trap Conflict Reset occurs. The hard traps include exceptions of Priority Levels 13 through 15, inclusive. The address error (Level 13) and oscillator error (Level 14) traps fall into this category.

The Trap Reset (TRAPR) flag in the Reset Control (RCON<15>) register is set to indicate the Trap Conflict Reset. Refer to **Section 7.0 "Interrupt Controller"** for more information on Trap Conflict Resets.

# 6.7 Configuration Mismatch Reset

To maintain the integrity of the Peripheral Pin Select Control registers, they are constantly monitored with shadow registers in hardware. If an unexpected change in any of the registers occur (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset occurs.

The Configuration Mismatch (CM) flag in the Reset Control (RCON<9>) register is set to indicate the Configuration Mismatch Reset. Refer to **Section 10.0 "I/O Ports"** for more information on the Configuration Mismatch Reset.

| Note: | The    | Configuration      | Mismatch     | Reset   |

|-------|--------|--------------------|--------------|---------|

|       | featu  | re and associate   | d Reset flag | are not |

|       | availa | able on all device | es.          |         |

## 6.8 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

The Illegal Opcode or Uninitialized W Access Reset (IOPUWR) flag in the Reset Control (RCON<14>) register is set to indicate the illegal condition device Reset.

#### 6.8.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The Illegal Opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the Illegal Opcode Reset, use only the lower 16 bits of each program memory section to store the data values. The upper 8 bits should be programmed with 3Fh, which is an illegal opcode value.

| R/W-0            | R-0          | U-0                                       | U-0        | U-0              | U-0             | U-0             | U-0    |

|------------------|--------------|-------------------------------------------|------------|------------------|-----------------|-----------------|--------|

| ALTIVT           | DISI         | —                                         |            | _                | —               |                 |        |

| oit 15           |              |                                           |            |                  |                 |                 | bit 8  |

|                  |              |                                           |            |                  |                 |                 |        |

| U-0              | U-0          | U-0                                       | U-0        | U-0              | R/W-0           | R/W-0           | R/W-0  |

| —                |              |                                           | _          | —                | INT2EP          | INT1EP          | INT0EP |

| bit 7            |              |                                           |            |                  |                 |                 | bit C  |

|                  |              |                                           |            |                  |                 |                 |        |

| Legend:          |              |                                           |            |                  |                 |                 |        |

| R = Readable bit |              | W = Writable I                            | oit        | •                | mented bit, rea |                 |        |

| -n = Value a     | t POR        | '1' = Bit is set                          |            | '0' = Bit is cle | eared           | x = Bit is unkr | nown   |

|                  |              |                                           |            |                  |                 |                 |        |

| bit 15           |              | able Alternate Int                        | •          | r Table bit      |                 |                 |        |

|                  |              | ernate vector table<br>ndard (default) ve | -          |                  |                 |                 |        |

| bit 14           |              | Instruction Status                        |            |                  |                 |                 |        |

| DIT 14           |              | instruction Status                        |            |                  |                 |                 |        |

|                  |              | struction is active                       |            |                  |                 |                 |        |

| bit 13-3         |              | ented: Read as '0                         |            |                  |                 |                 |        |

| bit 2            | -            | ternal Interrupt 2                        |            | t Polaritv Selec | t bit           |                 |        |

|                  |              | t on negative edg                         | •          | ,,               |                 |                 |        |

|                  |              | t on positive edge                        |            |                  |                 |                 |        |

| bit 1            | INT1EP: Ex   | ternal Interrupt 1                        | Edge Detec | t Polarity Selec | t bit           |                 |        |

|                  |              | t on negative edg                         |            |                  |                 |                 |        |

|                  | 0 = Interrup | t on positive edge                        | Э          |                  |                 |                 |        |

| bit 0            |              | ternal Interrupt 0                        | •          | t Polarity Selec | t bit           |                 |        |

|                  | •            | t on negative edg                         |            |                  |                 |                 |        |

|                  | 0 – Interrun | t on positive edge                        | <b>`</b>   |                  |                 |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| 11.0         | 11.0           |                                   |                   |                   |                  |                 |        |

|--------------|----------------|-----------------------------------|-------------------|-------------------|------------------|-----------------|--------|

| U-0          | U-0            | R/W-0                             | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|              |                | ADIE                              | U1TXIE            | U1RXIE            | SPI1IE           | SPI1EIE         | T3IE   |

| bit 15       |                |                                   |                   |                   |                  |                 | bit    |

| R/W-0        | R/W-0          | R/W-0                             | U-0               | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2IE         | OC2IE          | IC2IE                             | 0-0               | T1IE              | OC1IE            | IC1IE           | INTOIE |

| bit 7        | OOZIL          | IOZIL                             |                   | 1112              | OOTIL            | IOTIL           | bit    |

|              |                |                                   |                   |                   |                  |                 | bit    |

| Legend:      |                |                                   |                   |                   |                  |                 |        |

| R = Readab   | le bit         | W = Writable                      | bit               | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value a | t POR          | '1' = Bit is se                   | t                 | '0' = Bit is clea |                  | x = Bit is unkn | own    |

|              |                |                                   |                   |                   |                  |                 |        |

| bit 15-14    | Unimplemen     | ted: Read as                      | ʻ0'               |                   |                  |                 |        |

| bit 13       | ADIE: ADC1     | Conversion C                      | omplete Interru   | upt Enable bit    |                  |                 |        |

|              |                | request enable                    |                   |                   |                  |                 |        |

|              | •              | request not en                    |                   |                   |                  |                 |        |

| bit 12       |                |                                   | er Interrupt Ena  | able bit          |                  |                 |        |

|              |                | request enable<br>request not en  |                   |                   |                  |                 |        |

| bit 11       | -              | -                                 | Interrupt Enabl   | e bit             |                  |                 |        |

|              |                | request enable                    | =                 |                   |                  |                 |        |

|              | 0 = Interrupt  | request not en                    | abled             |                   |                  |                 |        |

| bit 10       | SPI1IE: SPI1   | Event Interrup                    | ot Enable bit     |                   |                  |                 |        |

|              |                | request enable                    |                   |                   |                  |                 |        |

| bit 9        | -              | request not en<br>I1 Event Interr |                   |                   |                  |                 |        |

| DIL 9        |                | request enable                    | •                 |                   |                  |                 |        |

|              |                | request not en                    |                   |                   |                  |                 |        |

| bit 8        | T3IE: Timer3   | Interrupt Enat                    | ole bit           |                   |                  |                 |        |

|              |                | request enable                    |                   |                   |                  |                 |        |

|              | -              | request not en                    |                   |                   |                  |                 |        |

| bit 7        |                | Interrupt Enat                    |                   |                   |                  |                 |        |

|              | •              | request enable<br>request not en  |                   |                   |                  |                 |        |

| bit 6        | -              | -                                 | hannel 2 Interr   | upt Enable bit    |                  |                 |        |

|              | -              | request enable                    |                   |                   |                  |                 |        |

|              |                | request not en                    |                   |                   |                  |                 |        |

| bit 5        | IC2IE: Input ( | Capture Chanr                     | nel 2 Interrupt I | Enable bit        |                  |                 |        |

|              |                | request enable                    |                   |                   |                  |                 |        |

| L:4          | -              | request not en                    |                   |                   |                  |                 |        |

| bit 4        | -              | ted: Read as                      |                   |                   |                  |                 |        |

| bit 3        |                | Interrupt Enat                    |                   |                   |                  |                 |        |

|              |                | request enable                    |                   |                   |                  |                 |        |

| bit 2        | -              | -                                 | hannel 1 Interr   | upt Enable bit    |                  |                 |        |

|              | -              | request enable                    |                   |                   |                  |                 |        |

|              |                |                                   |                   |                   |                  |                 |        |

#### DECISTED 7-12 IECO INTERRIET ENABLE CONTROL DECISTER O

| U-0                 | R/W-1                                                                                                           | R/W-0                                                                                                                                 | R/W-0                                                             | U-0                            | R/W-1            | R/W-0           | R/W-0    |

|---------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------|------------------|-----------------|----------|

| —                   | ADCP1IP2                                                                                                        | ADCP1IP1                                                                                                                              | ADCP1IP0                                                          | —                              | ADCP0IP2         | ADCP0IP1        | ADCP0IP0 |

| oit 15              |                                                                                                                 |                                                                                                                                       | •                                                                 |                                |                  |                 | bit 8    |

|                     |                                                                                                                 |                                                                                                                                       |                                                                   |                                |                  |                 |          |

| U-0                 | U-0                                                                                                             | U-0                                                                                                                                   | U-0                                                               | U-0                            | U-0              | U-0             | U-0      |

| _                   | —                                                                                                               | —                                                                                                                                     | —                                                                 | —                              | —                |                 | _        |

| oit 7               | ·                                                                                                               | •                                                                                                                                     |                                                                   |                                |                  |                 | bit 0    |

|                     |                                                                                                                 |                                                                                                                                       |                                                                   |                                |                  |                 |          |

| Legend:             |                                                                                                                 |                                                                                                                                       |                                                                   |                                |                  |                 |          |

| R = Readable        | e bit                                                                                                           | W = Writable                                                                                                                          | bit                                                               | U = Unimpler                   | mented bit, read | l as '0'        |          |

| -n = Value at       | POR                                                                                                             | '1' = Bit is set                                                                                                                      |                                                                   | '0' = Bit is cle               | ared             | x = Bit is unkr | nown     |

|                     |                                                                                                                 |                                                                                                                                       |                                                                   |                                |                  |                 |          |

| bit 15              | Unimplemen                                                                                                      | ted: Read as '                                                                                                                        | 0'                                                                |                                |                  |                 |          |

| L 1 4 4 4 0         |                                                                                                                 |                                                                                                                                       |                                                                   |                                |                  |                 |          |

| DIT 14-12           | ADCP1IP<2:0                                                                                                     | D>: ADC Pair 1                                                                                                                        | Conversion E                                                      | Oone Interrupt                 | Priority bits    |                 |          |

| Dit 14-12           |                                                                                                                 | D>: ADC Pair 1<br>ot is Priority 7 (                                                                                                  |                                                                   | •                              | Priority bits    |                 |          |

| DIT 14-12           |                                                                                                                 |                                                                                                                                       |                                                                   | •                              | Priority bits    |                 |          |

| dit 14-12           |                                                                                                                 |                                                                                                                                       |                                                                   | •                              | Priority bits    |                 |          |

| DIT 14-12           |                                                                                                                 | ot is Priority 7 (                                                                                                                    |                                                                   | •                              | Priority bits    |                 |          |

| dit 14-12           | 111 = Interrup<br>•<br>•<br>001 = Interrup                                                                      | ot is Priority 7 (                                                                                                                    | highest priorit                                                   | •                              | Priority bits    |                 |          |

| bit 14-12<br>bit 11 | <pre>111 = Interrup</pre>                                                                                       | ot is Priority 7 (<br>ot is Priority 1                                                                                                | highest priorit <u>i</u><br>abled                                 | •                              | Priority bits    |                 |          |

|                     | <pre>111 = Interrup</pre>                                                                                       | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis                                                                            | highest priorit <u>;</u><br>abled<br>0'                           | y interrupt)                   |                  |                 |          |

| pit 11              | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>ADCP0IP<2:0                       | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '                                                   | highest priority<br>abled<br>0'<br>) Conversion E                 | y interrupt)<br>Done Interrupt |                  |                 |          |

| pit 11              | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>ADCP0IP<2:0                       | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '<br><b>)&gt;:</b> ADC Pair 0                       | highest priority<br>abled<br>0'<br>) Conversion E                 | y interrupt)<br>Done Interrupt |                  |                 |          |

| pit 11              | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>ADCP0IP<2:0                       | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '<br><b>)&gt;:</b> ADC Pair 0                       | highest priority<br>abled<br>0'<br>) Conversion E                 | y interrupt)<br>Done Interrupt |                  |                 |          |

| pit 11              | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>ADCP0IP<2:0                       | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '<br><b>D&gt;:</b> ADC Pair 0<br>ot is Priority 7 ( | highest priority<br>abled<br>0'<br>) Conversion E                 | y interrupt)<br>Done Interrupt |                  |                 |          |

| pit 11              | <pre>111 = Interrup 001 = Interrup 000 = Interrup Unimplemen ADCP0IP&lt;2:0 111 = Interrup 001 = Interrup</pre> | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '<br><b>D&gt;:</b> ADC Pair 0<br>ot is Priority 7 ( | highest priorit<br>abled<br>o'<br>Conversion E<br>highest priorit | y interrupt)<br>Done Interrupt |                  |                 |          |

#### REGISTER 7-32: IPC27: INTERRUPT PRIORITY CONTROL REGISTER 27

# 8.4 Oscillator Control Registers

# **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,2)</sup>

| U-0     | R-0    | R-0   | R-0   | U-0   | R/W-y                | R/W-y                | R/W-y                |

|---------|--------|-------|-------|-------|----------------------|----------------------|----------------------|

| —       | COSC2  | COSC1 | COSC0 | —     | NOSC2 <sup>(3)</sup> | NOSC1 <sup>(3)</sup> | NOSC0 <sup>(3)</sup> |

| bit 15  |        |       |       |       |                      |                      | bit 8                |

|         |        |       |       |       |                      |                      |                      |

| R/W-0   | R/W-0  | R-0   | U-0   | R/C-0 | U-0                  | U-0                  | R/W-0                |

| CLKLOCK | IOLOCK | LOCK  | —     | CF    | _                    | —                    | OSWEN                |

| bit 7   |        |       |       |       |                      |                      | bit 0                |

| Legend:           | y = Value set from Co | y = Value set from Configuration bits on POR |                    |  |  |  |  |  |  |

|-------------------|-----------------------|----------------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                        | t, read as '0'     |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |  |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits (read-only)                                                                                                                                                                                                                                                                    |

|           | <pre>111 = Fast RC oscillator (FRC) with divide-by-n 110 = Fast RC oscillator (FRC) with divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Reserved 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL 000 = Fast RC oscillator (FRC)</pre> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(3)</sup>                                                                                                                                                                                                                                                                     |

|           | <pre>111 = Fast RC oscillator (FRC) with divide-by-n 110 = Fast RC oscillator (FRC) with divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Reserved 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL</pre>                                |

|           | 000 = Fast RC oscillator (FRC)                                                                                                                                                                                                                                                                                              |

| bit 7     | CLKLOCK: Clock Lock Enable bit                                                                                                                                                                                                                                                                                              |

|           | <pre>If Clock Switching is Enabled and FSCM is Disabled, (FOSC<fcksm> = 0b01): 1 = Clock switching is disabled, system clock source is locked 0 = Clock switching is enabled, system clock source can be modified by clock switching</fcksm></pre>                                                                          |

| bit 6     | IOLOCK: Peripheral Pin Select Lock bit                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Peripheral Pin Select is locked, write to Peripheral Pin Select registers not allowed</li> <li>0 = Peripheral Pin Select is not locked, write to Peripheral Pin Select registers allowed</li> </ul>                                                                                                            |

| bit 5     | LOCK: PLL Lock Status bit (read-only)                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Indicates that PLL is in lock, or PLL start-up timer is satisfied</li> <li>0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled</li> </ul>                                                                                                                                  |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

| Note 1:   | Writes to this register require an unlock sequence. Refer to " <b>Oscillator (Part IV)</b> " (DS70307) in the<br>"dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.                                                                                                             |

| 2:        | This register is reset only on a Power-on Reset (POR).                                                                                                                                                                                                                                                                      |

| 3:        | Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.<br>This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.                                            |

mode as a transition clock source between the two PLL modes.

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP19R5 | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

**RP18R3**

**RP18R2**

**RP18R1**

**RP18R0**

bit 0

RP18R4

#### REGISTER 10-24: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

**RP18R5**

bit 7

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP19R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP19 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP18R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP18 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

| U-0                            | U-0        | R/W-0            | R/W-0              | R/W-0                              | R/W-0  | R/W-0           | R/W-0  |

|--------------------------------|------------|------------------|--------------------|------------------------------------|--------|-----------------|--------|

| _                              |            | RP21R5           | RP21R4             | RP21R3                             | RP21R2 | RP21R1          | RP21R0 |

| bit 15                         |            |                  |                    |                                    |        |                 | bit 8  |

|                                |            |                  |                    |                                    |        |                 |        |

| U-0                            | U-0        | R/W-0            | R/W-0              | R/W-0                              | R/W-0  | R/W-0           | R/W-0  |

| —                              | —          | RP20R5           | RP20R4             | RP20R3                             | RP20R2 | RP20R1          | RP20R0 |

| bit 7                          |            |                  |                    |                                    |        | •               | bit 0  |

|                                |            |                  |                    |                                    |        |                 |        |

| Legend:                        |            |                  |                    |                                    |        |                 |        |

| R = Readable                   | bit        | W = Writable     | bit                | U = Unimplemented bit, read as '0' |        |                 |        |

| -n = Value at POR '1' = Bit is |            | '1' = Bit is set | t '0' = Bit is cle |                                    | ared   | x = Bit is unkr | nown   |

|                                |            |                  |                    |                                    |        |                 |        |

| bit 15-14                      | Unimplemen | ted: Read as '   | כ'                 |                                    |        |                 |        |

#### REGISTER 10-25: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10<sup>(1)</sup>

| bit 13-8 | <b>RP21R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP21 Output Pin bits (see Table 10-2 for peripheral function numbers) |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                               |

|          |                                                                                                                                          |

bit 5-0 **RP20R<5:0>:** Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 10-2 for peripheral function numbers)

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

### REGISTER 15-11: DTRx: PWMx DEAD-TIME REGISTER

| U-0               | U-0   | R/W-0            | R/W-0            | R/W-0   | R/W-0                              | R/W-0 | R/W-0              |  |

|-------------------|-------|------------------|------------------|---------|------------------------------------|-------|--------------------|--|

| —                 | _     |                  |                  | DTR>    | <13:8>                             |       |                    |  |

| bit 15            |       |                  |                  |         |                                    |       | bit 8              |  |

|                   |       |                  |                  |         |                                    |       |                    |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0            | R/W-0   | R/W-0                              | R/W-0 | R/W-0              |  |

|                   |       |                  | DTR              | 2x<7:0> |                                    |       |                    |  |

| bit 7             |       |                  |                  |         |                                    |       | bit 0              |  |

|                   |       |                  |                  |         |                                    |       |                    |  |

| Legend:           |       |                  |                  |         |                                    |       |                    |  |

| R = Readable bit  |       | W = Writable     | W = Writable bit |         | U = Unimplemented bit, read as '0' |       |                    |  |

| -n = Value at POR |       | '1' = Bit is set | '1' = Bit is set |         | '0' = Bit is cleared               |       | x = Bit is unknown |  |

bit 15-14Unimplemented: Read as '0'bit 13-0DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 15-12: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0                  | U-0   | R/W-0            | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              |  |

|----------------------|-------|------------------|------------------|------------------------------------|----------------------|-------|--------------------|--|

| —                    | _     |                  |                  | ALTDTI                             | Rx<13:8>             |       |                    |  |

| bit 15               |       |                  |                  |                                    |                      |       | bit 8              |  |

| R/W-0                | R/W-0 | R/W-0            | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              |  |

|                      |       |                  | ALTD             | TR <7:0>                           |                      |       |                    |  |

| bit 7                |       |                  |                  |                                    |                      |       | bit 0              |  |

| Legend:              |       |                  |                  |                                    |                      |       |                    |  |

| R = Readable bit     |       | W = Writable     | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |  |

| -n = Value at POR '1 |       | '1' = Bit is set | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

# 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CxSTAT are read/write:

- I2CxRSR is the shift register used for shifting data internal to the module and the user application has no access to it

- I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- The I2CxADD register holds the slave address

- A status bit, ADD10, indicates 10-Bit Addressing mode

- The I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV, and an interrupt pulse is generated.

# REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                          |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                      |

|       | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit.<br/>Hardware is clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                      |

|       | 1 = Enables Receive mode for $I^2C$ . Hardware is clear at end of eighth bit of master receive data byte.<br>0 = Receive sequence is not in progress                                                                             |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                |

|       | <ul><li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at end of master Stop sequence.</li><li>0 = Stop condition is not in progress</li></ul>                                                            |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                     |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at end of master Repeated Start sequence.                                                                                                        |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                  |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                      |

|       | 1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at end of master Start sequence.                                                                                                                          |

|       | 0 = Start condition is not in progress                                                                                                                                                                                           |

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

#### REGISTER 19-7: ADCPC2: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 2<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0  | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|--------|-------|--------|----------|----------|----------|----------|----------|

| IRQEN5 | PEND5 | SWTRG5 | TRGSRC54 | TRGSRC53 | TRGSRC52 | TRGSRC51 | TRGSRC50 |

| bit 15 |       |        |          |          |          |          | bit 8    |

| R/W-0  | R/W-0 | R/W-0  | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|--------|-------|--------|----------|----------|----------|----------|----------|

| IRQEN4 | PEND4 | SWTRG4 | TRGSRC44 | TRGSRC43 | TRGSRC42 | TRGSRC41 | TRGSRC40 |

| bit 7  |       |        |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15  | IRQEN5: Interrupt Request Enable 5 bit                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables IRQ generation when requested conversion of Channels AN11 and AN10 is completed</li> <li>0 = IRQ is not generated</li> </ul>  |

| bit 14  | PEND5: Pending Conversion Status 5 bit                                                                                                             |

|         | <ul> <li>1 = Conversion of Channels AN11 and AN10 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul> |

| bit 13  | SWTRG5: Software Trigger 5 bit                                                                                                                     |

|         | 1 = Starts conversion of AN11 and AN10 (if selected by the TRGSRCx bits) <sup>(2)</sup>                                                            |

|         | This bit is automatically cleared by hardware when the PEND5 bit is set.                                                                           |

|         | 0 = Conversion has not started                                                                                                                     |

| Note 1: | This register is only implemented in the dsPIC33FJ16GS504 devices.                                                                                 |

2: The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

| DC CHARACTERISTICS |                   |                                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |     |      |                         |  |

|--------------------|-------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|------|-------------------------|--|

| Param<br>No.       | Symbol            | Characteristic                                                              | Min Typ <sup>(1)</sup> Max Units Conditions                                                                                                                                                                                                                                             |   |     |      |                         |  |

| Operati            | Operating Voltage |                                                                             |                                                                                                                                                                                                                                                                                         |   |     |      |                         |  |

| DC10               | Vdd               | Supply Voltage <sup>(4)</sup>                                               | 3.0                                                                                                                                                                                                                                                                                     | _ | 3.6 | V    | Industrial and Extended |  |

| DC12               | Vdr               | RAM Data Retention Voltage <sup>(2)</sup>                                   | 1.8                                                                                                                                                                                                                                                                                     | _ | —   | V    |                         |  |

| DC16               | VPOR              | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal            | —                                                                                                                                                                                                                                                                                       | _ | Vss | V    |                         |  |

| DC17               | SVDD              | VDD Rise Rate <sup>(3)</sup><br>to Ensure Internal<br>Power-on Reset Signal | 0.03                                                                                                                                                                                                                                                                                    | — |     | V/ms | 0V-3.0V in 0.1 seconds  |  |

# TABLE 24-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: This is the limit to which VDD may be lowered without losing RAM data.

3: These parameters are characterized but not tested in manufacturing.

**4:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 24-11 for BOR values.

| AC CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |

| HSP35              | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               | -   | —   | 35  | ns    |            |  |

| HSP40              | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 25  | —   | —   | ns    |            |  |

| HSP41              | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 25  | —   | —   | ns    |            |  |

| HSP51              | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                  | 15  | —   | 55  | ns    | See Note 2 |  |

#### TABLE 25-11: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Assumes 50 pF load on all SPIx pins.

#### TABLE 25-12: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |

| HSP35              | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               | I   |     | 35  | ns    |            |  |

| HSP40              | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 25  |     |     | ns    |            |  |

| HSP41              | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 25  | _   | _   | ns    |            |  |

| HSP51              | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                  | 15  | —   | 55  | ns    | See Note 2 |  |

| HSP60              | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                                                                                                |     |     | 55  | ns    |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Assumes 50 pF load on all SPIx pins.

# 26.0 50 MIPS ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 electrical characteristics for devices operating at 50 MIPS.

The specifications for 50 MIPS are identical to those shown in **Section 24.0 "Electrical Characteristics"**, with the exception of the parameters listed in this section.

Parameters in this section begin with the letter "M", which denotes 50 MIPS operation. For example, Parameter DC29a in **Section 24.0** "Electrical Characteristics", is the up to 40 MIPS operation equivalent of MDC29a.

Absolute maximum ratings for the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 50 MIPS devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                 | 40°C to +85°C  |

|--------------------------------------------------------------------------------|----------------|

| Storage temperature                                                            | 65°C to +150°C |

| Voltage on VDD with respect to Vss                                             | 0.3V to +4.0V  |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup> |                |

| Voltage on any 5V tolerant pin with respect to Vss, when Vdd $\geq 3.0V^{(3)}$ | 0.3V to +5.6V  |

| Voltage on any 5V tolerant pin with respect to Vss, when $VDD < 3.0V^{(3)}$    |                |

| Maximum current out of Vss pin                                                 |                |

| Maximum current into Vod pin <sup>(2)</sup>                                    | 250 mA         |

| Maximum current sourced/sunk by any 4x I/O pin                                 |                |

| Maximum current sourced/sunk by any 8x I/O pin                                 | 25 mA          |

| Maximum current sourced/sunk by any 16x I/O pin                                | 45 mA          |

| Maximum current sunk by all ports                                              | 200 mA         |

| Maximum current sourced by all ports <sup>(2)</sup>                            | 200mA          |

|                                                                                |                |

# **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

2: Maximum allowable current is a function of device maximum power dissipation (see Table 24-2).

**3:** See the **"Pin Diagrams"** section for 5V tolerant pins.

#### 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | MILLIMETERS |           |     |      |  |  |

|--------------------------|-------------|-----------|-----|------|--|--|

| Dimension Lim            |             | MIN       | NOM | MAX  |  |  |

| Number of Pins           | N           | 18        |     |      |  |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |  |

| Overall Height           | A           | -         | -   | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |  |

| Overall Length           | D           | 11.55 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |  |

| Foot Angle               | $\varphi$   | 0°        | -   | 8°   |  |  |