#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 16KB (16K × 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 2K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

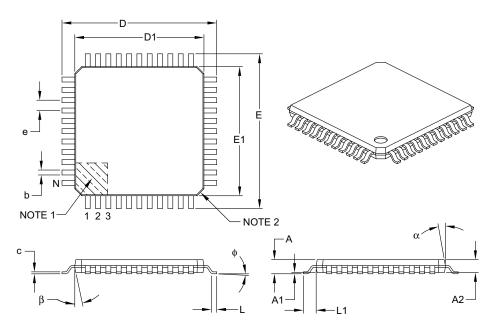

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402-50i-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70202) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access to program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping, as described in **Section 4.6 "Interfacing Program and Data Memory Spaces"**.

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

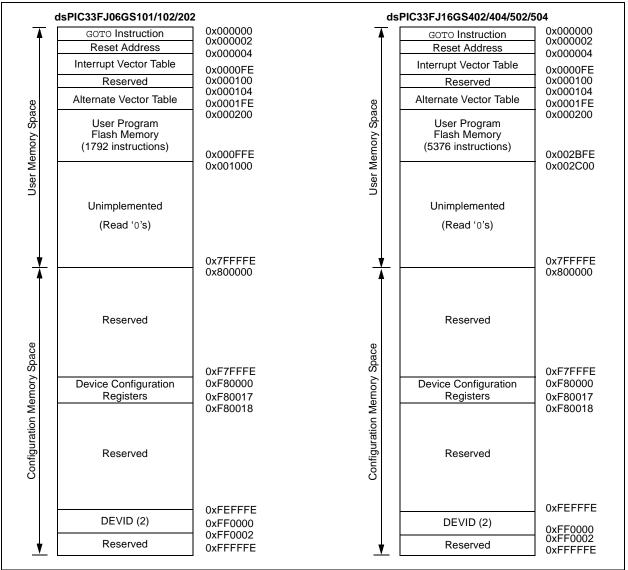

The memory maps for the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices are shown in Figure 4-1.

# FIGURE 4-1: PROGRAM MEMORY MAPS FOR dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 DEVICES

## TABLE 4-33: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|--------|----------|----------|----------|----------|----------|----------|-------|-------|----------|----------|----------|----------|----------|----------|---------------|

| RPINR0       | 0680        | _      | -      | INT1R5   | INT1R4   | INT1R3   | INT1R2   | INT1R1   | INT1R0   | _     |       | -        | _        | _        | —        | _        | _        | 3F00          |

| RPINR1       | 0682        |        |        | _        | _        | _        | _        | _        | _        | _     | _     | INT2R5   | INT2R4   | INT2R3   | INT2R2   | INT2R1   | INT2R0   | 003F          |

| RPINR2       | 0684        |        |        | T1CKR5   | T1CKR4   | T1CKR3   | T1CKR2   | T1CKR1   | T1CKR0   | _     | _     | _        | _        | _        | _        | _        | _        | 0000          |

| RPINR3       | 0686        |        |        | T3CKR5   | T3CKR4   | T3CKR3   | T3CKR2   | T3CKR1   | T3CKR0   | _     | _     | T2CKR5   | T2CKR4   | T2CKR3   | T2CKR2   | T2CKR1   | T2CKR0   | 3F3F          |

| RPINR7       | 068E        | _      | _      | IC2R5    | IC2R4    | IC2R3    | IC2R2    | IC2R1    | IC2R0    | _     | _     | IC1R5    | IC1R4    | IC1R3    | IC1R2    | IC1R1    | IC1R0    | 3F3F          |

| RPINR11      | 0696        | _      | _      | _        | _        | —        | _        | _        | _        | _     | _     | OCFAR5   | OCFAR4   | OCFAR3   | OCFAR2   | OCFAR1   | OCFAR0   | 3F3F          |

| RPINR18      | 06A4        |        |        | U1CTSR5  | U1CTSR4  | U1CTSR3  | U1CTSR2  | U1CTSR1  | U1CTSR0  | _     | _     | U1RXR5   | U1RXR4   | U1RXR3   | U1RXR2   | U1RXR1   | U1RXR0   | 003F          |

| RPINR20      | 06A8        | -      |        | SCK1R5   | SCK1R4   | SCK1R3   | SCK1R2   | SCK1R1   | SCK1R0   | _     | _     | SDI1R5   | SDI1R4   | SDI1R3   | SDI1R2   | SDI1R1   | SDI1R0   | 3F3F          |

| RPINR21      | 06AA        |        |        | _        | _        | _        | _        | _        | _        | _     | _     | SS1R5    | SS1R54   | SS1R3    | SS1R2    | SS1R1    | SS1R0    | 0000          |

| RPINR29      | 06BA        |        |        | FLT1R5   | FLT1R4   | FLT1R3   | FLT1R2   | FLT1R1   | FLT1R0   | _     | _     | _        | _        | _        | _        | _        | _        | 3F00          |

| RPINR30      | 06BC        |        |        | FLT3R5   | FLT3R4   | FLT3R3   | FLT3R2   | FLT3R1   | FLT3R0   | _     | _     | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | 3F3F          |

| RPINR31      | 06BE        |        |        | FLT5R5   | FLT5R4   | FLT5R3   | FLT5R2   | FLT5R1   | FLT5R0   | _     | _     | FLT4R5   | FLT4R4   | FLT4R3   | FLT4R2   | FLT4R1   | FLT4R0   | 3F3F          |

| RPINR32      | 06C0        |        |        | FLT7R5   | FLT7R4   | FLT7R3   | FLT7R2   | FLT7R1   | FLT7R0   | _     | _     | FLT6R5   | FLT6R4   | FLT6R3   | FLT6R2   | FLT6R1   | FLT6R0   | 3F3F          |

| RPINR33      | 06C2        | _      | _      | SYNCI1R5 | SYNCI1R4 | SYNCI1R3 | SYNCI1R2 | SYNCI1R1 | SYNCI1R0 | _     | _     | FLT8R5   | FLT8R4   | FLT8R3   | FLT8R2   | FLT8R1   | FLT8R0   | 3F3F          |

| RPINR34      | 06C4        | _      | _      | _        | _        | -        |          | _        | —        | —     |       | SYNCI2R5 | SYNCI2R4 | SYNCI2R3 | SYNCI2R2 | SYNCI2R1 | SYNCI2R0 | 3F3F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-34: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ06GS101

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| RPOR0        | 06D0        | _      |        | RP1R5  | RP1R4  | RP1R3  | RP1R2  | RP1R1  | RP1R0  | _     |       | RP0R5  | RP0R4  | RP0R3  | RP0R2  | RP0R1  | RP0R0  | 0000          |

| RPOR1        | 06D2        |        | _      | RP3R5  | RP3R4  | RP3R3  | RP3R2  | RP3R1  | RP3R0  |       | _     | RP2R5  | RP2R4  | RP2R3  | RP2R2  | RP2R1  | RP2R0  | 0000          |

| RPOR2        | 06D4        |        | _      | RP5R5  | RP5R4  | RP5R3  | RP5R2  | RP5R1  | RP5R0  |       | _     | RP4R5  | RP4R4  | RP4R3  | RP4R2  | RP4R1  | RP4R0  | 0000          |

| RPOR3        | 06D6        |        | _      | RP7R5  | RP7R4  | RP7R3  | RP7R2  | RP7R1  | RP7R0  |       | _     | RP6R5  | RP6R4  | RP6R3  | RP6R2  | RP6R1  | RP6R0  | 0000          |

| RPOR16       | 06F0        |        | _      | RP33R5 | RP33R4 | RP33R3 | RP33R2 | RP33R1 | RP33R0 |       | _     | RP32R5 | RP32R4 | RP32R3 | RP32R2 | RP32R1 | RP32R0 | 0000          |

| RPOR17       | 06F2        |        | _      | RP35R5 | RP35R4 | RP35R3 | RP35R2 | RP35R1 | RP35R0 | -     | _     | RP34R5 | RP34R4 | RP34R3 | RP34R2 | RP34R1 | RP34R0 | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 4.4 Modulo Addressing

Modulo Addressing mode is a method used to provide an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.4.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that will operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

MOV #0x1100, W0 Byte MOV W0, XMODSRT ;set modulo start address Address #0x1163, W0 MOV W0, MODEND MOV ;set modulo end address 0x1100 MOV #0x8001, W0 MOV W0, MODCON ;enable W1, X AGU for modulo MOV #0x0000, W0 ;W0 holds buffer fill value MOV #0x1110, W1 ;point W1 to buffer 0x1163 DO AGAIN, #0x31 ;fill the 50 buffer locations MOV WO, [W1++] ;fill the next location AGAIN: INC W0, W0 ; increment the fill value Start Addr = 0x1100End Addr = 0x1163Length = 0x0032 words

FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

| R/W-0                                                                    | R-0                                                                       | U-0                               | U-0        | U-0              | U-0    | U-0             | U-0    |  |  |  |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------|------------|------------------|--------|-----------------|--------|--|--|--|--|

| ALTIVT                                                                   | DISI                                                                      | —                                 |            | —                | —      |                 |        |  |  |  |  |

| oit 15                                                                   |                                                                           |                                   |            |                  |        |                 | bit 8  |  |  |  |  |

|                                                                          |                                                                           |                                   |            |                  |        |                 |        |  |  |  |  |

| U-0                                                                      | U-0                                                                       | U-0                               | U-0        | U-0              | R/W-0  | R/W-0           | R/W-0  |  |  |  |  |

| —                                                                        |                                                                           |                                   |            | —                | INT2EP | INT1EP          | INT0EP |  |  |  |  |

| bit 7                                                                    |                                                                           |                                   |            |                  |        |                 | bit C  |  |  |  |  |

|                                                                          |                                                                           |                                   |            |                  |        |                 |        |  |  |  |  |

| Legend:                                                                  |                                                                           |                                   |            |                  |        |                 |        |  |  |  |  |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0' |                                                                           |                                   |            |                  |        |                 |        |  |  |  |  |

| -n = Value a                                                             | t POR                                                                     | '1' = Bit is set                  |            | '0' = Bit is cle | eared  | x = Bit is unkr | nown   |  |  |  |  |

|                                                                          |                                                                           |                                   |            |                  |        |                 |        |  |  |  |  |

| bit 15                                                                   | ALTIVT: Enable Alternate Interrupt Vector Table bit                       |                                   |            |                  |        |                 |        |  |  |  |  |

|                                                                          | 1 = Use alternate vector table<br>0 = Use standard (default) vector table |                                   |            |                  |        |                 |        |  |  |  |  |

| bit 14                                                                   |                                                                           | · · ·                             |            |                  |        |                 |        |  |  |  |  |

| DIT 14                                                                   |                                                                           | DISI: DISI Instruction Status bit |            |                  |        |                 |        |  |  |  |  |

|                                                                          | 1 = DISI instruction is active<br>0 = DISI instruction is not active      |                                   |            |                  |        |                 |        |  |  |  |  |

| bit 13-3                                                                 |                                                                           | ented: Read as '0                 |            |                  |        |                 |        |  |  |  |  |

| bit 2                                                                    | -                                                                         | ternal Interrupt 2                |            | t Polaritv Selec | t bit  |                 |        |  |  |  |  |

|                                                                          |                                                                           | t on negative edg                 | •          | ,,               |        |                 |        |  |  |  |  |

|                                                                          |                                                                           | t on positive edge                |            |                  |        |                 |        |  |  |  |  |

| bit 1                                                                    | INT1EP: Ex                                                                | ternal Interrupt 1                | Edge Detec | t Polarity Selec | t bit  |                 |        |  |  |  |  |

|                                                                          |                                                                           | t on negative edg                 |            |                  |        |                 |        |  |  |  |  |

| 0 = Interrupt on positive edge                                           |                                                                           |                                   |            |                  |        |                 |        |  |  |  |  |

| bit 0                                                                    | INT0EP: External Interrupt 0 Edge Detect Polarity Select bit              |                                   |            |                  |        |                 |        |  |  |  |  |

|                                                                          | 1 = Interrupt on negative edge                                            |                                   |            |                  |        |                 |        |  |  |  |  |

|                                                                          | 0 – Interrun                                                              | t on positive edge                | <b>`</b>   |                  |        |                 |        |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| REGISTER 7    | 7-5: IFS0:                                                                          | INTERRUPT                        | FLAG STAT        | US REGISTE                        | ER 0             |                 |        |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------|----------------------------------|------------------|-----------------------------------|------------------|-----------------|--------|--|--|--|--|

| U-0           | U-0                                                                                 | R/W-0                            | R/W-0            | R/W-0                             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| —             |                                                                                     | ADIF                             | U1TXIF           | U1RXIF                            | SPI1IF           | SPI1EIF         | T3IF   |  |  |  |  |

| oit 15        |                                                                                     |                                  |                  |                                   |                  |                 | bit    |  |  |  |  |

| R/W-0         | R/W-0                                                                               | R/W-0                            | U-0              | R/W-0                             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| T2IF          | OC2IF                                                                               | IC2IF                            |                  | T1IF                              | OC1IF            | IC1IF           | INTOIF |  |  |  |  |

| bit 7         | 0021                                                                                | 10211                            |                  |                                   | 0011             | 10111           | bit    |  |  |  |  |

| Legend:       |                                                                                     |                                  |                  |                                   |                  |                 |        |  |  |  |  |

| R = Readable  | hit                                                                                 | W = Writable                     | hit              | LI – Unimplor                     | mented bit, read | d ac 'O'        |        |  |  |  |  |

| -n = Value at |                                                                                     | '1' = Bit is se                  |                  | 0 = 0 minipler<br>0' = Bit is cle |                  | x = Bit is unkn | 0000   |  |  |  |  |

|               | FÜR                                                                                 | 1 = DIL 15 50                    | ι                |                                   | aleu             |                 | OWI    |  |  |  |  |

| bit 15-14     | Unimplemer                                                                          | nted: Read as                    | ʻ0'              |                                   |                  |                 |        |  |  |  |  |

| bit 13        | ADIF: ADC C                                                                         | Group Convers                    | ion Complete I   | Interrupt Flag S                  | Status bit       |                 |        |  |  |  |  |

|               |                                                                                     | request has oc<br>request has no |                  |                                   |                  |                 |        |  |  |  |  |

| bit 12        | U1TXIF: UA                                                                          | RT1 Transmitte                   | r Interrupt Flag | g Status bit                      |                  |                 |        |  |  |  |  |

|               |                                                                                     | request has oc                   |                  |                                   |                  |                 |        |  |  |  |  |

|               | •                                                                                   | request has no                   |                  |                                   |                  |                 |        |  |  |  |  |

| bit 11        |                                                                                     | RT1 Receiver I                   |                  | Status bit                        |                  |                 |        |  |  |  |  |

|               |                                                                                     | request has oc<br>request has no |                  |                                   |                  |                 |        |  |  |  |  |

| bit 10        | -                                                                                   | Event Interrup                   |                  | oit                               |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt request has occurred                                                  |                                  |                  |                                   |                  |                 |        |  |  |  |  |

|               | •                                                                                   | request has no                   |                  |                                   |                  |                 |        |  |  |  |  |

| bit 9         | SPI1EIF: SPI1 Fault Interrupt Flag Status bit                                       |                                  |                  |                                   |                  |                 |        |  |  |  |  |

|               |                                                                                     | request has oc                   |                  |                                   |                  |                 |        |  |  |  |  |

| L:1 0         | -                                                                                   | request has no                   |                  |                                   |                  |                 |        |  |  |  |  |

| bit 8         | <b>T3IF:</b> Timer3 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                  |                  |                                   |                  |                 |        |  |  |  |  |

|               |                                                                                     | request has no                   |                  |                                   |                  |                 |        |  |  |  |  |

| bit 7         | -                                                                                   | Interrupt Flag                   |                  |                                   |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt                                                                       | request has oc                   | curred           |                                   |                  |                 |        |  |  |  |  |

|               | •                                                                                   | request has no                   |                  |                                   |                  |                 |        |  |  |  |  |

| bit 6         |                                                                                     | out Compare Cl                   |                  | upt Flag Status                   | s bit            |                 |        |  |  |  |  |

|               |                                                                                     | request has oc<br>request has no |                  |                                   |                  |                 |        |  |  |  |  |

| bit 5         | •                                                                                   | Capture Chanr                    |                  | Flag Status bit                   |                  |                 |        |  |  |  |  |

|               | -                                                                                   | request has oc                   | -                | lag claide bit                    |                  |                 |        |  |  |  |  |

|               |                                                                                     | request has no                   |                  |                                   |                  |                 |        |  |  |  |  |

| bit 4         | Unimplemer                                                                          | nted: Read as                    | ʻ0'              |                                   |                  |                 |        |  |  |  |  |

| bit 3         | T1IF: Timer1                                                                        | Interrupt Flag                   | Status bit       |                                   |                  |                 |        |  |  |  |  |

|               | •                                                                                   | request has oc<br>request has no |                  |                                   |                  |                 |        |  |  |  |  |

| bit 2         | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit                           |                                  |                  |                                   |                  |                 |        |  |  |  |  |

|               | -                                                                                   | request has oc                   |                  | -                                 |                  |                 |        |  |  |  |  |

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| U-0                          | U-0                                                     | U-0                                                                      | U-0                   | U-0                      | U-0             | U-0             | U-0    |  |  |  |  |  |

|------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|--------------------------|-----------------|-----------------|--------|--|--|--|--|--|

| _                            | —                                                       |                                                                          | _                     | —                        | _               | _               |        |  |  |  |  |  |

| oit 15                       |                                                         |                                                                          |                       |                          |                 |                 | bit    |  |  |  |  |  |

|                              |                                                         |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

| U-0                          | R/W-1                                                   | R/W-0                                                                    | R/W-0                 | U-0                      | R/W-1           | R/W-0           | R/W-0  |  |  |  |  |  |

| —                            | AC4IP2                                                  | AC4IP1                                                                   | AC4IP0                |                          | AC3IP2          | AC3IP1          | AC3IP0 |  |  |  |  |  |

| bit 7                        |                                                         |                                                                          |                       |                          |                 |                 | bit    |  |  |  |  |  |

|                              |                                                         |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

| <b>Legend:</b><br>R = Readat | le bit                                                  | W = Writable                                                             | hit                   | II – Unimplen            | nented bit, rea | d as '0'        |        |  |  |  |  |  |

| -n = Value a                 |                                                         | '1' = Bit is set                                                         |                       | '0' = Bit is clea        |                 | x = Bit is unkr |        |  |  |  |  |  |

|                              |                                                         |                                                                          |                       |                          | aleu            |                 | 100011 |  |  |  |  |  |

| bit 15-7                     | Unimplomon                                              | tod: Pood os '                                                           | 0'                    |                          |                 |                 |        |  |  |  |  |  |

|                              | -                                                       | Unimplemented: Read as '0'                                               |                       |                          |                 |                 |        |  |  |  |  |  |

| bit 6-4                      | AC4IP<2:0>: Analog Comparator 4 Interrupt Priority bits |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

|                              | 111 = Interrupt is Priority 7 (highest priority)        |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

|                              | •                                                       |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

|                              | •                                                       |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

|                              |                                                         |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

|                              | •                                                       |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

|                              | •<br>001 = Interru<br>000 = Interru                     | pt is Priority 1<br>pt source is dis                                     | abled                 |                          |                 |                 |        |  |  |  |  |  |

| bit 3                        | 000 = Interru                                           |                                                                          |                       |                          |                 |                 |        |  |  |  |  |  |

| bit 3<br>bit 2-0             | 000 = Interru<br>Unimplemen                             | pt source is dis<br>ted: Read as '                                       | 0'                    | upt Priority bits        |                 |                 |        |  |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>:              | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr | upt Priority bits<br>ty) |                 |                 |        |  |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>:              | pt source is dis<br>ted: Read as '                                       | 0'<br>arator 3 Interr |                          |                 |                 |        |  |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>:              | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr |                          |                 |                 |        |  |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>:              | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr |                          |                 |                 |        |  |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>:              | pt source is dis<br>ted: Read as '<br>Analog Compa<br>pt is Priority 7 ( | 0'<br>arator 3 Interr |                          |                 |                 |        |  |  |  |  |  |

#### REGISTER 7-31: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

| Input Name                                              | Function Name | Register | Configuration<br>Bits |

|---------------------------------------------------------|---------------|----------|-----------------------|

| External Interrupt 1                                    | INT1          | RPINR0   | INT1R<5:0>            |

| External Interrupt 2                                    | INT2          | RPINR1   | INT2R<5:0>            |

| Timer1 External Clock                                   | T1CK          | RPINR2   | T1CKR<5:0>            |

| Timer2 External Clock                                   | T2CK          | RPINR3   | T2CKR<5:0>            |

| Timer3 External Clock                                   | T3CK          | RPINR3   | T3CKR<5:0>            |

| Input Capture 1                                         | IC1           | RPINR7   | IC1R<5:0>             |

| Input Capture 2                                         | IC2           | RPINR7   | IC2R<5:0>             |

| Output Compare Fault A                                  | OCFA          | RPINR11  | OCFAR<5:0>            |

| UART1 Receive                                           | U1RX          | RPINR18  | U1RXR<5:0>            |

| UART1 Clear-to-Send                                     | U1CTS         | RPINR18  | U1CTSR<5:0>           |

| SPI Data Input 1                                        | SDI1          | RPINR20  | SDI1R<5:0>            |

| SPI Clock Input 1                                       | SCK1          | RPINR20  | SCK1R<5:0>            |

| SPI Slave Select Input 1                                | SS1           | RPINR21  | SS1R<5:0>             |

| PWM Fault Input PWM1                                    | FLT1          | RPINR29  | FLT1R<5:0>            |

| PWM Fault Input PWM2                                    | FLT2          | RPINR30  | FLT2R<5:0>            |

| PWM Fault Input PWM3                                    | FLT3          | RPINR30  | FLT3R<5:0>            |

| PWM Fault Input PWM4                                    | FLT4          | RPINR31  | FLT4R<5:0>            |

| PWM Fault Input PWM5                                    | FLT5          | RPINR31  | FLT5R<5:0>            |

| PWM Fault Input PWM6                                    | FLT6          | RPINR32  | FLT6R<5:0>            |

| PWM Fault Input PWM7                                    | FLT7          | RPINR32  | FLT7R<5:0>            |

| PWM Fault Input PWM8                                    | FLT8          | RPINR33  | FLT8R<5:0>            |

| External Synchronization signal to PWM Master Time Base | SYNCI1        | RPINR33  | SYNCI1R<5:0>          |

| External Synchronization signal to PWM Master Time Base | SYNCI2        | RPINR34  | SYNCI2R<5:0>          |

#### TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

| R/W-0                                 | U-0                                                                                                       | R/W-0                                                                                                           | U-0                                                                      | U-0                      | U-0             | U-0                               | U-0          |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------|-----------------|-----------------------------------|--------------|

| SPIEN                                 | _                                                                                                         | SPISIDL                                                                                                         | —                                                                        | —                        |                 | —                                 | —            |

| bit 15                                |                                                                                                           |                                                                                                                 |                                                                          |                          |                 |                                   | bit 8        |

| U-0                                   | R/C-0                                                                                                     | U-0                                                                                                             | U-0                                                                      | U-0                      | U-0             | R-0                               | R-0          |

|                                       | SPIROV                                                                                                    | —                                                                                                               | —                                                                        | _                        |                 | SPITBF                            | SPIRBF       |

| bit 7                                 |                                                                                                           |                                                                                                                 |                                                                          |                          |                 |                                   | bit 0        |

| Legend:                               |                                                                                                           | C = Clearable                                                                                                   | bit                                                                      |                          |                 |                                   |              |

| R = Readab                            | ole bit                                                                                                   | W = Writable I                                                                                                  | oit                                                                      | U = Unimpler             | nented bit, rea | d as '0'                          |              |

| -n = Value a                          | at POR                                                                                                    | '1' = Bit is set                                                                                                |                                                                          | '0' = Bit is cle         | ared            | x = Bit is unkr                   | nown         |

| bit 14<br>bit 13<br>bit 12-7<br>bit 6 | 0 = Disables<br>Unimplemen<br>SPISIDL: SPI<br>1 = Discontin<br>0 = Continues<br>Unimplemen<br>SPIROV: SPI | ted: Read as '(<br>Ix Stop in Idle M<br>ues module opera<br>s module opera<br>ted: Read as '(<br>x Receive Over | )'<br>lode bit<br>eration when<br>tion in Idle mo<br>)'<br>flow Flag bit | device enters I<br>ode   | dle mode        |                                   |              |

|                                       | previous<br>0 = No overfl                                                                                 | data in the SPI<br>low has occurre                                                                              | xBUF registe                                                             |                          | arded. The use  | er software has                   | not read the |

| bit 5-2                               | •                                                                                                         | ted: Read as '0                                                                                                 |                                                                          |                          |                 |                                   |              |

| bit 1                                 | 1 = Transmit<br>0 = Transmit<br>location,                                                                 |                                                                                                                 | SPIxTXB is t<br>B is empty. A<br>B. Automatic                            | full<br>Automatically se |                 | vhen CPU writes<br>en the SPIx mo |              |

| bit 0                                 | 1 = Receive<br>0 = Receive<br>data from                                                                   |                                                                                                                 | RXB is full<br>, SPIxRXB is<br>IxRXB. Auton                              | empty. Autom             |                 | hardware when<br>when core reads  |              |

### REGISTER 16-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

## 21.0 SPECIAL FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33F/PIC24H Family Reference Manual" sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

- Brown-out Reset (BOR)

### 21.1 Configuration Bits

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices provide nonvolatile memory implementations for device Configuration bits. Refer to **"Device Configuration"** (DS70194) in the *"dsPIC33F/PIC24H Family Reference Manual"* for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 21-2.

Note that address, 0xF80000, is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using Table Reads and Table Writes.

The device Configuration register map is shown in Table 21-1.

| Address  | Name     | Bit 7  | Bit 6               | Bit 5   | Bit 4  | Bit 3                   | Bit 2    | Bit 1    | Bit 0    |  |

|----------|----------|--------|---------------------|---------|--------|-------------------------|----------|----------|----------|--|

| 0xF80000 | FBS      | —      | _                   |         | — BSS2 |                         | BSS1     | BSS0     | BWRP     |  |

| 0xF80002 | Reserved | —      | _                   | _       |        |                         |          | —        | —        |  |

| 0xF80004 | FGS      | —      | _                   | _       |        |                         | GSS1     | GSS0     | GWRP     |  |

| 0xF80006 | FOSCSEL  | IESO   | _                   | _       | —      |                         | FNOSC2   | FNOSC1   | FNOSC0   |  |

| 0xF80008 | FOSC     | FCKSM1 | FCKSM0              | IOL1WAY |        |                         | OSCIOFNC | POSCMD1  | POSCMD0  |  |

| 0xF8000A | FWDT     | FWDTEN | WINDIS              | _       | WDTPRE | WDTPOST3                | WDTPOST2 | WDTPOST1 | WDTPOST0 |  |

| 0xF8000C | FPOR     | —      | —                   | —       | —      | Reserved <sup>(2)</sup> | FPWRT2   | FPWRT1   | FPWRT0   |  |

| 0xF8000E | FICD     | Reser  | ved <sup>(1)</sup>  | JTAGEN  |        |                         |          | ICS1     | ICS0     |  |

| 0xF80010 | FUID0    |        | User Unit ID Byte 0 |         |        |                         |          |          |          |  |

| 0xF80012 | FUID1    |        | User Unit ID Byte 1 |         |        |                         |          |          |          |  |

### TABLE 21-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: These bits are reserved for use by development tools and must be programmed to '1'.

2: This bit reads the current programmed value.

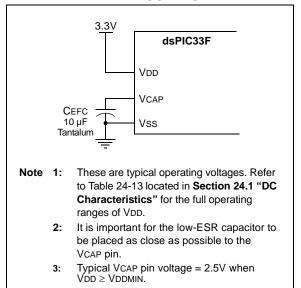

#### 21.2 On-Chip Voltage Regulator

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 21-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 24-13 located in **Section 24.1 "DC Characteristics"**.

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 21-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### 21.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| TABL               | E 22-2:              | INSTR                                                            | UCTION SET OVERVIE                  | W (CONTINUED)                          |               |                |                          |

|--------------------|----------------------|------------------------------------------------------------------|-------------------------------------|----------------------------------------|---------------|----------------|--------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                                                  | Assembly Syntax                     | Description                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 29                 | DIV                  | DIV.S                                                            | Wm, Wn                              | Signed 16/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.SD                                                           | Wm, Wn                              | Signed 32/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.U                                                            | Wm,Wn                               | Unsigned 16/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.UD                                                           | Wm,Wn                               | Unsigned 32/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF                                                             | Wm,Wn                               | Signed 16/16-bit Fractional Divide     | 1             | 18             | N,Z,C,OV                 |

| 31                 | DO                   | DO                                                               | <pre>#lit14,Expr</pre>              | Do code to PC + Expr, lit14 + 1 times  | 2             | 2              | None                     |

|                    |                      | DO                                                               | Wn,Expr                             | Do code to PC + Expr, (Wn) + 1 times   | 2             | 2              | None                     |

| 32                 | ED                   | ED                                                               | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance (no accumulate)     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                 | EDAC                 | EDAC                                                             | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance                     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 34                 | EXCH                 | EXCH                                                             | Wns,Wnd                             | Swap Wns with Wnd                      | 1             | 1              | None                     |

| 35                 | FBCL                 | FBCL                                                             | Ws,Wnd                              | Find Bit Change from Left (MSb) Side   | 1             | 1              | С                        |

| 36                 | FF1L                 | FF1L                                                             | Ws,Wnd                              | Find First One from Left (MSb) Side    | 1             | 1              | С                        |

| 37                 | FF1R                 | FF1R                                                             | Ws,Wnd                              | Find First One from Right (LSb) Side   | 1             | 1              | С                        |

| 38                 | GOTO                 | GOTO                                                             | Expr                                | Go to Address                          | 2             | 2              | None                     |

|                    |                      | GOTO                                                             | Wn                                  | Go to Indirect                         | 1             | 2              | None                     |

| 39                 | INC                  | INC                                                              | f                                   | f = f + 1                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC                                                              | f,WREG                              | WREG = f + 1                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC                                                              | Ws,Wd                               | Wd = Ws + 1                            | 1             | 1              | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2                                                             | f                                   | f = f + 2                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2                                                             | f,WREG                              | WREG = f + 2                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2                                                             | Ws,Wd                               | Wd = Ws + 2                            | 1             | 1              | C,DC,N,OV,Z              |

| 41                 | IOR                  | IOR                                                              | f                                   | f = f .IOR. WREG                       | 1             | 1              | N,Z                      |

|                    | -                    | IOR                                                              | f,WREG                              | WREG = f .IOR. WREG                    | 1             | 1              | N,Z                      |

|                    |                      | IOR                                                              | #lit10,Wn                           | Wd = lit10 .IOR. Wd                    | 1             | 1              | N,Z                      |

|                    |                      | IOR                                                              | Wb,Ws,Wd                            | Wd = Wb .IOR. Ws                       | 1             | 1              | N,Z                      |

|                    |                      | IOR                                                              | Wb,#lit5,Wd                         | Wd = Wb .IOR. lit5                     | 1             | 1              | N,Z                      |

| 42                 | LAC                  | LAC                                                              | Wso,#Slit4,Acc                      | Load Accumulator                       | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                 | LNK                  | LNK                                                              | #lit14                              | Link Frame Pointer                     | 1             | 1              | None                     |

| 44                 | LSR                  | LSR                                                              | f                                   | f = Logical Right Shift f              | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR                                                              | f,WREG                              | WREG = Logical Right Shift f           | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR                                                              | Ws,Wd                               | Wd = Logical Right Shift Ws            | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR                                                              | Wb,Wns,Wnd                          | Wnd = Logical Right Shift Wb by Wns    | 1             | 1              | N,Z                      |

|                    |                      | LSR                                                              | Wb,#lit5,Wnd                        | Wnd = Logical Right Shift Wb by lit5   | 1             | 1              | N,Z                      |

| 45                 | MAC                  | MAC                                                              | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Accumulate                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC                                                              | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd             | Square and Accumulate                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 46                 | MOV                  | MOV                                                              | f,Wn                                | Move f to Wn                           | 1             | 1              | None                     |

|                    |                      | MOV                                                              | f                                   | Move f to f                            | 1             | 1              | N,Z                      |

|                    |                      | MOV                                                              | f,WREG                              | Move f to WREG                         | 1             | 1              | None                     |

|                    |                      | MOV                                                              | #lit16,Wn                           | Move 16-bit Literal to Wn              | 1             | 1              | None                     |

|                    |                      | MOV.b                                                            | #lit8,Wn                            | Move 8-bit Literal to Wn               | 1             | 1              | None                     |

|                    |                      | MOV                                                              | Wn,f                                | Move Wn to f                           | 1             | 1              | None                     |

|                    |                      | MOV                                                              | Wso,Wdo                             | Move Ws to Wd                          | 1             | 1              | None                     |

|                    |                      | MOV                                                              | WREG, f                             | Move WREG to f                         | 1             | 1              | None                     |

|                    |                      | MOV.D                                                            | Wns,Wd                              | Move Double from W(ns):W(ns + 1) to Wd | 1             | 2              | None                     |

|                    |                      | MOV.D                                                            | Ws,Wnd                              | Move Double from Ws to W(nd + 1):W(nd) | 1             | 2              | None                     |

| 47                 | MOVSAC               | MOVSAC Acc, Wx, Wxd, Wy, Wyd, AWB Prefetch and Store Accumulator |                                     |                                        |               | 1              | None                     |

## TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### TABLE 24-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHAR      | DC CHARACTERISTICS |                                                                                                 |       | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3): 3.0V to 3.6V \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq T_A \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq T_A \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |      |       |            |  |  |

|--------------|--------------------|-------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------|--|--|

| Param<br>No. | Symbol             | Character                                                                                       | istic | Min <sup>(1)</sup>                                                                                                                                                                                                                                                                                | Тур | Max  | Units | Conditions |  |  |

| BO10         | VBOR               | BOR Event on VDD Transition<br>High-to-Low<br>BOR Event is Tied to VDD Core<br>Voltage Decrease |       | 2.55                                                                                                                                                                                                                                                                                              |     | 2.79 | V     | See Note 2 |  |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: The device will operate as normal until the VDDMIN threshold is reached.

**3:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN.

## dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

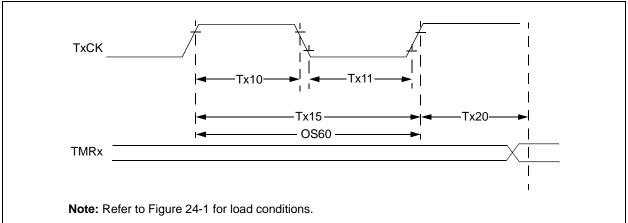

#### FIGURE 24-5: TIMER1, 2 AND 3 EXTERNAL CLOCK TIMING CHARACTERISTICS

| AC CHARACTERISTICS |           |                                                                                                    | (unl                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |               |       |                                                                            |

|--------------------|-----------|----------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|----------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Charao                                                                                             | cteristic                 | Min.                                                                                                                                                                                                                                                                                | Тур. | Max.          | Units | Conditions                                                                 |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                  | Synchronous no prescaler  | Tcy + 20                                                                                                                                                                                                                                                                            | —    | _             | ns    | Must also meet<br>Parameter TA15,<br>N = Prescale value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Synchronous with prescale |                                                                                                                                                                                                                                                                                     | —    | —             | ns    |                                                                            |

|                    |           |                                                                                                    | Asynchronou               | s 20                                                                                                                                                                                                                                                                                |      | —             | ns    |                                                                            |

| TA11               | ΤτχL      | Time i                                                                                             | Synchronous no prescaler  | Tcy + 20                                                                                                                                                                                                                                                                            | —    | —             | ns    | Must also meet<br>Parameter TA15,<br>N = Prescale value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Synchronous with prescale |                                                                                                                                                                                                                                                                                     | —    | —             | ns    |                                                                            |

|                    |           |                                                                                                    | Asynchronou               | s 20                                                                                                                                                                                                                                                                                | —    | —             | ns    |                                                                            |

| TA15               | ΤτχΡ      | Period no<br>Syr<br>with                                                                           | Synchronous no prescaler  | 2 Tcy + 40                                                                                                                                                                                                                                                                          | _    | —             | ns    |                                                                            |

|                    |           |                                                                                                    | Synchronous with prescale |                                                                                                                                                                                                                                                                                     | —    | _             | _     | N = Prescale value<br>(1, 8, 64, 256)                                      |

|                    |           |                                                                                                    | Asynchronou               | s 40                                                                                                                                                                                                                                                                                | —    | —             | ns    |                                                                            |

| OS60               | F⊤1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                           | DC                                                                                                                                                                                                                                                                                  | _    | 50            | kHz   |                                                                            |