Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\sim$   $\equiv$

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 2K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Through Hole                                                                      |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                           |

| Supplier Device Package    | 28-SPDIP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402-50i-sp |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3 Special MCU Features

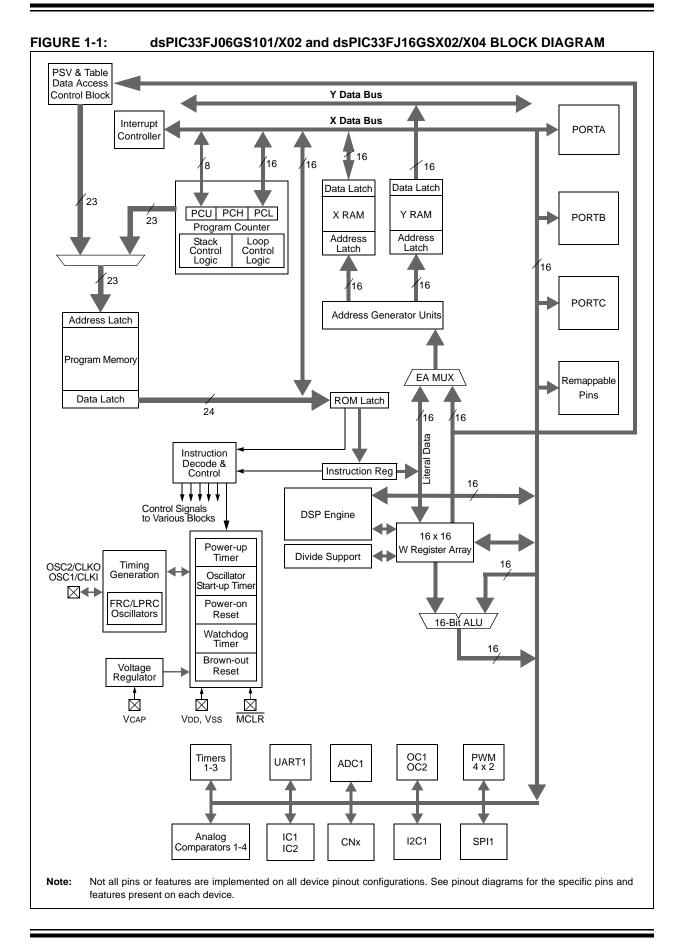

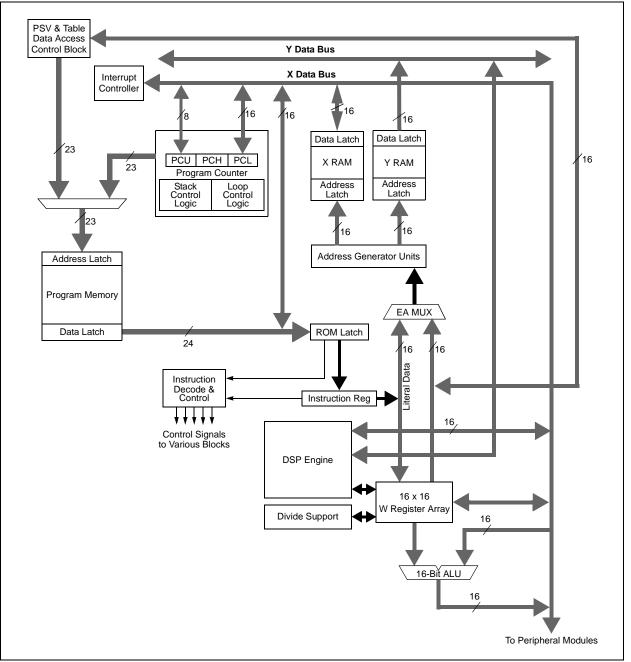

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices feature a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (1.0).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices support 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

FIGURE 3-1: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 CPU CORE BLOCK DIAGRAM

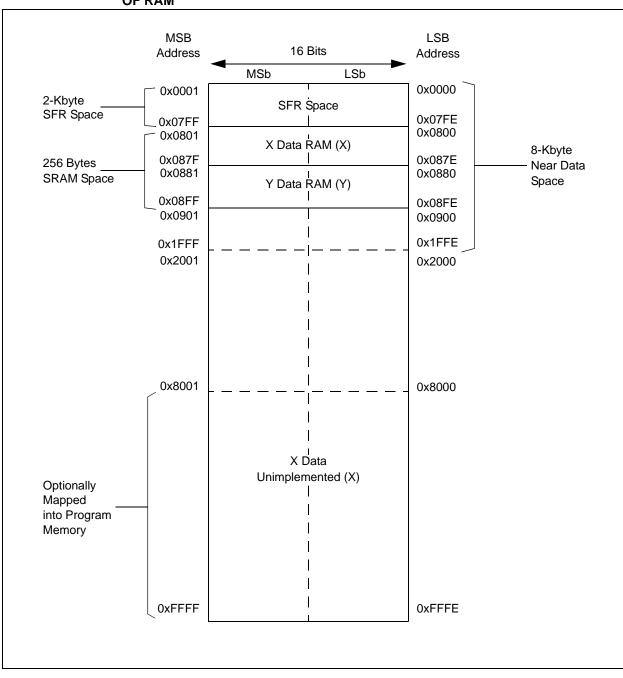

### FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJ06GS101/102 DEVICES WITH 256 BYTES OF RAM

### REGISTER 7-12: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0    | U-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0   |

|--------|-----|-----|-----|------|------|------|-------|

| —      | —   | _   | —   | ILR3 | ILR2 | ILR1 | ILR0  |

| bit 15 |     |     |     |      |      |      | bit 8 |

### REGISTER 7-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0   | R-0     |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:      |                 |                                |                        |                    |

|--------------|-----------------|--------------------------------|------------------------|--------------------|

| R = Readab   | le bit          | W = Writable bit               | U = Unimplemented bit, | , read as '0'      |

| -n = Value a | t POR           | '1' = Bit is set               | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-12    | Unimplen        | nented: Read as '0'            |                        |                    |

|              | •               |                                | (Loval bita            |                    |

| bit 11-8     |                 | New CPU Interrupt Priority     |                        |                    |

|              | 1111 <b>= C</b> | PU Interrupt Priority Level in | s 15                   |                    |

|              | •               |                                |                        |                    |

|              | •               |                                |                        |                    |

|              | •               |                                | - 4                    |                    |

|              |                 | PU Interrupt Priority Level is |                        |                    |

|              |                 | PU Interrupt Priority Level i  | 50                     |                    |

| bit 7        | Unimplen        | nented: Read as '0'            |                        |                    |

| bit 6-0      | VECNUM          | <6:0>: Vector Number of P      | ending Interrupt bits  |                    |

|              | 0111111         | = Interrupt vector pending i   | is Number 135          |                    |

|              | •               |                                |                        |                    |

|              | •               |                                |                        |                    |

|              | •               |                                |                        |                    |

|              | 0000001         | = Interrupt vector pending i   | is Number 9            |                    |

|              | 0000000         | = Interrupt vector pending i   | is Number 8            |                    |

|              |                 |                                |                        |                    |

|               |             |                 | -              |                                     | -                |                    |           |

|---------------|-------------|-----------------|----------------|-------------------------------------|------------------|--------------------|-----------|

| U-0           | U-0         | U-0             | U-0            | U-0                                 | U-0              | U-0                | R/W-0     |

|               |             | —               |                | —                                   | —                | —                  | PLLDIV<8> |

| bit 15        |             |                 |                |                                     |                  |                    | bit 8     |

| R/W-0         | R/W-0       | R/W-1           | R/W-1          | R/W-0                               | R/W-0            | R/W-0              | R/W-0     |

| 10000         | 10,00 0     |                 |                | IV<7:0>                             | 1000 0           | 10000              | 1010 0    |

| bit 7         |             |                 |                |                                     |                  |                    | bit 0     |

| Legend:       |             |                 |                |                                     |                  |                    |           |

| R = Readabl   | le bit      | W = Writable    | bit            | U = Unimpler                        | mented bit, read | l as '0'           |           |

| -n = Value at |             | 1' = Bit is set |                | $0^{\circ} = \text{Bit is cleared}$ |                  | x = Bit is unknown |           |

|               |             |                 |                |                                     |                  |                    |           |

| bit 15-9      | Unimplemen  | ted: Read as '  | י'             |                                     |                  |                    |           |

| bit 8-0       | PLLDIV<8:0> | >: PLL Feedbac  | k Divisor bits | (also denoted                       | as 'M', PLL mu   | ltiplier)          |           |

|               | 111111111 = | = 513           |                |                                     |                  |                    |           |

|               | •           |                 |                |                                     |                  |                    |           |

|               | •           |                 |                |                                     |                  |                    |           |

|               | •           |                 |                |                                     |                  |                    |           |

|               | 000110000=  | = 50 (default)  |                |                                     |                  |                    |           |

|               | •           |                 |                |                                     |                  |                    |           |

|               | •           |                 |                |                                     |                  |                    |           |

|               | •           |                 |                |                                     |                  |                    |           |

|               | 000000010=  | = 4             |                |                                     |                  |                    |           |

|               | 000000001 = |                 |                |                                     |                  |                    |           |

|               | 000000000 = | = 2             |                |                                     |                  |                    |           |

|               |             |                 |                |                                     |                  |                    |           |

## REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

NOTES:

| U-0                   | U-0                                                                                                                                                         | R/W-1                                                                                                                                                                                                                                    | R/W-1                                              | R/W-1             | R/W-1           | R/W-1           | R/W-1 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|-----------------|-----------------|-------|

|                       | _                                                                                                                                                           | IC2R5                                                                                                                                                                                                                                    | IC2R4                                              | IC2R3             | IC2R2           | IC2R1           | IC2R0 |

| bit 15                |                                                                                                                                                             |                                                                                                                                                                                                                                          |                                                    |                   |                 |                 | bit   |

| U-0                   | U-0                                                                                                                                                         | R/W-1                                                                                                                                                                                                                                    | R/W-1                                              | R/W-1             | R/W-1           | R/W-1           | R/W-1 |

|                       | —                                                                                                                                                           | IC1R5                                                                                                                                                                                                                                    | IC1R4                                              | IC1R3             | IC1R2           | IC1R1           | IC1R0 |

| bit 7                 |                                                                                                                                                             |                                                                                                                                                                                                                                          |                                                    |                   |                 |                 | bit   |

| Legend:               |                                                                                                                                                             |                                                                                                                                                                                                                                          |                                                    |                   |                 |                 |       |

| R = Readab            | le bit                                                                                                                                                      | W = Writable                                                                                                                                                                                                                             | bit                                                | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value a          | t POR                                                                                                                                                       | '1' = Bit is set                                                                                                                                                                                                                         | t                                                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-14<br>bit 13-8 | IC2R<5:0>: /                                                                                                                                                | ÷ .                                                                                                                                                                                                                                      |                                                    | to the Correspo   | onding RPn Pi   | n bits          |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                | but tied to Vss<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3                                                                                                                           | 4<br>3                                             |                   |                 |                 |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                | out tied to RP3<br>out tied to RP3<br>out tied to RP3                                                                                                                                                                                    | 4<br>3                                             |                   |                 |                 |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                | but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3                                                                                                                                              | 4<br>3                                             |                   |                 |                 |       |

| bit 7-6               | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•                                                                                      | but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3                                                                                                                                              | 4<br>3<br>2                                        |                   |                 |                 |       |

| bit 7-6<br>bit 5-0    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>ut tied to RP0<br>hted: Read as f                                                                                                         | 4<br>3<br>2<br>0'                                  | to the Correspo   | onding RPn Pi   | n bits          |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>ut tied to RP0<br>hted: Read as f                                                                                                         | 4<br>3<br>2<br>0'<br>apture 1 (IC1)<br>5<br>4<br>3 | to the Correspo   | onding RPn Pi   | n bits          |       |

|                       | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | but tied to RP3<br>but tied to RP0<br><b>Ited:</b> Read as '<br>Assign Input Ca<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3<br>but tied to RP3; | 4<br>3<br>2<br>0'<br>apture 1 (IC1)<br>5<br>4<br>3 | to the Correspo   | onding RPn Pi   | n bits          |       |

### REGISTER 10-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0    | U-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|------|--------|--------|--------|--------|--------|--------|

|        | —    | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |      |        |        |        |        |        | bit 8  |

|        |      |        |        |        |        |        |        |

| 11.0   | 11.0 |        |        |        |        |        |        |

### REGISTER 10-20: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5<sup>(1)</sup>

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP11R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP10R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is not implemented in the dsPIC33FJ06GS101 device.

| U-0         | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0           | R/W-0  | R/W-0  |

|-------------|-----|--------|--------|--------|-----------------|--------|--------|

| —           | —   | RP13R5 | RP13R4 | RP13R3 | RP13R2          | RP13R1 | RP13R0 |

| bit 15      |     |        |        |        |                 |        | bit 8  |

|             |     |        |        |        |                 |        |        |

| U-0         | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0           | R/W-0  | R/W-0  |

| —           | —   | RP12R5 | RP12R4 | RP12R3 | RP12R2          | RP12R1 | RP12R0 |

| bit 7       |     |        |        |        |                 |        | bit 0  |

|             |     |        |        |        |                 |        |        |

| Legend:     |     |        |        |        |                 |        |        |

| D Doodoblob | :+  |        | h:+    |        | nonted hit read | oo 'O' |        |

## **REGISTER 10-21:** RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6<sup>(1)</sup>

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP13R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP13 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP12R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP12 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is not implemented in the dsPIC33FJ06GS101 device.

### REGISTER 15-4: SEVTCMP: PWM SPECIAL EVENT COMPARE REGISTER

| R/W-0                              | R/W-0 | R/W-0            | R/W-0                              | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|------------------|------------------------------------|-----------------|-------|-------|-------|

|                                    |       |                  | SEVTC                              | MP <15:8>       |       |       |       |

| bit 15                             |       |                  |                                    |                 |       |       | bit 8 |

| Г                                  |       |                  |                                    |                 |       |       |       |

| R/W-0                              | R/W-0 | R/W-0            | R/W-0                              | R/W-0           | U-0   | U-0   | U-0   |

|                                    | SE    | EVTCMP <7:3>     | •                                  |                 | —     | —     | —     |

| bit 7                              |       |                  |                                    |                 |       |       | bit 0 |

| Legend:                            |       |                  |                                    |                 |       |       |       |

| R = Readable bit W = Writable bit  |       |                  | U = Unimplemented bit, read as '0' |                 |       |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cle | ared                               | x = Bit is unkr | nown  |       |       |

bit 15-3 SEVTCMP<12:0>: Special Event Compare Count Value bits

bit 2-0 Unimplemented: Read as '0'

### **REGISTER 15-5:** MDC: PWM MASTER DUTY CYCLE REGISTER<sup>(1,2)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------|-----------------|-----------------|-------|-------|

|                                    |       |       | MDC              | <15:8>          |                 |       |       |

| bit 15                             |       |       |                  |                 |                 |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | MDC              | C<7:0>          |                 |       |       |

| bit 7                              |       |       |                  |                 |                 |       | bit C |

| Legend:                            |       |       |                  |                 |                 |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplen     | nented bit, rea | d as '0'        |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |       |

bit 15-0 MDC<15:0>: Master PWM Duty Cycle Value bits

**Note 1:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

### REGISTER 19-5: ADCPC0: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 0

| R/W-0  | R/W-0 | R/W-0  | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|--------|-------|--------|----------|----------|----------|----------|----------|

| IRQEN1 | PEND1 | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 |

| bit 15 |       |        |          |          |          |          | bit 8    |

| R/W-0  | R/W-0 | R/W-0  | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|--------|-------|--------|----------|----------|----------|----------|----------|

| IRQEN0 | PEND0 | SWTRG0 | TRGSRC04 | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 |

| bit 7  |       |        |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15  | IRQEN1: Interrupt Request Enable 1 bit                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables IRQ generation when requested conversion of Channels AN3 and AN2 is completed</li> <li>0 = IRQ is not generated</li> </ul>                                                                               |

| bit 14  | PEND1: Pending Conversion Status 1 bit                                                                                                                                                                                        |

|         | <ul> <li>1 = Conversion of Channels AN3 and AN2 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul>                                                                              |

| bit 13  | SWTRG1: Software Trigger 1 bit                                                                                                                                                                                                |

|         | <ul> <li>1 = Starts conversion of AN3 and AN2 (if selected by the TRGSRCx bits)<sup>(1)</sup><br/>This bit is automatically cleared by hardware when the PEND1 bit is set.</li> <li>0 = Conversion has not started</li> </ul> |

| Note 1: | The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions                                                                                                            |

**Note 1:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

### REGISTER 19-6: ADCPC1: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 1

| R/W-0                 | R/W-0                | R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   |

|-----------------------|----------------------|-----------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| IRQEN3 <sup>(1)</sup> | PEND3 <sup>(1)</sup> | SWTRG3 <sup>(1)</sup> | TRGSRC34 <sup>(1)</sup> | TRGSRC33 <sup>(1)</sup> | TRGSRC32 <sup>(1)</sup> | TRGSRC31 <sup>(1)</sup> | TRGSRC30 <sup>(1)</sup> |

| bit 15                |                      |                       |                         |                         |                         |                         | bit 8                   |

| R/W-0                 | R/W-0                | R/W-0     | R/W-0       | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   |

|-----------------------|----------------------|-----------|-------------|-------------------------|-------------------------|-------------------------|-------------------------|

| IRQEN2 <sup>(2)</sup> | PEND2 <sup>(2)</sup> | SWTRG2(2) | TRGSRC24(2) | TRGSRC23 <sup>(2)</sup> | TRGSRC22 <sup>(2)</sup> | TRGSRC21 <sup>(2)</sup> | TRGSRC20 <sup>(2)</sup> |

| bit 7                 |                      |           |             |                         |                         |                         | bit 0                   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, reac | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | <b>IRQEN3:</b> Interrupt Request Enable 3 bit <sup>(1)</sup><br>1 = Enables IRQ generation when requested conversion of Channels AN7 and AN6 is completed<br>0 = IRQ is not generated                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14  | PEND3: Pending Conversion Status 3 bit <sup>(1)</sup>                                                                                                                                                                         |

|         | <ul> <li>1 = Conversion of Channels AN7 and AN6 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul>                                                                              |

| bit 13  | SWTRG3: Software Trigger 3 bit <sup>(1)</sup>                                                                                                                                                                                 |

|         | <ul> <li>1 = Starts conversion of AN7 and AN6 (if selected by the TRGSRCx bits)<sup>(3)</sup><br/>This bit is automatically cleared by hardware when the PEND3 bit is set.</li> <li>0 = Conversion has not started</li> </ul> |

| Note 1: | These bits are available in the dsPIC33FJ16GS402/404, dsPIC33FJ16GS504, dsPIC33FJ16GS502 and dsPIC33FJ06GS101 devices only.                                                                                                   |

- 2: These bits are available in the dsPIC33FJ16GS502, dsPIC33FJ16GS504, dsPIC33FJ06GS102, dsPIC33FJ06GS202 and dsPIC33FJ16GS402/404 devices only.

- **3:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

#### REGISTER 19-7: ADCPC2: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 2<sup>(1)</sup> (CONTINUED)

```

bit 4-0

TRGSRC4<4:0>: Trigger 4 Source Selection bits

Selects trigger source for conversion of Analog Channels AN9 and AN8.

11111 = Timer2 period match

11011 = Reserved

11010 = PWM Generator 4 current-limit ADC trigger

11001 = PWM Generator 3 current-limit ADC trigger

11000 = PWM Generator 2 current-limit ADC trigger

10111 = PWM Generator 1 current-limit ADC trigger

10110 = Reserved

10010 = Reserved

10001 = PWM Generator 4 secondary trigger is selected

10000 = PWM Generator 3 secondary trigger is selected

01111 = PWM Generator 2 secondary trigger is selected

01110 = PWM Generator 1 secondary trigger is selected

01101 = Reserved

01100 = Timer1 period match

01000 = Reserved

00111 = PWM Generator 4 primary trigger is selected

00110 = PWM Generator 3 primary trigger is selected

00101 = PWM Generator 2 primary trigger is selected

00100 = PWM Generator 1 primary trigger is selected

00011 = PWM Special Event Trigger is selected

00010 = Global software trigger is selected

00001 = Individual software trigger is selected

00000 = No conversion is enabled

```

- Note 1: This register is only implemented in the dsPIC33FJ16GS504 devices.

- 2: The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

## REGISTER 19-8: ADCPC3: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup>

| bit 4-0 | TRGSRC6<4:0>: Trigger 6 Source Selection bits<br>Selects trigger source for conversion of Analog Channels AN13 and AN12.<br>11111 = Timer2 period match |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00111 = PWM Generator 4 primary trigger is selected<br>00110 = PWM Generator 3 primary trigger is selected                                              |

- Note 1: This register is only implemented on the dsPIC33FJ16GS502 and dsPIC33FJ16GS504 devices.

- 2: The trigger source must be set as global software trigger prior to setting this bit to '1'. If other conversions are in progress, conversion will be performed when the conversion resources are available.

| DC CHARACTERISTICS |                            |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |       |                                              |  |  |

|--------------------|----------------------------|------|------------------------------------------------------|------------|-------|----------------------------------------------|--|--|

| Parameter<br>No.   | Typical <sup>(1)</sup>     | Мах  | Units                                                | Conditions |       |                                              |  |  |

| Power-Down         | Current (IPD) <sup>(</sup> | 2,4) |                                                      |            |       |                                              |  |  |

| DC60d              | 125                        | 500  | μA                                                   | -40°C      |       |                                              |  |  |

| DC60a              | 135                        | 500  | μΑ                                                   | +25°C      | 3.3V  | Base Power-Down Current                      |  |  |

| DC60b              | 235                        | 500  | μΑ                                                   | +85°C      | 3.3V  | Base Power-Down Current                      |  |  |

| DC60c              | 565                        | 950  | μΑ                                                   | +125°C     |       |                                              |  |  |

| DC61d              | 40                         | 50   | μΑ                                                   | -40°C      |       |                                              |  |  |

| DC61a              | 40                         | 50   | μΑ                                                   | +25°C      | 2.21/ | Match do a Time of Course at Aburat(3)       |  |  |

| DC61b              | 40                         | 50   | μA                                                   | +85°C      | 3.3V  | Watchdog Timer Current: ∆IwDT <sup>(3)</sup> |  |  |

| DC61c              | 80                         | 90   | μA                                                   | +125°C     |       |                                              |  |  |

#### TABLE 24-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: Data in the Typical column is at 3.3V, +25°C unless otherwise stated.

2: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all ones)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- JTAG disabled

- **3:** The ∆ current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

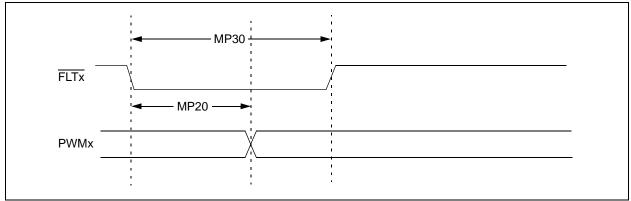

#### FIGURE 24-9: HIGH-SPEED PWMx MODULE FAULT TIMING CHARACTERISTICS

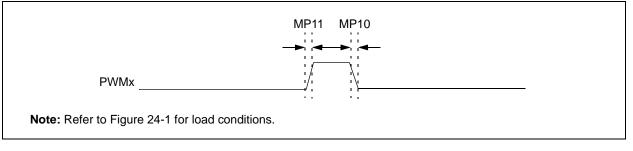

### FIGURE 24-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

### TABLE 24-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |     |     |       |                |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------|----------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min  | Тур | Max | Units | Conditions     |

| MP10               | TFPWM  | PWMx Output Fall Time                                                                                                                                                                                                                                                                   | —    | 2.5 | —   | ns    |                |

| MP11               | TRPWM  | PWMx Output Rise Time                                                                                                                                                                                                                                                                   | —    | 2.5 | —   | ns    |                |

| MP20               | Tfd    | Fault Input ↓ to PWM<br>I/O Change                                                                                                                                                                                                                                                      | —    |     | 15  | ns    |                |

| MP30               | Тғн    | Minimum PWMx Fault Pulse<br>Width                                                                                                                                                                                                                                                       | 8    | _   | —   | ns    | DTC<1:0> = 10  |

| MP31               | TPDLY  | Tap Delay                                                                                                                                                                                                                                                                               | 1.04 | —   | —   | ns    | Аськ = 120 MHz |

| MP32               | ACLK   | PWMx Input Clock                                                                                                                                                                                                                                                                        |      | _   | 120 | MHz   | See Note 2     |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: This parameter is a maximum allowed input clock for the PWMx module.

| DC CHARACTERISTICS |         | Standard Operating Conditions (see Note 1): 3.0V to 3.6V<br>Operating temperature: $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |               |       |               |       |                                                                                                |

|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|---------------|-------|------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol  | Characteristic                                                                                                                                                                                   | Min           | Тур   | Max           | Units | Comments                                                                                       |

| DA10               | RLOAD   | Resistive Output Load<br>Impedance                                                                                                                                                               | ЗК            | _     | —             | Ω     |                                                                                                |

| DA11               | CLOAD   | Output Load Capacitance                                                                                                                                                                          | —             | 20    | 35            | pF    |                                                                                                |

| DA12               | Ιουτ    | Output Current Drive<br>Strength                                                                                                                                                                 | -1740         | ±1400 | +1770         | μA    | Sink and source                                                                                |

| DA13               | VRANGE  | Full Output Drive Strength<br>Voltage Range                                                                                                                                                      | AVss + 250 mV |       | AVDD – 900 mV | V     |                                                                                                |

| DA14               | VLRANGE | Output Drive Voltage<br>Range at Reduced<br>Current Drive of 50 μA                                                                                                                               | AVss + 50 mV  | _     | AVDD – 500 mV | V     |                                                                                                |

| DA15               | IDD     | Current Consumed when<br>Module is Enabled,<br>High-Power Mode                                                                                                                                   | 369           | 626   | 948           | μΑ    | Module will always<br>consume this<br>current even if no<br>load is connected to<br>the output |

| DA16               | ROUTON  | Output Impedance when<br>Module is Enabled                                                                                                                                                       | —             | 1200  | —             | Ω     |                                                                                                |

### TABLE 24-44: DAC OUTPUT BUFFER DC SPECIFICATIONS

**Note 1:** Module is functional at VBOR < VDD < VDDMIN, but with degraded performance. Module functionality is tested but not characterized.

### 28.1 Package Marking Information (Continued)

44-Lead QFN

44-Lead TQFP

44-Lead VTLA (TLA)

Example

Example

Example

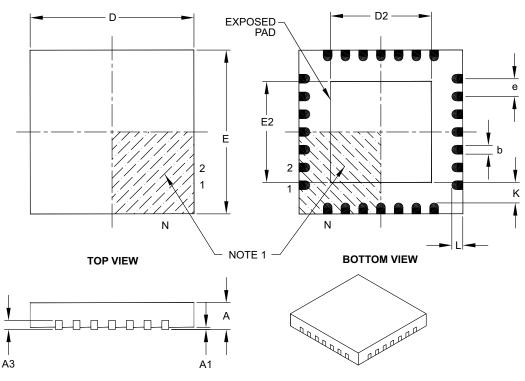

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |          |      |  |  |

|------------------------|------------------|-------------|----------|------|--|--|

| Dimens                 | Dimension Limits |             | NOM      | MAX  |  |  |

| Number of Pins         | Ν                | 28          |          |      |  |  |

| Pitch                  | е                | 0.65 BSC    |          |      |  |  |

| Overall Height         | А                | 0.80        | 0.90     | 1.00 |  |  |

| Standoff               | A1               | 0.00        | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3               | 0.20 REF    |          |      |  |  |

| Overall Width          | E                | 6.00 BSC    |          |      |  |  |

| Exposed Pad Width      | E2               | 3.65        | 3.70     | 4.70 |  |  |

| Overall Length         | D                |             | 6.00 BSC |      |  |  |

| Exposed Pad Length     | D2               | 3.65        | 3.70     | 4.70 |  |  |

| Contact Width          | b                | 0.23        | 0.38     | 0.43 |  |  |

| Contact Length         | L                | 0.30        | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | К                | 0.20        | -        | -    |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124B

| TABLE A-1: | MAJOR SECTION UPDATES (CONTINUED) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Section Name             | Update Description                                                                                                                                                                                                                            |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 23.0 "Electrical | Updated Typ values for Thermal Packaging Characteristics (Table 23-3).                                                                                                                                                                        |

| Characteristics"         | Removed Typ value for DC Temperature and Voltage Specifications Parameter DC12 (Table 23-4).                                                                                                                                                  |

|                          | Updated all Typ values and conditions for DC Characteristics: Operating Current (IDD), updated last sentence in Note 2 (Table 23-5).                                                                                                          |

|                          | Updated all Typ values for DC Characteristics: Idle Current (IIDLE) (see Table 23-6).                                                                                                                                                         |

|                          | Updated all Typ values for DC Characteristics: Power Down Current (IPD) (see Table 23-7).                                                                                                                                                     |

|                          | Updated all Typ values for DC Characteristics: Doze Current (IDOZE) (see Table 23-8).                                                                                                                                                         |

|                          | Added Note 4 (reference to new table containing digital-only and analog pin information, as well as Current Sink/Source capabilities) in the I/O Pin Input Specifications (Table 23-9).                                                       |

|                          | Updated Max value for BOR electrical characteristics Parameter BO10 (see Table 23-11).                                                                                                                                                        |

|                          | Swapped Min and Typ values for Program Memory Parameters D136 and D137 (Table 23-12).                                                                                                                                                         |

|                          | Updated Typ values for Internal RC Accuracy Parameter F20 and added Extended temperature range to table heading (see Table 23-19).                                                                                                            |

|                          | Removed all values for Reset, Watchdog Timer, Oscillator Start-up Timer, and Power-up Timer Parameter SY20 and updated conditions, which now refers to <b>Section 20.4 "Watchdog Timer (WDT)</b> " and LPRC Parameter F21a (see Table 23-22). |

|                          | Added specifications to High-Speed PWM Module Timing Requirements for Tap Delay (Table 23-29).                                                                                                                                                |

|                          | Updated Min and Max values for 10-bit High-Speed Analog-to-Digital Module Parameters AD01 and AD11 (see Table 23-36).                                                                                                                         |

|                          | Updated Max value and unit of measure for DAC AC Specification (see Table 23-40).                                                                                                                                                             |